Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gz32vfaer |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Specific features in 48-pin LQFP are:

- Port A is 8 bits: PTA0-PTA7; shared with ADC and KBI modules

- Port B is 8 bits: PTB0–PTB7; shared with ADC module

- Port C is only 7 bits: PTC0–PTC6; shared with MSCAN module

- Port D is 8 bits: PTD0-PTD7; shared with SPI, TIM1, and TIM2 modules

- Port E is only 6 bits: PTE0-PTE5; shared with ESCI module

- Specific features in 64-pin QFP are:

- Port A is 8 bits: PTA0-PTA7; shared with ADC and KBI modules

- Port B is 8 bits: PTB0-PTB7; shared with ADC module

- Port C is only 7 bits: PTC0-PTC6; shared with MSCAN module

- Port D is 8 bits: PTD0-PTD7; shared with SPI, TIM1, andTIM2 modules

- Port E is only 6 bits: PTE0-PTE5; shared with ESCI module

- Port F is 8 bits: PTF0-PTF7; shared with TIM2 module

- Port G is 8 bits; PTG0–PTG7; shared with ADC module

#### 1.2.2 Features of the CPU08

Features of the CPU08 include:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908GZ60. Refer to Appendix A MC68HC908GZ48 and Appendix B MC68HC908GZ32.

# 1.4 Pin Assignments

Figure 1-2, Figure 1-3, and Figure 1-4 illustrate the pin assignments for the 32-pin LQFP, 48-pin LQFP, and 64-pin QFP respectively.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

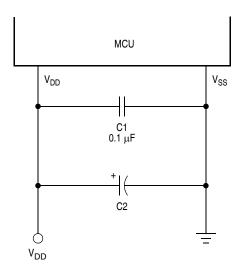

Note: Component values shown represent typical applications.

Figure 1-5. Power Supply Bypassing

# 1.5.2 Oscillator Pins (OSC1 and OSC2)

OSC1 and OSC2 are the connections for an external crystal, resonator, or clock circuit. See Chapter 4 Clock Generator Module (CGM).

# 1.5.3 External Reset Pin (RST)

A low on the  $\overline{RST}$  pin forces the MCU to a known startup state.  $\overline{RST}$  is bidirectional, allowing a reset of the entire system. It is driven low when any internal reset source is asserted. This pin contains an internal pullup resistor. See Chapter 15 System Integration Module (SIM).

# 1.5.4 External Interrupt Pin (IRQ)

IRQ is an asynchronous external interrupt pin. This pin contains an internal pullup resistor. See Chapter 8 External Interrupt (IRQ).

# 1.5.5 CGM Power Supply Pins ( $V_{DDA}$ and $V_{SSA}$ )

$V_{DDA}$  and  $V_{SSA}$  are the power supply pins for the analog portion of the clock generator module (CGM). Decoupling of these pins should be as per the digital supply. See Chapter 4 Clock Generator Module (CGM).

# 1.5.6 External Filter Capacitor Pin (CGMXFC)

CGMXFC is an external filter capacitor connection for the CGM. See Chapter 4 Clock Generator Module (CGM).

# 1.5.7 ADC Power Supply/Reference Pins (V<sub>DDAD</sub>/V<sub>REFH</sub> and V<sub>SSAD</sub>/V<sub>REFL</sub>)

$V_{DDAD}$  and  $V_{SSAD}$  are the power supply pins to the analog-to-digital converter (ADC).  $V_{REFH}$  and  $V_{REFL}$  are the reference voltage pins for the ADC.  $V_{REFH}$  is the high reference supply for the ADC, and by default the  $V_{DDAD}/V_{REFH}$  pin should be externally filtered and connected to the same voltage potential as  $V_{DD}$ .

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

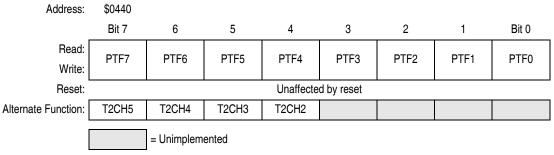

# **1.5.13 Port F I/O Pins (PTF7/T2CH5-PTF0)**

PTF7–PTF4 are special-function, bidirectional I/O port pins that can be individually programmed to be timer interface module (TIM2) pins.

PTF3-PTF0 are general-purpose, bidirectional I/O port pins that contain higher current sink/source capability.

PTF7–PTF0 are only available on the 64-pin QFP package. See Chapter 18 Timer Interface Module (TIM1), Chapter 19 Timer Interface Module (TIM2), and Chapter 13 Input/Output (I/O) Ports.

# 1.5.14 Port G I/O Pins (PTG7/AD23-PTBG0/AD16)

PTG7–PTG0 are general-purpose, bidirectional I/O port pins that can also be used for analog-to-digital converter (ADC) inputs. PTG7–PTG0 are only available on the 64-pin QFP package. See Chapter 13 Input/Output (I/O) Ports and Chapter 3 Analog-to-Digital Converter (ADC).

#### 1.5.15 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to  $V_{DD}$  or  $V_{SS}$ .

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

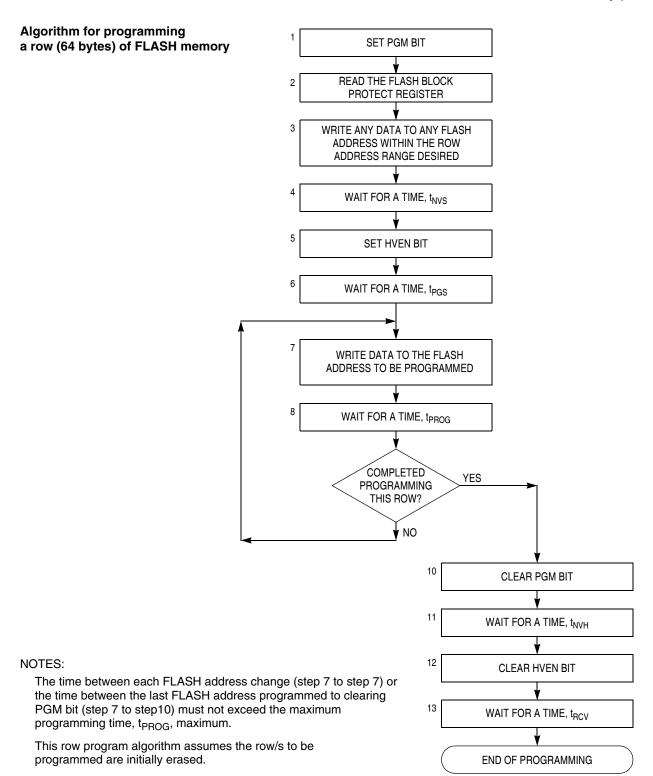

Figure 2-6. FLASH-1 Programming Algorithm Flowchart

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

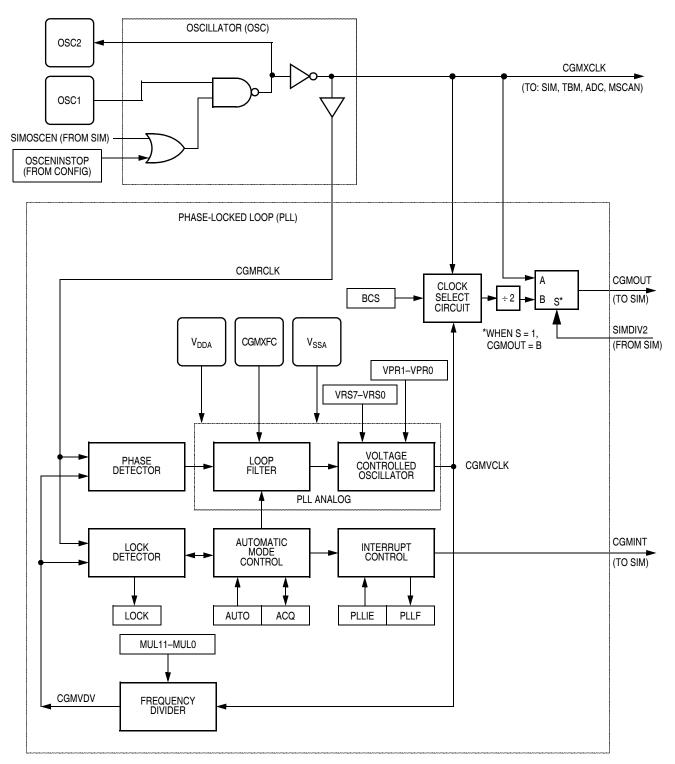

#### **Clock Generator Module (CGM)**

Figure 4-1. CGM Block Diagram

#### **Clock Generator Module (CGM)**

External factors, however, can cause drastic changes in the operation of the PLL. These factors include noise injected into the PLL through the filter capacitor, filter capacitor leakage, stray impedances on the circuit board, and even humidity or circuit board contamination.

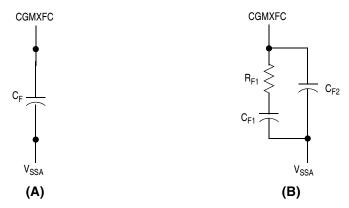

# 4.8.3 Choosing a Filter

As described in 4.8.2 Parametric Influences on Reaction Time, the external filter network is critical to the stability and reaction time of the PLL. The PLL is also dependent on reference frequency and supply voltage.

Figure 4-9 shows two types of filter circuits. In low-cost applications, where stability and reaction time of the PLL are not critical, the three component filter network shown in Figure 4-9 (B) can be replaced by a single capacitor, C<sub>F</sub>, as shown in shown in Figure 4-9 (A). Refer to Table 4-5 for recommended filter components at various reference frequencies. For reference frequencies between the values listed in the table, extrapolate to the nearest common capacitor value. In general, a slightly larger capacitor provides more stability at the expense of increased lock time.

Figure 4-9. PLL Filter

**Table 4-5. Example Filter Component Values**

| f <sub>RCLK</sub> | C <sub>F1</sub> | C <sub>F2</sub> | R <sub>F1</sub> | C <sub>F</sub> |

|-------------------|-----------------|-----------------|-----------------|----------------|

| 1 MHz             | 8.2 nF          | 820 pF          | 2k              | 18 nF          |

| 2 MHz             | 4.7 nF          | 470 pF          | 2k              | 6.8 nF         |

| 3 MHz             | 3.3 nF          | 330 pF          | 2k              | 5.6 nF         |

| 4 MHz             | 2.2 nF          | 220 pF          | 2k              | 4.7 nF         |

| 5 MHz             | 1.8 nF          | 180 pF          | 2k              | 3.9 nF         |

| 6 MHz             | 1.5 nF          | 150 pF          | 2k              | 3.3 nF         |

| 7 MHz             | 1.2 nF          | 120 pF          | 2k              | 2.7 nF         |

| 8 MHz             | 1 nF            | 100 pF          | 2k              | 2.2 nF         |

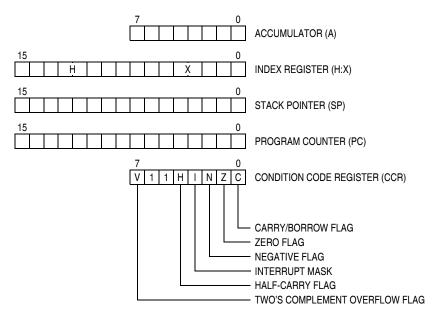

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

#### 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

# 7.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# Chapter 8 External Interrupt (IRQ)

## 8.1 Introduction

The IRQ (external interrupt) module provides a maskable interrupt input.

## 8.2 Features

Features of the IRQ module include:

- A dedicated external interrupt pin (IRQ)

- IRQ interrupt control bits

- Hysteresis buffer

- Programmable edge-only or edge and level interrupt sensitivity

- Automatic interrupt acknowledge

- Internal pullup resistor

# 8.3 Functional Description

A low applied to the external interrupt pin can latch a central processor unit (CPU) interrupt request. Figure 8-1 shows the structure of the IRQ module.

Interrupt signals on the  $\overline{IRQ}$  pin are latched into the IRQ latch. An interrupt latch remains set until one of the following actions occurs:

- Vector fetch A vector fetch automatically generates an interrupt acknowledge signal that clears the latch that caused the vector fetch.

- Software clear Software can clear an interrupt latch by writing to the appropriate acknowledge

bit in the interrupt status and control register (INTSCR). Writing a 1 to the ACK bit clears the IRQ

latch.

- Reset A reset automatically clears the interrupt latch.

The external interrupt pin is falling-edge triggered out of reset and is software-configurable to be either falling-edge or falling-edge and low-level triggered. The MODE bit in the INTSCR controls the triggering sensitivity of the IRQ pin.

When an interrupt pin is edge-triggered only (MODE = 0), the interrupt remains set until a vector fetch, software clear, or reset occurs.

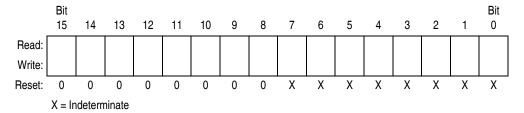

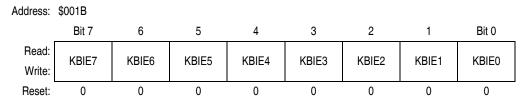

# 9.7.2 Keyboard Interrupt Enable Register

The keyboard interrupt enable register enables or disables each port A pin to operate as a keyboard interrupt pin.

Figure 9-5. Keyboard Interrupt Enable Register (INTKBIER)

## KBIE7-KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch interrupt requests. Reset clears the keyboard interrupt enable register.

- 1 = PTAx pin enabled as keyboard interrupt pin

- 0 = PTAx pin not enabled as keyboard interrupt pin

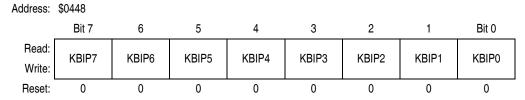

# 9.7.3 Keyboard Interrupt Polarity Register

The KBIP7–KBIP0 bits determine the polarity of the keyboard pin detection. These bits along with the MODEK bit determine whether a logic level (0 or 1) and/or a falling (or rising) edge is being detected. The KBIPx bits also select the pullup resistor (KBIPx = 0) or pulldown resistor (KBIPx = 1) for each enabled keyboard interrupt pin.

Figure 9-6. Keyboard Interrupt Polarity Register (INTKBIPR)

#### KBIP7-KBIP0 — Keyboard Interrupt Polarity Bits

Each of these read/write bits enables the polarity of the keyboard interrupt pin. Reset clears the keyboard interrupt polarity register.

- 1 = Keyboard polarity is rising edge and/or high level

- 0 = Keyboard polarity is falling edge and/or low level

# Input/Output (I/O) Ports

# **Table 13-1. Port Control Register Bits Summary (Continued)**

| Port | Bit | DDR   | Мс      | odule Control  | Mod                | dule Control | Pin          |

|------|-----|-------|---------|----------------|--------------------|--------------|--------------|

|      | 0   | DDRD0 |         |                |                    |              | PTD0/SS/MCLK |

|      | 1   | DDRD1 | ODI     | ODE            |                    |              | PTD1/MISO    |

|      | 2   | DDRD2 | SPI     | SPE            |                    |              | PTD2/MOSI    |

| _    | 3   | DDRD3 |         |                |                    |              | PTD3/SPSCK   |

| D    | 4   | DDRD4 | TIMA    | ELS0B:ELS0A    | 1 –                | _            | PTD4/T1CH0   |

|      | 5   | DDRD5 | TIM1    | ELS1B:ELS1A    |                    |              | PTD5/T1CH1   |

|      | 6   | DDRD6 | TIM2    | ELS0B:ELS0A    | ELS0B:ELS0A PTD6/T |              | PTD6/T2CH0   |

|      | 7   | DDRD7 | I IIVIZ | ELS1B:ELS1A    |                    |              | PTD7/T2CH1   |

|      | 0   | DDRE0 | 001     | ENCOL          |                    |              | PTE0/TxD     |

|      | 1   | DDRE1 | SCI     | ENSCI          |                    |              | PTE1/RxD     |

| E    | 2   | DDRE2 |         |                |                    |              | PTE2         |

|      | 3   | DDRE3 |         |                | _                  |              | PTE3         |

|      | 4   | DDRE4 |         |                |                    |              | PTE4         |

|      | 5   | DDRE5 |         |                |                    |              | PTE5         |

|      | 0   | DDRF0 |         |                |                    |              | PTF0         |

|      | 1   | DDRF1 |         |                |                    |              | PTF1         |

|      | 2   | DDRF2 |         |                |                    |              | PTF2         |

| F    | 3   | DDRF3 |         |                |                    |              | PTF3         |

|      | 4   | DDRF4 |         | ELS2B:ELS2A    |                    | _            | PTF4/T2CH2   |

|      | 5   | DDRF5 | TIM2    | ELS3B:ELS3A    |                    |              | PTF5/T2CH3   |

|      | 6   | DDRF6 | I IIVIZ | ELS4B:ELS4A    |                    |              | PTF6/T2CH4   |

|      | 7   | DDRF7 |         | ELS5B:ELS5A    |                    |              | PTF7/T2CH5   |

|      | 0   | DDRG0 |         |                |                    |              | PTG0/AD16    |

|      | 1   | DDRG1 |         |                |                    |              | PTG1/AD17    |

|      | 2   | DDRG2 | - ADC   |                |                    |              | PTG2/AD18    |

| G    | 3   | DDRG3 |         | ADCH[23:16]    |                    |              | PTG3/AD19    |

|      | 4   | DDRG4 |         | ADOI 1[23, 10] | _                  | _            | PTG4/AD20    |

|      | 5   | DDRG5 |         |                |                    |              | PTG5/AD21    |

|      | 6   | DDRG6 |         |                |                    |              | PTG6/AD22    |

|      | 7   | DDRG7 |         |                |                    |              | PTG7/AD23    |

Input/Output (I/O) Ports

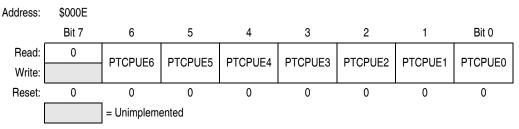

# 13.5.3 Port C Input Pullup Enable Register

The port C input pullup enable register (PTCPUE) contains a software configurable pullup device for each of the seven port C pins. Each bit is individually configurable and requires that the data direction register, DDRC, bit be configured as an input. Each pullup is automatically and dynamically disabled when a port bit's DDRC is configured for output mode.

Figure 13-12. Port C Input Pullup Enable Register (PTCPUE)

## PTCPUE6-PTCPUE0 — Port C Input Pullup Enable Bits

These writable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port C pin configured to have internal pullup

- 0 = Corresponding port C pin internal pullup disconnected

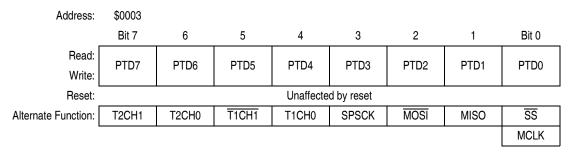

# 13.6 Port D

Port D is an 8-bit special-function port that shares four of its pins with the serial peripheral interface (SPI) module and four of its pins with two timer interface (TIM1 and TIM2) modules. Port D also has software configurable pullup devices if configured as an input port. PTD0 is shared with the MCLK output.

# 13.6.1 Port D Data Register

The port D data register (PTD) contains a data latch for each of the eight port D pins.

Figure 13-13. Port D Data Register (PTD)

### PTD7-PTD0 — Port D Data Bits

These read/write bits are software-programmable. Data direction of each port D pin is under the control of the corresponding bit in data direction register D. Reset has no effect on port D data.

#### T2CH1 and T2CH0 — Timer 2 Channel I/O Bits

The PTD5/T2CH1-PTD4/T2CH0 pins are the TIM2 input capture/output compare pins. The edge/level select bits, ELSxB:ELSxA, determine whether the PTD7/T2CH1-PTD6/T2CH0 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 18 Timer Interface Module (TIM1) and Chapter 19 Timer Interface Module (TIM2).

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

## 13.8 Port F

Port F is an 8-bit special-function port that shares four of its pins with the timer interface (TIM2) module.

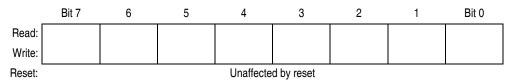

# 13.8.1 Port F Data Register

The port F data register (PTF) contains a data latch for each of the eight port F pins.

Figure 13-20. Port F Data Register (PTF)

#### PTF7-PTF0 — Port F Data Bits

These read/write bits are software-programmable. Data direction of each port F pin is under the control of the corresponding bit in data direction register F. Reset has no effect on port F data.

#### T2CH5-T2CH2 — Timer 2 Channel I/O Bits

The PTF7/T2CH5–PTF4/T2CH2 pins are the TIM2 input capture/output compare pins. The edge/level select bits, ELSxB:ELSxA, determine whether the PTF7/T2CH5–PTF4/T2CH2 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 18 Timer Interface Module (TIM1) and Chapter 19 Timer Interface Module (TIM2).

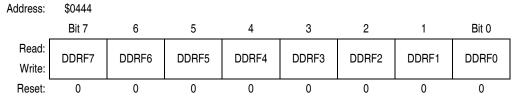

# 13.8.2 Data Direction Register F

Data direction register F (DDRF) determines whether each port F pin is an input or an output. Writing a 1 to a DDRF bit enables the output buffer for the corresponding port F pin; a 0 disables the output buffer.

Figure 13-21. Data Direction Register F (DDRF)

## DDRF7-DDRF0 — Data Direction Register F Bits

These read/write bits control port F data direction. Reset clears DDRF7–DDRF0, configuring all port F pins as inputs.

- 1 = Corresponding port F pin configured as output

- 0 = Corresponding port F pin configured as input

#### NOTE

Avoid glitches on port F pins by writing to the port F data register before changing data direction register F bits from 0 to 1.

Figure 13-22 shows the port F I/O logic.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### **System Integration Module (SIM)**

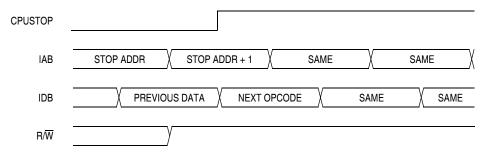

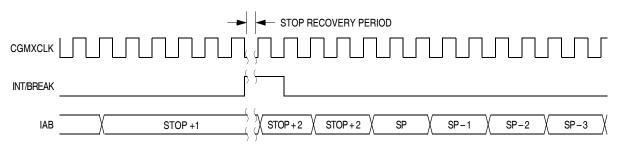

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 15-19 shows stop mode entry timing. Figure 15-20 shows stop mode recovery time from interrupt.

#### NOTE

To minimize stop current, all pins configured as inputs should be driven to a 1 or 0.

Note: Previous data can be operand data or the STOP opcode, depending on the last instruction.

Figure 15-19. Stop Mode Entry Timing

Figure 15-20. Stop Mode Recovery from Interrupt

# 15.7 SIM Registers

The SIM has three memory-mapped registers. Table 15-4 shows the mapping of these registers.

**Table 15-4. SIM Registers**

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

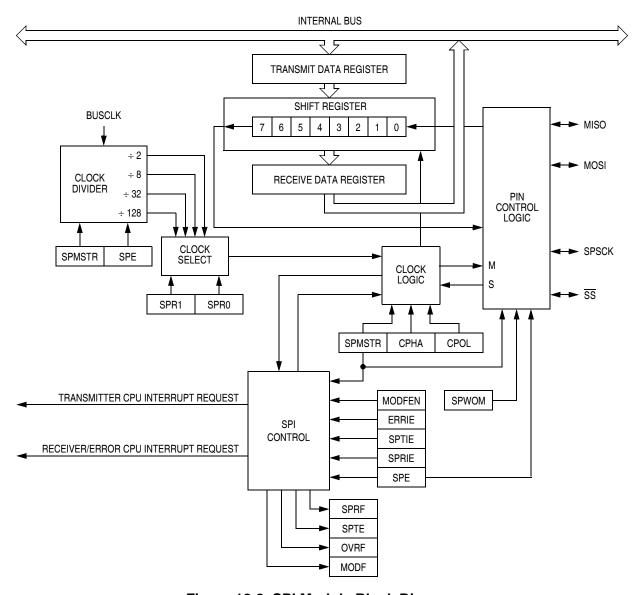

Figure 16-2. SPI Module Block Diagram

| Addr.  | Register Name               |                 | Bit 7 | 6          | 5      | 4         | 3          | 2        | 1      | Bit 0  |

|--------|-----------------------------|-----------------|-------|------------|--------|-----------|------------|----------|--------|--------|

| \$0010 | SPI Control Register (SPCR) | Read:<br>Write: | SPRIE | R          | SPMSTR | CPOL      | СРНА       | SPWOM    | SPE    | SPTIE  |

|        | See page 255.               | Reset:          | 0     | 0          | 1      | 0         | 1          | 0        | 0      | 0      |

|        | SPI Status and Control      | Read:           | SPRF  | ERRIE      | OVRF   | MODF      | SPTE       | MODFEN   | SPR1   | SPR0   |

| \$0011 | Register (SPSCR)            | Write:          |       | ENNIE      |        |           |            | WODI LIV | 31 111 | 31 110 |

|        | See page 256.               | Reset:          | 0     | 0          | 0      | 0         | 1          | 0        | 0      | 0      |

|        | SPI Data Register           | Read:           | R7    | R6         | R5     | R4        | R3         | R2       | R1     | R0     |

| \$0012 | (SPDR)                      | Write:          | T7    | T6         | T5     | T4        | T3         | T2       | T1     | T0     |

|        | See page 258. Res           |                 |       |            |        | Unaffecte | d by reset |          |        |        |

|        |                             |                 | R     | = Reserved |        |           | = Unimplem | ented    |        |        |

Figure 16-3. SPI I/O Register Summary

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# Chapter 17 Timebase Module (TBM)

## 17.1 Introduction

This section describes the timebase module (TBM). The TBM will generate periodic interrupts at user selectable rates using a counter clocked by the external clock source. This TBM version uses 15 divider stages, eight of which are user selectable. A configuration option bit to select an additional 128 divide of the external clock source can be selected. See Chapter 5 Configuration Register (CONFIG)

## 17.2 Features

Features of the TBM module include:

- External clock or an additional divide-by-128 selected by configuration option bit as clock source

- Software configurable periodic interrupts with divide-by: 8, 16, 32, 64, 128, 2048, 8192, and 32768 taps of the selected clock source

- Configurable for operation during stop mode to allow periodic wakeup from stop

# 17.3 Functional Description

This module can generate a periodic interrupt by dividing the clock source supplied from the clock generator module, CGMXCLK.

The counter is initialized to all 0s when TBON bit is cleared. The counter, shown in Figure 17-1, starts counting when the TBON bit is set. When the counter overflows at the tap selected by TBR2–TBR0, the TBIF bit gets set. If the TBIE bit is set, an interrupt request is sent to the CPU. The TBIF flag is cleared by writing a 1 to the TACK bit. The first time the TBIF flag is set after enabling the timebase module, the interrupt is generated at approximately half of the overflow period. Subsequent events occur at the exact period.

The timebase module may remain active after execution of the STOP instruction if the crystal oscillator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

# 17.4 Interrupts

The timebase module can periodically interrupt the CPU with a rate defined by the selected TBMCLK and the select bits TBR2–TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

#### NOTE

Interrupts must be acknowledged by writing a 1 to the TACK bit.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

|      |      |      | Divider   |           |  |

|------|------|------|-----------|-----------|--|

| TBR2 | TBR1 | TBR0 | TMBCLKSEL |           |  |

| IBNZ | IBNI | IDNO | 0         | 1         |  |

| 0    | 0    | 0    | 32,768    | 4,194,304 |  |

| 0    | 0    | 1    | 8192      | 1,048,576 |  |

| 0    | 1    | 0    | 2048      | 262144    |  |

| 0    | 1    | 1    | 128       | 16,384    |  |

| 1    | 0    | 0    | 64        | 8192      |  |

| 1    | 0    | 1    | 32        | 4096      |  |

| 1    | 1    | 0    | 16        | 2048      |  |

| 1    | 1    | 1    | 8         | 1024      |  |

Table 17-1. Timebase Divider Selection

As an example, a 4.9152 MHz crystal, with the TMBCLKSEL set for divide-by-128 and the TBR2–TBR0 set to {011}, the divider is 16,384 and the interrupt rate calculates to:

$$\frac{16,384}{4.9152 \times 10^6} = 3.33 \text{ ms}$$

#### NOTE

Do not change TBR2-TBR0 bits while the timebase is enabled (TBON = 1).

## 17.6 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power- consumption standby modes.

#### 17.6.1 Wait Mode

The timebase module remains active after execution of the WAIT instruction. In wait mode the timebase register is not accessible by the CPU.

If the timebase functions are not required during wait mode, reduce the power consumption by stopping the timebase before executing the WAIT instruction.

## 17.6.2 **Stop Mode**

The timebase module may remain active after execution of the STOP instruction if the oscillator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

If the oscillator has not been enabled to operate in stop mode, the timebase module will not be active during stop mode. In stop mode, the timebase register is not accessible by the CPU.

If the timebase functions are not required during stop mode, reduce power consumption by disabling the timebase module before executing the STOP instruction.

## 18.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the T1CH0 pin. The TIM1 channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM1 channel 0 status and control register (T1SC0) links channel 0 and channel 1. The TIM1 channel 0 registers initially control the pulse width on the T1CH0 pin. Writing to the TIM1 channel 1 registers enables the TIM1 channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM1 channel registers (0 or 1) that control the pulse width are the ones written to last. T1SC0 controls and monitors the buffered PWM function, and TIM1 channel 1 status and control register (T1SC1) is unused. While the MS0B bit is set, the channel 1 pin, T1CH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

#### 18.3.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use the following initialization procedure:

- 1. In the TIM1 status and control register (T1SC):

- a. Stop the TIM1 counter by setting the TIM1 stop bit, TSTOP.

- b. Reset the TIM1 counter and prescaler by setting the TIM1 reset bit, TRST.

- 2. In the TIM1 counter modulo registers (T1MODH:T1MODL), write the value for the required PWM period.

- 3. In the TIM1 channel x registers (T1CHxH:T1CHxL), write the value for the required pulse width.

- 4. In TIM1 channel x status and control register (T1SCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. See Table 18-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (polarity 1 to clear output on compare) or 1:1 (polarity 0 to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 18-2.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM1 status control register (T1SC), clear the TIM1 stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM1 channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM1 status control

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

**Timer Interface Module (TIM1)**

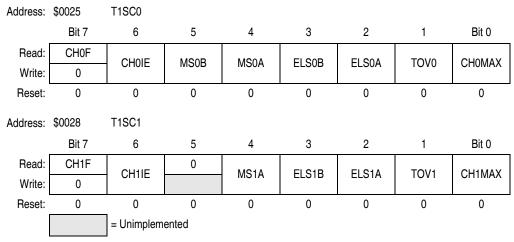

# 18.8.4 TIM1 Channel Status and Control Registers

Each of the TIM1 channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM1 overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 18-8. TIM1 Channel Status and Control Registers (T1SC0:T1SC1)

### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM1 counter registers matches the value in the TIM1 channel x registers.

Clear CHxF by reading the TIM1 channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

# CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM1 CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

#### **Timer Interface Module (TIM2)**

Writing to the TIM2 channel 5 registers enables the TIM2 channel 5 registers to synchronously control the output after the TIM2 overflows. At each subsequent overflow, the TIM2 channel registers (4 or 5) that control the output are the ones written to last. T2SC4 controls and monitors the buffered output compare function, and TIM2 channel 5 status and control register (T2SC5) is unused. While the MS4B bit is set, the channel 5 pin, T2CH5, is available as a general-purpose I/O pin.

#### NOTE

In buffered output compare operation, do not write new output compare values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered output compares.

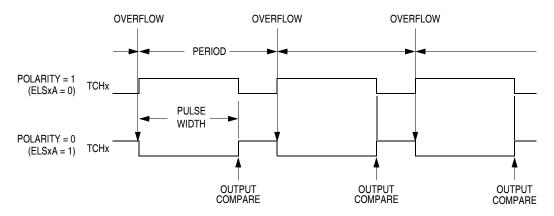

# 19.3.4 Pulse Width Modulation (PWM)

By using the toggle-on-overflow feature with an output compare channel, the TIM2 can generate a PWM signal. The value in the TIM2 counter modulo registers determines the period of the PWM signal. The channel pin toggles when the counter reaches the value in the TIM2 counter modulo registers. The time between overflows is the period of the PWM signal.

As Figure 19-4 shows, the output compare value in the TIM2 channel registers determines the pulse width of the PWM signal. The time between overflow and output compare is the pulse width. Program the TIM2 to clear the channel pin on output compare if the polarity of the PWM pulse is 1 (ELSxA = 0). Program the TIM2 to set the pin if the polarity of the PWM pulse is 0 (ELSxA = 1).

Figure 19-4. PWM Period and Pulse Width

The value in the TIM2 counter modulo registers and the selected prescaler output determines the frequency of the PWM output. The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIM2 counter modulo registers produces a PWM period of 256 times the internal bus clock period if the prescaler select value is 000 (see 19.8.1 TIM2 Status and Control Register).

The value in the TIM2 channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM2 channel registers produces a duty cycle of 128/256 or 50%.

## **Electrical Specifications**

# 21.3 Functional Operating Range

| Characteristic              | Symbol          | Value                | Unit |

|-----------------------------|-----------------|----------------------|------|

| Operating temperature range | T <sub>A</sub>  | -40 to +125          | °C   |

| Operating voltage range     | V <sub>DD</sub> | 5.0 ±10%<br>3.3 ±10% | V    |

# 21.4 Thermal Characteristics

| Characteristic                                        | Symbol            | Value                                                                    | Unit |

|-------------------------------------------------------|-------------------|--------------------------------------------------------------------------|------|

| Thermal resistance 32-pin LQFP 48-pin LQFP 64-pin QFP | $\theta_{\sf JA}$ | 95<br>95<br>54                                                           | °C/W |

| I/O pin power dissipation                             | P <sub>I/O</sub>  | User determined                                                          | W    |

| Power dissipation <sup>(1)</sup>                      | P <sub>D</sub>    | $P_D = (I_{DD} \times V_{DD}) + P_{I/O} = K/(T_J + 273 ^{\circ}C)$       | W    |

| Constant <sup>(2)</sup>                               | К                 | $P_{D} \times (T_{A} + 273 \text{ °C})$ $+ P_{D}^{2} \times \theta_{JA}$ | W/°C |

| Average junction temperature                          | T <sub>J</sub>    | $T_A + (P_D \times \theta_{JA})$                                         | °C   |

<sup>1.</sup> Power dissipation is a function of temperature.

<sup>2.</sup> K is a constant unique to the device. K can be determined for a known  $T_A$  and measured  $P_D$ . With this value of K,  $P_D$  and  $T_J$  can be determined for any value of  $T_A$ .