Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                   |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | CANbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 37                                                         |

| Program Memory Size        | 48KB (48K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1.5К х 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | A/D 24x10b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908gz48cfae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 21.9   | Clock Generation Module (CGM) Characteristics | 322 |

|--------|-----------------------------------------------|-----|

| 21.9.1 | CGM Operating Conditions                      | 322 |

| 21.9.2 | CGM Component Information                     | 322 |

| 21.9.3 | CGM Acquisition/Lock Time Information         | 323 |

| 21.10  | 5.0-Volt ADC Characteristics                  | 324 |

| 21.11  | 3.3-Volt ADC Characteristics                  | 325 |

| 21.12  | 5.0-Volt SPI Characteristics                  | 326 |

| 21.13  | 3.3-Volt SPI Characteristics                  | 327 |

| 21.14  | Timer Interface Module Characteristics        | 330 |

| 21.15  | Memory Characteristics                        | 331 |

# Chapter 22 Ordering Information and Mechanical Specifications

| 22.1 | Introduction       | 333 |

|------|--------------------|-----|

| 22.2 | MC Order Numbers   | 333 |

| 22.3 | Package Dimensions | 333 |

## Appendix A MC68HC908GZ48

| A.1 | Introduction         | 343 |

|-----|----------------------|-----|

| A.2 | Block Diagram        | 343 |

| A.3 | Memory               | 343 |

| A.4 | Ordering Information | 346 |

## Appendix B MC68HC908GZ32

| B.1 | Introduction         | 347 |

|-----|----------------------|-----|

| B.2 | Block Diagram        | 347 |

| B.3 | Memory               | 347 |

| B.4 | Ordering Information | 350 |

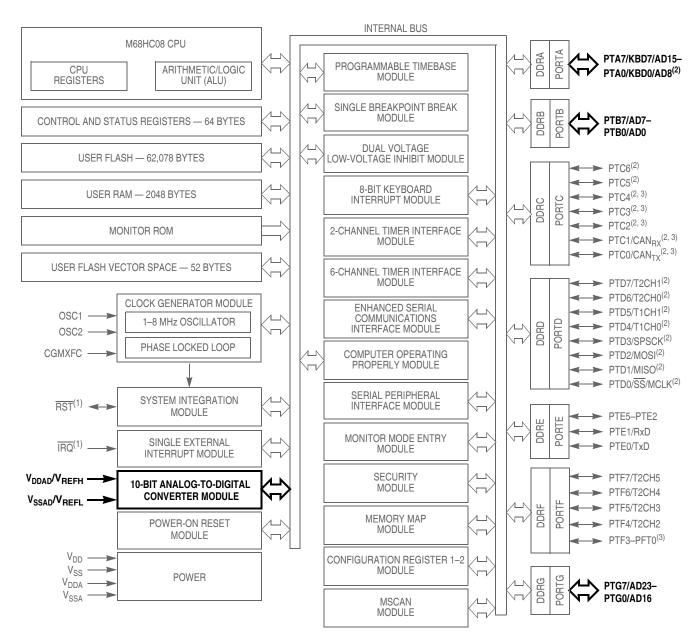

**General Description**

#### Analog-to-Digital Converter (ADC)

1. Pin contains integrated pullup device.

2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

3. Higher current drive port pins

#### Figure 3-1. Block Diagram Highlighting ADC Block and Pins

## 4.4 I/O Signals

The following paragraphs describe the CGM I/O signals.

#### 4.4.1 Crystal Amplifier Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier.

### 4.4.2 Crystal Amplifier Output Pin (OSC2)

The OSC2 pin is the output of the crystal oscillator inverting amplifier.

#### 4.4.3 External Filter Capacitor Pin (CGMXFC)

The CGMXFC pin is required by the loop filter to filter out phase corrections. An external filter network is connected to this pin. (See Figure 4-2.)

#### NOTE

To prevent noise problems, the filter network should be placed as close to the CGMXFC pin as possible, with minimum routing distances and no routing of other signals across the network.

### 4.4.4 PLL Analog Power Pin (V<sub>DDA</sub>)

$V_{DDA}$  is a power pin used by the analog portions of the PLL. Connect the  $V_{DDA}$  pin to the same voltage potential as the  $V_{DD}$  pin.

#### NOTE

Route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 4.4.5 PLL Analog Ground Pin (V<sub>SSA</sub>)

$V_{SSA}$  is a ground pin used by the analog portions of the PLL. Connect the  $V_{SSA}$  pin to the same voltage potential as the  $V_{SS}$  pin.

#### NOTE

Route  $V_{SSA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

#### 4.4.6 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables the oscillator and PLL.

## 4.4.7 Oscillator Enable in Stop Mode Bit (OSCENINSTOP)

OSCENINSTOP is a bit in the CONFIG2 register that enables the oscillator to continue operating during stop mode. If this bit is set, the oscillator continues running during stop mode. If this bit is not set (default), the oscillator is controlled by the SIMOSCEN signal which will disable the oscillator during stop mode.

## 4.8 Acquisition/Lock Time Specifications

The acquisition and lock times of the PLL are, in many applications, the most critical PLL design parameters. Proper design and use of the PLL ensures the highest stability and lowest acquisition/lock times.

### 4.8.1 Acquisition/Lock Time Definitions

Typical control systems refer to the acquisition time or lock time as the reaction time, within specified tolerances, of the system to a step input. In a PLL, the step input occurs when the PLL is turned on or when it suffers a noise hit. The tolerance is usually specified as a percent of the step input or when the output settles to the desired value plus or minus a percent of the frequency change. Therefore, the reaction time is constant in this definition, regardless of the size of the step input. For example, consider a system with a 5 percent acquisition time tolerance. If a command instructs the system to change from 0 Hz to 1 MHz, the acquisition time is the time taken for the frequency to reach 1 MHz  $\pm$ 50 kHz. Fifty kHz = 5% of the 1-MHz step input. If the system is operating at 1 MHz and suffers a -100-kHz noise hit, the acquisition time taken to return from 900 kHz to 1 MHz  $\pm$ 5 kHz. Five kHz = 5% of the 100-kHz step input.

Other systems refer to acquisition and lock times as the time the system takes to reduce the error between the actual output and the desired output to within specified tolerances. Therefore, the acquisition or lock time varies according to the original error in the output. Minor errors may not even be registered. Typical PLL applications prefer to use this definition because the system requires the output frequency to be within a certain tolerance of the desired frequency regardless of the size of the initial error.

#### 4.8.2 Parametric Influences on Reaction Time

Acquisition and lock times are designed to be as short as possible while still providing the highest possible stability. These reaction times are not constant, however. Many factors directly and indirectly affect the acquisition time.

The most critical parameter which affects the reaction times of the PLL is the reference frequency,  $f_{RCLK}$ . This frequency is the input to the phase detector and controls how often the PLL makes corrections. For stability, the corrections must be small compared to the desired frequency, so several corrections are required to reduce the frequency error. Therefore, the slower the reference the longer it takes to make these corrections. This parameter is under user control via the choice of crystal frequency f<sub>XCLK</sub>. (See 4.3.3 PLL Circuits and 4.3.6 Programming the PLL.)

Another critical parameter is the external filter network. The PLL modifies the voltage on the VCO by adding or subtracting charge from capacitors in this network. Therefore, the rate at which the voltage changes for a given frequency error (thus change in charge) is proportional to the capacitance. The size of the capacitor also is related to the stability of the PLL. If the capacitor is too small, the PLL cannot make small enough adjustments to the voltage and the system cannot lock. If the capacitor is too large, the PLL may not be able to adjust the voltage in a reasonable time. (See 4.8.3 Choosing a Filter.)

Also important is the operating voltage potential applied to  $V_{DDA}$ . The power supply potential alters the characteristics of the PLL. A fixed value is best. Variable supplies, such as batteries, are acceptable if they vary within a known range at very slow speeds. Noise on the power supply is not acceptable, because it causes small frequency errors which continually change the acquisition time of the PLL.

Temperature and processing also can affect acquisition time because the electrical characteristics of the PLL change. The part operates as specified as long as these influences stay within the specified limits.

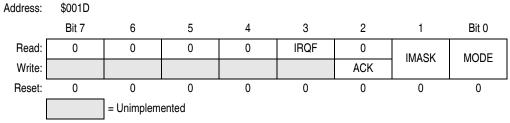

External Interrupt (IRQ)

## 8.6 IRQ Status and Control Register

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. The INTSCR:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

#### Figure 8-3. IRQ Status and Control Register (INTSCR)

#### IRQF — IRQ Flag Bit

This read-only status bit is high when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

#### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0. Reset clears ACK.

#### IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

- 1 = IRQ interrupt requests disabled

- 0 = IRQ interrupt requests enabled

#### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin. Reset clears MODE.

- 1 = IRQ interrupt requests on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt requests on falling edges only

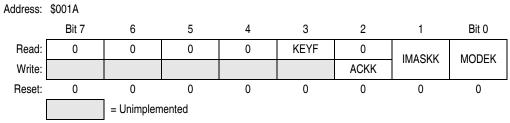

#### Keyboard Interrupt Module (KBI)

## 9.7.1 Keyboard Status and Control Register

The keyboard status and control register:

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- · Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

#### Figure 9-4. Keyboard Status and Control Register (INTKBSCR)

#### Bits 7-4 — Not used

These read-only bits always read as 0s.

#### **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending. Reset clears the KEYF bit.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

#### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request. ACKK always reads as 0. Reset clears ACKK.

#### **IMASKK** — Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests. Reset clears the IMASKK bit.

1 = Keyboard interrupt requests masked

0 = Keyboard interrupt requests not masked

#### MODEK — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins. Reset clears MODEK.

1 = Keyboard interrupt requests on edge and level detect

0 = Keyboard interrupt requests on edges only

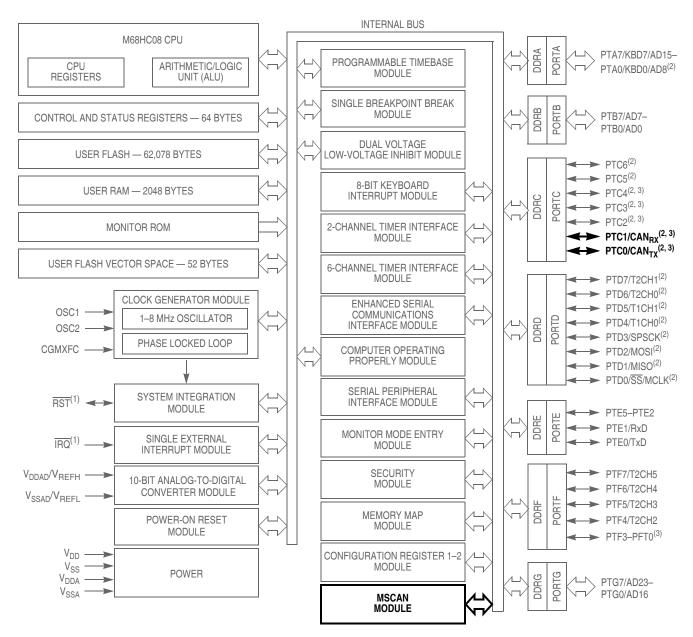

#### **MSCAN08 Controller (MSCAN08)**

1. Pin contains integrated pullup device.

2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

3. Higher current drive port pins

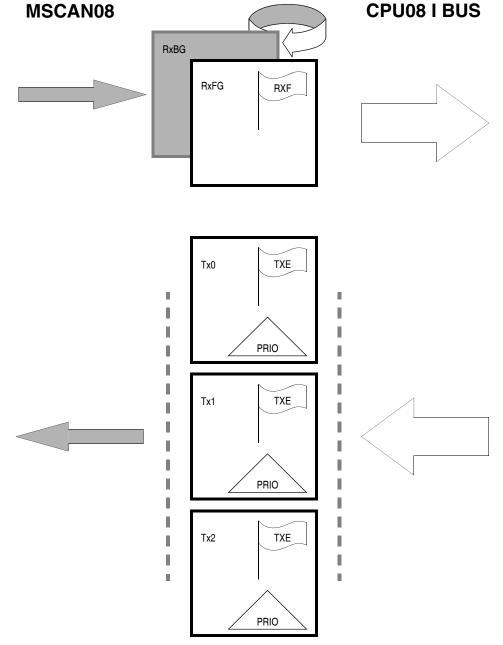

Figure 12-3. User Model for Message Buffer Organization

#### 12.4.3 Transmit Structures

The MSCAN08 has a triple transmit buffer scheme to allow multiple messages to be set up in advance and to achieve an optimized real-time performance. The three buffers are arranged as shown in Figure 12-3.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see 12.12 Programmer's Model of Message Storage). An additional transmit buffer priority register (TBPR) contains an 8-bit "local priority" field (PRIO) (see 12.12.5 Transmit Buffer Priority Registers).

#### MSCAN08 Controller (MSCAN08)

| MSCAN08 Mode | CPU Mode                               |                         |  |

|--------------|----------------------------------------|-------------------------|--|

|              | STOP                                   | WAIT or RUN             |  |

| Power Down   | SLPAK = X <sup>(1)</sup><br>SFTRES = X |                         |  |

| Sleep        |                                        | SLPAK = 1<br>SFTRES = 0 |  |

| Soft Reset   |                                        | SLPAK = 0<br>SFTRES = 1 |  |

| Normal       |                                        | SLPAK = 0<br>SFTRES = 0 |  |

#### Table 12-2. MSCAN08 versus CPU Operating Modes

1. 'X' means don't care.

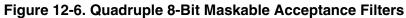

#### 12.8.1 MSCAN08 Sleep Mode

The CPU can request the MSCAN08 to enter the low-power mode by asserting the SLPRQ bit in the module configuration register (see Figure 12-7). The time when the MSCAN08 enters sleep mode depends on its activity:

- If it is transmitting, it continues to transmit until there is no more message to be transmitted, and then goes into sleep mode

- If it is receiving, it waits for the end of this message and then goes into sleep mode

- If it is neither transmitting or receiving, it will immediately go into sleep mode

#### NOTE

The application software must avoid setting up a transmission (by clearing or more TXE flags) and immediately request sleep mode (by setting SLPRQ). It then depends on the exact sequence of operations whether MSCAN08 starts transmitting or goes into sleep mode directly.

#### **TERRIF** — Transmitter Error Passive Interrupt Flag

This flag is set when the MSCAN08 goes into error passive status due to the transmit error counter exceeding 127 and the bus-off interrupt flag is not set<sup>(1)</sup>. If not masked, an error interrupt is pending while this flag is set.

1 = MSCAN08 went into transmit error passive status.

0 = No transmit error passive status has been reached.

#### BOFFIF — Bus-Off Interrupt Flag

This flag is set when the MSCAN08 goes into bus-off status, due to the transmit error counter exceeding 255. It cannot be cleared before the MSCAN08 has monitored 128 times 11 consecutive 'recessive' bits on the bus. If not masked, an error interrupt is pending while this flag is set.

1 = MSCAN08has gone into bus-off status.

0 = No bus-off status has been reached.

#### **OVRIF** — Overrun Interrupt Flag

This flag is set when a data overrun condition occurs. If not masked, an error interrupt is pending while this flag is set.

1 = A data overrun has been detected since last clearing the flag.

0 = No data overrun has occurred.

#### RXF — Receive Buffer Full

The RXF flag is set by the MSCAN08 when a new message is available in the foreground receive buffer. This flag indicates whether the buffer is loaded with a correctly received message. After the CPU has read that message from the receive buffer the RXF flag must be cleared to release the buffer. A set RXF flag prohibits the exchange of the background receive buffer into the foreground buffer. If not masked, a receive interrupt is pending while this flag is set.

1 = The receive buffer is full. A new message is available.

0 = The receive buffer is released (not full).

#### NOTE

To ensure data integrity, no registers of the receive buffer shall be read while the RXF flag is cleared. The CRFLG register is held in the reset state when the SFTRES bit in CMCR0 is set.

<sup>1.</sup> Condition to set the flag: TERRIF = (128  $\rightarrow$  TEC  $\rightarrow$  255) & BOFFIF

## 13.8 Port F

Port F is an 8-bit special-function port that shares four of its pins with the timer interface (TIM2) module.

## 13.8.1 Port F Data Register

The port F data register (PTF) contains a data latch for each of the eight port F pins.

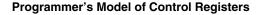

Figure 13-20. Port F Data Register (PTF)

#### PTF7-PTF0 — Port F Data Bits

These read/write bits are software-programmable. Data direction of each port F pin is under the control of the corresponding bit in data direction register F. Reset has no effect on port F data.

#### T2CH5–T2CH2 — Timer 2 Channel I/O Bits

The PTF7/T2CH5–PTF4/T2CH2 pins are the TIM2 input capture/output compare pins. The edge/level select bits, ELSxB:ELSxA, determine whether the PTF7/T2CH5–PTF4/T2CH2 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 18 Timer Interface Module (TIM1) and Chapter 19 Timer Interface Module (TIM2).

#### 13.8.2 Data Direction Register F

Data direction register F (DDRF) determines whether each port F pin is an input or an output. Writing a 1 to a DDRF bit enables the output buffer for the corresponding port F pin; a 0 disables the output buffer.

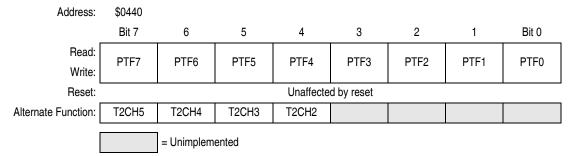

Figure 13-21. Data Direction Register F (DDRF)

#### DDRF7–DDRF0 — Data Direction Register F Bits

These read/write bits control port F data direction. Reset clears DDRF7–DDRF0, configuring all port F pins as inputs.

1 = Corresponding port F pin configured as output

0 = Corresponding port F pin configured as input

#### NOTE

Avoid glitches on port F pins by writing to the port F data register before changing data direction register F bits from 0 to 1.

Figure 13-22 shows the port F I/O logic.

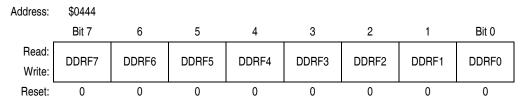

#### Enhanced Serial Communications Interface (ESCI) Module

SL = 1 -> SCI\_CLK = BUSCLK SL = 0 -> SCI\_CLK = CGMXCLK

Figure 14-3. ESCI Module Block Diagram

#### Enhanced Serial Communications Interface (ESCI) Module

#### IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive 1s appear on the receiver input. IDLE generates an ESCI receiver CPU interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

1 = Receiver input idle

0 = Receiver input active (or idle since the IDLE bit was cleared)

#### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

1 = Receive shift register full and SCRF = 1

0 = No receiver overrun

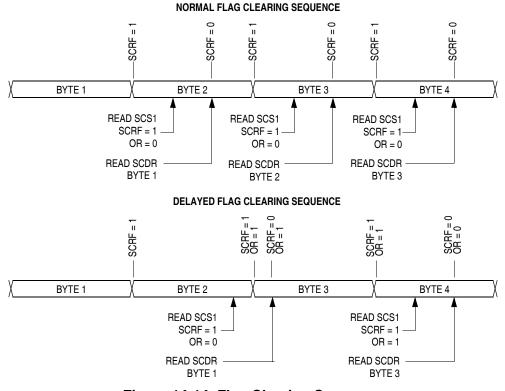

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 14-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

Figure 14-14. Flag Clearing Sequence

#### Enhanced Serial Communications Interface (ESCI) Module

#### **ARUN**— Arbiter Counter Running Flag

This read-only bit indicates the arbiter counter is running. Reset clears ARUN.

- 1 = Arbiter counter running

- 0 = Arbiter counter stopped

#### **AROVFL**— Arbiter Counter Overflow Bit

This read-only bit indicates an arbiter counter overflow. Clear AROVFL by writing any value to SCIACTL. Writing 0s to AM1 and AM0 resets the counter keeps it in this idle state. Reset clears AROVFL.

1 = Arbiter counter overflow has occurred

0 = No arbiter counter overflow has occurred

#### **ARD8**— Arbiter Counter MSB

This read-only bit is the MSB of the 9-bit arbiter counter. Clear ARD8 by writing any value to SCIACTL. Reset clears ARD8.

#### 14.9.2 ESCI Arbiter Data Register

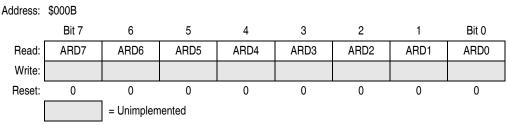

#### Figure 14-20. ESCI Arbiter Data Register (SCIADAT)

#### ARD7–ARD0 — Arbiter Least Significant Counter Bits

These read-only bits are the eight LSBs of the 9-bit arbiter counter. Clear ARD7–ARD0 by writing any value to SCIACTL. Writing 0s to AM1 and AM0 permanently resets the counter and keeps it in this idle state. Reset clears ARD7–ARD0.

#### 14.9.3 Bit Time Measurement

Two bit time measurement modes, described here, are available according to the state of ACLK.

- ACLK = 0 The counter is clocked with the bus clock divided by four. The counter is started when a falling edge on the RxD pin is detected. The counter will be stopped on the next falling edge. ARUN is set while the counter is running, AFIN is set on the second falling edge on RxD (for instance, the counter is stopped). This mode is used to recover the received baud rate. See Figure 14-21.

- ACLK = 1 The counter is clocked with one half of the ESCI input clock generated by the ESCI prescaler. The counter is started when a 0 is detected on RxD (see Figure 14-22). A 0 on RxD on enabling the bit time measurement with ACLK = 1 leads to immediate start of the counter (see Figure 14-23). The counter will be stopped on the next rising edge of RxD. This mode is used to measure the length of a received break.

#### 14.9.4 Arbitration Mode

If AM[1:0] is set to 10, the arbiter module operates in arbitration mode. On every rising edge of SCI\_TxD (output of the ESCI module, internal chip signal), the counter is started. When the counter reaches \$38 (ACLK = 0) or \$08 (ACLK = 1), RxD is statically sensed. If in this case, RxD is sensed low (for example,

#### Serial Peripheral Interface (SPI) Module

1. Pin contains integrated pullup device.

2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

3. Higher current drive port pins

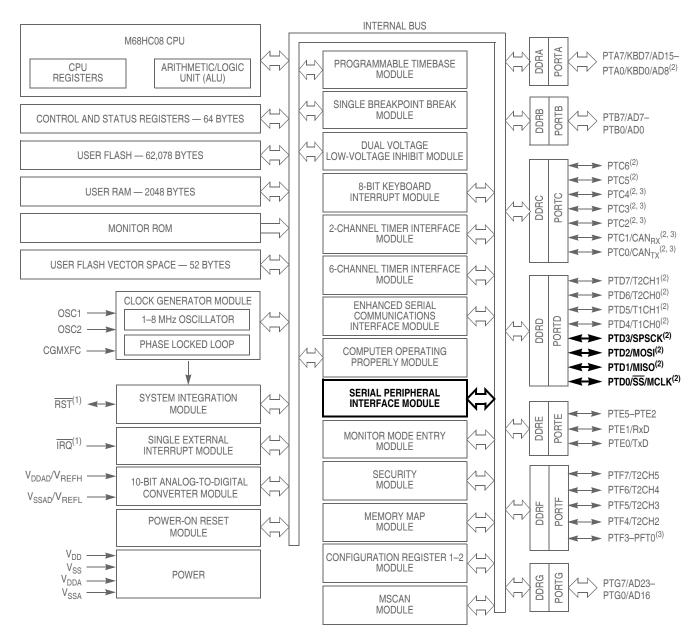

#### Figure 16-1. Block Diagram Highlighting SPI Block and Pins

## 16.5 Queuing Transmission Data

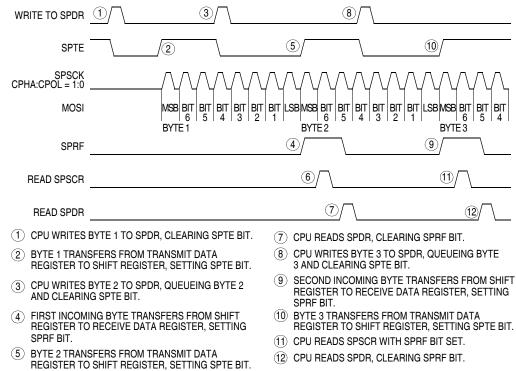

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI configured as a master, a gueued data byte is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready to accept new data. Write to the transmit data register only when SPTE is high. Figure 16-9 shows the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL = 1:0).

- (6) CPU READS SPSCR WITH SPRF BIT SET.

- Figure 16-9. SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes between transmissions as in a system with a single data buffer. Also, if no new data is written to the data buffer, the last value contained in the shift register is the next data word to be transmitted.

For an idle master or idle slave that has no data loaded into its transmit buffer, the SPTE is set again no more than two bus cycles after the transmit buffer empties into the shift register. This allows the user to queue up a 16-bit value to send. For an already active slave, the load of the shift register cannot occur until the transmission is completed. This implies that a back-to-back write to the transmit data register is not possible. SPTE indicates when the next write can occur.

**I/O Registers**

#### SPRF — SPI Receiver Full Bit

This clearable, read-only flag is set each time a byte transfers from the shift register to the receive data register. SPRF generates a CPU interrupt request if the SPRIE bit in the SPI control register is set also.

During an SPRF CPU interrupt, the CPU clears SPRF by reading the SPI status and control register with SPRF set and then reading the SPI data register.

Reset clears the SPRF bit.

1 = Receive data register full

0 = Receive data register not full

#### ERRIE — Error Interrupt Enable Bit

This read/write bit enables the MODF and OVRF bits to generate CPU interrupt requests. Reset clears the ERRIE bit.

- 1 = MODF and OVRF can generate CPU interrupt requests

- 0 = MODF and OVRF cannot generate CPU interrupt requests

#### **OVRF** — Overflow Bit

This clearable, read-only flag is set if software does not read the byte in the receive data register before the next full byte enters the shift register. In an overflow condition, the byte already in the receive data register is unaffected, and the byte that shifted in last is lost. Clear the OVRF bit by reading the SPI status and control register with OVRF set and then reading the receive data register. Reset clears the OVRF bit.

1 = Overflow

0 = No overflow

#### MODF — Mode Fault Bit

This clearable, read-only flag is set in a slave SPI if the  $\overline{SS}$  pin goes high during a transmission with MODFEN set. In a master SPI, the MODF flag is set if the  $\overline{SS}$  pin goes low at any time with the MODFEN bit set. Clear MODF by reading the SPI status and control register (SPSCR) with MODF set and then writing to the SPI control register (SPCR). Reset clears the MODF bit.

$1 = \overline{SS}$  pin at inappropriate logic level

$0 = \overline{SS}$  pin at appropriate logic level

#### SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE CPU interrupt request if SPTIE in the SPI control register is set also.

#### NOTE

Do not write to the SPI data register unless SPTE is high.

During an SPTE CPU interrupt, the CPU clears SPTE by writing to the transmit data register.

Reset sets the SPTE bit.

1 = Transmit data register empty

0 = Transmit data register not empty

#### MODFEN — Mode Fault Enable Bit

This read/write bit, when set, allows the MODF flag to be set. If the MODF flag is set, clearing MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is 0, then the  $\overline{SS}$  pin is available as a general-purpose I/O.

## Appendix A MC68HC908GZ48

## A.1 Introduction

The MC68HC908GZ48 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

The information contained in this document pertains to the MC68HC908GZ48 with the exceptions shown in this appendix.

## A.2 Block Diagram

See Figure A-1.

## A.3 Memory

The MC68HC908GZ48 can address 48 Kbytes of memory space. The memory map, shown in Figure A-2, includes:

- 48 Kbytes of user FLASH memory

- 1536 bytes of random-access memory (RAM)

- 52 bytes of user-defined vectors