Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                   |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, SCI, SPI                                                      |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 53                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 24x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-QFP                                                                |

| Supplier Device Package    | 64-QFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gz48cfue |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12.7             | Protocol Violation Protection              | . 144 |

|------------------|--------------------------------------------|-------|

| 12.8             | Low-Power Modes                            | . 144 |

| 12.8.1           | MSCAN08 Sleep Mode                         | . 145 |

| 12.8.2           | MSCAN08 Soft Reset Mode                    | . 146 |

| 12.8.3           | MSCAN08 Power-Down Mode                    |       |

| 12.8.4           | CPU Wait Mode                              | . 147 |

| 12.8.5           | Programmable Wakeup Function               |       |

| 12.9             | Timer Link                                 |       |

|                  | Clock System                               |       |

| 12.11            | Memory Map                                 |       |

|                  | Programmer's Model of Message Storage      |       |

| 12.12.1          |                                            |       |

| 12.12.2          | · ·                                        |       |

| 12.12.3          |                                            |       |

| 12.12.4          |                                            |       |

| 12.12.5          |                                            |       |

|                  | Programmer's Model of Control Registers    |       |

| 12.13.1          |                                            |       |

| 12.13.2          |                                            |       |

| 12.13.3          |                                            |       |

| 12.13.4          | 9 - 9                                      |       |

| 12.13.5          |                                            |       |

| 12.13.6          |                                            |       |

| 12.13.7          | ·                                          |       |

| 12.13.8          |                                            |       |

| 12.13.9          | · · · · · · · · · · · · · · · · · · ·      |       |

| 12.13.1          |                                            |       |

| 12.13.1          | 11 MSCAN08 Transmit Error Counter          | . 166 |

| 12.13.1          | 12 MSCAN08 Identifier Acceptance Registers | . 166 |

| 12.13.1          | ·                                          |       |

|                  | Chapter 13                                 |       |

|                  | Input/Output (I/O) Ports                   |       |

| 13.1             | Introduction                               | . 169 |

| 13.2             | Unused Pin Termination                     |       |

| 13.3             | Port A                                     |       |

| 13.3.1           | Port A Data Register                       |       |

| 13.3.2           | Data Direction Register A                  |       |

| 13.3.3           | Port A Input Pullup Enable Register        |       |

| 13.4             |                                            |       |

| 13.4.1           | Port B Data Register Port B Data Register  |       |

| 13.4.1           | Data Direction Register B                  |       |

|                  |                                            |       |

| 13.5             | Port C                                     |       |

| 13.5.1           | Port C Data Register                       |       |

| 13.5.2<br>13.5.3 | Data Direction Register C                  |       |

| 13.5.3           | Port C Input Pullup Enable Register        | . 180 |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# **Table of Contents**

| 19.7<br>19.7.1 | I/O  | Signals                                             | 290 |

|----------------|------|-----------------------------------------------------|-----|

| 19.7.2         |      | TIM2 Channel I/O Pins (T2CH5:T2CH2 and T2CH1:T2CH0) | 290 |

| 19.8           | I/O  | Registers                                           | 290 |

| 19.8.1         |      | TIM2 Status and Control Register                    | 291 |

| 19.8.2         |      | TIM2 Counter Registers                              | 292 |

| 19.8.3         |      | TIM2 Counter Modulo Registers                       | 293 |

| 19.8.4         |      | TIM2 Channel Status and Control Registers           | 293 |

| 19.8.5         |      | TIM2 Channel Registers                              | 297 |

|                |      | Chapter 20                                          |     |

|                |      | Development Support                                 |     |

| 20.1           | Intr | oduction                                            | 299 |

| 20.2           | Bre  | eak Module (BRK)                                    | 299 |

| 20.2.1         |      | Functional Description                              |     |

| 20.2.1.        | 1    | Flag Protection During Break Interrupts             |     |

| 20.2.1.        | 2    | TIM During Break Interrupts                         |     |

| 20.2.1.        | 3    | COP During Break Interrupts                         |     |

| 20.2.2         |      | Break Module Registers                              |     |

| 20.2.2.        | 1    | Break Status and Control Register                   |     |

| 20.2.2.        | 2    | Break Address Registers                             |     |

| 20.2.2.        | 3    | Break Status Register                               |     |

| 20.2.2.        | 4    | Break Flag Control Register                         |     |

| 20.2.3         |      | Low-Power Modes                                     | 304 |

| 20.3           | Мо   | nitor Module (MON)                                  | 305 |

| 20.3.1         |      | Functional Description                              |     |

| 20.3.1.        | 1    | Normal Monitor Mode                                 |     |

| 20.3.1.        | 2    | Forced Monitor Mode                                 | 309 |

| 20.3.1.        | 3    | Monitor Vectors                                     | 309 |

| 20.3.1.        | 4    | Data Format                                         | 310 |

| 20.3.1.        | 5    | Break Signal                                        | 310 |

| 20.3.1.        | 6    | Baud Rate                                           | 310 |

| 20.3.1.        | 7    | Commands                                            | 310 |

| 20.3.2         |      | Security                                            | 314 |

|                |      | Chapter 21                                          |     |

|                |      | Electrical Specifications                           |     |

| 21.1           | Intr | oduction                                            | 315 |

| 21.2           | Ab   | solute Maximum Ratings                              | 315 |

| 21.3           | Fui  | nctional Operating Range                            | 316 |

| 21.4           |      | ermal Characteristics                               |     |

| 21.5           |      | -Vdc Electrical Characteristics                     |     |

| 21.6           |      | -Vdc Electrical Characteristics                     |     |

|                |      |                                                     |     |

| 21.7           |      | -Volt Control Timing                                |     |

| 21.8           | 3.3  | -Volt Control Timing                                | 321 |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

| 322 |

|-----|

| 322 |

| 322 |

| 323 |

| 324 |

| 325 |

| 326 |

| 327 |

| 330 |

| 331 |

|     |

|     |

| 333 |

| 333 |

| 333 |

|     |

|     |

| 343 |

| 343 |

| 343 |

| 346 |

|     |

|     |

| 347 |

| 347 |

| 347 |

| 350 |

|     |

# **Chapter 1 General Description**

# 1.1 Introduction

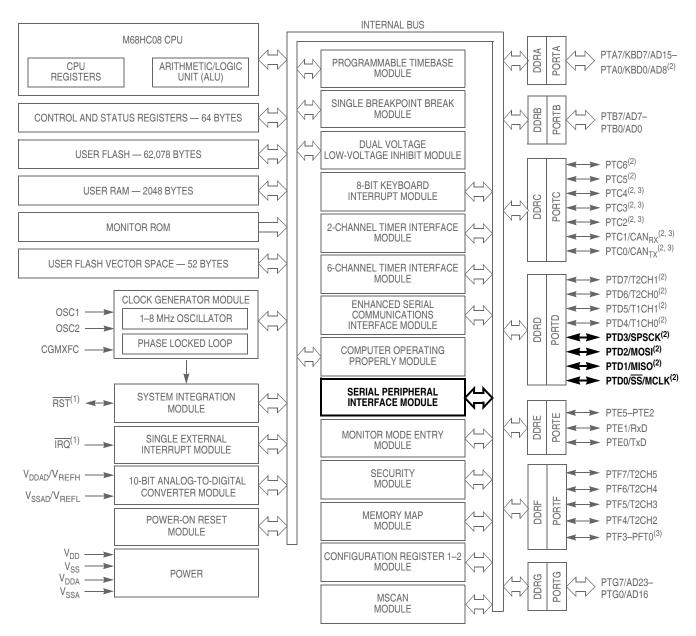

The MC68HC908GZ60, MC68HC908GZ48, and MC68HC908GZ32 are members of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

The information contained in this document pertains to all three devices with the exceptions noted in Appendix A MC68HC908GZ48 and Appendix B MC68HC908GZ32.

# 1.2 Features

For convenience, features have been organized to reflect:

- Standard features

- Features of the CPU08

#### 1.2.1 Standard Features

Features of the MC68HC908GZ60 include:

- High-performance M68HC08 architecture optimized for C-compilers

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- 8-MHz internal bus frequency

- Clock generation module supporting 1-MHz to 8-MHz crystals

- MSCAN08 (scalable controller area network) controller (implementing 2.0b protocol as defined in BOSCH specification dated September 1991)

- FLASH program memory security<sup>(1)</sup>

- On-chip programming firmware for use with host personal computer which does not require high voltage for entry

- In-system programming (ISP)

- System protection features:

- Optional computer operating properly (COP) reset

- Low-voltage detection with optional reset and selectable trip points for 3.3-V and 5.0-V operation

- Illegal opcode detection with reset

- Illegal address detection with reset

- Low-power design; fully static with stop and wait modes

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

| Addr.  | Register Name                                                            |                          | Bit 7 | 6         | 5       | 4         | 3                      | 2          | 1        | Bit 0    |

|--------|--------------------------------------------------------------------------|--------------------------|-------|-----------|---------|-----------|------------------------|------------|----------|----------|

|        | ESCI Data Register                                                       | Read:                    | R7    | R6        | R5      | R4        | R3                     | R2         | R1       | R0       |

| \$0018 | (SCDR)                                                                   | Write:                   | T7    | T6        | T5      | T4        | T3                     | T2         | T1       | T0       |

|        | See page 212.                                                            | Reset:                   |       | I.        | l       | Unaffecte | d by reset             |            | I.       | <u> </u> |

| \$0019 | ESCI Baud Rate Register (SCBR)                                           | Read:<br>Write:          | LINT  | LINR      | SCP1    | SCP0      | R                      | SCR2       | SCR1     | SCR0     |

|        | See page 212.                                                            | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 0        |

|        | Keyboard Status and Control                                              | Read:                    | 0     | 0         | 0       | 0         | KEYF                   | 0          | IMASKK   | MODEK    |

| \$001A | Register (INTKBSCR)                                                      | Write:                   |       |           |         |           |                        | ACKK       | IIVIASKK | MODEK    |

|        | See page 120.                                                            | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 0        |

| \$001B | Keyboard Interrupt Enable<br>\$001B Register (INTKBIER)<br>See page 121. | Read:<br>Write:          | KBIE7 | KBIE6     | KBIE5   | KBIE4     | KBIE3                  | KBIE2      | KBIE1    | KBIE0    |

|        |                                                                          | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 0        |

|        | Timebase Module Control<br>Register (TBCR)                               | ıle Control Read: TBIF - | TDDO  | TBR2 TBR1 | TBR0    | 0         | TBIE                   | TBON       | R        |          |

| \$001C |                                                                          | Write:                   |       | IDMZ      | IDNI    | IDNU      | TACK                   | TBIE   IBO | IBON     | n        |

|        | See page 262.                                                            | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 0        |

|        | IRQ Status and Control                                                   | Read:                    | 0     | 0         | 0       | 0         | IRQF                   | 0          | IMASK    | MODE     |

| \$001D | Register (INTSCR)                                                        | Write:                   |       |           |         |           |                        | ACK        | IIVIAGN  | MODE     |

|        | See page 114.                                                            | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 0        |

|        | Configuration Register 2                                                 | Read:                    | 0     | MCLKSEL   | MCLK1   | MCLK0     | MSCAN-                 | TMBCLK-    | OSCENIN- | SCIBDSRC |

| \$001E | (CONFIG2) <sup>(1)</sup><br>See page 92.                                 | Write:                   |       | WICLKSEL  | WICLKI  | WICLKU    | EN <sup>(1)</sup>      | SEL        | STOP     |          |

|        | See page 92.                                                             | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 1        |

| \$001F | Configuration Register 1 (CONFIG1) <sup>(1)</sup>                        | Read:<br>Write:          | COPRS | LVISTOP   | LVIRSTD | LVIPWRD   | LVI5OR3 <sup>(1)</sup> | SSREC      | STOP     | COPD     |

|        | See page 93.                                                             | Reset:                   | 0     | 0         | 0       | 0         | 0                      | 0          | 0        | 0        |

<sup>1.</sup> One-time writable register after each reset, except MSCANEN and LVI5OR3 bits. MSCANEN andLVI5OR3 bits are only reset via POR (power-on reset).

|                             |                         | _      |        |            |       |             |    |              |     |       |

|-----------------------------|-------------------------|--------|--------|------------|-------|-------------|----|--------------|-----|-------|

|                             | TIM1 Status and Control | Read:  | TOF    | TOIE       | TSTOP | 0           | 0  | PS2          | PS1 | PS0   |

| • ,                         | Register (T1SC)         | Write: | 0      | IOIL       | 10101 | TRST        |    | 1 02         | 101 | 1 00  |

|                             | See page 271.           | Reset: | 0      | 0          | 1     | 0           | 0  | 0            | 0   | 0     |

|                             | TIM1 Counter            | Read:  | Bit 15 | 14         | 13    | 12          | 11 | 10           | 9   | Bit 8 |

| \$0021                      | Register High (T1CNTH)  | Write: |        |            |       |             |    |              |     |       |

| See page 27                 | See page 273.           | Reset: | 0      | 0          | 0     | 0           | 0  | 0            | 0   | 0     |

|                             | TIM1 Counter            | Read:  | Bit 7  | 6          | 5     | 4           | 3  | 2            | 1   | Bit 0 |

| \$0022 Register Low (T1CNTL | Write:                  |        |        |            |       |             |    |              |     |       |

|                             | See page 273.           | Reset: | 0      | 0          | 0     | 0           | 0  | 0            | 0   | 0     |

|                             | TIM1 Counter Modulo     | Read:  | Bit 15 | 14         | 13    | 12          | 11 | 10           | 9   | Bit 8 |

| \$0023                      | Register High (T1MODH)  | Write: | כו וום | 14         | 13    | 12          | 11 | 10           | 9   | DIL 0 |

|                             | See page 273.           | Reset: | 1      | 1          | 1     | 1           | 1  | 1            | 1   | 1     |

|                             |                         |        |        | = Unimplem | ented | R = Reserve | d  | U = Unaffect | ed  |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 9)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# Memory

| Addr.  | Register Name                                        |                 | Bit 7                                       | 6                         | 5        | 4           | 3              | 2        | 1        | Bit 0  |  |

|--------|------------------------------------------------------|-----------------|---------------------------------------------|---------------------------|----------|-------------|----------------|----------|----------|--------|--|

|        | ADC Status and Control                               | Read:           | COCO                                        | AIEN                      | ADCO     | ADCH4       | ADCH3          | ADCH2    | ADCH1    | ADCH0  |  |

| \$003C | Register (ADSCR)                                     | Write:          | R                                           |                           |          |             |                |          |          |        |  |

|        | See page 68.                                         | Reset:          | 0                                           | 0                         | 0        | 1           | 1              | 1        | 1        | 1      |  |

|        | ADC Data High Register                               | Read:           | 0                                           | 0                         | 0        | 0           | 0              | 0        | AD9      | AD8    |  |

| \$003D | (ADRH)                                               | Write:          |                                             |                           |          |             |                |          |          |        |  |

|        | See page 70.                                         | Reset:          |                                             | 1                         | 1        |             | d by reset     |          | 1        | 1      |  |

|        | ADC Data Low Register                                | Read:           | AD7                                         | AD6                       | AD5      | AD4         | A3             | AD2      | AD1      | AD0    |  |

| \$003E | (ADRL)<br>See page 70.                               | Write:          |                                             |                           |          |             |                |          |          |        |  |

|        | See page 70.                                         | Reset:          |                                             | ı                         | 1        | Unaffecte   | d by reset     |          | ı        |        |  |

|        | ADC Clock Register                                   | Read:           | ADIV2                                       | ADIV1                     | ADIV0    | ADICLK      | MODE1          | MODE0    | R        | 0      |  |

| \$003F | (ADCLK)<br>See page 72.                              | Write:          |                                             |                           | <u> </u> |             |                |          |          |        |  |

|        | oce page 72.                                         | Reset:          | 0                                           | 0                         | 0        | 0           | 0              | 1        | 0        | 0      |  |

| \$0440 | Port F Data Register<br>(PTF)                        | Read:<br>Write: | PTF7                                        | PTF6                      | PTF5     | PTF4        | PTAF3          | PTF2     | PTF1     | PTF0   |  |

|        | See page 185.                                        | Reset:          |                                             |                           |          | Unaffecte   | d by reset     |          |          |        |  |

| \$0441 | Port G Data Register<br>(PTG)<br>See page 186.       | Read:<br>Write: | PTG7                                        | PTG6                      | PTG5     | PTG4        | PTG3           | PTG2     | PTG1     | PTG0   |  |

|        |                                                      | Reset:          |                                             | l .                       |          | Unaffecte   | d by reset     |          | l .      |        |  |

| \$0444 | Data Direction Register F<br>(DDRF)<br>See page 185. | Read:<br>Write: | DDRF7                                       | DDRF6                     | DDRF5    | DDRF4       | DDRF3          | DDRF2    | DDRF1    | DDRF0  |  |

|        |                                                      | Reset:          | 0                                           | 0                         | 0        | 0           | 0              | 0        | 0        | 0      |  |

| \$0445 | Data Direction Register G (DDRG)                     | Read:<br>Write: | DDRG7                                       | DDRG6                     | DDRG5    | DDRG4       | DDRG3          | DDRG2    | DDRG1    | DDRG0  |  |

|        | See page 187.                                        | Reset:          | 0                                           | 0                         | 0        | 0           | 0              | 0        | 0        | 0      |  |

| \$0448 | Keyboard Interrupt<br>Polarity Register              | Read:<br>Write: | KBIP7                                       | KBIP6                     | KBIP5    | KBIP4       | KBIP3          | KBIP2    | KBIP1    | KBIP0  |  |

|        | (INTKBIPR)<br>See page 121.                          | Reset:          | 0                                           | 0                         | 0        | 0           | 0              | 0        | 0        | 0      |  |

|        | TIM2 Channel 2 Status and                            | Read:           | CH2F                                        |                           |          |             |                |          |          |        |  |

| \$0456 | Control Register (T2SC2)                             | Write:          | 0                                           | CH2IE                     | MS2B     | MS2A        | ELS2B          | ELS2A    | TOV2     | CH2MAX |  |

|        | See page 297.                                        | Reset:          | 0                                           | 0                         | 0        | 0           | 0              | 0        | 0        | 0      |  |

| \$0457 | TIM2 Channel 2<br>Register High (T2CH2H)             | Read:<br>Write: | Bit 15                                      | 14                        | 13       | 12          | 11             | 10       | 9        | Bit 8  |  |

|        | See page 297.                                        | Reset:          |                                             | <u>I</u>                  | L        | Indetermina | te after reset | <u> </u> | <u>I</u> |        |  |

| \$0458 | TIM2 Channel 2<br>Register Low (T2CH2L)              | Read:<br>Write: | Bit 7                                       | 6                         | 5        | 4           | 3              | 2        | 1        | Bit 0  |  |

|        | See page 297.                                        | Reset:          |                                             | Indeterminate after reset |          |             |                |          |          |        |  |

|        |                                                      |                 | = Unimplemented R = Reserved U = Unaffected |                           |          |             |                |          |          |        |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 6 of 9)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

Decreasing the value in FL2BPR by one increases the protected range by one page (128 bytes). However, programming the block protect register with \$FE protects a range twice that size, 256 bytes, in the corresponding array. \$FE means that locations \$7F00–\$7FFF are protected in FLASH-2.

The FLASH memory does not exist at some locations. The block protection range configuration is unaffected if FLASH memory does not exist in that range. Refer to Figure 2-1 and make sure that the desired locations are protected.

# 2.7.3 FLASH-2 Block Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made for protecting blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by using the FLASH-2 block protection register (FL2BPR). FL2BPR determines the range of the FLASH-2 memory which is to be protected. The range of the protected area starts from a location defined by FL2BPR and ends at the bottom of the FLASH-2 memory (\$7FFF). When the memory is protected, the HVEN bit can not be set in either ERASE or PROGRAM operations.

#### NOTE

In performing a program or erase operation, the FLASH-2 block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLASH-2 block protect register is programmed with all 0's, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within FL2BPR are programmed (0), they lock a block of memory address ranges as shown in 2.7.2.2 FLASH-2 Block Protect Register. If FL2BPR is programmed with any value other than \$FF, the protected block of FLASH memory can not be erased or programmed.

#### NOTE

The vector locations and the FLASH block protect registers are located in the same page. FL1BPR and FL2BPR are not protected with special hardware or software. Therefore, if this page is not protected by FL1BPR and the vector locations are erased by either a page or a mass erase operation, both FL1BPR and FL2BPR will also get erased.

# 2.7.4 FLASH-2 Mass Erase Operation

Use this step-by-step procedure to erase the entire FLASH-2 memory:

- 1. Set both the ERASE bit and the MASS bit in the FLASH-2 control register (FL2CR).

- 2. Read the FLASH-2 block protect register (FL2BPR).

#### NOTE

Mass erase is disabled whenever any block is protected (FL2BPR does not equal \$FF).

- 3. Write to any FLASH-2 address within the FLASH-2 array with any data.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>MFBASE</sub> (minimum 4 ms).

- 7. Clear the EBASE and MASS bits.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# 4.3.1 Crystal Oscillator Circuit

The crystal oscillator circuit consists of an inverting amplifier and an external crystal. The OSC1 pin is the input to the amplifier and the OSC2 pin is the output. The SIMOSCEN signal from the system integration module (SIM) or the OSCENINSTOP bit in the CONFIG register enable the crystal oscillator circuit.

The CGMXCLK signal is the output of the crystal oscillator circuit and runs at a rate equal to the crystal frequency. CGMXCLK is then buffered to produce CGMRCLK, the PLL reference clock.

CGMXCLK can be used by other modules which require precise timing for operation. The duty cycle of CGMXCLK is not guaranteed to be 50% and depends on external factors, including the crystal and related external components. An externally generated clock also can feed the OSC1 pin of the crystal oscillator circuit. Connect the external clock to the OSC1 pin and let the OSC2 pin float.

# 4.3.2 Phase-Locked Loop Circuit (PLL)

The PLL is a frequency generator that can operate in either acquisition mode or tracking mode, depending on the accuracy of the output frequency. The PLL can change between acquisition and tracking modes either automatically or manually.

# 4.3.3 PLL Circuits

The PLL consists of these circuits:

- Voltage-controlled oscillator (VCO)

- Modulo VCO frequency divider

- Phase detector

- Loop filter

- Lock detector

The operating range of the VCO is programmable for a wide range of frequencies and for maximum immunity to external noise, including supply and CGMXFC noise. The VCO frequency is bound to a range from roughly one-half to twice the center-of-range frequency,  $f_{VRS}$ . Modulating the voltage on the CGMXFC pin changes the frequency within this range. By design,  $f_{VRS}$  is equal to the nominal center-of-range frequency,  $f_{NOM}$ , (71.4 kHz) times a linear factor, L, and a power-of-two factor, E, or  $(L \times 2^E)f_{NOM}$ .

CGMRCLK is the PLL reference clock, a buffered version of CGMXCLK. CGMRCLK runs at a frequency,  $f_{RCLK}$ . The VCO's output clock, CGMVCLK, running at a frequency,  $f_{VCLK}$ , is fed back through a programmable modulo divider. The modulo divider reduces the VCO clock by a factor, N. The dividers output is the VCO feedback clock, CGMVDV, running at a frequency,  $f_{VDV} = f_{VCLK}/(N)$ . (For more information, see 4.3.6 Programming the PLL.)

The phase detector then compares the VCO feedback clock, CGMVDV, with the final reference clock, CGMRDV. A correction pulse is generated based on the phase difference between the two signals. The loop filter then slightly alters the DC voltage on the external capacitor connected to CGMXFC based on the width and direction of the correction pulse. The filter can make fast or slow corrections depending on its mode, described in 4.3.4 Acquisition and Tracking Modes. The value of the external capacitor and the reference frequency determines the speed of the corrections and the stability of the PLL.

The lock detector compares the frequencies of the VCO feedback clock, CGMVDV, and the reference clock, CGMRCLK. Therefore, the speed of the lock detector is directly proportional to the reference

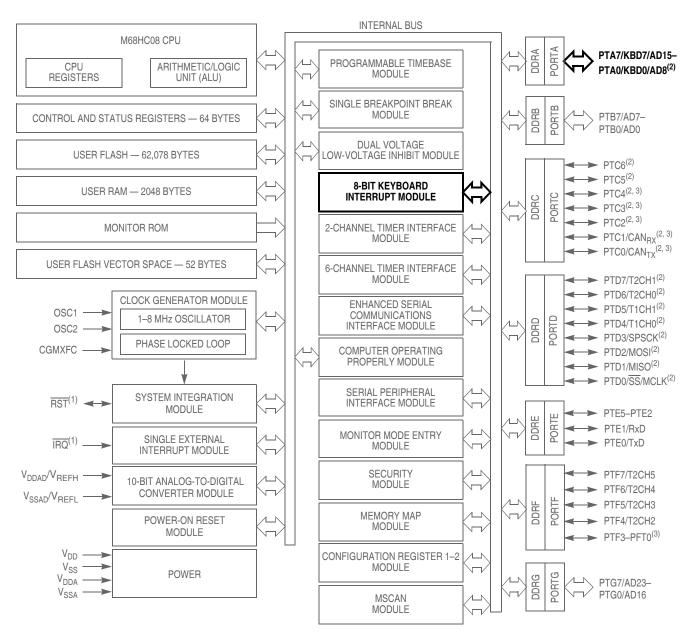

#### **Keyboard Interrupt Module (KBI)**

- 1. Pin contains integrated pullup device.

- 2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

- 3. Higher current drive port pins

Figure 9-1. Block Diagram Highlighting KBI Block and Pins

#### **MSCAN08 Controller (MSCAN08)**

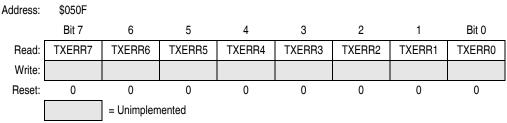

# 12.13.11 MSCAN08 Transmit Error Counter

Figure 12-26. Transmit Error Counter (CTXERR)

This read-only register reflects the status of the MSCAN08 transmit error counter.

#### NOTE

Both error counters may only be read when in sleep or soft reset mode.

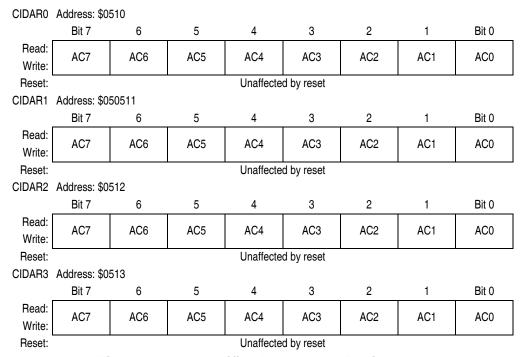

# 12.13.12 MSCAN08 Identifier Acceptance Registers

On reception each message is written into the background receive buffer. The CPU is only signalled to read the message, however, if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message will be overwritten by the next message (dropped).

The acceptance registers of the MSCAN08 are applied on the IDR0 to IDR3 registers of incoming messages in a bit by bit manner.

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers only the first two (CIDMR0/CIDMR1 and CIDAR0/CIDAR1) are applied.

Figure 12-27. Identifier Acceptance Registers (CIDAR0–CIDAR3)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### PTG7-PTG0 — Port G Data Bits

These read/write bits are software-programmable. Data direction of each port G pin is under the control of the corresponding bit in data direction register G. Reset has no effect on port G data.

#### AD23-AD16 — Analog-to-Digital Input Bits

AD23–AD16 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port G pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry.

#### NOTE

Care must be taken when reading port G while applying analog voltages to AD23–AD16 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTGx/ADx pin, while PTG is read as a digital input during the CPU read cycle. Those ports not selected as analog input channels are considered digital I/O ports.

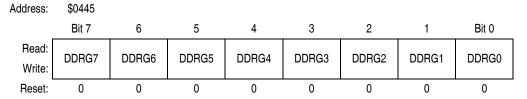

# 13.9.2 Data Direction Register G

Data direction register G (DDRG) determines whether each port G pin is an input or an output. Writing a 1 to a DDRG bit enables the output buffer for the corresponding port G pin; a 0 disables the output buffer.

Figure 13-24. Data Direction Register G (DDRG)

#### DDRG7-DDRG0 — Data Direction Register G Bits

These read/write bits control port G data direction. Reset clears DDRG7–DDRG0], configuring all port G pins as inputs.

- 1 = Corresponding port G pin configured as output

- 0 = Corresponding port G pin configured as input

#### NOTE

Avoid glitches on port G pins by writing to the port G data register before changing data direction register G bits from 0 to 1.

Figure 13-25 shows the port G I/O logic.

When bit DDRGx is a 1, reading address \$0441 reads the PTGx data latch. When bit DDRGx is a 0, reading address \$0441 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 13-8 summarizes the operation of the port G pins.

# 14.9 ESCI Arbiter

The ESCI module comprises an arbiter module designed to support software for communication tasks as bus arbitration, baud rate recovery and break time detection. The arbiter module consists of an 9-bit counter with 1-bit overflow and control logic. The CPU can control operation mode via the ESCI arbiter control register (SCIACTL).

# 14.9.1 ESCI Arbiter Control Register

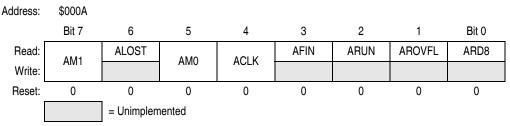

Figure 14-19. ESCI Arbiter Control Register (SCIACTL)

#### AM1 and AM0 — Arbiter Mode Select Bits

These read/write bits select the mode of the arbiter module as shown in Table 14-12. Reset clears AM1 and AM0.

| AM[1:0] | ESCI Arbiter Mode    |

|---------|----------------------|

| 0 0     | Idle / counter reset |

| 0 1     | Bit time measurement |

| 1 0     | Bus arbitration      |

**Table 14-12. ESCI Arbiter Selectable Modes**

# **ALOST** — Arbitration Lost Flag

This read-only bit indicates loss of arbitration. Clear ALOST by writing a 0 to AM1. Reset clears ALOST.

Reserved / do not use

#### **ACLK — Arbiter Counter Clock Select Bit**

This read/write bit selects the arbiter counter clock source. Reset clears ACLK.

- 1 = Arbiter counter is clocked with one half of the ESCI input clock generated by the ESCI prescaler

- 0 = Arbiter counter is clocked with the bus clock divided by four

1 1

#### NOTE

For ACLK = 1, the arbiter input clock is driven from the ESCI prescaler. The prescaler can be clocked by either the bus clock or CGMXCLK depending on the state of the SCIBDSRC bit in CONFIG2.

#### **AFIN— Arbiter Bit Time Measurement Finish Flag**

This read-only bit indicates bit time measurement has finished. Clear AFIN by writing any value to SCIACTL. Reset clears AFIN.

- 1 = Bit time measurement has finished

- 0 = Bit time measurement not yet finished

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### Serial Peripheral Interface (SPI) Module

- 1. Pin contains integrated pullup device.

- 2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

- 3. Higher current drive port pins

Figure 16-1. Block Diagram Highlighting SPI Block and Pins

#### SPRF — SPI Receiver Full Bit

This clearable, read-only flag is set each time a byte transfers from the shift register to the receive data register. SPRF generates a CPU interrupt request if the SPRIE bit in the SPI control register is set also.

During an SPRF CPU interrupt, the CPU clears SPRF by reading the SPI status and control register with SPRF set and then reading the SPI data register.

Reset clears the SPRF bit.

- 1 = Receive data register full

- 0 = Receive data register not full

#### **ERRIE** — Error Interrupt Enable Bit

This read/write bit enables the MODF and OVRF bits to generate CPU interrupt requests. Reset clears the ERRIE bit.

- 1 = MODF and OVRF can generate CPU interrupt requests

- 0 = MODF and OVRF cannot generate CPU interrupt requests

#### OVRF — Overflow Bit

This clearable, read-only flag is set if software does not read the byte in the receive data register before the next full byte enters the shift register. In an overflow condition, the byte already in the receive data register is unaffected, and the byte that shifted in last is lost. Clear the OVRF bit by reading the SPI status and control register with OVRF set and then reading the receive data register. Reset clears the OVRF bit.

- 1 = Overflow

- 0 = No overflow

#### MODF — Mode Fault Bit

This clearable, read-only flag is set in a slave SPI if the SS pin goes high during a transmission with MODFEN set. In a master SPI, the MODF flag is set if the SS pin goes low at any time with the MODFEN bit set. Clear MODF by reading the SPI status and control register (SPSCR) with MODF set and then writing to the SPI control register (SPCR). Reset clears the MODF bit.

- $1 = \overline{SS}$  pin at inappropriate logic level

- $0 = \overline{SS}$  pin at appropriate logic level

# SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE CPU interrupt request if SPTIE in the SPI control register is set also.

#### NOTE

Do not write to the SPI data register unless SPTE is high.

During an SPTE CPU interrupt, the CPU clears SPTE by writing to the transmit data register.

Reset sets the SPTE bit.

- 1 = Transmit data register empty

- 0 = Transmit data register not empty

#### **MODFEN** — Mode Fault Enable Bit

This read/write bit, when set, allows the MODF flag to be set. If the MODF flag is set, clearing MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is 0, then the  $\overline{SS}$  pin is available as a general-purpose I/O.

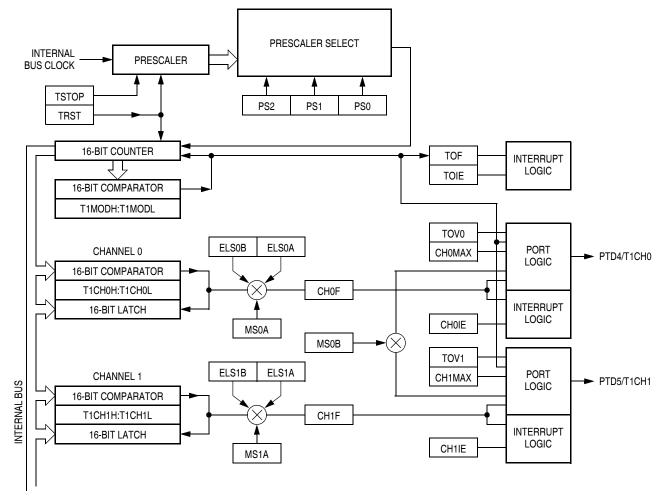

Figure 18-2. TIM1 Block Diagram

# 18.3.3 Output Compare

With the output compare function, the TIM1 can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM1 can set, clear, or toggle the channel pin. Output compares can generate TIM1 CPU interrupt requests.

# 18.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 18.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM1 channel registers.

An unsynchronized write to the TIM1 channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM1 overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM1 may pass the new value before it is written.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### **Timer Interface Module (TIM1)**

register 0 (TSCR0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM1 overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 18.8.4 TIM1 Channel Status and Control Registers.

# 18.4 Interrupts

The following TIM1 sources can generate interrupt requests:

- TIM1 overflow flag (TOF) The TOF bit is set when the TIM1 counter reaches the modulo value programmed in the TIM1 counter modulo registers. The TIM1 overflow interrupt enable bit, TOIE, enables TIM1 overflow CPU interrupt requests. TOF and TOIE are in the TIM1 status and control register.

- TIM1 channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE =1. CHxF and CHxIE are in the TIM1 channel x status and control register.

#### 18.5 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM1 remains active after the execution of a WAIT instruction. In wait mode the TIM1 registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM1 can bring the MCU out of wait mode.

If TIM1 functions are not required during wait mode, reduce power consumption by stopping the TIM1 before executing the WAIT instruction.

# 18.6 TIM1 During Break Interrupts

A break interrupt stops the TIM1 counter and inhibits input captures.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See Figure 15-21. Break Status Register (BSR).

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

# 19.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 19.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the value currently in the TIM2 channel registers.

An unsynchronized write to the TIM2 channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM2 overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM2 may pass the new value before it is written to the timer channel (T2CHxH:T2CHxL) registers.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the

new value in the output compare interrupt routine. The output compare interrupt occurs at the end

of the current pulse. The interrupt routine has until the end of the PWM period to write the new

value.

- When changing to a longer pulse width, enable TIM2 overflow interrupts and write the new value in the TIM2 overflow interrupt routine. The TIM2 overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

# 19.3.4.2 Buffered PWM Signal Generation

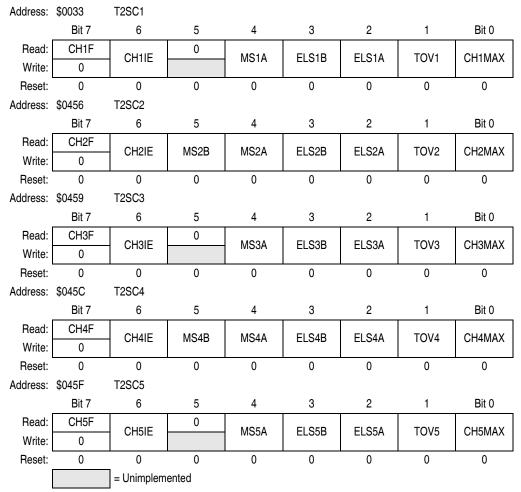

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the T2CH0 pin. The TIM2 channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM2 channel 0 status and control register (T2SC0) links channel 0 and channel 1. The TIM2 channel 0 registers initially control the pulse width on the T2CH0 pin. Writing to the TIM2 channel 1 registers enables the TIM2 channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM2 channel registers (0 or 1) that control the pulse width are the ones written to last. T2SC0 controls and monitors the buffered PWM function, and TIM2 channel 1 status and control register (T2SC1) is unused. While the MS0B bit is set, the channel 1 pin, T2CH1, is available as a general-purpose I/O pin.

Channels 2 and 3 can be linked to form a buffered PWM channel whose output appears on the T2CH2 pin. The TIM2 channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS2B bit in TIM2 channel 2 status and control register (T2SC2) links channel 2 and channel 3. The TIM2 channel 2 registers initially control the pulse width on the T2CH2 pin. Writing to the TIM2 channel 3 registers enables the TIM2 channel 3 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM2 channel registers (2 or 3) that control the pulse width are the ones written to last. T2SC2 controls and monitors the buffered PWM

#### **Timer Interface Module (TIM2)**

Figure 19-8. TIM2 Channel Status and Control Registers (T2SC0:T2SC5) (Continued)

#### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM2 counter registers matches the value in the TIM2 channel x registers.

When CHxIE = 1, clear CHxF by reading TIM2 channel x status and control register with CHxF set, and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

# CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM2 CPU interrupts on channel x.

Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# **Electrical Specifications**

# 21.12 5.0-Volt SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                   | Min                                              | Max                                   | Unit             |

|----------------------------------|----------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|---------------------------------------|------------------|

|                                  | Operating frequency Master Slave                                     | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub> | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz       |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub>                      | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                     | 1                                                | _                                     | t <sub>CYC</sub> |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                      | 1                                                | _                                     | t <sub>CYC</sub> |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 6                                | Data setup time (inputs) Master Slave                                | t <sub>SU(M)</sub>                       | 30<br>30                                         |                                       | ns<br>ns         |

| 7                                | Data hold time (inputs) Master Slave                                 | t <sub>H(M)</sub>                        | 30<br>30                                         | _<br>_                                | ns<br>ns         |

| 8                                | Access time, slave <sup>(3)</sup> CPHA = 0 CPHA = 1                  | t <sub>A(CP0)</sub>                      | 0<br>0                                           | 40<br>40                              | ns<br>ns         |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                      | _                                                | 40                                    | ns               |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub> t <sub>V(S)</sub>      | _                                                | 50<br>50                              | ns<br>ns         |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub>                       | 0<br>0                                           | _                                     | ns<br>ns         |

- 1. Numbers refer to dimensions in Figure 21-2 and Figure 21-3.

2. All timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless noted; 100 pF load on all SPI pins.

3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

- 5. With 100 pF on all SPI pins

326 Freescale Semiconductor

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# Appendix B MC68HC908GZ32

# **B.1 Introduction**

The MC68HC908GZ32 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

The information contained in this document pertains to the MC68HC908GZ32 with the exceptions shown in this appendix.

# **B.2 Block Diagram**

See Figure B-1.

# **B.3 Memory**

The MC68HC908GZ32 can address 32 Kbytes of memory space. The memory map, shown in Figure B-2, includes:

- 32 Kbytes of user FLASH memory

- 1536 bytes of random-access memory (RAM)

- 52 bytes of user-defined vectors