Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, SCI, SPI                                                      |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 53                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 24x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-QFP                                                                |

| Supplier Device Package    | 64-QFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gz48vfue |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 4 Clock Generator Module (CGM)

| 4.1    | Introduction                                     | 73 |

|--------|--------------------------------------------------|----|

| 4.2    | Features                                         | 73 |

| 4.3    | Functional Description                           | 73 |

| 4.3.1  | Crystal Oscillator Circuit                       | 75 |

| 4.3.2  | Phase-Locked Loop Circuit (PLL)                  | 75 |

| 4.3.3  | PLL Circuits                                     |    |

| 4.3.4  | Acquisition and Tracking Modes                   | 76 |

| 4.3.5  | Manual and Automatic PLL Bandwidth Modes         |    |

| 4.3.6  | Programming the PLL                              |    |

| 4.3.7  | Special Programming Exceptions                   | 79 |

| 4.3.8  | Base Clock Selector Circuit                      | 79 |

| 4.3.9  | CGM External Connections                         | 80 |

| 4.4    | I/O Signals                                      | 81 |

| 4.4.1  | Crystal Amplifier Input Pin (OSC1)               |    |

| 4.4.2  | Crystal Amplifier Output Pin (OSC2)              |    |

| 4.4.3  | External Filter Capacitor Pin (CGMXFC)           | 81 |

| 4.4.4  | PLL Analog Power Pin (V <sub>DDA</sub> )         |    |

| 4.4.5  | PLL Analog Ground Pin (V <sub>SSA</sub> )        | 81 |

| 4.4.6  | Oscillator Enable Signal (SIMOSCEN)              | 81 |

| 4.4.7  | Oscillator Enable in Stop Mode Bit (OSCENINSTOP) | 81 |

| 4.4.8  | Crystal Output Frequency Signal (CGMXCLK)        |    |

| 4.4.9  | CGM Base Clock Output (CGMOUT)                   | 82 |

| 4.4.10 | CGM CPU Interrupt (CGMINT)                       | 82 |

| 4.5    | CGM Registers                                    | 82 |

| 4.5.1  | PLL Control Register                             | 83 |

| 4.5.2  | PLL Bandwidth Control Register                   | 85 |

| 4.5.3  | PLL Multiplier Select Register High              | 86 |

| 4.5.4  | PLL Multiplier Select Register Low               |    |

| 4.5.5  | PLL VCO Range Select Register                    | 87 |

| 4.6    | Interrupts                                       | 88 |

| 4.7    | Special Modes                                    | 88 |

| 4.7.1  | Wait Mode                                        | 88 |

| 4.7.2  | Stop Mode                                        | 88 |

| 4.7.3  | CGM During Break Interrupts                      | 88 |

| 4.8    | Acquisition/Lock Time Specifications             | 89 |

| 4.8.1  | Acquisition/Lock Time Definitions                |    |

| 4.8.2  | Parametric Influences on Reaction Time           |    |

| 4.8.3  | Choosing a Filter                                |    |

|        | Chapter 5                                        |    |

|        | Configuration Register (CONFIG)                  |    |

| 5.1    | Introduction                                     | 91 |

| 5.2    | Functional Description                           | 91 |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

Programming tools are available from Freescale. Contact your local Freescale representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents. (1)

## 2.7.2 FLASH-2 Control and Block Protect Registers

The FLASH-2 array has two registers that control its operation, the FLASH-2 control register (FL2CR) and the FLASH-2 block protect register (FL2BPR).

## 2.7.2.1 FLASH-2 Control Register

The FLASH-2 control register (FL2CR) controls FLASH-2 program and erase operations.

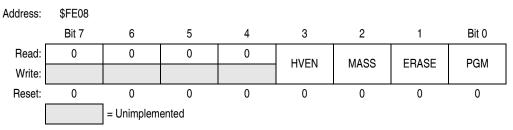

Figure 2-7. FLASH-2 Control Register (FL2CR)

## **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

## MASS — Mass Erase Control Bit

Setting this read/write bit configures the FLASH-2 array for mass or page erase operation.

- 1 = Mass erase operation selected

- 0 = Page erase operation selected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be set at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

#### **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

# Chapter 3 Analog-to-Digital Converter (ADC)

## 3.1 Introduction

This section describes the 10-bit analog-to-digital converter (ADC).

## 3.2 Features

Features of the ADC module include:

- 24 channels with multiplexed input

- · Linear successive approximation with monotonicity

- 10-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock

- Left or right justified result

- · Left justified sign data mode

# 3.3 Functional Description

The ADC provides 24 pins for sampling external sources at pins PTG7/AD23–PTG0/AD16, PTA7/KBD7/AD15–PTA0/KBD0/AD8, and PTB7/AD7–PTB0/AD0. An analog multiplexer allows the single ADC converter to select one of 24 ADC channels as ADC voltage in (V<sub>ADIN</sub>). V<sub>ADIN</sub> is converted by the successive approximation register-based analog-to-digital converter. When the conversion is completed, ADC places the result in the ADC data register and sets a flag or generates an interrupt. See Figure 3-2.

#### 3.3.1 ADC Port I/O Pins

PTG7/AD23–PTG0/AD16, PTA7/KBD7/AD15–PTA0/KBD0/AD8, and PTB7/AD7–PTB0/AD0 are general-purpose I/O (input/output) pins that share with the ADC channels. The channel select bits define which ADC channel/port pin will be used as the input signal. The ADC overrides the port I/O logic by forcing that pin as input to the ADC. The remaining ADC channels/port pins are controlled by the port I/O logic and can be used as general-purpose I/O. Writes to the port register or data direction register (DDR) will not have any affect on the port pin that is selected by the ADC. A read of a port pin in use by the ADC will return a 0.

61

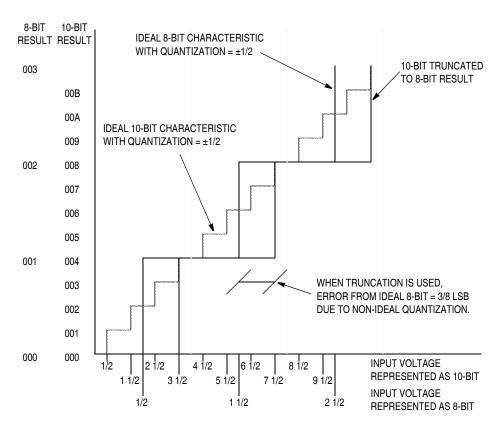

Left justified sign data mode is similar to left justified mode with one exception. The MSB of the 10-bit result, AD9 located in ADRH, is complemented. This mode of operation is useful when a result, represented as a signed magnitude from mid-scale, is needed. Finally, 8-bit truncation mode will place the eight MSBs in the ADC data register low, ADRL. The two LSBs are dropped. This mode of operation is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

# **NOTE**Quantization error is affected when only the most significant eight bits are used as a result. See Figure 3-3.

Figure 3-3. Bit Truncation Mode Error

# 3.4 Monotonicity

The conversion process is monotonic and has no missing codes.

# 3.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating CPU interrupts after each ADC conversion. A CPU interrupt is generated if the COCO bit is a 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

## **Computer Operating Properly (COP) Module**

To prevent inadvertently turning off the COP with a STOP instruction, a configuration option is available that disables the STOP instruction. When the STOP bit in the configuration register has the STOP instruction disabled, execution of a STOP instruction results in an illegal opcode reset.

# 6.8 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

# Table 7-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Operation Description                                                                                                                                                                                                                                                                                                                                                        |   | Effect<br>on CC |   |          |     |     | Address<br>Mode                       | Opcode                             | Operand        | les    |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------|---|----------|-----|-----|---------------------------------------|------------------------------------|----------------|--------|

| Form                                                         | operation.                            |                                                                                                                                                                                                                                                                                                                                                                              |   | V H I N Z C     |   | Add      | Opc | Ope | Cycles                                |                                    |                |        |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | _ | _               | 1 | _        | _   | _   | INH                                   | 83                                 |                | 9      |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    | 1 | 1               | 1 | ‡        | 1   | 1   | INH                                   | 84                                 |                | 2      |

| TAX                                                          | Transfer A to X                       | X ← (A)                                                                                                                                                                                                                                                                                                                                                                      | - | -               | _ | -        | -   | -   | INH                                   | 97                                 |                | 1      |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | - | -               | _ | -        | -   | -   | INH                                   | 85                                 |                | 1      |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       | 0 | _               | _ | <b>‡</b> | 1   | ı   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 311324 |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | - | -               | - | -        | -   | -   | INH                                   | 95                                 |                | 2      |

| TXA                                                          | Transfer X to A                       | A ← (X)                                                                                                                                                                                                                                                                                                                                                                      | - | -               | _ | -        | -   | -   | INH                                   | 9F                                 |                | 1      |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | - | -               | _ | _        | _   | -   | INH                                   | 94                                 |                | 2      |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | - | -               | 0 | -        | -   | _   | INH                                   | 8F                                 |                | 1      |

| Α     | Accumulator                                                         | n            | Any bit                                     |

|-------|---------------------------------------------------------------------|--------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr          | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC           | Program counter                             |

| dd    | Direct address of operand                                           | PCH          | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction |              | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL          | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel          | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr           | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1          | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            | SP2          | - · · · · · · · · · · · · · · · · · · ·     |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP           | Stack pointer                               |

| Н     | Half-carry bit                                                      | U            | Undefined                                   |

| Н     | Index register high byte                                            | V            | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | X            | Index register low byte                     |

| 1     | Interrupt mask                                                      | Z            | Zero bit                                    |

| ii    | Immediate operand byte                                              | &            | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              | 1_           | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$     | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()           | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | -( )         | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #            | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **           | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$ | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?            | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :            | Concatenated with                           |

| M     | Memory location                                                     | 1            | Set or cleared                              |

| N     | Negative bit                                                        | _            | Not affected                                |

# 7.8 Opcode Map

See Table 7-2.

#### **MSCAN08 Controller (MSCAN08)**

completed within the inter-frame sequence (IFS) to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU reacts with short latencies to the transmit interrupt.

A double buffer scheme would de-couple the re-loading of the transmit buffers from the actual message being sent and as such reduces the reactiveness requirements on the CPU. Problems may arise if the sending of a message would be finished just while the CPU re-loads the second buffer. In that case, no buffer would then be ready for transmission and the bus would be released.

At least three transmit buffers are required to meet the first of the above requirements under all circumstances. The MSCAN08 has three transmit buffers.

The second requirement calls for some sort of internal prioritization which the MSCAN08 implements with the "local priority" concept described in 12.4.2 Receive Structures.

### 12.4.2 Receive Structures

The received messages are stored in a 2-stage input first in first out (FIFO). The two message buffers are mapped using a "ping pong" arrangement into a single memory area (see Figure 12-3). While the background receive buffer (RxBG) is exclusively associated to the MSCAN08, the foreground receive buffer (RxFG) is addressable by the central processor unit (CPU08). This scheme simplifies the handler software, because only one address area is applicable for the receive process.

Both buffers have a size of 13 bytes to store the CAN control bits, the identifier (standard or extended), and the data content. For details, see 12.12 Programmer's Model of Message Storage.

The receiver full flag (RXF) in the MSCAN08 receiver flag register (CRFLG), signals the status of the foreground receive buffer. When the buffer contains a correctly received message with matching identifier, this flag is set. See 12.13.5 MSCAN08 Receiver Flag Register (CRFLG)

On reception, each message is checked to see if it passes the filter (for details see 12.5 Identifier Acceptance Filter) and in parallel is written into RxBG. The MSCAN08 copies the content of RxBG into RxFG<sup>(1)</sup>, sets the RXF flag, and generates a receive interrupt to the CPU<sup>(2)</sup>. The user's receive handler has to read the received message from RxFG and to reset the RXF flag to acknowledge the interrupt and to release the foreground buffer. A new message which can follow immediately after the IFS field of the CAN frame, is received into RxBG. The overwriting of the background buffer is independent of the identifier filter function.

When the MSCAN08 module is transmitting, the MSCAN08 receives its own messages into the background receive buffer, RxBG. It does NOT overwrite RxFG, generate a receive interrupt or acknowledge its own messages on the CAN bus. The exception to this rule is in loop-back mode (see 12.13.2 MSCAN08 Module Control Register 1), where the MSCAN08 treats its own messages exactly like all other incoming messages. The MSCAN08 receives its own transmitted messages in the event that it loses arbitration. If arbitration is lost, the MSCAN08 must be prepared to become the receiver.

An overrun condition occurs when both the foreground and the background receive message buffers are filled with correctly received messages with accepted identifiers and another message is correctly received from the bus with an accepted identifier. The latter message will be discarded and an error interrupt with overrun indication will be generated if enabled. The MSCAN08 is still able to transmit messages with both receive message buffers filled, but all incoming messages are discarded.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

<sup>1.</sup> Only if the RXF flag is not set.

<sup>2.</sup> The receive interrupt will occur only if not masked. A polling scheme can be applied on RXF also.

- 2. Two identifier acceptance filters, each to be applied to:

- The 14 most significant bits of the extended identifier plus the SRR and the IDE bits of CAN2.0B messages, or

- b. The 11 bits of the identifier plus the RTR and IDE bits of CAN 2.0A/B messages.

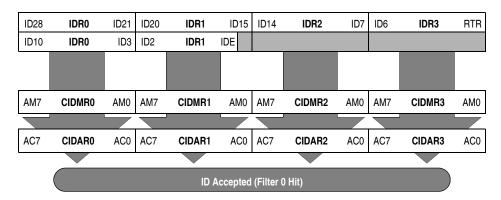

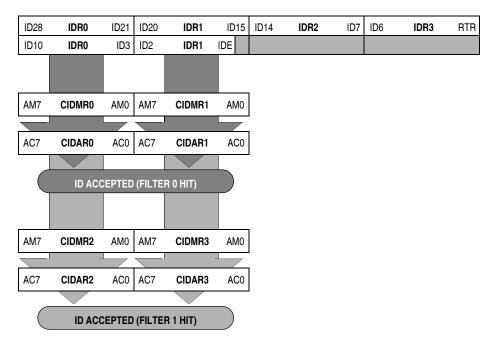

Figure 12-5 shows how the 32-bit filter bank (CIDAR0–CIDAR3 and CIDMR0–CIDMR3) produces filter 0 and 1 hits.

- 3. Four identifier acceptance filters, each to be applied to the first eight bits of the identifier. This mode implements four independent filters for the first eight bits of a CAN 2.0A/B compliant standard identifier. Figure 12-6 shows how the 32-bit filter bank (CIDAR0–CIDAR3 and CIDMR0–CIDMR3) produces filter 0 to 3 hits.

- 4. Closed filter. No CAN message will be copied into the foreground buffer RxFG, and the RXF flag will never be set.

Figure 12-4. Single 32-Bit Maskable Identifier Acceptance Filter

Figure 12-5. Dual 16-Bit Maskable Acceptance Filters

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

Input/Output (I/O) Ports

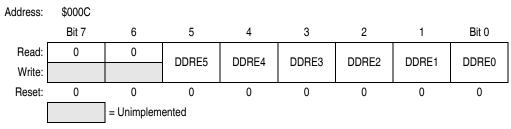

## 13.7.2 Data Direction Register E

Data direction register E (DDRE) determines whether each port E pin is an input or an output. Writing a 1 to a DDRE bit enables the output buffer for the corresponding port E pin; a 0 disables the output buffer.

Figure 13-18. Data Direction Register E (DDRE)

## DDRE5-DDRE0 — Data Direction Register E Bits

These read/write bits control port E data direction. Reset clears DDRE5–DDRE0, configuring all port E pins as inputs.

- 1 = Corresponding port E pin configured as output

- 0 = Corresponding port E pin configured as input

#### NOTE

Avoid glitches on port E pins by writing to the port E data register before changing data direction register E bits from 0 to 1.

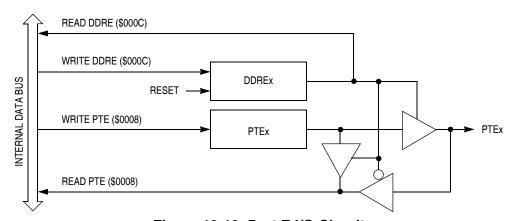

Figure 13-19 shows the port E I/O logic.

When bit DDREx is a 1, reading address \$0008 reads the PTEx data latch. When bit DDREx is a 0, reading address \$0008 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 13-6 summarizes the operation of the port E pins.

Figure 13-19. Port E I/O Circuit Table 13-6. Port E Pin Functions

| DDRE | PTE              | I/O Pin                    | Accesses to DDRE | Accesses to PTE |                          |  |  |

|------|------------------|----------------------------|------------------|-----------------|--------------------------|--|--|

| Bit  | Bit              | Mode                       | Read/Write       | Read            | Write                    |  |  |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRE5-DDRE0      | Pin             | PTE5-PTE0 <sup>(3)</sup> |  |  |

| 1    | Х                | Output                     | DDRE5-DDRE0      | PTE5-PTE0       | PTE5-PTE0                |  |  |

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

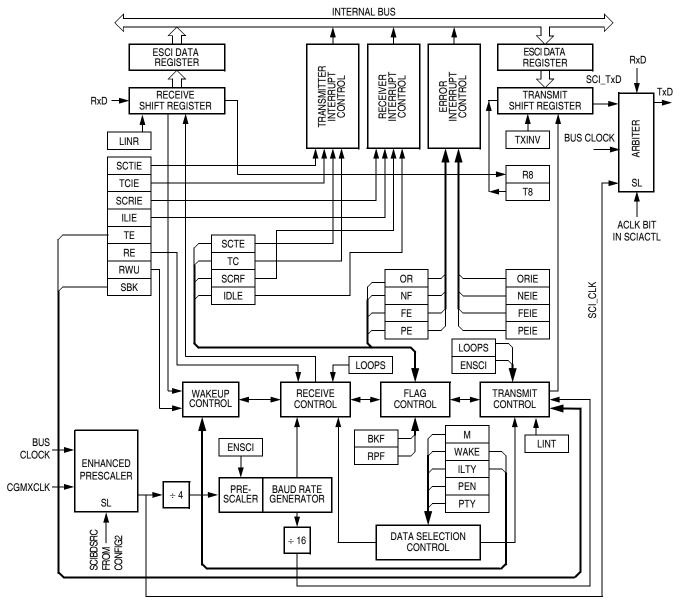

## **Enhanced Serial Communications Interface (ESCI) Module**

SL = 1 -> SCI\_CLK = BUSCLK SL = 0 -> SCI\_CLK = CGMXCLK

Figure 14-3. ESCI Module Block Diagram

## 14.5.2 Stop Mode

The ESCI module is inactive in stop mode. The STOP instruction does not affect ESCI register states. ESCI module operation resumes after the MCU exits stop mode.

Because the internal clock is inactive during stop mode, entering stop mode during an ESCI transmission or reception results in invalid data.

## 14.6 ESCI During Break Module Interrupts

The BCFE bit in the break flag control register (SBFCR) enables software to clear status bits during the break state. See 20.2 Break Module (BRK).

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

## 14.7 I/O Signals

Port E shares two of its pins with the ESCI module. The two ESCI I/O pins are:

- PTE0/TxD transmit data

- PTE1/RxD receive data

## 14.7.1 PTE0/TxD (Transmit Data)

The PTE0/TxD pin is the serial data output from the ESCI transmitter. The ESCI shares the PTE0/TxD pin with port E. When the ESCI is enabled, the PTE0/TxD pin is an output regardless of the state of the DDRE0 bit in data direction register E (DDRE).

## 14.7.2 PTE1/RxD (Receive Data)

The PTE1/RxD pin is the serial data input to the ESCI receiver. The ESCI shares the PTE1/RxD pin with port E. When the ESCI is enabled, the PTE1/RxD pin is an input regardless of the state of the DDRE1 bit in data direction register E (DDRE).

# 14.8 I/O Registers

These I/O registers control and monitor ESCI operation:

- ESCI control register 1, SCC1

- ESCI control register 2, SCC2

- ESCI control register 3, SCC3

- ESCI status register 1, SCS1

- ESCI status register 2, SCS2

- ESCI data register, SCDR

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

**Enhanced Serial Communications Interface (ESCI) Module**

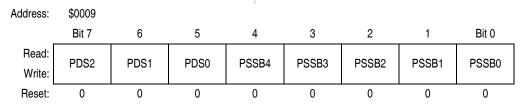

## 14.8.8 ESCI Prescaler Register

The ESCI prescaler register (SCPSC) together with the ESCI baud rate register selects the baud rate for both the receiver and the transmitter.

#### NOTE

There are two prescalers available to adjust the baud rate. One in the ESCI baud rate register and one in the ESCI prescaler register.

Figure 14-18. ESCI Prescaler Register (SCPSC)

## PDS2-PDS0 — Prescaler Divisor Select Bits

These read/write bits select the prescaler divisor as shown in Table 14-9. Reset clears PDS2-PDS0.

#### NOTE

The setting of '000' will bypass not only this prescaler but also the prescaler divisor fine adjust (PDFA). It is not recommended to bypass the prescaler while ENSCI is set, because the switching is not glitch free.

| Table | 14-9. E | ESCII | Prescaler | Division | Ratio |

|-------|---------|-------|-----------|----------|-------|

|-------|---------|-------|-----------|----------|-------|

| PDS[2:1:0] | Prescaler Divisor (PD) |

|------------|------------------------|

| 0 0 0      | Bypass this prescaler  |

| 0 0 1      | 2                      |

| 0 1 0      | 3                      |

| 0 1 1      | 4                      |

| 1 0 0      | 5                      |

| 1 0 1      | 6                      |

| 1 1 0      | 7                      |

| 1 1 1      | 8                      |

## PSSB4-PSSB0 — Clock Insertion Select Bits

These read/write bits select the number of clocks inserted in each 32 output cycle frame to achieve more timing resolution on the **average** prescaler frequency as shown in Table 14-10. Reset clears PSSB4–PSSB0.

**Table 14-10. ESCI Prescaler Divisor Fine Adjust**

| PSSB[4:3:2:1:0] | Prescaler Divisor Fine Adjust (PDFA) |

|-----------------|--------------------------------------|

| 0 0 0 0 0       | 0/32 = 0                             |

| 0 0 0 0 1       | 1/32 = 0.03125                       |

| 0 0 0 1 0       | 2/32 = 0.0625                        |

| 0 0 0 1 1       | 3/32 = 0.09375                       |

| 0 0 1 0 0       | 4/32 = 0.125                         |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

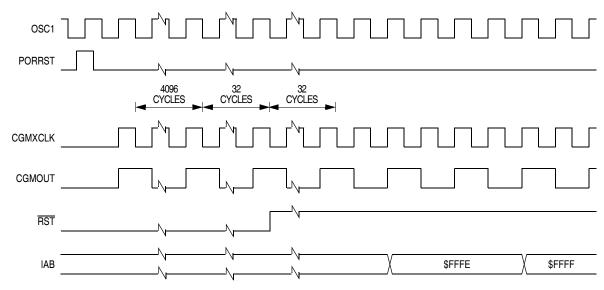

Figure 15-7. POR Recovery

## 15.3.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

If the stop enable bit, STOP, in the CONFIG1 register is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the  $\overline{RST}$  pin for all internal reset sources.

## 15.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the RST pin for all internal reset sources.

## 15.3.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the  $V_{TRIPF}$  voltage. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RST) is asserted if the LVIPWRD and LVIRSTD bits in the CONFIG1 register are 0. The RST pin will be held low while the SIM counter counts out 4096 + 32 CGMXCLK cycles after  $V_{DD}$  rises above  $V_{TRIPR}$ . Thirty-two CGMXCLK cycles later, the CPU is released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the RST pin for all internal reset sources.

## 15.3.2.6 Monitor Mode Entry Module Reset (MODRST)

The monitor mode entry module reset (MODRST) asserts its output to the SIM when monitor mode is entered in the condition where the reset vectors are erased (\$FF) (see 20.3.1.1 Normal Monitor Mode). When MODRST gets asserted, an internal reset occurs. The SIM actively pulls down the RST pin for all internal reset sources.

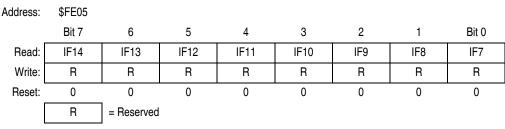

## Interrupt Status Register 2

Figure 15-13. Interrupt Status Register 2 (INT2)

## IF14-IF7 — Interrupt Flags 14-7

These flags indicate the presence of interrupt requests from the sources shown in Table 15-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

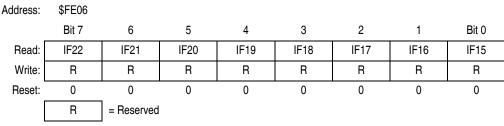

## Interrupt Status Register 3

Figure 15-14. Interrupt Status Register 3 (INT3)

## IF22-IF15 — Interrupt Flags 22-15

These flags indicate the presence of an interrupt request from the source shown in Table 15-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

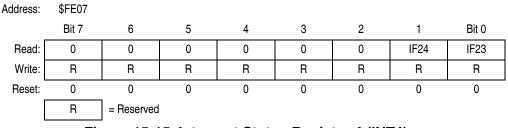

## Interrupt Status Register 4

Figure 15-15. Interrupt Status Register 4 (INT4)

## Bits 7-2 — Always read 0

## IF24-IF23 — Interrupt Flags 24-23

These flags indicate the presence of an interrupt request from the source shown in Table 15-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### **Timer Interface Module (TIM1)**

- 1. Pin contains integrated pullup device.

- 2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

- 3. Higher current drive port pins

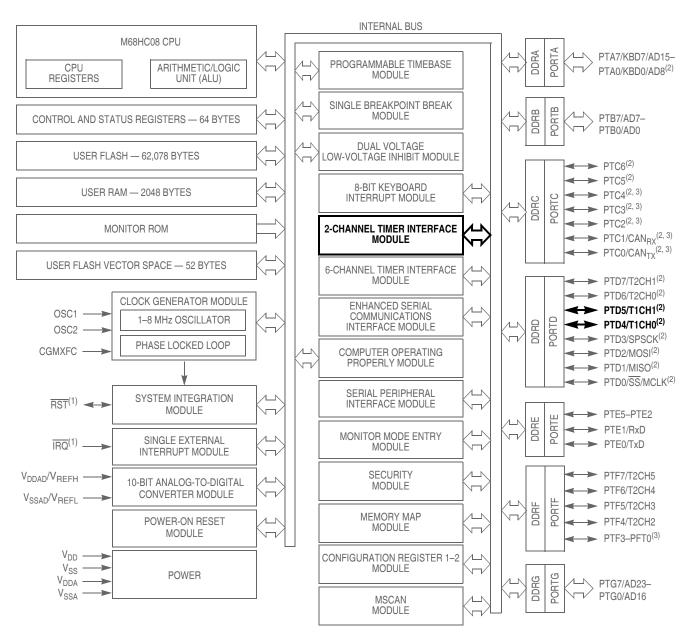

Figure 18-1. Block Diagram Highlighting TIM1 Block and Pins

## 19.8.3 TIM2 Counter Modulo Registers

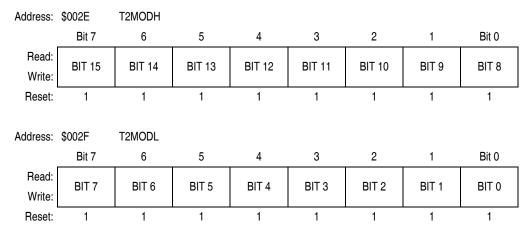

The read/write TIM2 modulo registers contain the modulo value for the TIM2 counter. When the TIM2 counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIM2 counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (T2MODH) inhibits the TOF bit and overflow interrupts until the low byte (T2MODL) is written. Reset sets the TIM2 counter modulo registers.

Figure 19-7. TIM2 Counter Modulo Registers (T2MODH and T2MODL)

#### NOTE

Reset the TIM2 counter before writing to the TIM2 counter modulo registers.

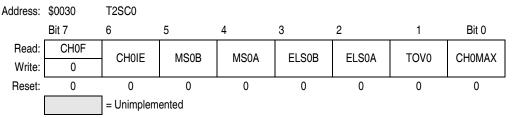

## 19.8.4 TIM2 Channel Status and Control Registers

Each of the TIM2 channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM2 overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 19-8. TIM2 Channel Status and Control Registers (T2SC0:T2SC5)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

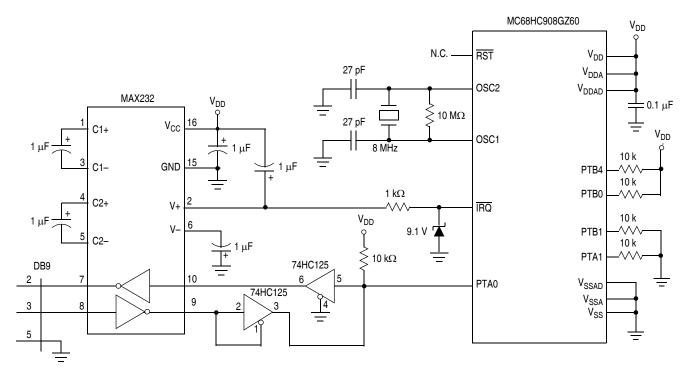

Figure 20-10. Normal Monitor Mode Circuit

Figure 20-11. Forced Monitor Mode

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

## **Electrical Specifications**

# 21.9 Clock Generation Module (CGM) Characteristics

# 21.9.1 CGM Operating Conditions

| Characteristic                                 | Symbol                               | Min                              | Тур   | Max                              | Unit |

|------------------------------------------------|--------------------------------------|----------------------------------|-------|----------------------------------|------|

| Operating voltage                              | V <sub>DDA</sub><br>V <sub>SSA</sub> | $V_{DD} - 0.3$<br>$V_{SS} - 0.3$ |       | $V_{DD} + 0.3$<br>$V_{SS} + 0.3$ | V    |

| Crystal reference frequency                    | f <sub>RCLK</sub>                    | 1                                | _     | 8                                | MHz  |

| Input clock frequency (PLL off) <sup>(1)</sup> | f <sub>XCLK</sub>                    | _                                | _     | 32                               | MHz  |

| Range nominal multiplier                       | f <sub>NOM</sub>                     | _                                | 71.42 | _                                | kHz  |

| VCO center-of-range frequency <sup>(2)</sup>   | f <sub>VRS</sub>                     | 71.42k                           | _     | 40M                              | Hz   |

| VCO operating frequency <sup>(3)</sup>         | f <sub>VCLK</sub>                    | 71.42k                           | _     | 32M                              | Hz   |

- 1. External square wave applied to OSC1. Voltage levels must be rail-to-rail and duty cycle must be 50%.

- 2. Range of frequencies that VCO can produce to generate input clock to frequency divider during acquisition and tracking modes.

- 3. Allowed VCO operating range.

## 21.9.2 CGM Component Information

| Characteristic                                      | Symbol            | Min                                            | Тур                       | Max | Unit |  |  |  |

|-----------------------------------------------------|-------------------|------------------------------------------------|---------------------------|-----|------|--|--|--|

| Crystal frequency                                   | f <sub>XCLK</sub> | 1                                              | _                         | 8   | MHz  |  |  |  |

| Crystal load capacitance <sup>(1)</sup>             | C <sub>L</sub>    | _                                              | 20                        | _   | pF   |  |  |  |

| Crystal fixed capacitance <sup>(2)</sup>            | C <sub>1</sub>    | _                                              | (2 x C <sub>L</sub> ) – 5 | 47  | pF   |  |  |  |

| Crystal tuning capacitance <sup>(3)</sup>           | C <sub>2</sub>    | _                                              | (2 x C <sub>L</sub> ) – 5 | 47  | pF   |  |  |  |

| Feedback bias resistor                              | R <sub>B</sub>    | _                                              | 1                         | 10  | MΩ   |  |  |  |

| Series damping resistor                             | R <sub>S</sub>    | 0                                              | 0                         | _   | kΩ   |  |  |  |

| V <sub>DDA</sub> /V <sub>SSA</sub> bypass capacitor | C <sub>byp</sub>  | _                                              | 0.1                       | _   | μF   |  |  |  |

| CGMXFC filter values                                | See Ta            | See Table 4-5. Example Filter Component Values |                           |     |      |  |  |  |

- 1. Consult crystal manufacturer's specification.

- 2. Capacitor on OSC1 pin. Does not include parasitic capacitance due to package, pin, and board.

- 3. Capacitor on OSC2 pin. Does not include parasitic capacitance due to package, pin, and board.

**Electrical Specifications**

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

## Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

## For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005, 2006, 2007. All rights reserved.