Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | CANbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 53                                                         |

| Program Memory Size        | 60KB (60K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 2K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | A/D 24x10b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 64-QFP                                                     |

| Supplier Device Package    | 64-QFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908gz60cfue |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

| Addr.         | Register Name                                         |                 | Bit 7                        | 6                   | 5      | 4           | 3              | 2            | 1     | Bit 0                                        |  |  |

|---------------|-------------------------------------------------------|-----------------|------------------------------|---------------------|--------|-------------|----------------|--------------|-------|----------------------------------------------|--|--|

| \$003C        | ADC Status and Control<br>Register (ADSCR)            | Read:<br>Write: | COCO<br>R                    | AIEN                | ADCO   | ADCH4       | ADCH3          | ADCH2        | ADCH1 | ADCH0                                        |  |  |

|               | See page 68.                                          | Reset:          | 0                            | 0                   | 0      | 1           | 1              | 1            | 1     | 1                                            |  |  |

|               | ADC Data High Register                                | Read:           | 0                            | 0                   | 0      | 0           | 0              | 0            | AD9   | AD8                                          |  |  |

| \$003D (ADRH) |                                                       | Write:          |                              |                     |        |             |                |              |       |                                              |  |  |

|               | See page 70.                                          | Reset:          |                              | Unaffected by reset |        |             |                |              |       |                                              |  |  |

|               | ADC Data Low Register                                 | Read:           | AD7                          | AD6                 | AD5    | AD4         | A3             | AD2          | AD1   | AD0                                          |  |  |

| \$003E        | (ADRL)                                                | Write:          |                              |                     |        |             |                |              |       |                                              |  |  |

|               | See page 70.                                          | Reset:          |                              |                     |        | Unaffecte   | d by reset     |              |       |                                              |  |  |

| \$003F        | ADC Clock Register<br>(ADCLK)                         | Read:<br>Write: | ADIV2                        | ADIV1               | ADIV0  | ADICLK      | MODE1          | MODE0        | R     | 0                                            |  |  |

|               | See page 72.                                          | Reset:          | 0                            | 0                   | 0      | 0           | 0              | 1            | 0     | 0                                            |  |  |

| \$0440        | Port F Data Register<br>(PTF)                         | Read:<br>Write: | PTF7                         | PTF6                | PTF5   | PTF4        | PTAF3          | PTF2         | PTF1  | PTF0                                         |  |  |

|               | See page 185.                                         | Reset:          |                              |                     |        | Unaffecte   | d by reset     |              |       | <u>.                                    </u> |  |  |

| \$0441        | Port G Data Register<br>(PTG)                         | Read:<br>Write: | PTG7                         | PTG6                | PTG5   | PTG4        | PTG3           | PTG2         | PTG1  | PTG0                                         |  |  |

|               | See page 186.                                         | Reset:          |                              | 1                   |        | Unaffecte   | d by reset     |              | 1     | I                                            |  |  |

| \$0444        | Data Direction Register F<br>(DDRF)                   | Read:<br>Write: | DDRF7                        | DDRF6               | DDRF5  | DDRF4       | DDRF3          | DDRF2        | DDRF1 | DDRF0                                        |  |  |

|               | See page 185.                                         | Reset:          | 0                            | 0                   | 0      | 0           | 0              | 0            | 0     | 0                                            |  |  |

| \$0445        | Data Direction Register G<br>(DDRG)                   | Read:<br>Write: | DDRG7                        | DDRG6               | DDRG5  | DDRG4       | DDRG3          | DDRG2        | DDRG1 | DDRG0                                        |  |  |

|               | See page 187.                                         | Reset:          | 0                            | 0                   | 0      | 0           | 0              | 0            | 0     | 0                                            |  |  |

| \$0448        | Keyboard Interrupt<br>Polarity Register<br>(INTKBIPR) | Read:<br>Write: | KBIP7                        | KBIP6               | KBIP5  | KBIP4       | KBIP3          | KBIP2        | KBIP1 | KBIP0                                        |  |  |

|               | See page 121.                                         | Reset:          | 0                            | 0                   | 0      | 0           | 0              | 0            | 0     | 0                                            |  |  |

|               | TIM2 Channel 2 Status and                             | Read:           | CH2F                         |                     | MOOD   | 14004       |                | FL 00A       | TO1/0 | OLIONAAV                                     |  |  |

| \$0456        | Control Register (T2SC2)                              | Write:          | 0                            | CH2IE               | MS2B   | MS2A        | ELS2B          | ELS2A        | TOV2  | CH2MAX                                       |  |  |

|               | See page 297.                                         | Reset:          | 0                            | 0                   | 0      | 0           | 0              | 0            | 0     | 0                                            |  |  |

| \$0457        | TIM2 Channel 2<br>Register High (T2CH2H)              | Read:<br>Write: | Bit 15                       | 14                  | 13     | 12          | 11             | 10           | 9     | Bit 8                                        |  |  |

|               | See page 297.                                         | Reset:          |                              | 1                   | 1      | Indetermina | te after reset |              | 1     | <u>.                                    </u> |  |  |

| \$0458        | TIM2 Channel 2<br>Register Low (T2CH2L)               | Read:<br>Write: | Bit 7                        | 6                   | 5      | 4           | 3              | 2            | 1     | Bit 0                                        |  |  |

|               | See page 297.                                         | Reset:          | t: Indeterminate after reset |                     |        |             |                |              |       |                                              |  |  |

|               |                                                       |                 |                              | = Unimplem          | nented | R = Reserve | d              | U = Unaffect | ted   |                                              |  |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 6 of 9)

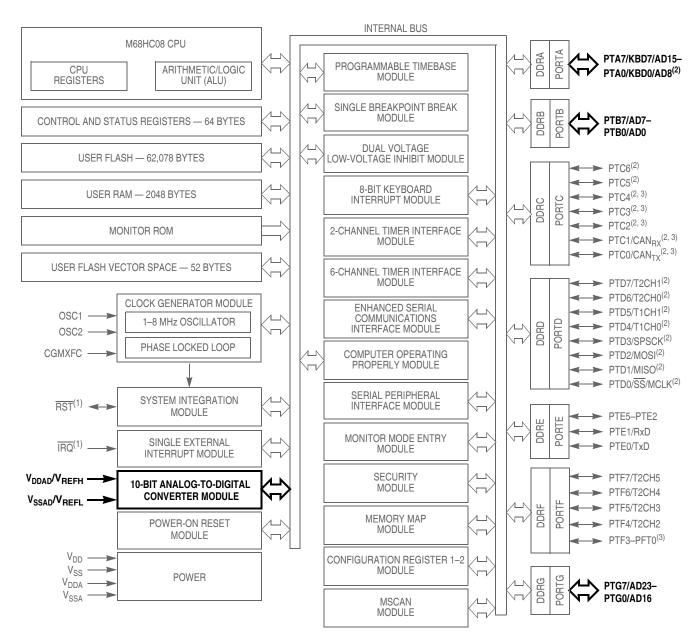

### Analog-to-Digital Converter (ADC)

1. Pin contains integrated pullup device.

2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

3. Higher current drive port pins

### Figure 3-1. Block Diagram Highlighting ADC Block and Pins

### **Configuration Register (CONFIG)**

### LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module (see Chapter 11 Low-Voltage Inhibit (LVI)). The voltage mode selected for the LVI should match the operating  $V_{DD}$  (see Chapter 21

Electrical Specifications) for the LVI's voltage trip points for each of the modes.

1 = LVI operates in 5-V mode

0 = LVI operates in 3-V mode

### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 CGMXCLK cycles instead of a 4096-CGMXCLK cycle delay.

1 = Stop mode recovery after 32 CGMXCLK cycles

0 = Stop mode recovery after 4096 CGMXCLK cycles

### NOTE

Exiting stop mode by any reset will result in the long stop recovery.

The short stop recovery delay can be enabled when using a crystal or resonator and the OSCENINSTOP bit is set. The short stop recovery delay can be enabled when an external oscillator is used, regardless of the OSCENINSTOP setting.

The short stop recovery delay must be disabled when the OSCENINSTOP bit is clear and a crystal or resonator is used.

### STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

### COPD — COP Disable Bit

COPD disables the COP module. See Chapter 6 Computer Operating Properly (COP) Module.

- 1 = COP module disabled

- 0 = COP module enabled

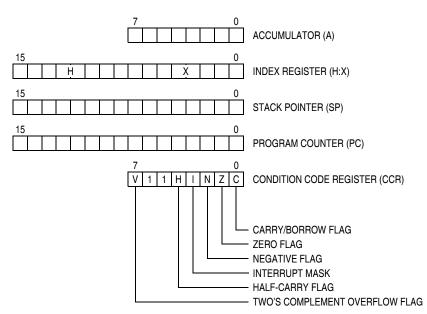

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

# 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

# 7.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

| Source<br>Form                                                                                        | Operation                                            | Description                                                                                                                                                                                                                                                                                                                                   |   |    | Effect<br>on CCR |    |   |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                                                       | les                                       |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------------------|----|---|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|

| Form                                                                                                  | ·                                                    |                                                                                                                                                                                                                                                                                                                                               |   |    | I                | NZ |   | С | Add<br>Moo                                                                                   |                                                  | Ope                                                                           | Cycles                                    |

| BHS rel                                                                                               | Branch if Higher or Same<br>(Same as BCC)            | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$                                                                                                                                                                                                                                                                                             | - | -  | -                | -  | - | - | REL                                                                                          | 24                                               | rr                                                                            | 3                                         |

| BIH rel                                                                                               | Branch if IRQ Pin High                               | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 1$                                                                                                                                                                                                                                                                                           | - | -  | -                | -  | - | - | REL                                                                                          | 2F                                               | rr                                                                            | 3                                         |

| BIL rel                                                                                               | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                  | - | -  | Ι                | Ι  | - | Ι | REL                                                                                          | 2E                                               | rr                                                                            | 3                                         |

| BIT #opr<br>BIT opr<br>BIT opr,<br>BIT opr,X<br>BIT opr,X<br>BIT x<br>BIT opr,SP<br>BIT opr,SP        | Bit Test                                             | (A) & (M)                                                                                                                                                                                                                                                                                                                                     | 0 | _  | _                | ţ  | ţ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff                                     | 2<br>3<br>4<br>3<br>2<br>4<br>5           |

| BLE opr                                                                                               | Branch if Less Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                           | - | -  | -                | -  | - | - | REL                                                                                          | 93                                               | rr                                                                            | 3                                         |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                                                                                                                                                                                                                                                                                             | - | -  | -                | -  | - | - | REL                                                                                          | 25                                               | rr                                                                            | 3                                         |

| BLS rel                                                                                               | Branch if Lower or Same                              | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                    | - | -  | -                | -  |   | - | REL                                                                                          | 23                                               | rr                                                                            | 3                                         |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                    | - | -  | -                | -  | - | - | REL                                                                                          | 91                                               | rr                                                                            | 3                                         |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                       | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | -  | - | - | REL                                                                                          | 2C                                               | rr                                                                            | 3                                         |

| BMI rel                                                                                               | Branch if Minus                                      | $PC \leftarrow (PC) + 2 + rel? (N) = 1$                                                                                                                                                                                                                                                                                                       | - | -  | -                | -  | - | - | REL                                                                                          | 2B                                               | rr                                                                            | 3                                         |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                         | $PC \leftarrow (PC) + 2 + rel? (I) = 1$                                                                                                                                                                                                                                                                                                       | - | -  | -                | -  | - | - | REL                                                                                          | 2D                                               | rr                                                                            | 3                                         |

| BNE rel                                                                                               | Branch if Not Equal                                  | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | -  | - | - | REL                                                                                          | 26                                               | rr                                                                            | 3                                         |

| BPL rel                                                                                               | Branch if Plus                                       | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | -  | - | - | REL                                                                                          | 2A                                               | rr                                                                            | 3                                         |

| BRA rel                                                                                               | Branch Always                                        | $PC \leftarrow (PC) + 2 + rel$                                                                                                                                                                                                                                                                                                                | - | -  | -                | -  | - | - | REL                                                                                          | 20                                               | rr                                                                            | 3                                         |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                    | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                         | _ | _  | _                | _  | _ | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 555555555                                 |

| BRN rel                                                                                               | Branch Never                                         | $PC \leftarrow (PC) + 2$                                                                                                                                                                                                                                                                                                                      | - | -  | -                | -  | - | - | REL                                                                                          | 21                                               | rr                                                                            | 3                                         |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                      | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                         | _ | _  | _                | _  | _ | Ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555<br>55555555555555555555555555555 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                                | Mn ← 1                                                                                                                                                                                                                                                                                                                                        | _ | _  | _                | _  | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                            | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4      |

| BSR rel                                                                                               | Branch to Subroutine                                 | $\begin{array}{l} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\  SP \leftarrow (SP) - 1 \\  PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                              | _ | _  | _                | _  | _ | - | REL                                                                                          | AD                                               | rr                                                                            | 4                                         |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                          | $\begin{array}{c} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$ | _ | _  | _                | _  | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                               | 5<br>4<br>4<br>5<br>4<br>6                |

| CLC                                                                                                   | Clear Carry Bit                                      | C ← 0                                                                                                                                                                                                                                                                                                                                         | - | -  | -                | -  | - | 0 | INH                                                                                          | 98                                               |                                                                               | 1                                         |

| CLI                                                                                                   | Clear Interrupt Mask                                 | l ← 0                                                                                                                                                                                                                                                                                                                                         | - | 1- | 0                | -  | - | - | INH                                                                                          | 9A                                               |                                                                               | 2                                         |

| Table 7-1. Instruction Set Summary | (Sheet 2 of 6) |

|------------------------------------|----------------|

|------------------------------------|----------------|

Low-Power Modes

# 10.15 Exiting Wait Mode

These events restart the CPU clock and load the program counter with the reset vector or with an interrupt vector:

- External reset A low on the RST pin resets the MCU and loads the program counter with the contents of locations \$FFFE and \$FFFF.

- External interrupt A high-to-low transition on an external interrupt pin (IRQ pin) loads the program counter with the contents of locations: \$FFFA and \$FFFB; IRQ pin.

- Break interrupt In emulation mode, a break interrupt loads the program counter with the contents of \$FFFC and \$FFFD.

- Computer operating properly (COP) module reset A timeout of the COP counter resets the MCU and loads the program counter with the contents of \$FFFE and \$FFFF.

- Low-voltage inhibit (LVI) module reset A power supply voltage below the V<sub>TRIPF</sub> voltage resets the MCU and loads the program counter with the contents of locations \$FFFE and \$FFFF.

- Clock generator module (CGM) interrupt A CPU interrupt request from the CGM loads the program counter with the contents of \$FFF8 and \$FFF9.

- Keyboard interrupt (KBI) module A CPU interrupt request from the KBI module loads the program counter with the contents of \$FFE0 and \$FFE1.

- Timer 1 interface (TIM1) module interrupt A CPU interrupt request from the TIM1 loads the program counter with the contents of:

- \$FFF2 and \$FFF3; TIM1 overflow

- \$FFF4 and \$FFF5; TIM1 channel 1

- \$FFF6 and \$FFF7; TIM1 channel 0

- Timer 2 interface module (TIM2) interrupt A CPU interrupt request from the TIM2 loads the program counter with the contents of:

- \$FFEC and \$FFED; TIM2 overflow

- \$FFEE and \$FFEF; TIM2 channel 1

- \$FFF0 and \$FFF1; TIM2 channel 0

- \$FFCC and \$FFCD; TIM2 channel 5

- \$FFCE and \$FFCF; TIM2 channel 4

- \$FFD0 and \$FFD1; TIM2 channel 3

- \$FFD2 and \$FFD3; TIM2 channel 2

- Serial peripheral interface (SPI) module interrupt A CPU interrupt request from the SPI loads the program counter with the contents of:

- \$FFE8 and \$FFE9; SPI transmitter

- \$FFEA and \$FFEB; SPI receiver

- Serial communications interface (SCI) module interrupt A CPU interrupt request from the SCI loads the program counter with the contents of:

- \$FFE2 and \$FFE3; SCI transmitter

- \$FFE4 and \$FFE5; SCI receiver

- \$FFE6 and \$FFE7; SCI receiver error

- Analog-to-digital converter (ADC) module interrupt A CPU interrupt request from the ADC loads the program counter with the contents of: \$FFDE and \$FFDF; ADC conversion complete.

- Timebase module (TBM) interrupt A CPU interrupt request from the TBM loads the program counter with the contents of: \$FFDC and \$FFDD; TBM interrupt.

# 12.12 Programmer's Model of Message Storage

This section details the organization of the receive and transmit message buffers and the associated control registers. For reasons of programmer interface simplification, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13-byte data structure. An additional transmit buffer priority register (TBPR) is defined for the transmit buffers.

| Addr <sup>(1)</sup> | Register Name                                    |

|---------------------|--------------------------------------------------|

| \$05b0              | IDENTIFIER REGISTER 0                            |

| \$05b1              | IDENTIFIER REGISTER 1                            |

| \$05b2              | IDENTIFIER REGISTER 2                            |

| \$05b3              | IDENTIFIER REGISTER 3                            |

| \$05b4              | DATA SEGMENT REGISTER 0                          |

| \$05b5              | DATA SEGMENT REGISTER 1                          |

| \$05b6              | DATA SEGMENT REGISTER 2                          |

| \$05b7              | DATA SEGMENT REGISTER 3                          |

| \$05b8              | DATA SEGMENT REGISTER 4                          |

| \$05b9              | DATA SEGMENT REGISTER 5                          |

| \$05bA              | DATA SEGMENT REGISTER 6                          |

| \$05bB              | DATA SEGMENT REGISTER 7                          |

| \$05bC              | DATA LENGTH REGISTER                             |

| \$05bD              | TRANSMIT BUFFER PRIORITY REGISTER <sup>(2)</sup> |

| \$05bE              | UNUSED                                           |

| \$05bF              | UNUSED                                           |

1. Where b equals the following:

b = 4 for receive buffer

b = 5 for transmit buffer 0

b = 6 for transmit buffer 1

b = 7 for transmit buffer 2

2. Not applicable for receive buffers

### Figure 12-11. Message Buffer Organization

Input/Output (I/O) Ports

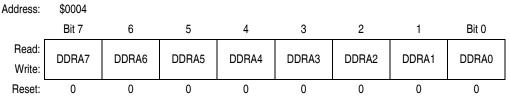

# 13.3.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 13-3. Data Direction Register A (DDRA)

# DDRA7–DDRA0 — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA7–DDRA0, configuring all port A pins as inputs.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

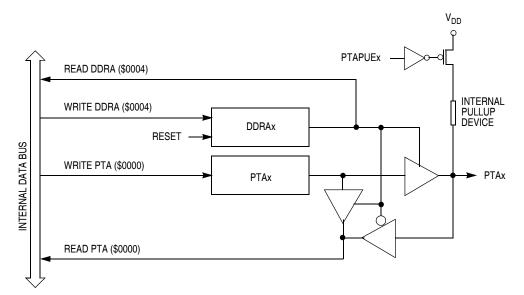

Figure 13-4 shows the port A I/O logic.

When bit DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When bit DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 13-2 summarizes the operation of the port A pins.

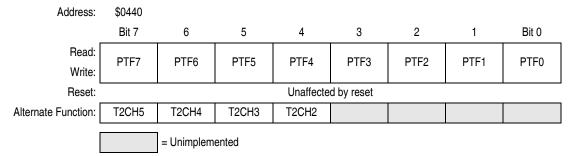

# 13.8 Port F

Port F is an 8-bit special-function port that shares four of its pins with the timer interface (TIM2) module.

# 13.8.1 Port F Data Register

The port F data register (PTF) contains a data latch for each of the eight port F pins.

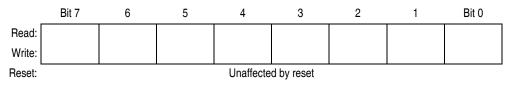

Figure 13-20. Port F Data Register (PTF)

### PTF7–PTF0 — Port F Data Bits

These read/write bits are software-programmable. Data direction of each port F pin is under the control of the corresponding bit in data direction register F. Reset has no effect on port F data.

### T2CH5–T2CH2 — Timer 2 Channel I/O Bits

The PTF7/T2CH5–PTF4/T2CH2 pins are the TIM2 input capture/output compare pins. The edge/level select bits, ELSxB:ELSxA, determine whether the PTF7/T2CH5–PTF4/T2CH2 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 18 Timer Interface Module (TIM1) and Chapter 19 Timer Interface Module (TIM2).

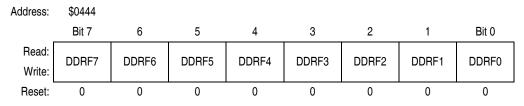

# 13.8.2 Data Direction Register F

Data direction register F (DDRF) determines whether each port F pin is an input or an output. Writing a 1 to a DDRF bit enables the output buffer for the corresponding port F pin; a 0 disables the output buffer.

Figure 13-21. Data Direction Register F (DDRF)

### DDRF7–DDRF0 — Data Direction Register F Bits

These read/write bits control port F data direction. Reset clears DDRF7–DDRF0, configuring all port F pins as inputs.

1 = Corresponding port F pin configured as output

0 = Corresponding port F pin configured as input

### NOTE

Avoid glitches on port F pins by writing to the port F data register before changing data direction register F bits from 0 to 1.

Figure 13-22 shows the port F I/O logic.

**Functional Description**

To initiate an ESCI transmission:

- 1. Enable the ESCI by writing a 1 to the enable ESCI bit (ENSCI) in ESCI control register 1 (SCC1).

- 2. Enable the transmitter by writing a 1 to the transmitter enable bit (TE) in ESCI control register 2 (SCC2).

- 3. Clear the ESCI transmitter empty bit (SCTE) by first reading ESCI status register 1 (SCS1) and then writing to the SCDR. For 9-bit data, also write the T8 bit in SCC3.

- 4. Repeat step 3 for each subsequent transmission.

At the start of a transmission, transmitter control logic automatically loads the transmit shift register with a preamble of 1s. After the preamble shifts out, control logic transfers the SCDR data into the transmit shift register. A 0 start bit automatically goes into the least significant bit (LSB) position of the transmit shift register. A 1 stop bit goes into the most significant bit (MSB) position.

The ESCI transmitter empty bit, SCTE, in SCS1 becomes set when the SCDR transfers a byte to the transmit shift register. The SCTE bit indicates that the SCDR can accept new data from the internal data bus. If the ESCI transmit interrupt enable bit, SCTIE, in SCC2 is also set, the SCTE bit generates a transmitter CPU interrupt request.

When the transmit shift register is not transmitting a character, the TxD pin goes to the idle condition, high. If at any time software clears the ENSCI bit in ESCI control register 1 (SCC1), the transmitter and receiver relinquish control of the port E pins.

### 14.4.2.3 Break Characters

Writing a 1 to the send break bit, SBK, in SCC2 loads the transmit shift register with a break character. For TXINV = 0 (output not inverted), a transmitted break character contains all 0s and has no start, stop, or parity bit. Break character length depends on the M bit in SCC1 and the LINR bits in SCBR. As long as SBK is at 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one 1. The automatic 1 at the end of a break character guarantees the recognition of the start bit of the next character.

When LINR is cleared in SCBR, the ESCI recognizes a break character when a start bit is followed by eight or nine 0 data bits and a 0 where the stop bit should be, resulting in a total of 10 or 11 consecutive 0 data bits. When LINR is set in SCBR, the ESCI recognizes a break character when a start bit is followed by 9 or 10 0 data bits and a 0 where the stop bit should be, resulting in a total of 11 or 12 consecutive 0 data bits.

Receiving a break character has these effects on ESCI registers:

- Sets the framing error bit (FE) in SCS1

- Sets the ESCI receiver full bit (SCRF) in SCS1

- Clears the ESCI data register (SCDR)

- Clears the R8 bit in SCC3

- Sets the break flag bit (BKF) in SCS2

- May set the overrun (OR), noise flag (NF), parity error (PE), or reception in progress flag (RPF) bits

# 14.5.2 Stop Mode

The ESCI module is inactive in stop mode. The STOP instruction does not affect ESCI register states. ESCI module operation resumes after the MCU exits stop mode.

Because the internal clock is inactive during stop mode, entering stop mode during an ESCI transmission or reception results in invalid data.

# 14.6 ESCI During Break Module Interrupts

The BCFE bit in the break flag control register (SBFCR) enables software to clear status bits during the break state. See 20.2 Break Module (BRK).

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

# 14.7 I/O Signals

Port E shares two of its pins with the ESCI module. The two ESCI I/O pins are:

- PTE0/TxD transmit data

- PTE1/RxD receive data

# 14.7.1 PTE0/TxD (Transmit Data)

The PTE0/TxD pin is the serial data output from the ESCI transmitter. The ESCI shares the PTE0/TxD pin with port E. When the ESCI is enabled, the PTE0/TxD pin is an output regardless of the state of the DDRE0 bit in data direction register E (DDRE).

### 14.7.2 PTE1/RxD (Receive Data)

The PTE1/RxD pin is the serial data input to the ESCI receiver. The ESCI shares the PTE1/RxD pin with port E. When the ESCI is enabled, the PTE1/RxD pin is an input regardless of the state of the DDRE1 bit in data direction register E (DDRE).

# 14.8 I/O Registers

These I/O registers control and monitor ESCI operation:

- ESCI control register 1, SCC1

- ESCI control register 2, SCC2

- ESCI control register 3, SCC3

- ESCI status register 1, SCS1

- ESCI status register 2, SCS2

- ESCI data register, SCDR

### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (high). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

1 = Transmitter enabled

0 = Transmitter disabled

### NOTE

Writing to the TE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

### **RE** — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

1 = Receiver enabled

0 = Receiver disabled

### NOTE

Writing to the RE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

### RWU — Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

1 = Standby state

0 = Normal operation

### SBK — Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a 1. The 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no 1s between them. Reset clears the SBK bit.

1 = Transmit break characters

0 = No break characters being transmitted

### NOTE

Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the ESCI to send a break character instead of a preamble.

# 14.8.3 ESCI Control Register 3

ESCI control register 3 (SCC3):

- Stores the ninth ESCI data bit received and the ninth ESCI data bit to be transmitted.

- Enables these interrupts:

- Receiver overrun

- Noise error

- Framing error

- Parity error

Enhanced Serial Communications Interface (ESCI) Module

### System Integration Module (SIM)

| Source                    | Flag                                                   | Mask <sup>(1)</sup>                                     | INT Register<br>Flag | Priority <sup>(2)</sup> | Vector<br>Address |

|---------------------------|--------------------------------------------------------|---------------------------------------------------------|----------------------|-------------------------|-------------------|

| Reset                     | None                                                   | None                                                    | None                 | 0                       | \$FFFE\$FFFF      |

| SWI instruction           | None                                                   | None                                                    | None                 | 0                       | \$FFFC\$FFFD      |

| IRQ pin                   | IRQF                                                   | IMASK1                                                  | IF1                  | 1                       | \$FFFA—\$FFFB     |

| CGM change in lock        | PLLF                                                   | PLLIE                                                   | IF2                  | 2                       | \$FFF8-\$FFF9     |

| TIM1 channel 0            | CH0F                                                   | CH0IE                                                   | IF3                  | 3                       | \$FFF6-\$FFF7     |

| TIM1 channel 1            | CH1F                                                   | CH1IE                                                   | IF4                  | 4                       | \$FFF4-\$FFF5     |

| TIM1 overflow             | TOF                                                    | TOIE                                                    | IF5                  | 5                       | \$FFF2\$FFF3      |

| TIM2 channel 0            | CH0F                                                   | CHOIE                                                   | IF6                  | 6                       | \$FFF0\$FFF1      |

| TIM2 channel 1            | CH1F                                                   | CH1IE                                                   | IF7                  | 7                       | \$FFEE-\$FFEF     |

| TIM2 overflow             | TOF                                                    | TOIE                                                    | IF8                  | 8                       | \$FFEC\$FFED      |

| SPI receiver full         | SPRF                                                   | SPRIE                                                   |                      |                         |                   |

| SPI overflow              | OVRF                                                   | ERRIE                                                   | IF9                  | 9                       | \$FFEA\$FFEB      |

| SPI mode fault            | MODF                                                   | ERRIE                                                   |                      |                         |                   |

| SPI transmitter empty     | SPTE                                                   | SPTIE                                                   | IF10                 | 10                      | \$FFE8\$FFE9      |

| SCI receiver overrun      | OR                                                     | ORIE                                                    |                      |                         |                   |

| SCI noise flag            | NF                                                     | NEIE                                                    |                      |                         |                   |

| SCI framing error         | FE                                                     | FEIE                                                    | IF11                 | 11                      | \$FFE6-\$FFE7     |

| SCI parity error          | PE                                                     | PEIE                                                    | •                    |                         |                   |

| SCI receiver full         | SCRF                                                   | SCRIE                                                   | 1510                 | 10                      |                   |

| SCI input idle            | IDLE                                                   | ILIE                                                    | IF12                 | 12                      | \$FFE4-\$FFE5     |

| SCI transmitter empty     | SCTE                                                   | SCTIE                                                   | 1510                 | 10                      |                   |

| SCI transmission complete | TC                                                     | TCIE                                                    | IF13                 | 13                      | \$FFE2-\$FFE3     |

| Keyboard pin              | KEYF                                                   | IMASKK                                                  | IF14                 | 14                      | \$FFE0-\$FFE1     |

| ADC conversion complete   | COCO                                                   | AIEN                                                    | IF15                 | 15                      | \$FFDE-\$FFDF     |

| Timebase                  | TBIF                                                   | TBIE                                                    | IF16                 | 16                      | \$FFDC\$FFDD      |

| MSCAN08 receiver wakeup   | WUPIF                                                  | WUPIE                                                   | IF17                 | 17                      | \$FFDA-\$FFDB     |

| MSCAN08 error             | RWRNIF<br>TWRNIF<br>RERIF<br>TERRIF<br>BOFFIF<br>OVRIF | RWRNIE<br>TWRNIE<br>RERRIE<br>TERRIE<br>BOFFIE<br>OVRIE | IF18                 | 18                      | \$FFD8–\$FFD9     |

| MSCAN08 receiver          | RXF                                                    | RXFIE                                                   | IF19                 | 19                      | \$FFD6\$FFD7      |

| MSCAN08 transmitter       | TXE2<br>TXE1<br>TXE0                                   | TXEIE2<br>TXEIE1<br>TXEIE0                              | IF20                 | 20                      | \$FFD4–\$FFD5     |

| TIM2 channel 2            | CH2F                                                   | CH2IE                                                   | IF21                 | 21                      | \$FFD2–FFD3       |

| TIM2 channel 3            | CH3F                                                   | CH3IE                                                   | IF22                 | 22                      | \$FFD0-FFD1       |

| TIM2 channel 4            | CH4F                                                   | CH4IE                                                   | IF23                 | 23                      | \$FFCE-FFCF       |

| TIM2 channel 5            | CH5F                                                   | CH5IE                                                   | IF24                 | 24                      | \$FFCC-FFCD       |

# Table 15-3. Interrupt Sources

1. The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction.

2. 0 = highest priority

#### Serial Peripheral Interface (SPI) Module

# **16.6 Error Conditions**

The following flags signal SPI error conditions:

- Overflow (OVRF) Failing to read the SPI data register before the next full byte enters the shift

register sets the OVRF bit. The new byte does not transfer to the receive data register, and the

unread byte still can be read. OVRF is in the SPI status and control register.

- Mode fault error (MODF) The MODF bit indicates that the voltage on the slave select pin (SS) is inconsistent with the mode of the SPI. MODF is in the SPI status and control register.

### 16.6.1 Overflow Error

The overflow flag (OVRF) becomes set if the receive data register still has unread data from a previous transmission when the capture strobe of bit 1 of the next transmission occurs. The bit 1 capture strobe occurs in the middle of SPSCK cycle 7 (see Figure 16-5 and Figure 16-7.) If an overflow occurs, all data received after the overflow and before the OVRF bit is cleared does not transfer to the receive data register and does not set the SPI receiver full bit (SPRF). The unread data that transferred to the receive data register before the overflow occurred can still be read. Therefore, an overflow error always indicates the loss of data. Clear the overflow flag by reading the SPI status and control register and then reading the SPI data register.

OVRF generates a receiver/error CPU interrupt request if the error interrupt enable bit (ERRIE) is also set. The SPRF, MODF, and OVRF interrupts share the same CPU interrupt vector (see Figure 16-12.) It is not possible to enable MODF or OVRF individually to generate a receiver/error CPU interrupt request. However, leaving MODFEN low prevents MODF from being set.

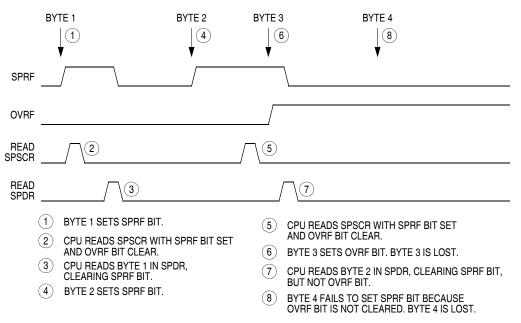

If the CPU SPRF interrupt is enabled and the OVRF interrupt is not, watch for an overflow condition. Figure 16-10 shows how it is possible to miss an overflow. The first part of Figure 16-10 shows how it is possible to read the SPSCR and SPDR to clear the SPRF without problems. However, as illustrated by the second transmission example, the OVRF bit can be set in between the time that SPSCR and SPDR are read.

Figure 16-10. Missed Read of Overflow Condition

# 18.8.2 TIM1 Counter Registers

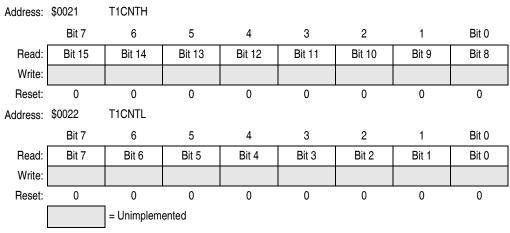

The two read-only TIM1 counter registers contain the high and low bytes of the value in the TIM1 counter. Reading the high byte (T1CNTH) latches the contents of the low byte (T1CNTL) into a buffer. Subsequent reads of T1CNTH do not affect the latched T1CNTL value until T1CNTL is read. Reset clears the TIM1 counter registers. Setting the TIM1 reset bit (TRST) also clears the TIM1 counter registers.

**NOTE** If you read T1CNTH during a break interrupt, be sure to unlatch T1CNTL by reading T1CNTL before exiting the break interrupt. Otherwise, T1CNTL retains the value latched during the break.

Figure 18-6. TIM1 Counter Registers (T1CNTH:T1CNTL)

### 18.8.3 TIM1 Counter Modulo Registers

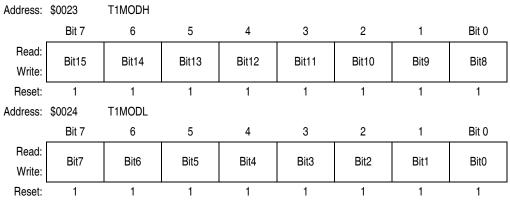

The read/write TIM1 modulo registers contain the modulo value for the TIM1 counter. When the TIM1 counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIM1 counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (T1MODH) inhibits the TOF bit and overflow interrupts until the low byte (T1MODL) is written. Reset sets the TIM1 counter modulo registers.

Figure 18-7. TIM1 Counter Modulo Registers (T1MODH:T1MODL)

NOTE

Reset the TIM1 counter before writing to the TIM1 counter modulo registers.

Timer Interface Module (TIM1)

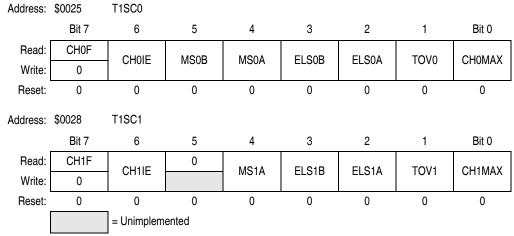

# 18.8.4 TIM1 Channel Status and Control Registers

Each of the TIM1 channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM1 overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

### Figure 18-8. TIM1 Channel Status and Control Registers (T1SC0:T1SC1)

### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM1 counter registers matches the value in the TIM1 channel x registers.

Clear CHxF by reading the TIM1 channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM1 CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

1 = Channel x CPU interrupt requests enabled

0 = Channel x CPU interrupt requests disabled

#### **Timer Interface Module (TIM2)**

| Address: | \$0033 | T2SC1      |       |       |       |       |      |               |

|----------|--------|------------|-------|-------|-------|-------|------|---------------|

|          | Bit 7  | 6          | 5     | 4     | 3     | 2     | 1    | Bit 0         |

| Read:    | CH1F   | CH1IE      | 0     | MS1A  | ELS1B | ELS1A | TOV1 | CH1MAX        |

| Write:   | 0      | OTTIL      |       |       |       | LLOIA | 1001 | OTTIVIAX      |

| Reset:   | 0      | 0          | 0     | 0     | 0     | 0     | 0    | 0             |

| Address: | \$0456 | T2SC2      |       |       |       |       |      |               |

|          | Bit 7  | 6          | 5     | 4     | 3     | 2     | 1    | Bit 0         |

| Read:    | CH2F   | CH2IE      | MS2B  | MS2A  | ELS2B | ELS2A | TOV2 | CH2MAX        |

| Write:   | 0      | UNZIE      | WIGED | WOLA  |       | LLOLA | 1012 | ONEMAX        |

| Reset:   | 0      | 0          | 0     | 0     | 0     | 0     | 0    | 0             |

| Address: | \$0459 | T2SC3      |       |       |       |       |      |               |

|          | Bit 7  | 6          | 5     | 4     | 3     | 2     | 1    | Bit 0         |

| Read:    | CH3F   | CH3IE      | 0     | MS3A  | ELS3B | ELS3A | TOV3 | <b>CH3MAX</b> |

| Write:   | 0      | ONDIE      |       | NIOOA | LLOOD | LLOOK | 1005 | ONDIVIAN      |

| Reset:   | 0      | 0          | 0     | 0     | 0     | 0     | 0    | 0             |

| Address: | \$045C | T2SC4      |       |       |       |       |      |               |

|          | Bit 7  | 6          | 5     | 4     | 3     | 2     | 1    | Bit 0         |

| Read:    | CH4F   | CH4IE      | MS4B  | MS4A  | ELS4B | ELS4A | TOV4 | CH4MAX        |

| Write:   | 0      | OTHE       | MOTE  | WO-7A |       | LLOHA | 1014 |               |

| Reset:   | 0      | 0          | 0     | 0     | 0     | 0     | 0    | 0             |

| Address: | \$045F | T2SC5      |       |       |       |       |      |               |

|          | Bit 7  | 6          | 5     | 4     | 3     | 2     | 1    | Bit 0         |

| Read:    | CH5F   | CH5IE      | 0     | MS5A  | ELS5B | ELS5A | TOV5 | CH5MAX        |

| Write:   | 0      | ONDIE      |       | NOSA  |       | LLOOK | 1005 | ONDIVIAN      |

| Reset:   | 0      | 0          | 0     | 0     | 0     | 0     | 0    | 0             |

|          |        | = Unimplem | ented |       |       |       |      |               |

# Figure 19-8. TIM2 Channel Status and Control Registers (T2SC0:T2SC5) (Continued)

### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM2 counter registers matches the value in the TIM2 channel x registers.

When CHxIE = 1, clear CHxF by reading TIM2 channel x status and control register with CHxF set, and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM2 CPU interrupts on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

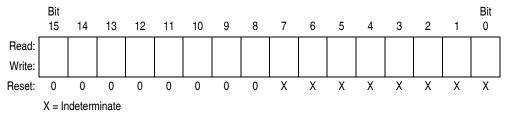

# 19.8.5 TIM2 Channel Registers

These read/write registers contain the captured TIM2 counter value of the input capture function or the output compare value of the output compare function. The state of the TIM2 channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM2 channel x registers (T2CHxH) inhibits input captures until the low byte (T2CHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM2 channel x registers (T2CHxH) inhibits output compares until the low byte (T2CHxL) is written.

| Address:        | \$0031 | T2CH0H |        |              |               |        |       |       |

|-----------------|--------|--------|--------|--------------|---------------|--------|-------|-------|

|                 | Bit 7  | 6      | 5      | 4            | 3             | 2      | 1     | Bit 0 |

| Read:<br>Write: | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11        | Bit 10 | Bit 9 | Bit 8 |

| Reset:          |        |        |        | Indeterminat | e after reset |        |       |       |

| Address:        | \$0032 | T2CH0L |        |              |               |        |       |       |

|                 | Bit 7  | 6      | 5      | 4            | 3             | 2      | 1     | Bit 0 |

| Read:<br>Write: | Bit 7  | Bit 6  | Bit 5  | Bit 4        | Bit 3         | Bit 2  | Bit 1 | Bit 0 |

| Reset:          |        |        |        | Indeterminat | e after reset |        |       |       |

| Address:        | \$0034 | T2CH1H |        |              |               |        |       |       |

|                 | Bit 7  | 6      | 5      | 4            | 3             | 2      | 1     | Bit 0 |

| Read:           | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11        | Bit 10 | Bit 9 | Bit 8 |

| Write:          | Bit 10 | DRTY   | Bit To | DRTE         | Bit II        | Bit To | Bito  | Dir o |

| Reset:          |        |        |        | Indeterminat | e after reset |        |       |       |

| Address:        | \$0035 | T2CH1L |        |              |               |        |       |       |

|                 | Bit 7  | 6      | 5      | 4            | 3             | 2      | 1     | Bit 0 |

| Read:           | Bit 7  | Bit 6  | Bit 5  | Bit 4        | Bit 3         | Bit 2  | Bit 1 | Bit 0 |

| Write:          |        | 2 0    | 20     |              |               |        | 2     | 2 0   |

| Reset:          |        |        |        | Indeterminat | e after reset |        |       |       |

| Address:        | \$0457 | T2CH2H |        |              |               |        |       |       |

|                 | Bit 7  | 6      | 5      | 4            | 3             | 2      | 1     | Bit 0 |

| Read:           | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11        | Bit 10 | Bit 9 | Bit 8 |

| Write:          | 2      |        | 2.1.10 |              |               | 2      | 2.00  | 2 0   |

| Reset:          |        |        |        | Indeterminat | e after reset |        |       |       |

| Address:        | \$0458 | T2CH2L |        |              |               |        |       |       |

|                 | Bit 7  | 6      | 5      | 4            | 3             | 2      | 1     | Bit 0 |

| Read:           | Bit 7  | Bit 6  | Bit 5  | Bit 4        | Bit 3         | Bit 2  | Bit 1 | Bit 0 |

| Write:          |        | Diro   | 5.0    |              |               |        |       |       |

| Reset:          |        |        |        | Indeterminat | e after reset |        |       |       |

Figure 19-10. TIM2 Channel Registers (T2CH0H/L:T2CH5H/L)

**Electrical Specifications**

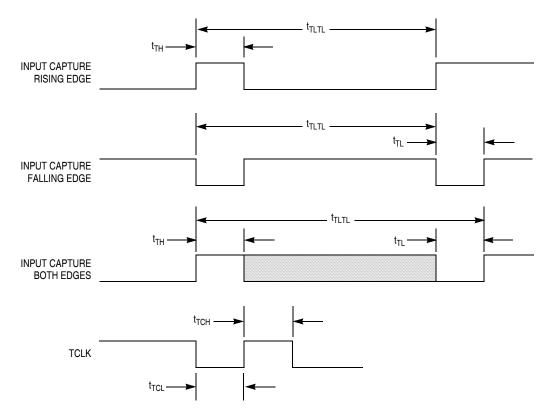

# 21.14 Timer Interface Module Characteristics

| Characteristic                  | Symbol                              | Min                  | Max | Unit             |

|---------------------------------|-------------------------------------|----------------------|-----|------------------|

| Timer input capture pulse width | t <sub>TH,</sub> t <sub>TL</sub>    | 2                    | _   | t <sub>cyc</sub> |

| Timer input capture period      | t <sub>TLTL</sub>                   | Note <sup>(1)</sup>  | _   | t <sub>cyc</sub> |

| Timer input clock pulse width   | t <sub>TCL</sub> , t <sub>TCH</sub> | t <sub>cyc</sub> + 5 | _   | ns               |

1. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 21-4. Timer Input Timing