Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb002-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                            | PIC24FJ32GB002                                                                                                                                      | PIC24FJ64GB002        | PIC24FJ32GB004    | PIC24FJ64GB004 |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|----------------|--|--|--|

| Operating Frequency                                 |                                                                                                                                                     | DC – 32 MHz           |                   |                |  |  |  |

| Program Memory (bytes)                              | 32K 64K                                                                                                                                             |                       | 32K               | 64K            |  |  |  |

| Program Memory (instructions)                       | 11,008                                                                                                                                              | 22,016                | 11,008            | 22,016         |  |  |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 8,1                   | 92                |                |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)      |                                                                                                                                                     | 45 (4                 | 1/4)              |                |  |  |  |

| I/O Ports                                           | Ports A                                                                                                                                             | and B                 | Ports A           | А, В, С        |  |  |  |

| Total I/O Pins                                      | 1                                                                                                                                                   | 9                     | 3                 | 3              |  |  |  |

| Remappable Pins                                     | 1                                                                                                                                                   | 5                     | 2                 | 5              |  |  |  |

| Timers:                                             |                                                                                                                                                     |                       | ·                 |                |  |  |  |

| Total Number (16-bit)                               |                                                                                                                                                     | 5(*                   | 1)                |                |  |  |  |

| 32-Bit (from paired 16-bit timers)                  | 2                                                                                                                                                   |                       |                   |                |  |  |  |

| Input Capture Channels                              | 5 <sup>(1)</sup>                                                                                                                                    |                       |                   |                |  |  |  |

| Output Compare/PWM Channels                         | 5 <sup>(1)</sup>                                                                                                                                    |                       |                   |                |  |  |  |

| Input Change Notification Interrupt                 | 1                                                                                                                                                   | 9                     | 29                |                |  |  |  |

| Serial Communications:                              |                                                                                                                                                     |                       |                   |                |  |  |  |

| UART                                                |                                                                                                                                                     | 2(                    |                   |                |  |  |  |

| SPI (3-wire/4-wire)                                 | 2 <sup>(1)</sup>                                                                                                                                    |                       |                   |                |  |  |  |

| I <sup>2</sup> C™                                   | 2                                                                                                                                                   |                       |                   |                |  |  |  |

| Parallel Communications (PMP/PSP)                   | Yes                                                                                                                                                 |                       |                   |                |  |  |  |

| JTAG Boundary Scan                                  | Yes                                                                                                                                                 |                       |                   |                |  |  |  |

| 10-Bit Analog-to-Digital Module<br>(input channels) | ç                                                                                                                                                   | )                     | 13                |                |  |  |  |

| Analog Comparators                                  | 3                                                                                                                                                   |                       |                   |                |  |  |  |

| CTMU Interface                                      | Yes                                                                                                                                                 |                       |                   |                |  |  |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                       |                   |                |  |  |  |

| Instruction Set                                     | 76 Base I                                                                                                                                           | nstructions, Multiple | Addressing Mode V | ariations      |  |  |  |

| Packages                                            | 28-Pin QFN, SOIC,                                                                                                                                   | SSOP and SPDIP        | 44-Pin QFN        | l and TQFP     |  |  |  |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ64GB004 FAMILY

**Note 1:** Peripherals are accessible through remappable pins.

|          | Р                             | in Numbe                             | r  |                     |                  |                                                       |  |  |  |

|----------|-------------------------------|--------------------------------------|----|---------------------|------------------|-------------------------------------------------------|--|--|--|

| Function | 28-Pin<br>SPDIP/<br>SOIC/SSOP | SPDIP/ 28-Pin 44-Pin<br>OFN OFN/TOFP |    | I/O Input<br>Buffer |                  | Description                                           |  |  |  |

| AN0      | 2                             | 27                                   | 19 | Ι                   | ANA              | A/D Analog Inputs.                                    |  |  |  |

| AN1      | 3                             | 28                                   | 20 | I                   | ANA              |                                                       |  |  |  |

| AN2      | 4                             | 1                                    | 21 | I                   | ANA              |                                                       |  |  |  |

| AN3      | 5                             | 2                                    | 22 | Ι                   | ANA              |                                                       |  |  |  |

| AN4      | 6                             | 3                                    | 23 | I                   | ANA              |                                                       |  |  |  |

| AN5      | 7                             | 4                                    | 24 | I                   | ANA              |                                                       |  |  |  |

| AN6      | _                             |                                      | 25 | I                   | ANA              |                                                       |  |  |  |

| AN7      | _                             |                                      | 26 | I                   | ANA              |                                                       |  |  |  |

| AN8      | _                             |                                      | 27 | Ι                   | ANA              |                                                       |  |  |  |

| AN9      | 26                            | 23                                   | 15 | I                   | ANA              |                                                       |  |  |  |

| AN10     | 25                            | 22                                   | 14 | Ι                   | ANA              |                                                       |  |  |  |

| AN11     | 24                            | 21                                   | 11 | I                   | ANA              |                                                       |  |  |  |

| AN12     | _                             | _                                    | 36 | I                   | ANA              |                                                       |  |  |  |

| ASCL1    | 3                             | 28                                   | 20 | I/O                 | l <sup>2</sup> C | Alternate I2C1 Synchronous Serial Clock Input/Output. |  |  |  |

| ASDA1    | 2                             | 27                                   | 19 | I/O                 | l <sup>2</sup> C | Alternate I2C1 Synchronous Serial Data Input/Output.  |  |  |  |

| AVdd     | _                             |                                      | 17 | Р                   | —                | Positive Supply for Analog modules.                   |  |  |  |

| AVss     | —                             | _                                    | 16 | Р                   | —                | Ground Reference for Analog modules.                  |  |  |  |

| C1INA    | 7                             | 4                                    | 24 | Ι                   | ANA              | Comparator 1 Input A.                                 |  |  |  |

| C1INB    | 6                             | 3                                    | 23 | Ι                   | ANA              | Comparator 1 Input B.                                 |  |  |  |

| C1INC    | 24                            | 21                                   | 11 | Ι                   | ANA              | Comparator 1 Input C.                                 |  |  |  |

| C1IND    | 9                             | 6                                    | 30 | Ι                   | ANA              | Comparator 1 Input D.                                 |  |  |  |

| C2INA    | 5                             | 2                                    | 22 | Ι                   | ANA              | Comparator 2 Input A.                                 |  |  |  |

| C2INB    | 4                             | 1                                    | 21 | Ι                   | ANA              | Comparator 2 Input B.                                 |  |  |  |

| C2INC    | 12                            | 9                                    | 34 | I                   | ANA              | Comparator 2 Input C.                                 |  |  |  |

| C2IND    | 11                            | 8                                    | 33 | Ι                   | ANA              | Comparator 2 Input D.                                 |  |  |  |

| C3INA    | 26                            | 23                                   | 15 | Ι                   | ANA              | Comparator 3 Input A.                                 |  |  |  |

| C3INB    | 25                            | 22                                   | 14 | I                   | ANA              | Comparator 3 Input B.                                 |  |  |  |

| C3INC    | 2                             | 27                                   | 19 | Ι                   | ANA              | Comparator 3 Input C.                                 |  |  |  |

| C3IND    | 3                             | 28                                   | 20 | I                   | ANA              | Comparator 3 Input D.                                 |  |  |  |

| CLKI     | 9                             | 6                                    | 30 | I                   | ANA              | Main Clock Input Connection.                          |  |  |  |

| CLKO     | 10                            | 7                                    | 31 | 0                   | —                | System Clock Output.                                  |  |  |  |

| TABLE 1-2: | PIC24FJ64GB004 FAMILY PINOUT DESCRIPTIONS |

|------------|-------------------------------------------|

| IADLL I-2. |                                           |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer

$I^2C^{TM} = I^2C/SMBus$  input buffer

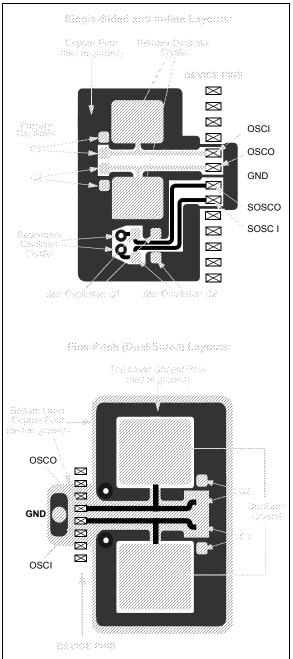

#### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### 3.0 CPU

| Note: | This data sheet summarizes the features    |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |

|       | Section 2. "CPU" (DS39703).                |  |  |  |  |  |

The PIC24F CPU has a 16-bit (data), modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

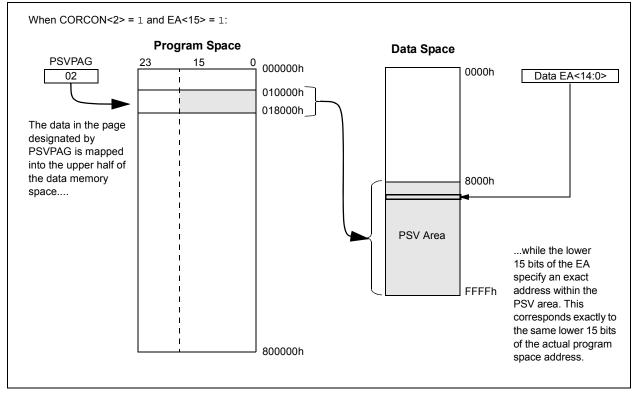

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported either directly or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

### 3.1 Programmer's Model

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory mapped.

#### TABLE 4-3: CPU CORE REGISTERS MAP

| IADLE        | 4-3. | CFU CORE REGISTERS MAP |                      |        |        |        |        |        |             |              |           |            |                |              |             |       |       |               |

|--------------|------|------------------------|----------------------|--------|--------|--------|--------|--------|-------------|--------------|-----------|------------|----------------|--------------|-------------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15                 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6     | Bit 5      | Bit 4          | Bit 3        | Bit 2       | Bit 1 | Bit 0 | All<br>Resets |

| WREG0        | 0000 |                        | Working Register 0   |        |        |        |        |        |             |              | 0000      |            |                |              |             |       |       |               |

| WREG1        | 0002 |                        |                      |        |        |        |        |        | Working I   | Register 1   |           |            |                |              |             |       |       | 0000          |

| WREG2        | 0004 |                        |                      |        |        |        |        |        | Working I   | Register 2   |           |            |                |              |             |       |       | 0000          |

| WREG3        | 0006 |                        |                      |        |        |        |        |        | Working I   | Register 3   |           |            |                |              |             |       |       | 0000          |

| WREG4        | 0008 |                        |                      |        |        |        |        |        | Working I   | Register 4   |           |            |                |              |             |       |       | 0000          |

| WREG5        | 000A |                        |                      |        |        |        |        |        | Working I   | Register 5   |           |            |                |              |             |       |       | 0000          |

| WREG6        | 000C |                        |                      |        |        |        |        |        | Working I   | Register 6   |           |            |                |              |             |       |       | 0000          |

| WREG7        | 000E |                        |                      |        |        |        |        |        | Working I   | Register 7   |           |            |                |              |             |       |       | 0000          |

| WREG8        | 0010 |                        |                      |        |        |        |        |        | Working I   | Register 8   |           |            |                |              |             |       |       | 0000          |

| WREG9        | 0012 |                        | Working Register 9 0 |        |        |        |        |        | 0000        |              |           |            |                |              |             |       |       |               |

| WREG10       | 0014 |                        |                      |        |        |        |        |        | Working F   | egister 10   |           |            |                |              |             |       |       | 0000          |

| WREG11       | 0016 |                        |                      |        |        |        |        |        | Working F   | Register 11  |           |            |                |              |             |       |       | 0000          |

| WREG12       | 0018 |                        |                      |        |        |        |        |        | Working R   | legister 12  |           |            |                |              |             |       |       | 0000          |

| WREG13       | 001A |                        | Working Register 13  |        |        |        |        |        | 0000        |              |           |            |                |              |             |       |       |               |

| WREG14       | 001C |                        |                      |        |        |        |        |        | Working F   | egister 14   |           |            |                |              |             |       |       | 0000          |

| WREG15       | 001E |                        |                      |        |        |        |        |        | Working F   | egister 15   |           |            |                |              |             |       |       | 0800          |

| SPLIM        | 0020 |                        |                      |        |        |        |        | Stack  | Pointer Lin | nit Value Re | gister    |            |                |              |             |       |       | xxxx          |

| PCL          | 002E |                        |                      |        |        |        |        | Progra | m Counter I | ow Word F    | Register  |            |                |              |             |       |       | 0000          |

| PCH          | 0030 | —                      | —                    | —      | —      | —      | —      | —      | —           |              |           | Progra     | m Counter      | Register Hig | gh Byte     |       |       | 0000          |

| TBLPAG       | 0032 | -                      | —                    | —      | —      | —      | -      | —      | —           |              |           | Table N    | lemory Pag     | e Address F  | Register    |       |       | 0000          |

| PSVPAG       | 0034 | _                      |                      | —      | —      | —      | _      | _      | —           |              | Р         | rogram Spa | ace Visibility | / Page Addr  | ress Regist | er    |       | 0000          |

| RCOUNT       | 0036 |                        |                      |        |        |        |        | Rep    | eat Loop C  | ounter Regi  | ster      |            |                |              |             |       |       | xxxx          |

| SR           | 0042 | _                      | —                    | —      | —      | —      | —      | —      | DC          | IPL2         | IPL1      | IPL0       | RA             | Ν            | OV          | Z     | С     | 0000          |

| CORCON       | 0044 | _                      |                      | —      | _      | _      | _      | —      | —           | _            | —         | —          | —              | IPL3         | PSV         | _     | _     | 0000          |

| DISICNT      | 0052 | _                      | —                    |        |        |        |        |        | Disabl      | e Interrupts | Counter R | egister    |                | •            |             |       |       | xxxx          |

|              |      |                        |                      |        |        |        |        |        |             |              |           |            |                |              |             |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit (MSb) of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the CPU Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

### Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

#### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

#### 5.6.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOP bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit (see Example 5-7).

#### EXAMPLE 5-7: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY – ASSEMBLY LANGUAGE CODE

| MOV<br>MOV                       | pointer to data Program Memory<br>#tblpage(PROG_ADDR), W0<br>W0, TBLPAG<br>#tbloffset(PROG_ADDR), W0 | ;<br>;Initialize PM Page Boundary SFR<br>;Initialize a register with program memory address        |

|----------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| MOV<br>TBLWTL                    | w2, [w0]                                                                                             | ;<br>;<br>; Write PM low word into program latch                                                   |

| ; Setup NVI<br>MOV               | W3, [W0++]<br>MCON for programming one word t<br>#0x4003, W0<br>W0, NVMCON                           | ; Write PM high byte into program latch<br>to data Program Memory<br>;<br>; Set NVMOP bits to 0011 |

| DISI<br>MOV<br>MOV               | #5<br>#0x55, W0<br>W0, NVMKEY                                                                        | ; Disable interrupts while the KEY sequence is written<br>; Write the key sequence                 |

| MOV<br>MOV<br>BSET<br>NOP<br>NOP | #0xAA, W0<br>W0, NVMKEY<br>NVMCON, #WR                                                               | ; Start the write cycle<br>; Insert two NOPs after the erase<br>; Command is asserted              |

#### EXAMPLE 5-8: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

unsigned int offset;

unsigned long progAddr = 0xXXXXXX;

// Address of word to program

unsigned int progDataL = 0xXXXX;

// Data to program lower word

// Data to program upper byte

unsigned char progDataH = 0xXX;

//Set up NVMCON for word programming

NVMCON = 0x4003;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

// Initialize PM Page Boundary SFR

TBLPAG = progAddr>>16;

offset = progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write latches

__builtin_tblwtl(offset, progDataL); // Write to address low

__builtin_tblwth(offset, progDataH); // Write to upper byte

// Write to address low word

asm("DISI #5");

// Block interrupts with priority < 7</pre>

// for next 5 instructions

__builtin_write_NVM();

// C30 function to perform unlock

// sequence and set WR

```

| U-0                    | U-0                                                                                | R/W-0                              | R/W-0            | R/W-0                            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------|------------------------------------|------------------|----------------------------------|------------------|-----------------|--------|--|--|--|--|

| —                      | —                                                                                  | AD1IF                              | U1TXIF           | U1RXIF                           | SPI1IF           | SPF1IF          | T3IF   |  |  |  |  |

| bit 15                 |                                                                                    |                                    |                  |                                  |                  |                 | bit 8  |  |  |  |  |

|                        |                                                                                    |                                    |                  |                                  |                  |                 |        |  |  |  |  |

| R/W-0                  | R/W-0                                                                              | R/W-0                              | U-0              | R/W-0                            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| T2IF                   | OC2IF                                                                              | IC2IF                              | <u> </u>         | T1IF                             | OC1IF            | IC1IF           | INT0IF |  |  |  |  |

| bit 7                  |                                                                                    |                                    |                  |                                  |                  |                 | bit C  |  |  |  |  |

|                        |                                                                                    |                                    |                  |                                  |                  |                 |        |  |  |  |  |

| Legend:<br>R = Readabl | a hit                                                                              | $\lambda = \lambda / ritabla$      | h:t              |                                  | antad hit raa    | d oo 'O'        |        |  |  |  |  |

| -n = Value at          |                                                                                    | W = Writable<br>'1' = Bit is se    |                  | 0 = Onimpien<br>0' = Bit is clea | nented bit, read | x = Bit is unkn |        |  |  |  |  |

|                        | FUR                                                                                | I – DILISSE                        | L                |                                  | areu             |                 | IOWIT  |  |  |  |  |

| bit 15-14              | Unimplemen                                                                         | ted: Read as                       | °0'              |                                  |                  |                 |        |  |  |  |  |

| bit 13                 | -                                                                                  |                                    |                  | t Flag Status bit                | t                |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        | 0 = Interrupt                                                                      | request has no                     | t occurred       |                                  |                  |                 |        |  |  |  |  |

| bit 12                 |                                                                                    |                                    | r Interrupt Flag | Status bit                       |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 11                 | •                                                                                  | request has no<br>PT1 Receiver I   | nterrupt Flag S  | tatus bit                        |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has no                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 10                 | SPI1IF: SPI1                                                                       | Event Interrup                     | ot Flag Status b | it                               |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        | •                                                                                  | request has no                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 9                  | SPF1IF: SPI1 Fault Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                    |                  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc<br>request has no   |                  |                                  |                  |                 |        |  |  |  |  |

| bit 8                  | •                                                                                  | Interrupt Flag                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has no                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 7                  |                                                                                    | Interrupt Flag                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

| L:1 0                  | •                                                                                  | request has no                     |                  |                                  | - 14             |                 |        |  |  |  |  |

| bit 6                  |                                                                                    | ut Compare Cr<br>request has oc    |                  | pt Flag Status t                 | DIT              |                 |        |  |  |  |  |

|                        |                                                                                    | request has no                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 5                  | •                                                                                  | •                                  | el 2 Interrupt F | lag Status bit                   |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  | •                                |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has no                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 4                  | -                                                                                  | nted: Read as                      |                  |                                  |                  |                 |        |  |  |  |  |

| bit 3                  |                                                                                    | Interrupt Flag                     |                  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc<br>request has no   |                  |                                  |                  |                 |        |  |  |  |  |

| bit 2                  | •                                                                                  | •                                  |                  | pt Flag Status t                 | oit              |                 |        |  |  |  |  |

| 5112                   | -                                                                                  | request has oc                     |                  | prindy oldido .                  |                  |                 |        |  |  |  |  |

|                        | 0 = Interrupt                                                                      | request has no                     | t occurred       |                                  |                  |                 |        |  |  |  |  |

| bit 1                  | IC1IF: Input (                                                                     | Capture Chann                      | el 1 Interrupt F | lag Status bit                   |                  |                 |        |  |  |  |  |

|                        |                                                                                    | request has oc                     |                  |                                  |                  |                 |        |  |  |  |  |

| hit O                  | -                                                                                  | request has no                     |                  |                                  |                  |                 |        |  |  |  |  |

| bit 0                  |                                                                                    | rnal Interrupt 0<br>request has oc | Flag Status bit  |                                  |                  |                 |        |  |  |  |  |

|                        |                                                                                    |                                    |                  |                                  |                  |                 |        |  |  |  |  |

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0                                                     | U-0           | U-0                                                      | U-0              | U-0              | U-0              | U-0                | U-0     |  |  |  |  |

|---------------------------------------------------------|---------------|----------------------------------------------------------|------------------|------------------|------------------|--------------------|---------|--|--|--|--|

| —                                                       | —             |                                                          |                  | _                | _                | —                  | —       |  |  |  |  |

| bit 15                                                  |               |                                                          |                  |                  |                  |                    | bit 8   |  |  |  |  |

|                                                         |               |                                                          |                  |                  |                  |                    |         |  |  |  |  |

| U-0                                                     | R/W-1         | R/W-0                                                    | R/W-0            | U-0              | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |

| _                                                       | SPI2IP2       | SPI2IP1                                                  | SPI2IP0          | —                | SPF2IP2          | SPF2IP1            | SPF2IP0 |  |  |  |  |

| bit 7                                                   |               |                                                          |                  |                  | ·                |                    | bit 0   |  |  |  |  |

|                                                         |               |                                                          |                  |                  |                  |                    |         |  |  |  |  |

| Legend:                                                 |               |                                                          |                  |                  |                  |                    |         |  |  |  |  |

| R = Readal                                              | ole bit       | W = Writable                                             | bit              | U = Unimpler     | mented bit, read | d as '0'           |         |  |  |  |  |

| -n = Value a                                            | at POR        | '1' = Bit is set                                         |                  | '0' = Bit is cle | ared             | x = Bit is unknown |         |  |  |  |  |

|                                                         |               |                                                          |                  |                  |                  |                    |         |  |  |  |  |

| bit 15-7                                                | Unimplemen    | ted: Read as '                                           | 0'               |                  |                  |                    |         |  |  |  |  |

| bit 6-4                                                 | SPI2IP<2:0>:  | SPI2 Event In                                            | terrupt Priority | bits             |                  |                    |         |  |  |  |  |

|                                                         | 111 = Interru | I = Interrupt is Priority 7 (highest priority interrupt) |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | •             |                                                          |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | •             |                                                          |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | 001 = Interru | pt is Priority 1                                         |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | 000 = Interru | pt source is dis                                         | abled            |                  |                  |                    |         |  |  |  |  |

| bit 3                                                   | Unimplemen    | ted: Read as '                                           | 0'               |                  |                  |                    |         |  |  |  |  |

| bit 2-0 SPF2IP<2:0>: SPI2 Fault Interrupt Priority bits |               |                                                          |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | 111 = Interru | pt is Priority 7(                                        | highest priority | interrupt)       |                  |                    |         |  |  |  |  |

|                                                         | •             |                                                          |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | •             |                                                          |                  |                  |                  |                    |         |  |  |  |  |

|                                                         | 001 = Interru | pt is Priority 1                                         |                  |                  |                  |                    |         |  |  |  |  |

|                                                         |               | pt source is dis                                         | abled            |                  |                  |                    |         |  |  |  |  |

|                                                         |               |                                                          |                  |                  |                  |                    |         |  |  |  |  |

#### REGISTER 7-25: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

#### 13.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are modules 3 and 4, and so on.) The odd-numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even module (ICy) provides the Most Significant 16 bits. Wrap-arounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

### 13.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx, or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the sync source before proceeding.

- Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSEL bits (ICxCON2<4:0>) to the desired sync/trigger source.

- Set the ICTSEL bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSEL bits before the Input Capture module is enabled for proper synchronization with the desired clock source.

- 6. Set the ICI bits (ICxCON1<6:5>) to the desired interrupt frequency

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSEL bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICM bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected trigger/sync source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even-numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSEL and SYNCSEL bits for both modules to select the same sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSEL and SYNCSEL settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>); this forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICI bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the sync source as the last step. Both input capture modules are held in Reset until the sync source is enabled.

- Use the ICM bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the trigger/sync source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the lsw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (perform automatically by hardware).

#### 14.4 Subcycle Resolution

The DCB bits (OCxCON2<10:9>) provide for resolution better than one instruction cycle. When used, they delay the falling edge generated by a match event by a portion of an instruction cycle.

For example, setting DCB<1:0> = 10 causes the falling edge to occur half way through the instruction cycle in which the match event occurs, instead of at the beginning. These bits cannot be used when OCM<2:0> = 001. When operating the module in PWM mode (OCM<2:0> = 110 or 111), the DCB bits will be double-buffered. The DCB bits are intended for use with a clock source identical to the system clock. When an OCx module with enabled prescaler is used, the falling edge delay caused by the DCB bits will be referenced to the system clock period, rather than the OCx module's period.

| <b>TABLE 14-1</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz) <sup>(1)</sup> |

|---------------------|--------------------------------------------------------------------------------|

|---------------------|--------------------------------------------------------------------------------|

| PWM Frequency     | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-------------------|--------|-------|--------|--------|---------|----------|---------|

| Prescaler Ratio   | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Value      | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits) | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

| <b>TABLE 14-2:</b> | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz) <sup>(1)</sup> |

|--------------------|----------------------------------------------------------------------------------|

|                    |                                                                                  |

| PWM Frequency     | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-------------------|---------|--------|--------|---------|----------|---------|---------|

| Prescaler Ratio   | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Value      | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits) | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

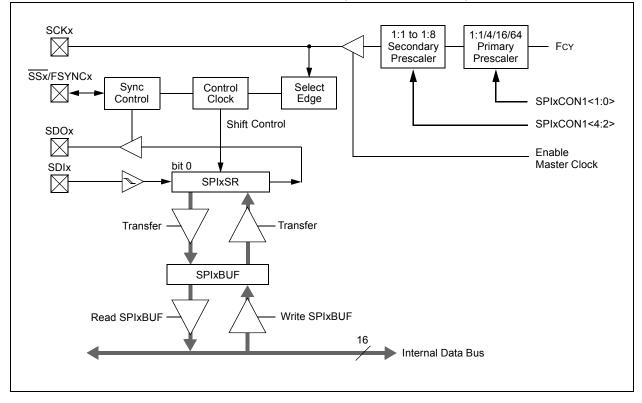

To set up the SPI module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1<8>) is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

#### FIGURE 15-1: SPIX MODULE BLOCK DIAGRAM (STANDARD MODE)

#### 18.3 USB Interrupts

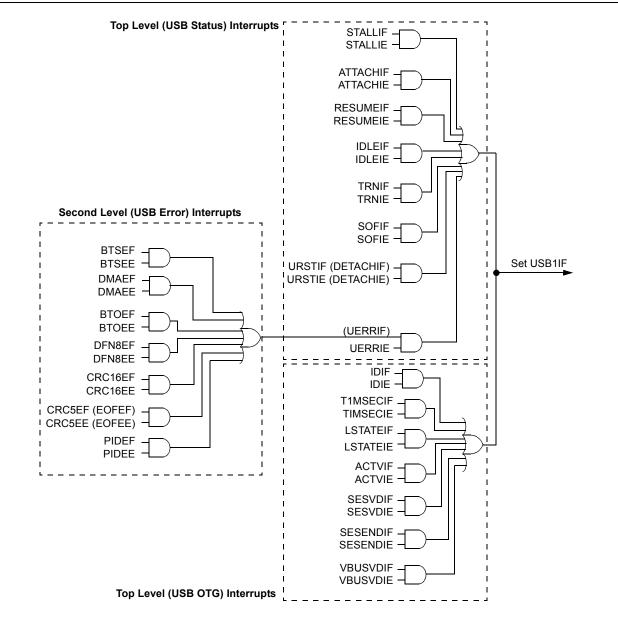

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 18-9 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second

#### FIGURE 18-9: USB OTG INTERRUPT FUNNEL

level consists of USB error conditions, which are enabled and flagged in the U1EIR and U1EIE registers. An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level.

Interrupts may be used to trap routine events in a USB transaction. Figure 18-10 provides some common events within a USB frame and their corresponding interrupts.

#### 18.7.2 USB INTERRUPT REGISTERS

#### REGISTER 18-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                            |                    |  |  |  |

|-------------------|------------------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit         | HS = Hardware Settable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                               |

|          | 1 = Change in ID state is detected                                                                                                |

|          | 0 = No ID state change                                                                                                            |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                 |

|          | 1 = The 1 millisecond timer has expired                                                                                           |

|          | 0 = The 1 millisecond timer has not expired                                                                                       |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                         |

|          | 1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different<br>from last time              |

|          | 0 = USB line state has not been stable for 1 ms                                                                                   |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                               |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                            |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                       |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup>                                         |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                              |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                      |

|          | 1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup>    |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                              |

| bit 1    | Unimplemented: Read as '0'                                                                                                        |

| bit 0    | VBUSVDIF A-Device VBUS Change Indicator bit                                                                                       |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the USB<br>OTG Specification) <sup>(1)</sup> |

|          | 0 = No VBUS change on A-device is detected                                                                                        |

| Note 1:  | VBUS threshold crossings may be either rising or falling.                                                                         |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits at the moment of the write to become cleared.

| R/W-0        | R/W-0                                      | R/W-0                         | R/W-0           | R/W-0             | R/W-0                        | R/W-0            | R/W-0         |  |  |  |  |

|--------------|--------------------------------------------|-------------------------------|-----------------|-------------------|------------------------------|------------------|---------------|--|--|--|--|

| ALRMEN       | CHIME                                      | AMASK3                        | AMASK2          | AMASK1            | AMASK0                       | ALRMPTR1         | ALRMPTR0      |  |  |  |  |

| bit 15       |                                            | *                             | •               |                   |                              | *                | bit 8         |  |  |  |  |

|              |                                            |                               |                 |                   |                              |                  |               |  |  |  |  |

| R/W-0        | R/W-0                                      | R/W-0                         | R/W-0           | R/W-0             | R/W-0                        | R/W-0            | R/W-0         |  |  |  |  |

| ARPT7        | ARPT6                                      | ARPT5                         | ARPT4           | ARPT3             | ARPT2                        | ARPT1            | ARPT0         |  |  |  |  |

| bit 7        |                                            |                               |                 |                   |                              |                  | bit           |  |  |  |  |

| Legend:      |                                            |                               |                 |                   |                              |                  |               |  |  |  |  |

| R = Readab   | le bit                                     | W = Writable                  | bit             | U = Unimplen      | nented bit, rea              | d as '0'         |               |  |  |  |  |

| -n = Value a |                                            | '1' = Bit is set              |                 | '0' = Bit is clea |                              | x = Bit is unkr  | nown          |  |  |  |  |

|              |                                            |                               |                 |                   |                              |                  |               |  |  |  |  |

| bit 15       | ALRMEN: AI                                 | arm Enable bit                |                 |                   |                              |                  |               |  |  |  |  |

|              |                                            |                               | ed automatical  | ly after an ala   | arm event whe                | never ARPT<7     | :0> = 00h and |  |  |  |  |

|              | CHIME =                                    | ,                             |                 |                   |                              |                  |               |  |  |  |  |

| L:1 4 4      | 0 = Alarm is                               |                               |                 |                   |                              |                  |               |  |  |  |  |

| bit 14       | CHIME: Chim                                |                               | T-7.0> hito oro | allowed to roll   | over from 00h                |                  |               |  |  |  |  |

|              |                                            | enabled; ARP<br>disabled; ARP |                 |                   |                              |                  |               |  |  |  |  |

| bit 13-10    |                                            | >: Alarm Mask                 |                 |                   |                              |                  |               |  |  |  |  |

|              |                                            | ry half second                | oonngaration s  | 10                |                              |                  |               |  |  |  |  |

|              | 0001 = Eve                                 |                               |                 |                   |                              |                  |               |  |  |  |  |

|              | 0010 = Every 10 seconds                    |                               |                 |                   |                              |                  |               |  |  |  |  |

|              | 0011 = Every minute                        |                               |                 |                   |                              |                  |               |  |  |  |  |

|              | 0100 = Eve<br>0101 = Eve                   | ry 10 minutes                 |                 |                   |                              |                  |               |  |  |  |  |

|              | 0110 = Onc                                 |                               |                 |                   |                              |                  |               |  |  |  |  |

|              | 0111 = Onc                                 |                               |                 |                   |                              |                  |               |  |  |  |  |

|              | 1000 = Onc                                 |                               |                 |                   |                              |                  |               |  |  |  |  |

|              |                                            | e a year (excep               |                 | red for Februa    | ry 29 <sup>th</sup> , once e | very 4 years)    |               |  |  |  |  |

|              |                                            | erved; do not u               |                 |                   |                              |                  |               |  |  |  |  |

| bit 9-8      |                                            | erved; do not u               |                 | dow Dointor h     | ito                          |                  |               |  |  |  |  |

| DIL 9-0      |                                            | :0>: Alarm Val                | •               |                   |                              | VVALH and ALF    |               |  |  |  |  |

|              |                                            |                               |                 |                   |                              | MVALH until it n |               |  |  |  |  |

|              | ALRMVAL<1                                  |                               |                 |                   |                              |                  |               |  |  |  |  |

|              | 00 <b>= ALRMM</b>                          | lin                           |                 |                   |                              |                  |               |  |  |  |  |

|              | 01 = ALRMW                                 |                               |                 |                   |                              |                  |               |  |  |  |  |