Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb002-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 28/44-Pin, 16-Bit, Flash Microcontrollers with USB On-The-Go (OTG) and nanoWatt XLP Technology

### **Universal Serial Bus Features:**

- USB v2.0 On-The-Go (OTG) Compliant

- Dual Role Capable can act as either Host or Peripheral

Low-Speed (1.5 Mb/s) and Full-Speed (12 Mb/s) USB Operation in Host mode

- Full-Speed USB Operation in Device mode

- High-Precision PLL for USB

- 0.25% Accuracy using Internal Oscillator No External Crystal Required

- Internal Voltage Boost Assist for USB Bus Voltage Generation

- Interface for Off-Chip Charge Pump for USB Bus

Voltage Generation

- Supports up to 32 Endpoints (16 bidirectional):

- USB module can use any RAM location on the device as USB endpoint buffers

- On-Chip USB Transceiver

- Interface for Off-Chip USB Transceiver

- Supports Control, Interrupt, Isochronous and Bulk Transfers

- · On-Chip Pull-up and Pull-Down Resistors

### **High-Performance CPU:**

- Modified Harvard Architecture

- Up to 16 MIPS Operation @ 32 MHz

- 8 MHz Internal Oscillator with 0.25% Typical Accuracy:

- 96 MHz PLL

- Multiple divide options

- 17-Bit x 17-Bit Single-Cycle Hardware Fractional/integer Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- C Compiler Optimized Instruction Set Architecture:

- 76 base instructions

- Flexible addressing modes

- · Linear Program Memory Addressing up to 12 Mbytes

- Linear Data Memory Addressing up to 64 Kbytes

- Two Address Generation Units for Separate Read and Write Addressing of Data Memory

#### **Power Management Modes:**

- Selectable Power Management modes with nanoWatt XLP Technology for Extremely Low Power:

- Deep Sleep mode allows near total power-down (20 nA typical and 500 nA with RTCC or WDT), along with the ability to wake-up on external triggers or self-wake on programmable WDT or RTCC alarm

- Extreme low-power DSBOR for Deep Sleep, LPBOR for all other modes

- Sleep mode shuts down peripherals and core for substantial power reduction, fast wake-up

- Idle mode shuts down the CPU and peripherals for significant power reduction, down to 4.5 μA typical

- Doze mode enables CPU clock to run slower than peripherals

- Alternate Clock modes allow on-the-fly switching to a lower clock speed for selective power reduction during Run mode down to 15 μA typical

#### **Special Microcontroller Features:**

- Operating Voltage Range of 2.0V to 3.6V

- Self-Reprogrammable under Software Control

- 5.5V Tolerant Input (digital pins only)

- · High-Current Sink/Source (18 mA/18 mA) on All I/O Pins

- Flash Program Memory:

- 10,000 erase/write cycle endurance (minimum)

- 20-year data retention minimum

- Selectable write protection boundary

- Fail-Safe Clock Monitor Operation:

- Detects clock failure and switches to on-chip FRC oscillator

- On-Chip 2.5V Regulator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Two Flexible Watchdog Timers (WDT) for Reliable Operation:

- Standard programmable WDT for normal operation

Extreme low-power WDT with programmable

- period of 2 ms to 26 days for Deep Sleep mode • In-Circuit Serial Programming™ (ICSP™) and In-Circuit Debug (ICD) via 2 Pins

- JTAG Boundary Scan Support

|                   |      | <u>ک</u>                |                 | Remappable Peripherals |                  |                  |                       |                  |     |      |                    |             |         |      |      |         |

|-------------------|------|-------------------------|-----------------|------------------------|------------------|------------------|-----------------------|------------------|-----|------|--------------------|-------------|---------|------|------|---------|

| PIC24FJ<br>Device | Pins | Program Memo<br>(Bytes) | SRAM<br>(Bytes) | Remappable<br>Pins     | Timers<br>16-Bit | Capture<br>Input | Compare/PWM<br>Output | UART w/<br>IrDA® | IdS | I²C™ | 10-Bit A/D<br>(ch) | Comparators | PMP/PSP | RTCC | CTMU | USB OTG |

| 32GB002           | 28   | 32K                     | 8K              | 15                     | 5                | 5                | 5                     | 2                | 2   | 2    | 9                  | 3           | Y       | Y    | Y    | Y       |

| 64GB002           | 28   | 64K                     | 8K              | 15                     | 5                | 5                | 5                     | 2                | 2   | 2    | 9                  | 3           | Y       | Y    | Y    | Y       |

| 32GB004           | 44   | 32K                     | 8K              | 25                     | 5                | 5                | 5                     | 2                | 2   | 2    | 13                 | 3           | Y       | Y    | Y    | Y       |

| 64GB004           | 44   | 64K                     | 8K              | 25                     | 5                | 5                | 5                     | 2                | 2   | 2    | 13                 | 3           | Y       | Y    | Y    | Y       |

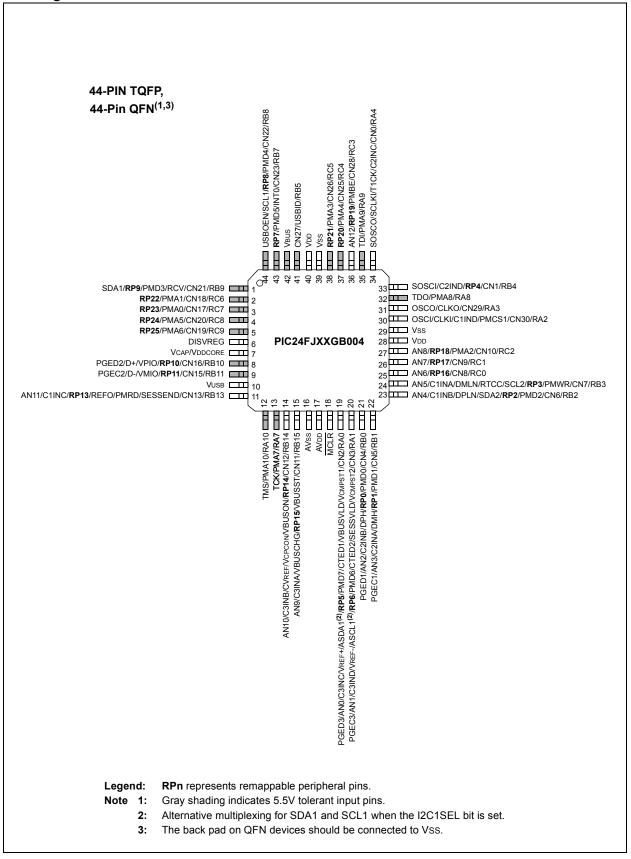

### **Pin Diagrams**

| Р                             | in Numbe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44-Pin<br>QFN/TQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input<br>Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 15                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | USB Voltage, Host mode (5V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 26                            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | USB External VBUS Control Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 25                            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | USB OTG External Charge Pump Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 26                            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | USB OTG Internal Charge Pump Feedback Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 2                             | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | USB VBUS Valid Status Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 20                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | External Filter Capacitor Connection (regulator enabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 25                            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | USB OTG VBUS PWM/Charge Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 13, 28                        | 10, 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28, 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Positive Supply for Peripheral Digital Logic and I/O Pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 20                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ρ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Positive Supply for Microcontroller Core Logic (regulator disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 22                            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | USB Differential Minus Input/Output (external transceiver).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 21                            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | USB Differential Plus Input/Output (external transceiver).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 3                             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A/D and Comparator Reference Voltage (low) Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 2                             | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A/D and Comparator Reference Voltage (high) Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 8, 27                         | 5, 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29, 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ground Reference for Logic and I/O Pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 23                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | USB Voltage (3.3V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                               | 28-Pin<br>SPDIP/<br>SOIC/SSOP<br>15<br>26<br>25<br>26<br>20<br>25<br>13, 28<br>20<br>25<br>13, 28<br>20<br>22<br>21<br>3<br>3<br>2<br>2<br>21<br>3<br>2<br>2<br>3<br>2<br>2<br>21<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>2<br>3<br>2<br>2<br>3<br>2<br>2<br>3<br>2<br>2<br>3<br>2<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | 28-Pin<br>SPDIP/<br>SOIC/SSOP         28-Pin<br>QFN           15         12           26         23           25         22           26         23           25         22           26         23           25         22           26         23           2         27           20         17           25         22           13, 28         10, 25           20         17           21         18           3         28           2         27           8, 27         5, 24 | SPDIP/<br>SOIC/SSOP         28-Pin<br>QFN         44-Pin<br>QFN/TQFP           15         12         42           26         23         15           25         22         14           26         23         15           25         22         14           26         23         15           2         27         19           20         17         7           25         22         14           13, 28         10, 25         28, 40           20         17         7           21         19         9           21         18         8           3         28         20           2         27         19           8, 27         5, 24         29, 39 | 28-Pin<br>SPDIP/<br>SOIC/SSOP         28-Pin<br>QFN         44-Pin<br>QFN/TQFP         I/O           15         12         42         P           26         23         15         O           25         22         14         O           26         23         15         I           2         27         19         I           20         17         7         P           25         22         14         O           26         23         15         I           2         27         19         I           20         17         7         P           25         22         14         O           13, 28         10, 25         28, 40         P           20         17         7         P           20         17         7         P           20         17         9         I/O           21         18         8         I/O           2         27         19         I           2         27         19         I           8, 27         5, 24         29, 39         P | 28-Pin<br>SPDIP/<br>SOIC/SSOP         28-Pin<br>QFN         44-Pin<br>QFN/TQFP         I/O         Input<br>Buffer           15         12         42         P            26         23         15         O            25         22         14         O            26         23         15         I         ANA           2         27         19         I         ST           20         17         7         P            25         22         144         O            26         23         15         I         ANA           2         27         19         I         ST           20         17         7         P            25         22         14         O            20         17         7         P            20         17         7         P            20         17         7         P            21         18         8         I/O         ST           3         28         20         I         ANA |  |  |

#### **TABLE 1-2:** PIC24FJ64GB004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer Legend: ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

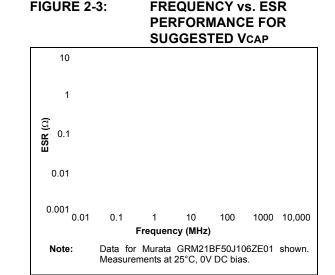

### 2.4 Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This secti | on applies   | only | to | PIC24FJ |

|-------|------------|--------------|------|----|---------|

|       |            | th an on-chi |      |    |         |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 26.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.