#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb002-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Р                             | in Numbe      | r                  |     |                 |                                                                                            |

|----------|-------------------------------|---------------|--------------------|-----|-----------------|--------------------------------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                                                |

| INT0     | 16                            | 13            | 43                 | I   | ST              | External Interrupt Input.                                                                  |

| MCLR     | 1                             | 26            | 18                 | Ι   | ST              | Master Clear (device Reset) Input. This line is brought low to cause a Reset.              |

| OSCI     | 9                             | 6             | 30                 | Ι   | ANA             | Main Oscillator Input Connection.                                                          |

| OSCO     | 10                            | 7             | 31                 | 0   | ANA             | Main Oscillator Output Connection.                                                         |

| PGEC1    | 5                             | 2             | 22                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP™ Programming Clock.                                      |

| PGED1    | 4                             | 1             | 21                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC2    | 22                            | 19            | 9                  | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED2    | 21                            | 18            | 8                  | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC3    | 3                             | 28            | 20                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED3    | 2                             | 27            | 19                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PMA0     | 10                            | 7             | 3                  | I/O | ST              | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 12                            | 9             | 2                  | I/O | ST              | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | —                             | _             | 27                 | 0   | _               | Parallel Master Port Address (Demultiplexed Master modes).                                 |

| PMA3     | _                             |               | 38                 | 0   | _               |                                                                                            |

| PMA4     | _                             |               | 37                 | 0   | _               |                                                                                            |

| PMA5     | _                             |               | 4                  | 0   | _               |                                                                                            |

| PMA6     | _                             |               | 5                  | 0   | _               |                                                                                            |

| PMA7     | _                             |               | 13                 | 0   | _               |                                                                                            |

| PMA8     | _                             |               | 32                 | 0   | _               |                                                                                            |

| PMA9     | _                             |               | 35                 | 0   | _               |                                                                                            |

| PMA10    | _                             |               | 12                 | 0   | _               |                                                                                            |

| PMCS1    | 9                             | 6             | 30                 | I/O | ST/TTL          | Parallel Master Port Chip Select 1 Strobe/Address Bit 15.                                  |

| PMBE     | 11                            | 8             | 36                 | 0   | _               | Parallel Master Port Byte Enable Strobe.                                                   |

| PMD0     | 4                             | 1             | 21                 | I/O | ST/TTL          | Parallel Master Port Data (Demultiplexed Master mode) or                                   |

| PMD1     | 5                             | 2             | 22                 | I/O | ST/TTL          | Address/Data (Multiplexed Master modes).                                                   |

| PMD2     | 6                             | 3             | 23                 | I/O | ST/TTL          | 1                                                                                          |

| PMD3     | 18                            | 15            | 1                  | I/O | ST/TTL          | 1                                                                                          |

| PMD4     | 17                            | 14            | 44                 | I/O | ST/TTL          | 1                                                                                          |

| PMD5     | 16                            | 13            | 43                 | I/O | ST/TTL          | 1                                                                                          |

| PMD6     | 3                             | 28            | 20                 | I/O | ST/TTL          | 1                                                                                          |

| PMD7     | 2                             | 27            | 19                 | I/O | ST/TTL          | 1                                                                                          |

| PMRD     | 24                            | 21            | 11                 | 0   | _               | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 7                             | 4             | 24                 | 0   | _               | Parallel Master Port Write Strobe.                                                         |

|          | TL = TTL inpu                 |               | 1                  | -   |                 | Schmitt Trigger input buffer                                                               |

| TABLE 1-2: | PIC24FJ64GB004 FAMILY PINOUT DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------------|

|            |                                                       |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

### TABLE 4-24: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _      | _      | _      | DPSLP  | СМ     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   |       | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | CPDIV1  | CPDIV0 | PLLEN  |       | —     | _      | _      | _     | 0100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _      | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 |         |        | _      |       |       | _      | _      | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information.

#### TABLE 4-25: DEEP SLEEP REGISTER MAP

| File Name                                                                      | Addr | Bit 15                                | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7        | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0   | All<br>Resets <sup>(1)</sup> |

|--------------------------------------------------------------------------------|------|---------------------------------------|--------|--------|--------|--------|--------|--------|------------|--------------|------------|-------|-------|-------|--------|-------|---------|------------------------------|

| DSCON                                                                          | 758  | DSEN                                  | -      |        |        | _      | —      |        | _          |              | _          | _     | _     |       | —      | DSBOR | RELEASE | 0000                         |

| DSWAKE                                                                         | 075A | _                                     | _      | _      | _      | _      | _      | _      | DSINT0     | DSFLT        | _          | _     | DSWDT | DSRTC | DSMCLR | _     | DSPOR   | 0001                         |

| DSGPR0                                                                         | 075C |                                       |        |        |        |        |        | Deep S | leep Gener | al Purpose R | Register 0 |       |       |       |        |       |         | 0000                         |

| DSGPR1                                                                         | 075E | Deep Sleep General Purpose Register 1 |        |        |        |        |        |        |            |              |            | 0000  |       |       |        |       |         |                              |

| Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |      |                                       |        |        |        |        |        |        |            |              |            |       |       |       |        |       |         |                              |

**Note 1:** The Deep Sleep registers are only reset on a VDD POR event.

### TABLE 4-26: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|-------|-------|-------|--------|--------|--------|--------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | —      | _      | _     | _     | _                    | ERASE | —     | _     | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | _      | _      | _      | —      | _      | _      | _     | _     | NVMKEY Register<7:0> |       |       |       |        | 0000   |        |        |                 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

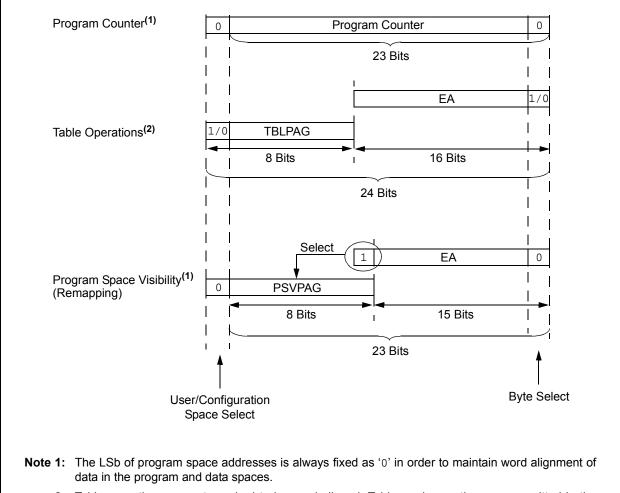

| TABLE 4-28: PROGRAM SPACE ADDRESS CONSTRUCTION |

|------------------------------------------------|

|------------------------------------------------|

| A                        | Access        |                          | Progra                       | m Space /                         | Address       |     |  |

|--------------------------|---------------|--------------------------|------------------------------|-----------------------------------|---------------|-----|--|

| Access Type              | Space         | <23>                     | <22:16>                      | <15>                              | <14:1>        | <0> |  |

| Instruction Access       | User          | 0                        |                              | PC<22:1>                          |               |     |  |

| (Code Execution)         |               |                          | 0xx xxxx xxxx xxxx xxxx xxx0 |                                   |               |     |  |

| TBLRD/TBLWT              | User          | TBI                      | LPAG<7:0>                    |                                   | Data EA<15:0> |     |  |

| (Byte/Word Read/Write)   |               | 02                       | xxx xxxx                     | XXXX XXXX XXXX XXXX               |               |     |  |

|                          | Configuration | TBI                      | LPAG<7:0>                    | Data EA<15:0>                     |               |     |  |

|                          |               | 1xxx xxxx xxxx xxxx xxxx |                              |                                   |               | xxx |  |

| Program Space Visibility | User          | 0                        | PSVPAG<7                     | 7:0> Data EA<14:0> <sup>(1)</sup> |               |     |  |

| (Block Remap/Read)       |               | 0                        | xxxx xx                      |                                   |               |     |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

**2:** Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

NOTES:

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 8. "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24F CPU. It has the following features:

- Up to 8 processor exceptions and software traps

- 7 user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors, consisting of 8 non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FJ64GB004 family devices implement non-maskable traps and unique interrupts. These are summarized in Table 7-1 and Table 7-2.

### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset which forces the PC to zero. The micro-controller then begins program execution at location 000000h. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-0         | R/W-0                              | R/W-0                                                  | R/W-0    | R/W-0             | R/W-0           | R/W-0           | U-0     |

|---------------|------------------------------------|--------------------------------------------------------|----------|-------------------|-----------------|-----------------|---------|

| U2TXIF        | U2RXIF                             | INT2IF                                                 | T5IF     | T4IF              | OC4IF           | OC3IF           |         |

| bit 15        |                                    | L                                                      |          |                   | 1               | - 4             | bit     |

|               |                                    |                                                        |          |                   |                 |                 |         |

| U-0           | U-0                                | U-0                                                    | R/W-0    | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

| _             |                                    |                                                        | INT1IF   | CNIF              | CMIF            | MI2C1IF         | SI2C1IF |

| bit 7         |                                    |                                                        |          | •                 | •               |                 | bit     |

|               |                                    |                                                        |          |                   |                 |                 |         |

| Legend:       |                                    |                                                        |          |                   |                 |                 |         |

| R = Readabl   | le bit                             | W = Writable                                           | bit      | U = Unimplem      | nented bit, rea | d as '0'        |         |

| -n = Value at | t POR                              | '1' = Bit is set                                       |          | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| bit 15        | 1 = Interrupt r<br>0 = Interrupt r | T2 Transmitter<br>equest has occ<br>equest has not     | occurred |                   |                 |                 |         |

| bit 14        | 1 = Interrupt r                    | RT2 Receiver Ir<br>request has occ<br>request has not  | urred    | tatus bit         |                 |                 |         |

| bit 13        | 1 = Interrupt r                    | nal Interrupt 2<br>request has occ<br>request has not  | curred   |                   |                 |                 |         |

| bit 12        | 1 = Interrupt r                    | Interrupt Flag S<br>request has occ<br>request has not | urred    |                   |                 |                 |         |

| bit 11        | 1 = Interrupt r                    | Interrupt Flag S<br>equest has occ<br>equest has not   | urred    |                   |                 |                 |         |

| bit 10        | 1 = Interrupt r                    | ut Compare Ch<br>equest has occ<br>equest has not      | urred    | ipt Flag Status b | bit             |                 |         |

| bit 9         | 1 = Interrupt r                    | ut Compare Cha<br>request has occ<br>request has not   | urred    | ipt Flag Status b | bit             |                 |         |

| bit 8-5       | -                                  | ted: Read as '                                         |          |                   |                 |                 |         |

| bit 4         | 1 = Interrupt r                    | nal Interrupt 1<br>request has occ<br>request has not  | urred    |                   |                 |                 |         |

| bit 3         | 1 = Interrupt r                    | hange Notifica<br>equest has occ<br>equest has not     | urred    | Flag Status bit   |                 |                 |         |

| bit 2         | 1 = Interrupt r                    | arator Interrupt<br>equest has occ<br>equest has not   | urred    | t                 |                 |                 |         |

| bit 1         | 1 = Interrupt r                    | ster I2C1 Event<br>equest has occ<br>equest has not    | urred    | ) Status bit      |                 |                 |         |

| bit 0         | 1 = Interrupt r                    | ve I2C1 Event I<br>request has occ<br>request has not  | curred   | Status bit        |                 |                 |         |

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

### 8.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 8-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The CLKDIV register (Register 8-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator. The OSCTUN register (Register 8-3) allows the user to fine tune the FRC Oscillator over a range of approximately  $\pm 12\%$ .

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | —   | CF     | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |        |        | bit 0 |

| Legend:           | CO = Clearable Only bit | SO = Settable Only bit      |                    |

|-------------------|-------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                |

|-----------|---------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                              |

|           | 111 = Fast RC Oscillator with Postscaler (FRCDIV)                         |

|           | 110 = Reserved                                                            |

|           | 101 = Low-Power RC Oscillator (LPRC)                                      |

|           | 100 = Secondary Oscillator (SOSC)                                         |

|           | 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)            |

|           | 010 = Primary Oscillator (XT, HS, EC)                                     |

|           | 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)          |

|           | 000 = Fast RC Oscillator (FRC)                                            |

| bit 11    | Unimplemented: Read as '0'                                                |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                   |

|           | 111 = Fast RC Oscillator with Postscaler (FRCDIV)                         |

|           | 110 = Reserved                                                            |

|           | 101 = Low-Power RC Oscillator (LPRC)                                      |

|           | 100 = Secondary Oscillator (SOSC)                                         |

|           | 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)            |

|           | 010 = Primary Oscillator (XT, HS, EC)                                     |

|           | 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)          |

|           | 000 = Fast RC Oscillator (FRC)                                            |

|           | and unlined for these bits are determined by the ENOCO Configuration bits |

- **Note 1:** Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1', once the IOLOCK bit is set, it cannot be cleared.

- 3: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

### 9.2.4.3 Exiting Deep Sleep Mode

Deep Sleep mode exits on any one of the following events:

- POR event on VDD supply. If there is no DSBOR circuit to re-arm the VDD supply POR circuit, the external VDD supply must be lowered to the natural arming voltage of the POR circuit.

- DSWDT time-out. When the DSWDT timer times out, the device exits Deep Sleep.

- RTCC alarm (if RTCEN = 1).

- Assertion ('0') of the  $\overline{\text{MCLR}}$  pin.

- Assertion of the INT0 pin (if the interrupt was enabled before Deep Sleep mode was entered). The polarity configuration is used to determine the assertion level ('0' or '1') of the pin that will cause an exit from Deep Sleep mode. Exiting from Deep Sleep mode requires a change on the INT0 pin while in Deep Sleep mode.

# **Note:** Any interrupt pending when entering Deep Sleep mode is cleared.

Exiting Deep Sleep mode generally does not retain the state of the device and is equivalent to a Power-on Reset (POR) of the device. Exceptions to this include the RTCC (if present), which remains operational through the wake-up, the DSGPRx registers and DSWDT.

Wake-up events that occur from the time Deep Sleep exits, until the time that the POR sequence completes, are ignored and are not captured in the DSWAKE register.

The sequence for exiting Deep Sleep mode is:

- 1. After a wake-up event, the device exits Deep Sleep and performs a POR. The DSEN bit is cleared automatically. Code execution resumes at the Reset vector.

- To determine if the device exited Deep Sleep, read the Deep Sleep bit, DPSLP (RCON<10>). This bit will be set if there was an exit from Deep Sleep mode. If the bit is set, clear it.

- 3. Determine the wake-up source by reading the DSWAKE register.

- Determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR bit (DSCON<1>).

- If application context data has been saved, read it back from the DSGPR0 and DSGPR1 registers.

- 6. Clear the RELEASE bit (DSCON<0>).

### 9.2.4.4 Deep Sleep Wake-up Time

Since wake-up from Deep Sleep results in a POR, the wake-up time from Deep Sleep is the same as the device POR time. Also, because the internal regulator is turned off, the voltage on VCAP may drop depending on how long the device is asleep. If VCAP has dropped below 2V, then there will be additional wake-up time while the regulator charges VCAP.

Deep Sleep wake-up time is specified in **Section 29.0 "Electrical Characteristics"** as TDSWU. This specification indicates the worst case wake-up time, including the full POR Reset time (including TPOR and TRST), as well as the time to fully charge a 10  $\mu$ F capacitor on VCAP which has discharged to 0V. Wake-up may be significantly faster if VCAP has not discharged.

### 9.2.4.5 Saving Context Data with the DSGPR0/DSGPR1 Registers

As exiting Deep Sleep mode causes a POR, most Special Function Registers reset to their default POR values. In addition, because VDDCORE power is not supplied in Deep Sleep mode, information in data RAM may be lost when exiting this mode.

Applications which require critical data to be saved prior to Deep Sleep may use the Deep Sleep General Purpose registers, DSGPR0 and DSGPR1, or data EEPROM (if available). Unlike other SFRs, the contents of these registers are preserved while the device is in Deep Sleep mode. After exiting Deep Sleep, software can restore the data by reading the registers and clearing the RELEASE bit (DSCON<0>).

### 9.2.4.6 I/O Pins During Deep Sleep Mode

During Deep Sleep, the general purpose I/O pins retain their previous states and the Secondary Oscillator (SOSC) will remain running, if enabled. Pins that are configured as inputs (TRIS bit set) prior to entry into Deep Sleep remain high-impedance during Deep Sleep. Pins that are configured as outputs (TRIS bit clear) prior to entry into Deep Sleep remain as output pins during Deep Sleep. While in this mode, they continue to drive the output level determined by their corresponding LAT bit at the time of entry into Deep Sleep. Once the device wakes back up, all I/O pins continue to maintain their previous states, even after the device has finished the POR sequence and is executing application code again. Pins configured as inputs during Deep Sleep remain high-impedance and pins configured as outputs continue to drive their previous value. After waking up, the TRIS and LAT registers, and the SOSCEN bit (OSCCON<1>) are reset. If firmware modifies any of these bits or registers, the I/O will not immediately go to the newly configured states. Once the firmware clears the RELEASE bit (DSCON<0>) the I/O pins are "released". This causes the I/O pins to take the states configured by their respective TRIS and LAT bit values.

This means that keeping the SOSC running after waking up requires the SOSCEN bit to be set before clearing RELEASE.

If the Deep Sleep BOR (DSBOR) is enabled, and a DSBOR or a true POR event occurs during Deep Sleep, the I/O pins will be immediately released similar to clearing the RELEASE bit. All previous state information will be lost, including the general purpose DSGPR0 and DSGPR1 contents.

If a MCLR Reset event occurs during Deep Sleep, the DSGPRx, DSCON and DSWAKE registers will remain valid and the RELEASE bit will remain set. The state of the SOSC will also be retained. The I/O pins, however, will be reset to their MCLR Reset state. Since RELEASE is still set, changes to the SOSCEN bit (OSCCON<1>) cannot take effect until the RELEASE bit is cleared.

In all other Deep Sleep wake-up cases, application firmware must clear the RELEASE bit in order to reconfigure the I/O pins.

### 9.2.4.7 Deep Sleep WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (CW4<7>). The device Watchdog Timer (WDT) need not be enabled for the DSWDT to function. Entry into Deep Sleep mode automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (CW4<4>). The postscaler options are programmed by the DSWDTPS<3:0> Configuration bits (CW4<3:0>). The minimum time-out period that can be achieved is 2.1 ms and the maximum is 25.7 days. For more details on the CW4 Configuration register and DSWDT configuration options, refer to **Section 26.0 "Special Features"**.

### 9.2.4.8 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If an accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCOSC Configuration bit (CW4<5>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

### 9.2.4.9 Checking and Clearing the Status of Deep Sleep Mode

Upon entry into Deep Sleep mode, the status bit, DPSLP (RCON<10>), becomes set and must be cleared by software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set. This is a normal Power-on Reset.

- Both the DPSLP and POR bits are set. This means that Deep Sleep mode was entered, the device was powered down and Deep Sleep mode was exited.

### 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains up to two 5-bit fields, with each field being associated with one RPn pin (see Register 10-15 through Register 10-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-3).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

| TABLE 10-3: | SELECTABLE OUTPUT SOURCES | (MAPS FUNCTION TO OUTPUT) |  |

|-------------|---------------------------|---------------------------|--|

|             |                           |                           |  |

| Output Function Number <sup>(1)</sup> | tput Function Number <sup>(1)</sup> Function |                          |  |

|---------------------------------------|----------------------------------------------|--------------------------|--|

| 0                                     | NULL <sup>(2)</sup>                          | Null                     |  |

| 1                                     | C1OUT                                        | Comparator 1 Output      |  |

| 2                                     | C2OUT                                        | Comparator 2 Output      |  |

| 3                                     | U1TX                                         | UART1 Transmit           |  |

| 4                                     | U1RTS <sup>(3)</sup>                         | UART1 Request To Send    |  |

| 5                                     | U2TX                                         | UART2 Transmit           |  |

| 6                                     | U2RTS <sup>(3)</sup>                         | UART2 Request To Send    |  |

| 7                                     | SDO1                                         | SPI1 Data Output         |  |

| 8                                     | SCK1OUT                                      | SPI1 Clock Output        |  |

| 9                                     | SS10UT                                       | SPI1 Slave Select Output |  |

| 10                                    | SDO2                                         | SPI2 Data Output         |  |

| 11                                    | SCK2OUT                                      | SPI2 Clock Output        |  |

| 12                                    | SS2OUT                                       | SPI2 Slave Select Output |  |

| 18                                    | OC1                                          | Output Compare 1         |  |

| 19                                    | OC2                                          | Output Compare 2         |  |

| 20                                    | OC3                                          | Output Compare 3         |  |

| 21                                    | OC4                                          | Output Compare 4         |  |

| 22                                    | OC5                                          | Output Compare 5         |  |

| 23-28                                 | (unused)                                     | NC                       |  |

| 29                                    | CTPLS                                        | CTMU Output Pulse        |  |

| 30                                    | 30 C3OUT Comparator 3 C                      |                          |  |

| 31                                    | (unused)                                     | NC                       |  |

**Note 1:** Setting the RPORx register with the listed value assigns that output function to the associated RPn pin.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

**3:** IrDA<sup>®</sup> BCLK functionality uses this output.

### REGISTER 10-11: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| _     | —   |     | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 12-8  | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                         |

| bit 4-0   | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to Corresponding RPn or RPIn Pin bits    |

### REGISTER 10-12: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0                           | U-0 | U-0              | U-0   | U-0                                | U-0   | U-0             | U-0   |

|-------------------------------|-----|------------------|-------|------------------------------------|-------|-----------------|-------|

| —                             | —   | _                | —     | —                                  | —     | —               | —     |

| bit 15                        |     |                  |       |                                    |       |                 | bit 8 |

|                               |     |                  |       |                                    |       |                 |       |

| U-0                           | U-0 | U-0              | R/W-1 | R/W-1                              | R/W-1 | R/W-1           | R/W-1 |

| _                             | _   | —                | SS1R4 | SS1R3                              | SS1R2 | SS1R1           | SS1R0 |

| bit 7                         |     |                  |       |                                    |       |                 | bit 0 |

|                               |     |                  |       |                                    |       |                 |       |

| Legend:                       |     |                  |       |                                    |       |                 |       |

| R = Readable bit W = Writable |     | W = Writable I   | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR             |     | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

|                               |     |                  |       |                                    |       |                 |       |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to Corresponding RPn or RPIn Pin bits

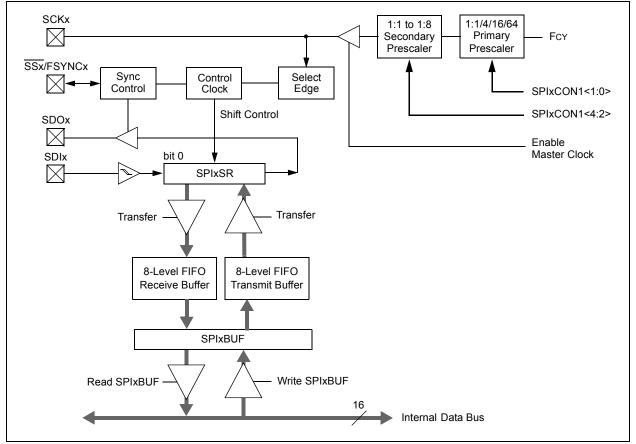

To set up the SPI module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 5. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 6. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

FIGURE 15-2: SPIX MODULE BLOCK DIAGRAM (ENHANCED MODE)

# 17.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

# EQUATION 17-1: UART BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** FCY denotes the instruction cycle clock

frequency (Fosc/2).**2:** Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 17-2: UART BAUD RATE WITH BRGH = $1^{(1,2)}$

|      |    | Baud Rate = $\frac{FCY}{4 \cdot (UxBRG + 1)}$         |

|------|----|-------------------------------------------------------|

|      |    | $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$           |

| Note | 1: | Fcy denotes the instruction cycle clock<br>frequency. |

|      | 2. | Based on $E_{CV} = E_{OSC}/2$ Doze mode               |

2: Based on FCY = FOSC/2, Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

## EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate =    | Fcy/(16 (UxBRG + 1))                          |

|------------------------|-----------------------------------------------|

|                        |                                               |

| Solving for UxBRG Val  | lue:                                          |

| UxBRG =                | ((FCY/Desired Baud Rate)/16) - 1              |

| UxBRG =                | ((400000/9600)/16) - 1                        |

| UxBRG =                | 25                                            |

| Calculated Baud Rate = | 4000000/(16 (25 + 1))                         |

| =                      | 9615                                          |

| Error =                | (Calculated Baud Rate – Desired Baud Rate)    |

|                        | Desired Baud Rate                             |

| =                      | (9615 - 9600)/9600                            |

| =                      | 0.16%                                         |

|                        |                                               |

| Note 1: Based on I     | FCY = FOSC/2, Doze mode and PLL are disabled. |

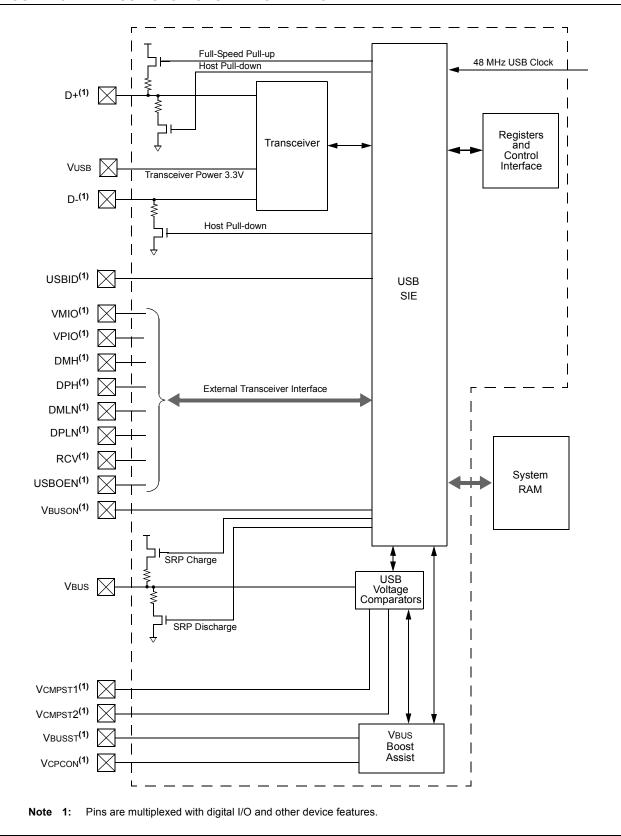

### FIGURE 18-1: USB OTG MODULE BLOCK DIAGRAM

### 18.1 Hardware Configuration

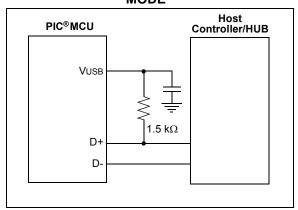

### 18.1.1 DEVICE MODE

### 18.1.1.1 D+ Pull-up Resistor

PIC24FJ64GB004 family devices have a built-in 1.5 kΩ resistor on the D+ line that is available when the microcontroller in operating in device mode. This is used to signal an external Host that the device is operating in Full-Speed Device mode. It is engaged by setting the USBEN bit (U1CON<0>). If the OTGEN bit (U1OTGCON<2>) is set, then the D+ pull-up is enabled through the DPPULUP bit (U1OTGCON<7>).

Alternatively, an external resistor may be used on D+, as shown in Figure 18-2.

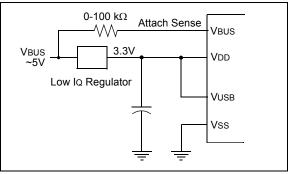

#### FIGURE 18-2: EXTERNAL PULL-UP FOR FULL-SPEED DEVICE MODE

### 18.1.1.2 Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- · Bus Power Only

- Self-Power Only

- Dual Power with Self-Power Dominance

Bus Power Only mode (Figure 18-3) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the USB 2.0 Specification, the total effective capacitance appearing across VBUs and ground must be no more than 10  $\mu$ F.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or Dpull-up resistor must remain active, which will consume some of the allowed suspend current.

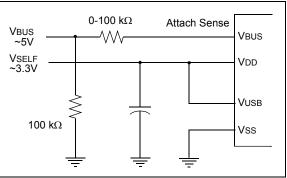

In Self-Power Only mode (Figure 18-4), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

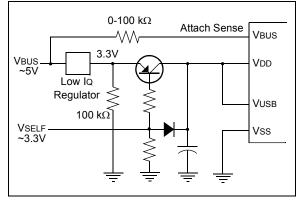

The Dual Power option with Self-Power Dominance (Figure 18-5) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual Power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

FIGURE 18-3: BUS POWER ONLY

FIGURE 18-4: SELF-POWER ONLY

FIGURE 18-5:

**DUAL POWER EXAMPLE**

### 18.3 USB Interrupts

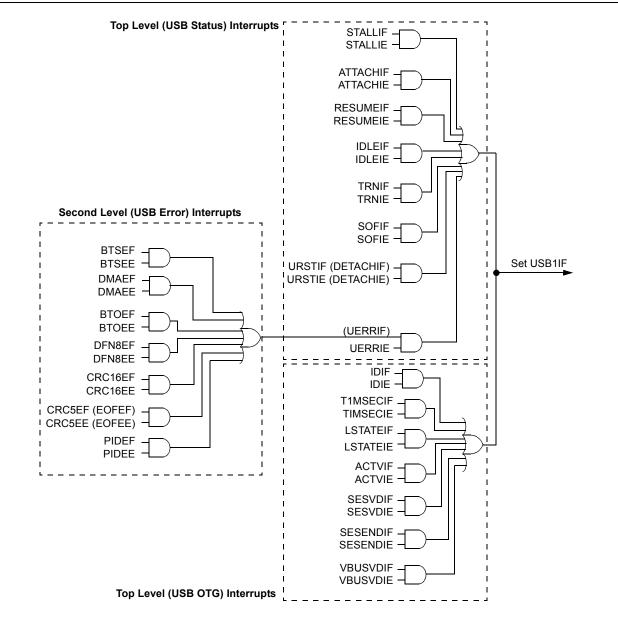

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 18-9 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second

### FIGURE 18-9: USB OTG INTERRUPT FUNNEL

level consists of USB error conditions, which are enabled and flagged in the U1EIR and U1EIE registers. An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level.

Interrupts may be used to trap routine events in a USB transaction. Figure 18-10 provides some common events within a USB frame and their corresponding interrupts.

## 26.0 SPECIAL FEATURES

- Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the following sections of the "PIC24F Family Reference Manual":

Section 9. "Watchdog Timer (WDT)" (DS39697)

- Section 32. "High-Level Device Integration" (DS39719)

- Section 33. "Programming and Diagnostics" (DS39716)

PIC24FJ64GB004 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- · Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming

- In-Circuit Emulation

### 26.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location F80000h. A detailed explanation of the various bit functions is provided in Register 26-1 through Register 26-6.

Note that address F80000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh) which can only be accessed using table reads and table writes.

### 26.1.1 CONSIDERATIONS FOR CONFIGURING PIC24FJ64GB004 FAMILY DEVICES

In PIC24FJ64GB004 family devices, the configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the three words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 26-1. These are packed representations of the actual device Configuration bits, whose actual locations are distributed among several locations in configuration space. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets.

**Note:** Configuration data is reloaded on all types of device Resets.

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The upper byte of all Flash Configuration Words in program memory should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

# TABLE 26-1: FLASH CONFIGURATION WORD LOCATIONS FOR PIC24FJ64GB004 FAMILY DEVICES DEVICES

| Device         | Configuration Word Addresses |       |       |       |  |  |

|----------------|------------------------------|-------|-------|-------|--|--|

| Device         | 1                            | 2     | 3     | 4     |  |  |

| PIC24FJ32GB00X | 57FEh                        | 57FCh | 57FAh | 57F8h |  |  |

| PIC24FJ64GB00X | ABFEh                        | ABFCh | ABFAh | ABF8h |  |  |

| AC CHARACTERISTICS                                                                                                          |       |                                             | $ \begin{array}{ l l l l l l l l l l l l l l l l l l l$ |            |       |     |                              |  |

|-----------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------|---------------------------------------------------------|------------|-------|-----|------------------------------|--|

| Param<br>No.         Sym         Characteristic <sup>(1)</sup> Min         Typ <sup>(2)</sup> Max         Units         Cor |       |                                             |                                                         | Conditions |       |     |                              |  |

| OS50                                                                                                                        | Fplli | PLL Input Frequency<br>Range <sup>(2)</sup> | 4                                                       | _          | 32    | MHz | ECPLL, HSPLL, XTPLL<br>modes |  |

| OS51                                                                                                                        | Fsys  | PLL Output Frequency<br>Range               | 95.76                                                   | _          | 96.24 | MHz |                              |  |

| OS52                                                                                                                        | TLOCK | PLL Start-up Time<br>(Lock Time)            | _                                                       | 180        | _     | μS  |                              |  |

| OS53                                                                                                                        | DCLK  | CLKO Stability (Jitter)                     | -0.25                                                   | _          | 0.25  | %   |                              |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 29-18: INTERNAL RC OSCILLATOR SPECIFICATIONS

|              |       |                               | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |     |   |    |            |  |

|--------------|-------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|----|------------|--|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup> | Min Typ Max Units Condition                                                                                                                                                                                                                                                    |     |   |    | Conditions |  |

|              | TFRC  | FRC Start-up Time             | —                                                                                                                                                                                                                                                                              | 15  | - | μS |            |  |

|              | Tlprc | LPRC Start-up Time            | —                                                                                                                                                                                                                                                                              | 500 | _ | μS |            |  |

### TABLE 29-19: INTERNAL RC OSCILLATOR ACCURACY

| АС СНА       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |               |     |       |                                                                            |

|--------------|------------------------------------------------------|-------|---------------|-----|-------|----------------------------------------------------------------------------|

| Param<br>No. | Characteristic                                       | Min   | Тур           | Мах | Units | Conditions                                                                 |

| F20          | FRC Accuracy @ 8 MHz <sup>(1,3)</sup>                | -1.25 | <u>+</u> 0.25 | 1.0 | %     | $-40^{\circ}C \leq Ta \leq +85^{\circ}C, \ 3.0V \leq V\text{DD} \leq 3.6V$ |

| F21          | LPRC Accuracy @ 31 kHz <sup>(2)</sup>                | -15   | _             | 15  | %     | $-40^{\circ}C \leq Ta \leq +85^{\circ}C, \ 3.0V \leq V\text{DD} \leq 3.6V$ |

Note 1: Frequency calibrated at 25°C and 3.3V. OSCTUN bits can be used to compensate for temperature drift.

2: Change of LPRC frequency as VDD changes.

**3:** To achieve this accuracy, physical stress applied to the microcontroller package (ex: by flexing the PCB) must be kept to a minimum.

| AC CHARACTERISTICS |        |                                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                          |  |

|--------------------|--------|---------------------------------------------------|-------------------------------------------------------|------|------|-------|------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                    | Min.                                                  | Тур  | Max. | Units | Conditions                               |  |

|                    |        | Cloc                                              | k Parame                                              | ters |      |       |                                          |  |

| AD50               | Tad    | ADC Clock Period                                  | 75                                                    | —    | —    | ns    | Tcy = 75 ns, AD1CON3<br>in default state |  |

| AD51               | tRC    | ADC Internal RC Oscillator<br>Period              | —                                                     | 250  | —    | ns    |                                          |  |

|                    |        | Con                                               | version R                                             | ate  |      |       |                                          |  |

| AD55               | tCONV  | Conversion Time                                   |                                                       | 12   |      | TAD   |                                          |  |

| AD56               | FCNV   | Throughput Rate                                   |                                                       |      | 500  | ksps  | AVDD > 2.7V                              |  |

| AD57               | tSAMP  | Sample Time                                       | —                                                     | 1    | —    | TAD   |                                          |  |

|                    |        | Cloc                                              | k Parame                                              | ters |      |       |                                          |  |

| AD61               | tPSS   | Sample Start Delay from setting Sample bit (SAMP) | 2                                                     |      | 3    | Tad   |                                          |  |

# TABLE 29-23: ADC CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Because the sample capacitors will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

## **30.0 PACKAGING INFORMATION**

### 30.1 Package Marking Information

28-Lead QFN

28-Lead SOIC (.300")

### 28-Lead SPDIP

### 28-Lead SSOP

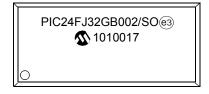

Example

| Legend: | XXX                                                                                                                   | Customer-specific information                                           |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

|         | Y Year code (last digit of calendar year)                                                                             |                                                                         |  |  |  |  |

|         | YY Year code (last 2 digits of calendar year)                                                                         |                                                                         |  |  |  |  |

|         | WW Week code (week of January 1 is week '01')                                                                         |                                                                         |  |  |  |  |

|         | NNN Alphanumeric traceability code                                                                                    |                                                                         |  |  |  |  |

|         |                                                                                                                       | Pb-free JEDEC designator for Matte Tin (Sn)                             |  |  |  |  |

|         | *                                                                                                                     | This package is Pb-free. The Pb-free JEDEC designator ((e3))            |  |  |  |  |

|         |                                                                                                                       | can be found on the outer packaging for this package.                   |  |  |  |  |

|         |                                                                                                                       | nt the full Microchip part number cannot be marked on one line, it will |  |  |  |  |

|         | be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                         |  |  |  |  |

### Example

PIC24FJ32GB002

1010017

-I/SP@3

### Example