Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

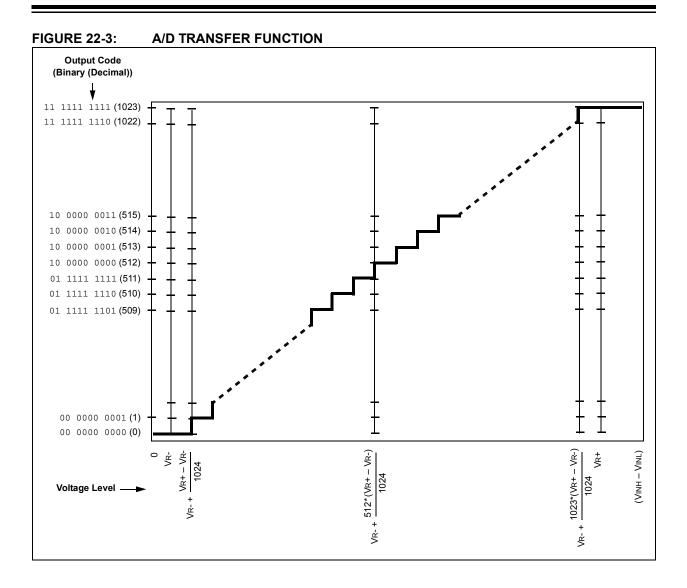

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb002t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

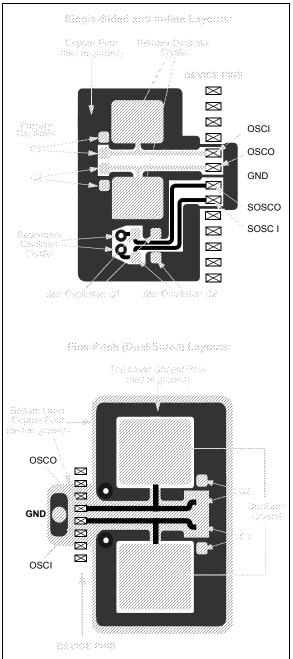

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### TABLE 4-15: PAD CONFIGURATION REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-----------|-----------|--------|---------------|

| PADCFG1   | 02FC | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | —     | _     | _     | RTSECSEL1 | RTSECSEL0 | PMPTTL | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: ADC REGISTER MAP

| IADLE 4   | -10. |        |                        |        |                       |        |        |        |                      |                      |                      |       |        |        |        |        |        |               |

|-----------|------|--------|------------------------|--------|-----------------------|--------|--------|--------|----------------------|----------------------|----------------------|-------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12                | Bit 11 | Bit 10 | Bit 9  | Bit 8                | Bit 7                | Bit 6                | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| ADC1BUF0  | 0300 |        |                        |        |                       |        |        |        | ADC Dat              | a Buffer 0           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF1  | 0302 |        |                        |        |                       |        |        |        | ADC Dat              | a Buffer 1           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF2  | 0304 |        |                        |        |                       |        |        |        | ADC Dat              | a Buffer 2           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF3  | 0306 |        |                        |        |                       |        |        |        | ADC Dat              | a Buffer 3           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF4  | 0308 |        | ADC Data Buffer 4 x    |        |                       |        |        |        |                      |                      | xxxx                 |       |        |        |        |        |        |               |

| ADC1BUF5  | 030A |        | ADC Data Buffer 5 xxxx |        |                       |        |        |        |                      |                      | xxxx                 |       |        |        |        |        |        |               |

| ADC1BUF6  | 030C |        |                        |        |                       |        |        |        | ADC Dat              | a Buffer 6           |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUF7  | 030E |        | ADC Data Buffer 7 xxx  |        |                       |        |        |        |                      | xxxx                 |                      |       |        |        |        |        |        |               |

| ADC1BUF8  | 0310 |        | ADC Data Buffer 8 xx   |        |                       |        |        |        |                      | xxxx                 |                      |       |        |        |        |        |        |               |

| ADC1BUF9  | 0312 |        | ADC Data Buffer 9 xx   |        |                       |        |        |        |                      |                      | xxxx                 |       |        |        |        |        |        |               |

| ADC1BUFA  | 0314 |        |                        |        |                       |        |        |        | ADC Data             | Buffer 10            |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFB  | 0316 |        |                        |        |                       |        |        |        | ADC Data             | a Buffer 11          |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFC  | 0318 |        |                        |        |                       |        |        |        | ADC Data             | Buffer 12            |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFD  | 031A |        |                        |        |                       |        |        |        | ADC Data             | Buffer 13            |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFE  | 031C |        |                        |        |                       |        |        |        | ADC Data             | Buffer 14            |                      |       |        |        |        |        |        | xxxx          |

| ADC1BUFF  | 031E |        |                        |        |                       |        |        | 1      | ADC Data             | Buffer 15            |                      |       |        |        |        |        | 1      | xxxx          |

| AD1CON1   | 0320 | ADON   | —                      | ADSIDL | —                     | —      | —      | FORM1  | FORM0                | SSRC2                | SSRC1                | SSRC0 | —      | —      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2   | 0322 | VCFG2  | VCFG1                  | VCFG0  | r                     | —      | CSCNA  | —      | —                    | BUFS                 | —                    | SMPI3 | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3   | 0324 | ADRC   | r                      | r      | SAMC4                 | SAMC3  | SAMC2  | SAMC1  | SAMC0                | ADCS7                | ADCS6                | ADCS5 | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS    | 0328 | CH0NB  | —                      | —      | CH0SB4                | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0               | CH0NA                | —                    | _     | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1PCFG   | 032C | PCFG15 |                        |        | PCFG12 <sup>(1)</sup> | PCFG11 | PCFG10 | PCFG9  |                      | PCFG7 <sup>(1)</sup> |                      | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000          |

| AD1CSSL   | 0330 | CSSL15 | CSSL14                 | CSSL13 | CSSL12 <sup>(1)</sup> | CSSL11 | CSSL10 | CSSL9  | CSSL8 <sup>(1)</sup> | CSSL7 <sup>(1)</sup> | CSSL6 <sup>(1)</sup> | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

Legend: — = unimplemented, read as '0', r = reserved, maintain as '0'. Reset values are shown in hexadecimal.

Note 1: Bits are not available on 28-pin devices; read as '0'.

### TABLE 4-17: CTMU REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON   | 033C | CTMUEN | —      | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON  | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  | _       | _        | _        | _       | _        | _        | _        | _        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

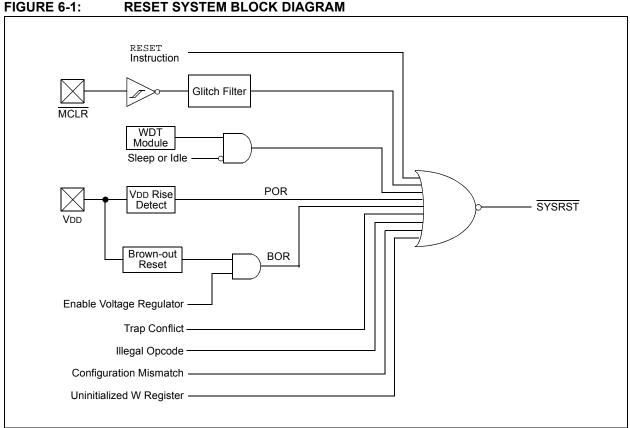

#### 6.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 7. "Reset" (DS39712).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Refer to the specific peripheral or CPU Note: section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A Power-on Reset will clear all bits, except for the BOR and POR bits (RCON<1:0>), which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

The status bits in the RCON register Note: should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

# 8.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or SOSC (if SOSCEN remains set).

- Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

A recommended code sequence for a clock switch includes the following:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- 2. Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8> in two back-to-back instructions.

- 3. Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0> in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 8-1.

#### EXAMPLE 8-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in |

|----------------------------------------|

| WO                                     |

| ;OSCCONH (high byte) Unlock Sequence   |

| MOV #OSCCONH, w1                       |

| MOV #0x78, w2                          |

| MOV #0x9A, w3                          |

| MOV.b w2, [w1]                         |

| MOV.b w3, [w1]                         |

| ;Set new oscillator selection          |

| MOV.b WREG, OSCCONH                    |

| ;OSCCONL (low byte) unlock sequence    |

| MOV #OSCCONL, w1                       |

| MOV #0x46, w2                          |

| MOV #0x57, w3                          |

| MOV.b w2, [w1]                         |

| MOV.b w3, [w1]                         |

| ;Start oscillator switch operation     |

| BSET OSCCON, #0                        |

|                                        |

# 8.6 Secondary Oscillator (SOSC)

#### 8.6.1 BASIC SOSC OPERATION

PIC24FJ64GB004 family devices do not have to set the SOSCEN bit to use the secondary oscillator. Any module requiring the SOSC (such as RTCC, Timer1 or DSWDT) will automatically turn on the SOSC when the clock signal is needed. The SOSC, however, has a long start-up time. To avoid delays for peripheral start-up, the SOSC can be manually started using the SOSCEN bit.

To use the secondary oscillator, the SOSCSEL<1:0> bits (CW3<9:8>) must be configured in an oscillator mode – either '11' or '01'. Setting SOSCSEL to '00' configures the SOSC pins for Digital mode, enabling digital I/O functionality on the pins. Digital functionality will not be available if the SOSC is configured in either of the oscillator modes.

### 8.6.2 LOW-POWER SOSC OPERATION

The secondary oscillator can operate in two distinct levels of power consumption based on device configuration. In Low-Power mode, the oscillator operates in a low drive strength, low-power state. By default, the oscillator uses a higher drive strength, and therefore, requires more power. The Secondary Oscillator Mode Configuration bits, SOSCSEL<1:0> (CW3<9:8>), determine the oscillator's power mode. Programming the SOSCSEL bits to '01' selects low-power operation.

The lower drive strength of this mode makes the SOSC more sensitive to noise and requires a longer start-up time. When Low-Power mode is used, care must be taken in the design and layout of the SOSC circuit to ensure that the oscillator starts up and oscillates properly.

#### 8.6.3 EXTERNAL (DIGITAL) CLOCK MODE (SCLKI)

The SOSC can also be configured to run from an external 32 kHz clock source, rather than the internal oscillator. In this mode, also referred to as Digital mode, the clock source provided on the SCLKI pin is used to clock any modules that are configured to use the secondary oscillator. In this mode, the crystal driving circuit is disabled and the SOSCEN bit (OSCCON<1>) has no effect.

### 8.6.4 SOSC LAYOUT CONSIDERATIONS

The pinout limitations on low pin count devices, such as those in the PIC24FJ64GB004 family, may make the SOSC more susceptible to noise than other PIC24F devices. Unless proper care is taken in the design and layout of the SOSC circuit, this external noise may introduce inaccuracies into the oscillator's period. In general, the crystal circuit connections should be as short as possible. It is also good practice to surround the crystal circuit with a ground loop or ground plane. For more information on crystal circuit design, please refer to **Section 6 "Oscillator"** (DS39700) of the *"PIC24F Family Reference Manual"*. Additional information is also available in these Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PICmicro<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design" (DS00849).

# 8.7 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FJ64GB004 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 8-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the POSCEN bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

### 9.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features    |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |  |  |

|       | Section 39. "Power-Saving Features         |  |  |  |  |  |  |  |  |

|       | with Deep Sleep" (DS39727).                |  |  |  |  |  |  |  |  |

The PIC24FJ64GB004 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep, Idle and Deep Sleep modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

#### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals except RTCC and DSWDT. It also freezes I/O states and removes power to SRAM and Flash memory. The assembly syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 9.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC, with LPRC as clock source, is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

| PWRSAV | #SLEEP_MODE  | ; Put the device into SLEEP mode      |

|--------|--------------|---------------------------------------|

| PWRSAV | #IDLE_MODE   | ; Put the device into IDLE mode       |

| BSET   | DSCON, #DSEN | ; Enable Deep Sleep                   |

| PWRSAV | #SLEEP_MODE  | ; Put the device into Deep SLEEP mode |

#### 10.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input, or two functional outputs configured as the same pin, there are no hardware enforced lock outs. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

#### 10.4.3.4 PPS Mapping Exceptions for PIC24FJ64GB0 Family Devices

Although the PPS registers allow for up to 32 remappable pins, not all of these are implemented in all devices. Exceptions and unimplemented RPn pins are listed in Table 10-4.

#### TABLE 10-4: REMAPPABLE PIN EXCEPTIONS FOR PIC24FJ64GB004 FAMILY DEVICES

| Device Pin | RP Pins (I/O) |                 |  |  |  |  |

|------------|---------------|-----------------|--|--|--|--|

| Count      | Total         | Unimplemented   |  |  |  |  |

| 28 Pins    | 15            | RP12, RP16-RP25 |  |  |  |  |

| 44 Pins    | 25            | RP12            |  |  |  |  |

#### 10.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit remapping lock

### 10.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW2<4>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

#### REGISTER 10-5: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 15 |     |     |       |       |       |       | bit 8 |

|        |     |     |       |       |       |       |       |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 12-8  | IC2R<4:0>: Assign Input Capture 2 (IC2) to Corresponding RPn or RPIn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                    |

| bit 4-0   | IC1R<4:0>: Assign Input Capture 1 (IC1) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 10-6: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

|           |     |     |       |       |       |       | bit C          |

|-----------|-----|-----|-------|-------|-------|-------|----------------|

| <br>bit 7 | —   | —   | IC3R4 | IC3R3 | IC3R2 | IC3R1 | IC3R0<br>bit ( |

| U-0       | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1          |

| bit 15    |     |     |       |       |       |       | bit 8          |

|           |     | —   | IC4R4 | IC4R3 | IC4R2 | IC4R1 | IC4R0          |

| U-0       | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1          |

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 IC4R<4:0>: Assign Input Capture 4 (IC4) to Corresponding RPn or RPIn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 IC3R<4:0>: Assign Input Capture 3 (IC3) to Corresponding RPn or RPIn Pin bits

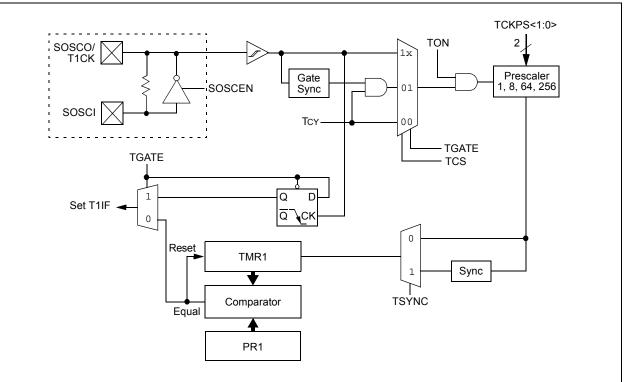

### 11.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### 18.7.1 USB OTG MODULE CONTROL REGISTERS

### REGISTER 18-3: U10TGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0 | U-0      | U-0                   | U-0                         | U-0      | U-0                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|-----------------------|-----------------------------|----------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _   | —        | —                     | —                           | —        | —                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | ·        |                       |                             | •        |                                                                                                              | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |                       |                             |          |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| U-0 | R-0, HSC | U-0                   | R-0, HSC                    | R-0, HSC | U-0                                                                                                          | R-0, HSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _   | LSTATE   | —                     | SESVD                       | SESEND   | _                                                                                                            | VBUSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | •        |                       | •                           | •        |                                                                                                              | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | _        | — — —<br>U-0 R-0, HSC | — — — —<br>U-0 R-0, HSC U-0 |          | -         -         -         -           U-0         R-0, HSC         U-0         R-0, HSC         R-0, HSC | -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - |

| Legend:           | U = Unimplemented bit, read as '0' |                                               |                    |  |  |

|-------------------|------------------------------------|-----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | ble bit HSC = Hardware Settable/Clearable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                          | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                            |

|          | <ul> <li>1 = No plug is attached, or a type B cable has been plugged into the USB receptacle</li> <li>0 = A type A plug has been plugged into the USB receptacle</li> </ul>               |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                   |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has NOT been stable for the previous 1 ms</li> </ul> |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_SESS_VLD (as defined in the USB OTG Specification) on the A or<br>B-device                                                                               |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                            |

| bit 2    | SESEND: B-Session End Indicator bit                                                                                                                                                       |

|          | 1 = The VBUS voltage is below VB_SESS_END (as defined in the USB OTG Specification) on the<br>B-device                                                                                    |

|          | 0 = The VBUS voltage is above VB_SESS_END on the B-device                                                                                                                                 |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 0    | VBUSVD: A-VBUS Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the USB OTG Specification) on the<br>A-device                                                                                    |

|          | 0 = The VBUS voltage is below VA_vBUS_vLD on the A-device                                                                                                                                 |

### REGISTER 18-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS | U-0 | R/K-0, HS | R/K-0, HS | R/K-0, HS | R/K-0, HS | R-0    | R/K-0, HS |

|-----------|-----|-----------|-----------|-----------|-----------|--------|-----------|

| STALLIF   | —   | RESUMEIF  | IDLEIF    | TRNIF     | SOFIF     | UERRIF | URSTIF    |

| bit 7     |     |           |           |           |           |        | bit 0     |

| Legend:           | U = Unimplemented bit, rea | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit | HS = Hardware Settable bit         |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                                                                                                                                                                |

|          | <ul> <li>1 = A STALL handshake was sent by the peripheral during the handshake phase of the transaction in<br/>Device mode</li> <li>0 = A STALL handshake has not been sent</li> </ul>                                                                                                                                                |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                            |

| bit 5    | -                                                                                                                                                                                                                                                                                                                                     |

| DIL 5    | <b>RESUMEIF:</b> Resume Interrupt bit 1 = A K-state was observed on the D+ or D- pin for 2.5 μs (differential '1' for low speed, differential '0' for full speed) 0 = No K-state was observed                                                                                                                                         |

| bit 4    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                                                                                                                                                                     |

|          | <ul> <li>1 = Idle condition was detected (constant Idle state of 3 ms or more)</li> <li>0 = No Idle condition was detected</li> </ul>                                                                                                                                                                                                 |

| bit 3    | TRNIF: Token Processing Complete Interrupt bit                                                                                                                                                                                                                                                                                        |

|          | <ul> <li>1 = Processing of current token was complete; read U1STAT register for endpoint information</li> <li>0 = Processing of current token was not complete; clear U1STAT register or load next token from STAT (clearing this bit causes the STAT FIFO to advance)</li> </ul>                                                     |

| bit 2    | SOFIF: Start-of-Frame Token Interrupt bit                                                                                                                                                                                                                                                                                             |

|          | <ul> <li>1 = A Start-of-Frame token received by the peripheral or the Start-of-Frame threshold was reached by<br/>the host</li> </ul>                                                                                                                                                                                                 |

|          | 0 = No Start-of-Frame token was received or threshold reached                                                                                                                                                                                                                                                                         |

| bit 1    | UERRIF: USB Error Condition Interrupt bit (read-only)                                                                                                                                                                                                                                                                                 |

|          | <ul> <li>1 = An unmasked error condition has occurred; only error states enabled in the U1EIE register can set<br/>this bit</li> </ul>                                                                                                                                                                                                |

|          | 0 = No unmasked error condition has occurred                                                                                                                                                                                                                                                                                          |

| bit 0    | URSTIF: USB Reset Interrupt bit                                                                                                                                                                                                                                                                                                       |

|          | <ul> <li>1 = Valid USB Reset has occurred for at least 2.5 μs; Reset state must be cleared before this bit can<br/>be reasserted</li> </ul>                                                                                                                                                                                           |

|          | 0 = No USB Reset has occurred. Individual bits can only be cleared by writing a '1' to the bit position<br>as part of a word write operation on the entire register. Using Boolean instructions or bitwise oper-<br>ations to write to a single bit position will cause all set bits at the moment of the write to become<br>cleared. |

| Note:    | Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits at the moment of the write to become cleared.                                           |

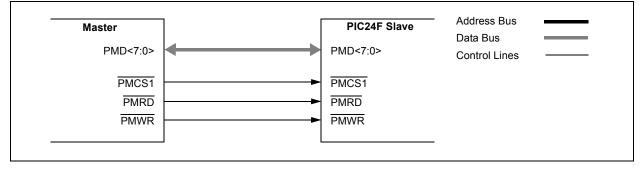

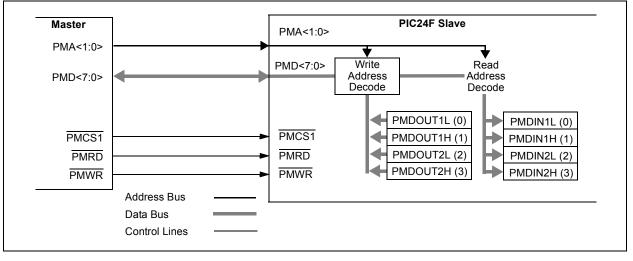

#### FIGURE 19-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

#### FIGURE 19-3: ADDRESSABLE PARALLEL SLAVE PORT EXAMPLE

#### TABLE 19-1: SLAVE MODE ADDRESS RESOLUTION

| PMA<1:0> | Output Register (Buffer) | Input Register (Buffer) |

|----------|--------------------------|-------------------------|

| 00       | PMDOUT1<7:0> (0)         | PMDIN1<7:0> (0)         |

| 01       | PMDOUT1<15:8> (1)        | PMDIN1<15:8> (1)        |

| 10       | PMDOUT2<7:0> (2)         | PMDIN2<7:0> (2)         |

| 11       | PMDOUT2<15:8> (3)        | PMDIN2<15:8> (3)        |

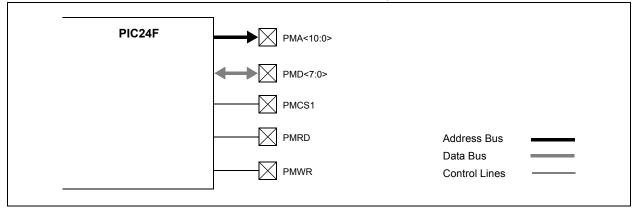

# FIGURE 19-4: MASTER MODE, DEMULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, SINGLE CHIP SELECT)

#### 25.2 Measuring Time

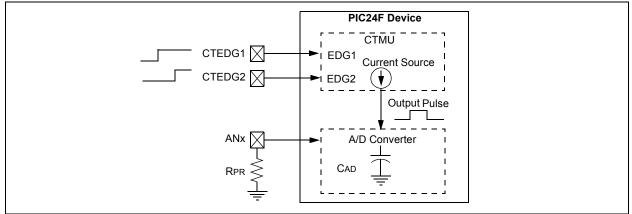

Time measurements on the pulse width can be similarly performed using the A/D module's internal capacitor (CAD) and a precision resistor for current calibration. Figure 25-2 shows the external connections used for time measurements, and how the CTMU and A/D modules are related in this application. This example also shows both edge events coming from the external CTEDG pins, but other configurations using internal edge sources are possible. For the smallest time measurements, select the internal A/D Channel 31, CH0S<4:0> = 11111. This minimizes any stray capacitance that may otherwise be associated with using an input pin, thus keeping the total capacitance to that of the A/D Converter itself (4-5 pF). A detailed discussion on measuring capacitance and time with the CTMU module is provided in the "PIC24F Family Reference Manual".

### 25.3 Pulse Generation and Delay

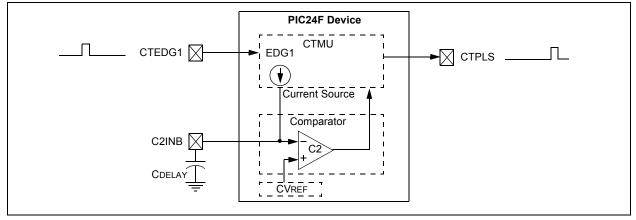

The CTMU module can also generate an output pulse with edges that are not synchronous with the device's system clock. More specifically, it can generate a pulse with a programmable delay from an edge event input to the module.

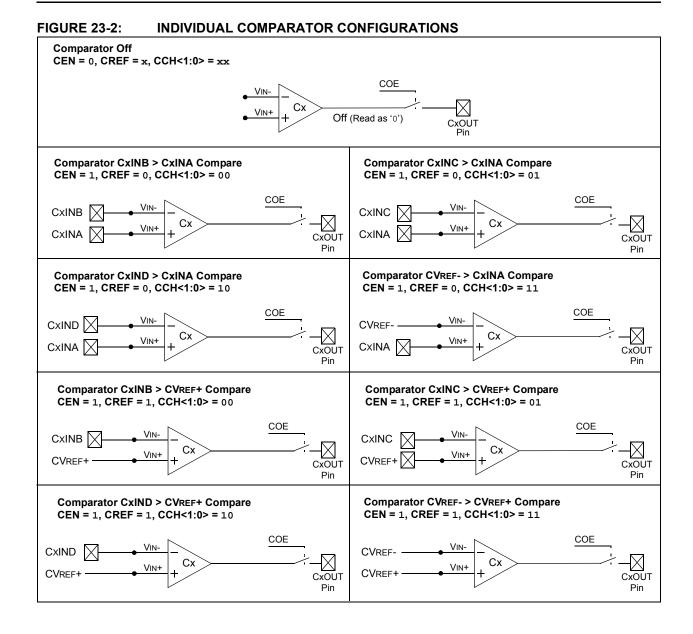

When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON<12>), the internal current source is connected to the B input of Comparator 2. A capacitor (CDELAY) is connected to the Comparator 2 pin, C2INB, and the comparator voltage reference, CVREF, is connected to C2INA. CVREF is then configured for a specific trip point. The module begins to charge CDELAY when an edge event is detected. When CDELAY charges above the CVREF trip point, a pulse is output on CTPLS. The length of the pulse delay is determined by the value of CDELAY and the CVREF trip point.

Figure 25-3 shows the external connections for pulse generation, as well as the relationship of the different analog modules required. While CTEDG1 is shown as the input pulse source, other options are available. A detailed discussion on pulse generation with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

# FIGURE 25-2: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

# FIGURE 25-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

| <b>TABLE 28-2:</b> | INSTRUCTION SET OVERVIEW | (CONTINUED) |  |

|--------------------|--------------------------|-------------|--|

|                    |                          |             |  |

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL  | Expr            | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL  | Wn              | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET  |                 | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE |                 | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW  | #lit10,Wn       | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC    | f               | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC    | f               | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE     | Ws,Wnd          | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM   | f               | f = FFFFh                               | 1             | 1              | None                     |

| -                    | SETM   | WREG            | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM   | Ws              | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL     | f               | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

|                      | SL     | f,WREG          | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Ws,Wd           | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB    | f               | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | f,WREG          | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | #lit10,Wn       | Wn = Wn – lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,#lit5,Wd     | Wd = Wb - lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | f,WREG          | WREG = f – WREG – $(\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      |        |                 | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              |                          |

|                      | SUBB   | #lit10,Wn       |                                         |               |                | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,Ws,Wd        | Wd = Wb - Ws - (C)                      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,#lit5,Wd     | Wd = Wb - lit5 - (C)                    | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR   | f               | f = WREG – f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | f,WREG          | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | f,WREG          | WREG = WREG – f – $(\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b | Wn              | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP   | Wn              | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

#### TABLE 29-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                    | Symbol | Min         | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| PIC24FJ64GB004 Family:                                                                                                    |        |             |             |      |      |

| Operating Junction Temperature Range                                                                                      | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation: | PD     | PINT + PI/O |             |      | W    |

| $PI/O = \Sigma (\{VDD - VOH\} \times IOH) + \Sigma (VOL \times IOL)$<br>Maximum Allowed Power Dissipation                 | Pdmax  | (           | Γj — Ta)/θj | A    | W    |

#### TABLE 29-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                              | Symbol | Тур  | Max | Unit | Notes    |

|---------------------------------------------|--------|------|-----|------|----------|

| Package Thermal Resistance, 300 mil SOIC    | θJA    | 49   |     | °C/W | (Note 1) |

| Package Thermal Resistance, 6x6x0.9 mm QFN  | θJA    | 33.7 | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 8x8x1 mm QFN    | θJA    | 28   | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 10x10x1 mm TQFP | θJA    | 39.3 | _   | °C/W | (Note 1) |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 29-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

| DC CHARACTERISTICS |                        |     | $\begin{array}{l} \mbox{Standard Operating Conditions: } 2.0V \ to \ 3.6V \ (unless \ otherwise \ state) \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ for \ Industrial \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \ for \ Extended \end{array}$ |            |                     |               |  |

|--------------------|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|---------------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Max | Units                                                                                                                                                                                                                                                                         | Conditions |                     |               |  |

| Idle Current (I    | IDLE) <sup>(2)</sup>   |     |                                                                                                                                                                                                                                                                               |            |                     |               |  |

| DC50               | 0.8                    | 1.0 | mA                                                                                                                                                                                                                                                                            | -40°C      |                     |               |  |

| DC50a              | 0.8                    | 1.0 | mA                                                                                                                                                                                                                                                                            | +25°C      | 2.0∨ <sup>(3)</sup> |               |  |

| DC50b              | 0.8                    | 1.0 | mA                                                                                                                                                                                                                                                                            | +85°C      | 2.00(*)             |               |  |

| DC50c              | 0.9                    | 1.1 | mA                                                                                                                                                                                                                                                                            | +125C      |                     |               |  |

| DC50d              | 1.1                    | 1.3 | mA                                                                                                                                                                                                                                                                            | -40°C      |                     | FRC (4 MIPS)  |  |

| DC50e              | 1.1                    | 1.3 | mA                                                                                                                                                                                                                                                                            | +25°C      | 3.3∨ <sup>(4)</sup> |               |  |

| DC50f              | 1.1                    | 1.3 | mA                                                                                                                                                                                                                                                                            | +85°C      |                     |               |  |

| DC50g              | 1.2                    | 1.4 | mA                                                                                                                                                                                                                                                                            | +125C      |                     |               |  |

| DC51               | 2.4                    | 8.0 | μΑ                                                                                                                                                                                                                                                                            | -40°C      |                     |               |  |