#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb002t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Р                             | in Numbe      | r                  |     |                 |                                                                                            |

|----------|-------------------------------|---------------|--------------------|-----|-----------------|--------------------------------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                                                |

| INT0     | 16                            | 13            | 43                 | I   | ST              | External Interrupt Input.                                                                  |

| MCLR     | 1                             | 26            | 18                 | Ι   | ST              | Master Clear (device Reset) Input. This line is brought low to cause a Reset.              |

| OSCI     | 9                             | 6             | 30                 | Ι   | ANA             | Main Oscillator Input Connection.                                                          |

| OSCO     | 10                            | 7             | 31                 | 0   | ANA             | Main Oscillator Output Connection.                                                         |

| PGEC1    | 5                             | 2             | 22                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP™ Programming Clock.                                      |

| PGED1    | 4                             | 1             | 21                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC2    | 22                            | 19            | 9                  | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED2    | 21                            | 18            | 8                  | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC3    | 3                             | 28            | 20                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED3    | 2                             | 27            | 19                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PMA0     | 10                            | 7             | 3                  | I/O | ST              | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 12                            | 9             | 2                  | I/O | ST              | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | —                             | _             | 27                 | 0   | _               | Parallel Master Port Address (Demultiplexed Master modes).                                 |

| PMA3     | _                             |               | 38                 | 0   | _               |                                                                                            |

| PMA4     | _                             |               | 37                 | 0   | _               |                                                                                            |

| PMA5     | _                             |               | 4                  | 0   | _               |                                                                                            |

| PMA6     | _                             |               | 5                  | 0   | _               |                                                                                            |

| PMA7     | _                             |               | 13                 | 0   | _               |                                                                                            |

| PMA8     | _                             |               | 32                 | 0   | _               |                                                                                            |

| PMA9     | _                             |               | 35                 | 0   | _               |                                                                                            |

| PMA10    | _                             |               | 12                 | 0   | _               |                                                                                            |

| PMCS1    | 9                             | 6             | 30                 | I/O | ST/TTL          | Parallel Master Port Chip Select 1 Strobe/Address Bit 15.                                  |

| PMBE     | 11                            | 8             | 36                 | 0   | _               | Parallel Master Port Byte Enable Strobe.                                                   |

| PMD0     | 4                             | 1             | 21                 | I/O | ST/TTL          | Parallel Master Port Data (Demultiplexed Master mode) or                                   |

| PMD1     | 5                             | 2             | 22                 | I/O | ST/TTL          | Address/Data (Multiplexed Master modes).                                                   |

| PMD2     | 6                             | 3             | 23                 | I/O | ST/TTL          | 1                                                                                          |

| PMD3     | 18                            | 15            | 1                  | I/O | ST/TTL          | 1                                                                                          |

| PMD4     | 17                            | 14            | 44                 | I/O | ST/TTL          | 1                                                                                          |

| PMD5     | 16                            | 13            | 43                 | I/O | ST/TTL          | 1                                                                                          |

| PMD6     | 3                             | 28            | 20                 | I/O | ST/TTL          | 1                                                                                          |

| PMD7     | 2                             | 27            | 19                 | I/O | ST/TTL          | 1                                                                                          |

| PMRD     | 24                            | 21            | 11                 | 0   | _               | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 7                             | 4             | 24                 | 0   | _               | Parallel Master Port Write Strobe.                                                         |

|          | TL = TTL inpu                 |               | 1                  | -   |                 | Schmitt Trigger input buffer                                                               |

| TABLE 1-2: | PIC24FJ64GB004 FAMILY PINOUT DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------------|

|            |                                                       |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

NOTES:

### 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                 | U-0                                                                                                     | U-0                                                                                                                                           | U-0            | U-0                 | U-0                | U-0               | R/W-0           |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|--------------------|-------------------|-----------------|--|--|--|--|--|

| _                   | —                                                                                                       | —                                                                                                                                             | _              | —                   | —                  | _                 | DC              |  |  |  |  |  |

| bit 15              |                                                                                                         |                                                                                                                                               |                |                     |                    |                   | bit 8           |  |  |  |  |  |

|                     |                                                                                                         |                                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| R/W-0 <sup>(*</sup> | <sup>1)</sup> R/W-0 <sup>(1)</sup>                                                                      | R/W-0 <sup>(1)</sup>                                                                                                                          | R-0            | R/W-0               | R/W-0              | R/W-0             | R/W-0           |  |  |  |  |  |

| IPL2 <sup>(2)</sup> | ) IPL1 <sup>(2)</sup>                                                                                   | IPL0 <sup>(2)</sup>                                                                                                                           | RA             | N                   | OV                 | Z                 | С               |  |  |  |  |  |

| bit 7               |                                                                                                         |                                                                                                                                               |                |                     |                    |                   | bit 0           |  |  |  |  |  |

|                     |                                                                                                         |                                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| Legend:             |                                                                                                         |                                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| R = Read            | able bit                                                                                                | W = Writable b                                                                                                                                | oit            | U = Unimplen        | nented bit, read   | as '0'            |                 |  |  |  |  |  |

| -n = Value          | e at POR                                                                                                | '1' = Bit is set                                                                                                                              |                | '0' = Bit is clea   | ared               | x = Bit is unkr   | nown            |  |  |  |  |  |

|                     |                                                                                                         |                                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| bit 15-9            | Unimplemen                                                                                              | nted: Read as '0                                                                                                                              | 3              |                     |                    |                   |                 |  |  |  |  |  |

| bit 8               |                                                                                                         | f Carry/Borrow b                                                                                                                              |                |                     |                    |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | out from the 4th l                                                                                                                            | ow-order bit ( | for byte-sized da   | ata) or 8th low-o  | order bit (for wo | ord-sized data) |  |  |  |  |  |

|                     | of the result occurred<br>0 = No carry out from the 4th or 8th low-order bit of the result has occurred |                                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| bit 7-5             | •                                                                                                       |                                                                                                                                               |                |                     |                    | cu                |                 |  |  |  |  |  |

|                     |                                                                                                         | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU interrupt priority level is 7 (15); user interrupts disabled |                |                     |                    |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | nterrupt priority l                                                                                                                           |                |                     | aloublea           |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | nterrupt priority l                                                                                                                           | • • •          |                     |                    |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | nterrupt priority le                                                                                                                          |                |                     |                    |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | nterrupt priority le<br>nterrupt priority le                                                                                                  |                |                     |                    |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | nterrupt priority l                                                                                                                           |                |                     |                    |                   |                 |  |  |  |  |  |

|                     | 000 <b>= CPU ir</b>                                                                                     | nterrupt priority l                                                                                                                           | evel is 0 (8)  |                     |                    |                   |                 |  |  |  |  |  |

| bit 4               | <b>RA:</b> REPEAT                                                                                       | Loop Active bit                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | oop in progress                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| 1.11.0              |                                                                                                         | oop not in progr                                                                                                                              | ess            |                     |                    |                   |                 |  |  |  |  |  |

| bit 3               | N: ALU Nega                                                                                             |                                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

|                     | 1 = Result wa                                                                                           | as negative                                                                                                                                   | (zero or posit | ive)                |                    |                   |                 |  |  |  |  |  |

| bit 2               | OV: ALU Ove                                                                                             | -                                                                                                                                             |                |                     |                    |                   |                 |  |  |  |  |  |

| 5112                |                                                                                                         | occurred for sig                                                                                                                              | ned (2's com   | olement) arithm     | etic in this arith | metic operatio    | n               |  |  |  |  |  |

|                     |                                                                                                         | ow has occurred                                                                                                                               |                |                     |                    |                   |                 |  |  |  |  |  |

| bit 1               | Z: ALU Zero                                                                                             | bit                                                                                                                                           |                |                     |                    |                   |                 |  |  |  |  |  |

|                     | •                                                                                                       | tion which effect                                                                                                                             |                |                     | •                  |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | 0 = The most recent operation which effects the Z bit has cleared it (i.e., a non-zero result)                                                |                |                     |                    |                   |                 |  |  |  |  |  |

| bit 0               | C: ALU Carry                                                                                            |                                                                                                                                               | Cignificant h  | it of the requilt o | oourrod            |                   |                 |  |  |  |  |  |

|                     |                                                                                                         | ut from the Most<br>out from the Most                                                                                                         |                |                     |                    |                   |                 |  |  |  |  |  |

|                     | -                                                                                                       |                                                                                                                                               | Ū              |                     |                    |                   |                 |  |  |  |  |  |

| Note 1:             | The IPL Status bi                                                                                       | -                                                                                                                                             |                | -                   | -                  |                   |                 |  |  |  |  |  |

| 2:                  | The IPL Status bi                                                                                       |                                                                                                                                               |                |                     |                    | n the CPU Inte    | errupt Priority |  |  |  |  |  |

|                     |                                                                                                         |                                                                                                                                               |                |                     | . 20 - 1.          |                   |                 |  |  |  |  |  |

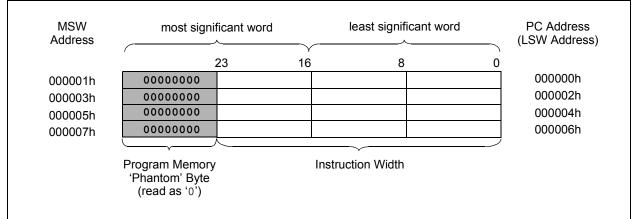

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h with the actual address for the start of code at 000002h.

PIC24F devices also have two interrupt vector tables, located from 000004h to 0000FFh and 000100h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### 4.1.3 FLASH CONFIGURATION WORDS

In PIC24FJ64GB004 family devices, the top four words of on-chip program memory are reserved for configuration information. On device Reset, the configuration information is copied into the appropriate Configuration registers. The addresses of the Flash Configuration Word for devices in the PIC24FJ64GB004 family are shown in Table 4-1. Their location in the memory map is shown with the other memory vectors in Figure 4-1.

The Configuration Words in program memory are a compact format. The actual Configuration bits are mapped in several different registers in the configuration memory space. Their order in the Flash Configuration Words do not reflect a corresponding arrangement in the configuration space. Additional details on the device Configuration Words are provided in **Section 26.1** "Configuration Bits".

# TABLE 4-1:FLASH CONFIGURATION<br/>WORDS FOR PIC24FJ64GB004<br/>FAMILY DEVICES

| Device       | Program<br>Memory<br>(Words) | Configuration<br>Word<br>Addresses |  |  |

|--------------|------------------------------|------------------------------------|--|--|

| PIC24FJ32GB0 | 11,008                       | 0057F8h:<br>0057FEh                |  |  |

| PIC24FJ64GB0 | 22,016                       | 00ABF8h:<br>00ABFEh                |  |  |

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

#### TABLE 4-18: USB OTG REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15                                   | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                                | Bit 8 | Bit 7               | Bit 6                   | Bit 5 | Bit 4    | Bit 3  | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|-----------|------|------------------------------------------|--------|--------|--------|--------|--------|--------------------------------------|-------|---------------------|-------------------------|-------|----------|--------|--------|---------|--------|---------------|

| U1EP0     | 04AA | —                                        | —      | _      | —      | —      | _      | —                                    | —     | LSPD <sup>(1)</sup> | RETRYDIS <sup>(1)</sup> | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP1     | 04AC | _                                        | -      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP2     | 04AE | —                                        |        | _      | _      | —      | _      | _                                    | _     | —                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP3     | 04B0 | _                                        | -      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP4     | 04B2 | _                                        | Ι      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP5     | 04B4 | _                                        | -      | _      | _      | _      | _      | _                                    |       | -                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP6     | 04B6 | —                                        | _      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP7     | 04B8 | _                                        | -      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP8     | 04BA | —                                        | _      | _      | _      | _      | _      | _                                    |       | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP9     | 04BC | _                                        | _      | _      | _      | _      | _      | _                                    |       | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP10    | 04BE | _                                        | -      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP11    | 04C0 | —                                        | _      | _      | _      | _      | _      | _                                    |       | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP12    | 04C2 | —                                        | _      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP13    | 04C4 | _                                        | -      | _      | _      | _      | _      | _                                    | _     | _                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP14    | 04C6 | —                                        | _      | _      | _      | _      |        | —                                    |       |                     | —                       | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1EP15    | 04C8 | _                                        | _      | _      | _      | _      |        | _                                    |       | -                   | —                       | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000          |

| U1PWMRRS  | 04CC | USB Power Supply PWM Duty Cycle Register |        |        |        |        |        | USB Power Supply PWM Period Register |       |                     |                         |       |          | 0000   |        |         |        |               |

| U1PWMCON  | 04CE | PWMEN                                    | —      | _      | _      | _      |        | PWMPOL                               | CNTEN | _                   | —                       | _     | _        | —      | _      | -       | _      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note** 1: Alternate register or bit definitions when the module is operating in Host mode.

2: This register is available in Host mode only.

#### TABLE 4-19: PARALLEL MASTER/SLAVE PORT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                              | Bit 13 | Bit 12  | Bit 11  | Bit 10                | Bit 9                | Bit 8                | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                | Bit 2                | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|-----------------------------------------------------|--------|---------|---------|-----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------|--------|---------------|

| PMCON     | 0600 | PMPEN  | _                                                   | PSIDL  | ADRMUX1 | ADRMUX0 | PTBEEN                | PTWREN               | PTRDEN               | CSF1                 | CSF0                 | ALP                  | _                    | CS1P                 | BEP                  | WRSP   | RDSP   | 0000          |

| PMMODE    | 0602 | BUSY   | IRQM1                                               | IRQM0  | INCM1   | INCM0   | MODE16                | MODE1                | MODE0                | WAITB1               | WAITB0               | WAITM3               | WAITM2               | WAITM1               | WAITM0               | WAITE1 | WAITE0 | 0000          |

| PMADDR    | 0604 | -      | CS1                                                 | _      | _       | _       | ADDR10 <sup>(1)</sup> | ADDR9 <sup>(1)</sup> | ADDR8 <sup>(1)</sup> | ADDR7 <sup>(1)</sup> | ADDR6 <sup>(1)</sup> | ADDR5 <sup>(1)</sup> | ADDR4 <sup>(1)</sup> | ADDR3 <sup>(1)</sup> | ADDR2 <sup>(1)</sup> | ADDR1  | ADDR0  | 0000          |

| PMDOUT1   |      |        | Parallel Port Data Out Register 1 (Buffers 0 and 1) |        |         |         |                       |                      |                      |                      |                      | 0000                 |                      |                      |                      |        |        |               |

| PMDOUT2   | 0606 |        | Parallel Port Data Out Register 2 (Buffers 2 and 3) |        |         |         |                       |                      |                      |                      |                      | 0000                 |                      |                      |                      |        |        |               |

| PMDIN1    | 0608 |        |                                                     |        |         |         | Pa                    | arallel Port I       | Data In Regi         | ister 1 (Buffe       | ers 0 and 1)         |                      |                      |                      |                      |        |        | 0000          |

| PMDIN2    | 060A |        |                                                     |        |         |         | Pa                    | arallel Port I       | Data In Regi         | ister 2 (Buffe       | ers 2 and 3)         |                      |                      |                      |                      |        |        | 0000          |

| PMAEN     | 060C | -      | PTEN14                                              | _      | _       | _       | PTEN10 <sup>(1)</sup> | PTEN9 <sup>(1)</sup> | PTEN8 <sup>(1)</sup> | PTEN7 <sup>(1)</sup> | PTEN6 <sup>(1)</sup> | PTEN5 <sup>(1)</sup> | PTEN4 <sup>(1)</sup> | PTEN3 <sup>(1)</sup> | PTEN2 <sup>(1)</sup> | PTEN1  | PTEN0  | 0000          |

| PMSTAT    | 060E | IBF    | IBOV                                                | _      | _       | IB3F    | IB2F                  | IB1F                 | IB0F                 | OBE                  | OBUF                 | _                    | _                    | OB3E                 | OB2E                 | OB1E   | OB0E   | 0000          |

PIC24FJ64GB004 FAMILY

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits are not available on 28-pin devices; read as '0'.

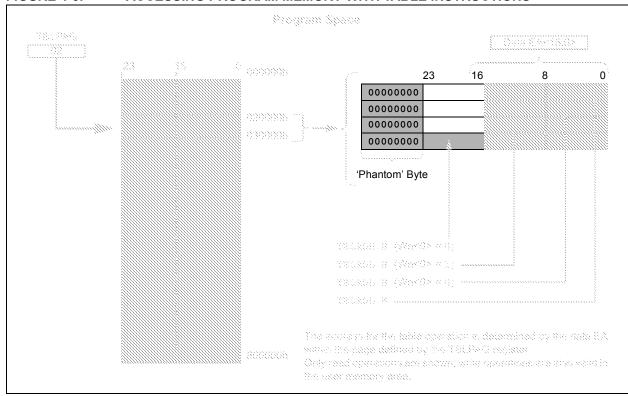

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when the byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only table read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

### FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

### 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features    |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |

|       | Section 4. "Program Memory"                |  |  |  |  |  |  |

|       | (DS39715).                                 |  |  |  |  |  |  |

The PIC24FJ64GB004 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 2.35V. (If the regulator is disabled, VDDCORE must be over 2.25V.)

It can be programmed in four ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ64GB004 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

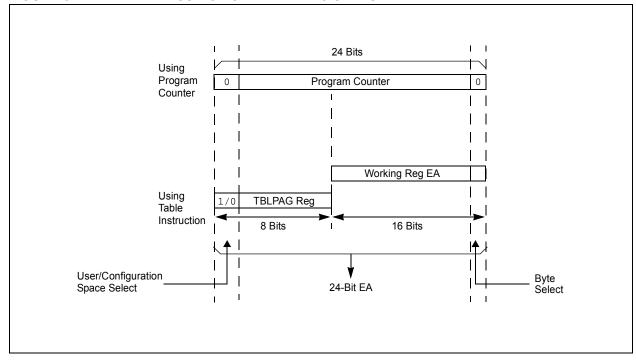

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| R/W-0, HS        | R/W-0, HS                                           | U-0                                                    | U-0                                                       | U-0                  | R/CO-0, HS                  | R/W-0, HS        | R/W-0         |  |  |  |

|------------------|-----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|----------------------|-----------------------------|------------------|---------------|--|--|--|

| TRAPR            | IOPUWR                                              | _                                                      |                                                           | —                    | DPSLP                       | СМ               | PMSLP         |  |  |  |

| bit 15           |                                                     |                                                        |                                                           |                      |                             |                  | bita          |  |  |  |

| R/W-0, HS        | R/W-0, HS                                           | R/W-0                                                  | R/W-0, HS                                                 | R/W-0, HS            | R/W-0, HS                   | R/W-1, HS        | R/W-1, HS     |  |  |  |

| EXTR             | SWR                                                 | SWDTEN <sup>(2)</sup>                                  | WDTO                                                      | SLEEP                | IDLE                        | BOR              | POR           |  |  |  |

| bit 7            |                                                     |                                                        |                                                           |                      |                             |                  | bit           |  |  |  |

| Legend:          |                                                     | CO = Clearab                                           | le Only bit                                               | HS = Hardwa          | re Settable bit             |                  |               |  |  |  |

| R = Readable     | e bit                                               | W = Writable                                           | -                                                         |                      | nented bit, read            | as '0'           |               |  |  |  |

| -n = Value at    |                                                     | '1' = Bit is set                                       |                                                           | '0' = Bit is clea    |                             | x = Bit is unkn  | own           |  |  |  |

| bit 15<br>bit 14 | 1 = A Trap Co<br>0 = A Trap Co                      | Reset Flag bit<br>onflict Reset ha<br>onflict Reset ha | s occurred<br>s not occurred                              | Access Report        | Elog bit                    |                  |               |  |  |  |

| DIL 14           | 1 = An illegal<br>Pointer ca                        | opcode detect<br>aused a Reset                         | Uninitialized W<br>ion, an illegal ad<br>nitialized W Res | ddress mode o        | r uninitialized W           | / register used  | as an Addres  |  |  |  |

| bit 13-11        | •                                                   | ted: Read as '                                         |                                                           |                      |                             |                  |               |  |  |  |

| bit 10           | •                                                   | DPSLP: Deep Sleep Mode Flag bit                        |                                                           |                      |                             |                  |               |  |  |  |

|                  |                                                     | ep has occurre<br>ep has not occu                      |                                                           |                      |                             |                  |               |  |  |  |

| bit 9            | 1 = A Configu                                       | ration Word Mi                                         | match Reset Fl<br>smatch Reset I<br>smatch Reset I        | has occurred         | ed                          |                  |               |  |  |  |

| bit 8            | 1 = Program                                         | memory bias v                                          | Power During Sl<br>oltage remains<br>oltage is powered    | powered durin        | g Sleep<br>Sleep and the vo | oltage regulator | enters Standb |  |  |  |

| bit 7            | 1 = A Master                                        |                                                        | R) Pin bit<br>et has occurre<br>et has not occu           |                      |                             |                  |               |  |  |  |

| bit 6            | <b>SWR:</b> Softwar<br>1 = A RESET i                | re Reset (Instruinstruction has                        | uction) Flag bit<br>been executed<br>not been execu       |                      |                             |                  |               |  |  |  |

| bit 5            | <b>SWDTEN:</b> So<br>1 = WDT is er<br>0 = WDT is di | nabled                                                 | Disable of WD1                                            | F bit <sup>(2)</sup> |                             |                  |               |  |  |  |

| bit 4            | 1 = WDT time                                        | ndog Timer Tim<br>-out has occur<br>-out has not oo    | red                                                       |                      |                             |                  |               |  |  |  |

| bit 3            | 1 = Device ha                                       | e From Sleep F<br>s been in Slee<br>s not been in S    | p mode                                                    |                      |                             |                  |               |  |  |  |

| bit 2            | IDLE: Wake-u                                        | ip From Idle Fl<br>s been in Idle i                    | ag bit<br>mode                                            |                      |                             |                  |               |  |  |  |

#### cause a device Reset. 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### REGISTER 7-1: SR: ALU STATUS REGISTER (IN CPU)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0               |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

|        | —   | —   | —   | _   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0                 | R/W-0                 | R/W-0                 | R-0               | R/W-0            | R/W-0             | R/W-0            | R/W-0            |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | 0V <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU interrupt priority level is 7 (15). User interrupts disabled. 110 = CPU interrupt priority level is 6 (14) 101 = CPU interrupt priority level is 5 (13) 100 = CPU interrupt priority level is 4 (12) 011 = CPU interrupt priority level is 3 (11) 010 = CPU interrupt priority level is 2 (10) 001 = CPU interrupt priority level is 1 (9) 000 = CPU interrupt priority level is 0 (8)

- **Note 1:** See Register 3-1 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

- **2:** The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the interrupt priority level if IPL3 = 1.

- 3: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

| REGISTER 7-2: | CORCON: CPU CONTROL REGISTER |

|---------------|------------------------------|

|               |                              |

| U-0    | U-0 | U-0 | U-0 | U-0                 | U-0                | U-0 | U-0   |

|--------|-----|-----|-----|---------------------|--------------------|-----|-------|

| —      | —   | —   | _   | _                   | —                  | —   | —     |

| bit 15 | •   |     |     |                     | •                  | •   | bit 8 |

|        |     |     |     |                     |                    |     |       |

| U-0    | U-0 | U-0 | U-0 | R/C-0               | R/W-0              | U-0 | U-0   |

| _      | —   | _   | _   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | _   | —     |

| bit 7  |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU interrupt priority level is greater than 7 0 = CPU interrupt priority level is 7 or less

- **Note 1:** See Register 3-2 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

| U-0            | U-0             | R/W-0                               | U-0             | U-0               | U-0  | R/W-0           | U-0             |

|----------------|-----------------|-------------------------------------|-----------------|-------------------|------|-----------------|-----------------|

|                | _               | PMPIE                               |                 | _                 |      | OC5IE           | _               |

| bit 15         |                 |                                     |                 |                   |      |                 | bit 8           |

| DAALO          | DAVA            | DAALO                               | 11.0            |                   |      | DAMA            | DAMA            |

| R/W-0<br>IC5IE | R/W-0           | R/W-0<br>IC3IE                      | U-0             | U-0               | U-0  | R/W-0<br>SPI2IE | R/W-0<br>SPF2IE |

| bit 7          | 104IE           | ICSIE                               | —               |                   | _    | SFIZIE          | bit C           |

|                |                 |                                     |                 |                   |      |                 |                 |

| _egend:        |                 |                                     |                 |                   |      |                 |                 |

| R = Readab     |                 | W = Writable                        | oit             | U = Unimplem      | -    | d as '0'        |                 |

| -n = Value a   | t POR           | '1' = Bit is set                    |                 | '0' = Bit is clea | ared | x = Bit is unkr | nown            |

| bit 15-14      | Unimplemen      | ted: Read as 'd                     | )'              |                   |      |                 |                 |

| bit 13         | •               | llel Master Port                    |                 | ble bit           |      |                 |                 |

|                |                 | request is enable                   | -               |                   |      |                 |                 |

|                |                 | request is not e                    |                 |                   |      |                 |                 |

| oit 12-10      | Unimplemen      | ted: Read as 'd                     | )'              |                   |      |                 |                 |

| oit 9          | OC5IE: Outpu    | ut Compare Cha                      | annel 5 Interru | upt Enable bit    |      |                 |                 |

|                |                 | request is enab<br>request is not e |                 |                   |      |                 |                 |

| bit 8          | -               | ted: Read as '(                     |                 |                   |      |                 |                 |

| bit 7          | •               | Capture Channe                      |                 | Enable bit        |      |                 |                 |

|                |                 | request is enab                     | -               |                   |      |                 |                 |

|                | 0 = Interrupt r | request is not e                    | nabled          |                   |      |                 |                 |

| bit 6          | •               | Capture Channe                      | •               | Enable bit        |      |                 |                 |

|                |                 | request is enab<br>request is not e |                 |                   |      |                 |                 |

| bit 5          | •               | Capture Channe                      |                 | nable bit         |      |                 |                 |

|                | -               | request is enable                   | -               |                   |      |                 |                 |

|                |                 | request is not e                    |                 |                   |      |                 |                 |

| bit 4-2        | Unimplemen      | ted: Read as 'd                     | )'              |                   |      |                 |                 |

| bit 1          | SPI2IE: SPI2    | Event Interrupt                     | Enable bit      |                   |      |                 |                 |

|                |                 | request is enab                     |                 |                   |      |                 |                 |

| -: 0           |                 | request is not e                    |                 |                   |      |                 |                 |

| oit 0          |                 | 2 Fault Interrupt                   | Enable bit      |                   |      |                 |                 |

|                | 1 - Internuct   | request is enab                     | ad              |                   |      |                 |                 |

#### REGISTER 7-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| _                           | R/W-1                                                                                                                         | R/W-0                                                                                                                                         | R/W-0                                                                               | U-0                               | R/W-1            | R/W-0           | R/W-0  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------|------------------|-----------------|--------|--|--|--|

|                             | T4IP2                                                                                                                         | T4IP1                                                                                                                                         | T4IP0                                                                               | _                                 | OC4IP2           | OC4IP1          | OC4IP0 |  |  |  |

| bit 15                      |                                                                                                                               | •                                                                                                                                             | •                                                                                   |                                   |                  | •               | bit 8  |  |  |  |

| U-0                         | R/W-1                                                                                                                         | R/W-0                                                                                                                                         | R/W-0                                                                               | U-0                               | U-0              | U-0             | U-0    |  |  |  |

| 0-0                         | OC3IP2                                                                                                                        | OC3IP1                                                                                                                                        | OC3IP0                                                                              | 0-0                               | 0-0              | 0-0             | 0-0    |  |  |  |

| <br>bit 7                   | UC3IF2                                                                                                                        | UC3IF I                                                                                                                                       | OCSIFU                                                                              | _                                 | _                |                 | bit (  |  |  |  |

|                             |                                                                                                                               |                                                                                                                                               |                                                                                     |                                   |                  |                 |        |  |  |  |

| Legend:                     |                                                                                                                               |                                                                                                                                               |                                                                                     |                                   |                  |                 |        |  |  |  |

| R = Readab                  |                                                                                                                               | W = Writable                                                                                                                                  |                                                                                     |                                   | mented bit, read | l as '0'        |        |  |  |  |

| -n = Value a                | It POR                                                                                                                        | '1' = Bit is set                                                                                                                              |                                                                                     | '0' = Bit is cle                  | eared            | x = Bit is unkr | iown   |  |  |  |

|                             |                                                                                                                               |                                                                                                                                               | - 1                                                                                 |                                   |                  |                 |        |  |  |  |

| bit 15                      | -                                                                                                                             | nted: Read as '                                                                                                                               |                                                                                     |                                   |                  |                 |        |  |  |  |

| bit 14-12                   |                                                                                                                               | imer4 Interrupt                                                                                                                               | •                                                                                   |                                   |                  |                 |        |  |  |  |

|                             | 111 = Interru                                                                                                                 | pt is Priority 7 (                                                                                                                            | highest priorit                                                                     | y interrupt)                      |                  |                 |        |  |  |  |

|                             | •                                                                                                                             |                                                                                                                                               |                                                                                     |                                   |                  |                 |        |  |  |  |

|                             | •                                                                                                                             |                                                                                                                                               |                                                                                     |                                   |                  |                 |        |  |  |  |

|                             |                                                                                                                               | pt is Priority 1                                                                                                                              |                                                                                     |                                   |                  |                 |        |  |  |  |

|                             | 000 = Interru                                                                                                                 | pt source is dis                                                                                                                              | abled                                                                               |                                   |                  |                 |        |  |  |  |

|                             | Unimplemented: Read as '0'                                                                                                    |                                                                                                                                               |                                                                                     |                                   |                  |                 |        |  |  |  |

| bit 11                      | Unimplemen                                                                                                                    | nted: Read as '                                                                                                                               | 0'                                                                                  |                                   |                  |                 |        |  |  |  |

|                             | -                                                                                                                             | nted: Read as '<br>: Output Compa                                                                                                             |                                                                                     | Interrupt Priorif                 | ty bits          |                 |        |  |  |  |

|                             | OC4IP<2:0>:                                                                                                                   |                                                                                                                                               | are Channel 4                                                                       |                                   | ty bits          |                 |        |  |  |  |

|                             | OC4IP<2:0>:                                                                                                                   | : Output Compa                                                                                                                                | are Channel 4                                                                       |                                   | ty bits          |                 |        |  |  |  |

|                             | OC4IP<2:0>:                                                                                                                   | : Output Compa                                                                                                                                | are Channel 4                                                                       |                                   | ty bits          |                 |        |  |  |  |

|                             | OC4IP<2:0>:<br>111 = Interru                                                                                                  | : Output Compa<br>pt is Priority 7 (                                                                                                          | are Channel 4                                                                       |                                   | ty bits          |                 |        |  |  |  |

|                             | OC4IP<2:0>:<br>111 = Interru<br>001 = Interru                                                                                 | : Output Compa                                                                                                                                | are Channel 4<br>highest priorit                                                    |                                   | ty bits          |                 |        |  |  |  |

| bit 11<br>bit 10-8<br>bit 7 | OC4IP<2:0>:<br>111 = Interru                                                                                                  | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                                      | are Channel 4<br>highest priorit<br>abled                                           |                                   | ty bits          |                 |        |  |  |  |

| bit 10-8<br>bit 7           | OC4IP<2:0>:<br>111 = Interru                                                                                                  | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>hted:</b> Read as '                                        | are Channel 4<br>highest priorit<br>abled<br>0'                                     | y interrupt)                      |                  |                 |        |  |  |  |

| bit 10-8                    | OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:                                   | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                  | are Channel 4<br>highest priorit<br>abled<br>0'<br>are Channel 3                    | y interrupt)<br>Interrupt Priorit |                  |                 |        |  |  |  |

| bit 10-8<br>bit 7           | OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:                                   | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>: Output Compa                             | are Channel 4<br>highest priorit<br>abled<br>0'<br>are Channel 3                    | y interrupt)<br>Interrupt Priorit |                  |                 |        |  |  |  |

| bit 10-8<br>bit 7           | OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:                                   | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>: Output Compa                             | are Channel 4<br>highest priorit<br>abled<br>0'<br>are Channel 3                    | y interrupt)<br>Interrupt Priorit |                  |                 |        |  |  |  |

| bit 10-8<br>bit 7           | OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru                  | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>: Output Compa<br>pt is Priority 7 ( | are Channel 4<br>highest priorit<br>abled<br>0'<br>are Channel 3                    | y interrupt)<br>Interrupt Priorit |                  |                 |        |  |  |  |

| bit 10-8<br>bit 7           | OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru | : Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>: Output Compa                             | are Channel 4<br>highest priorit<br>abled<br>o'<br>are Channel 3<br>highest priorit | y interrupt)<br>Interrupt Priorit |                  |                 |        |  |  |  |

#### REGISTER 7-23: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

#### REGISTER 10-7: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | _   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | IC5R4 | IC5R3 | IC5R2 | IC5R1 | IC5R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |