#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb004-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Р                             | in Numbe      | r                  |     |                  |                                                       |

|----------|-------------------------------|---------------|--------------------|-----|------------------|-------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer  | Description                                           |

| RP0      | 4                             | 1             | 21                 | I/O | ST               | Remappable Peripheral (input or output).              |

| RP1      | 5                             | 2             | 22                 | I/O | ST               |                                                       |

| RP2      | 6                             | 3             | 23                 | I/O | ST               |                                                       |

| RP3      | 7                             | 4             | 24                 | I/O | ST               |                                                       |

| RP4      | 11                            | 8             | 33                 | I/O | ST               |                                                       |

| RP5      | 2                             | 27            | 19                 | I/O | ST               |                                                       |

| RP6      | 3                             | 28            | 20                 | I/O | ST               |                                                       |

| RP7      | 16                            | 13            | 43                 | I/O | ST               |                                                       |

| RP8      | 17                            | 14            | 44                 | I/O | ST               |                                                       |

| RP9      | 18                            | 15            | 1                  | I/O | ST               |                                                       |

| RP10     | 21                            | 18            | 8                  | I/O | ST               |                                                       |

| RP11     | 22                            | 19            | 9                  | I/O | ST               |                                                       |

| RP13     | 24                            | 21            | 11                 | I/O | ST               |                                                       |

| RP14     | 25                            | 22            | 14                 | I/O | ST               |                                                       |

| RP15     | 26                            | 23            | 15                 | I/O | ST               |                                                       |

| RP16     | —                             | _             | 25                 | I/O | ST               |                                                       |

| RP17     | —                             | _             | 26                 | I/O | ST               |                                                       |

| RP18     | —                             | _             | 27                 | I/O | ST               |                                                       |

| RP19     | —                             | _             | 36                 | I/O | ST               |                                                       |

| RP20     | —                             | _             | 37                 | I/O | ST               |                                                       |

| RP21     | —                             | _             | 38                 | I/O | ST               |                                                       |

| RP22     | —                             | _             | 2                  | I/O | ST               | -                                                     |

| RP23     | —                             | _             | 3                  | I/O | ST               | -                                                     |

| RP24     | —                             | _             | 4                  | I/O | ST               | -                                                     |

| RP25     | —                             | —             | 5                  | I/O | ST               |                                                       |

| RTCC     | 7                             | 4             | 24                 | 0   | —                | Real-Time Clock Alarm/Seconds Pulse Output.           |

| SESSEND  | 24                            | 21            | 11                 | I   | ST               | USB VBUS Session End Status Input.                    |

| SESSVLD  | 3                             | 28            | 20                 | I   | ST               | USB VBUS Session Valid Status Input.                  |

| SCL1     | 17                            | 14            | 44                 | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output.           |

| SCL2     | 7                             | 4             | 24                 | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output.           |

| SDA1     | 18                            | 15            | 1                  | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                               |

| SDA2     | 6                             | 3             | 23                 | I/O | l <sup>2</sup> C | I2C2 Data Input/Output.                               |

| SOSCI    | 11                            | 8             | 33                 | I   | ANA              | Secondary Oscillator/Timer1 Clock Input.              |

| SOSCO    | 12                            | 9             | 34                 | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.             |

| T1CK     | 12                            | 9             | 34                 | I   | ST               | Timer1 Clock Input.                                   |

| ТСК      | 17                            | 14            | 13                 | I   | ST               | JTAG Test Clock Input.                                |

| TDI      | 16                            | 13            | 35                 | I   | ST               | JTAG Test Data Input.                                 |

| TDO      | 18                            | 15            | 32                 | 0   | —                | JTAG Test Data Output.                                |

| TMS      | 14                            | 11            | 12                 | I   | ST               | JTAG Test Mode Select Input.                          |

| USBID    | 14                            | 11            | 41                 | I   | ST               | USB OTG ID (OTG mode only).                           |

| USBOEN   | 17                            | 14            | 44                 | 0   | —                | USB Output Enable Control (for external transceiver). |

TABLE 1-2. PIC24F.I64GB004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer Legend:

ANA = Analog level input/output

$I^2C^{TM} = I^2C/SMBus$  input buffer

ST = Schmitt Trigger input buffer

### 10.3 Input Change Notification

The input change notification function of the I/O ports allows the PIC24FJ64GB004 family of devices to generate interrupt requests to the processor in response to a change of state on selected input pins. This feature is capable of detecting input Change-of-States (COS) even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 29 external inputs that may be selected (enabled) for generating an interrupt request on a Change-of-State.

Registers, CNEN1 and CNEN2, contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin has a weak pull-up connected to it. The pull-up acts as a current source that is connected to the pin. This eliminates the need for external resistors when push button or keypad devices are connected. The pull-ups are separately enabled using the CNPU1 and CNPU2 registers (for pull-ups). Each CN pin has individual control bits for its pull-up. Setting a control bit enables the weak pull-up for the corresponding pin.

When the internal pull-up is selected, the pin pulls up to VDD-0.7V (typical). Make sure that there is no external pull-up source when the internal pull-ups are enabled, as the voltage difference can cause a current path.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

### 10.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select feature provides an alternative to these choices by enabling the user's peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 10.4.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 25 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" in their full pin designation, where "n" is the remappable pin number.

See Table 1-2 for a summary of pinout options in each package offering.

#### 10.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

Peripheral Pin Select is not available for  $I^2C^{TM}$  change notification inputs, RTCC alarm outputs or peripherals with analog inputs.

A key difference between pin select and non pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 10.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (for example, OC and UART transmit) take priority over any general purpose digital functions permanently tied to that pin, such as PMP and port I/O. Specialized digital outputs, such as USB functionality, take priority over PPS outputs on the same pin. The pin diagrams at the beginning of this data sheet list peripheral outputs in order of priority. Refer to them for priority concerns on a particular pin.

Unlike devices with fixed peripherals, pin-selectable peripheral inputs never take ownership of a pin. The pin's output buffer is controlled by the pin's TRIS bit setting, or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly, reading the input. If an analog function is enabled on the same pin, the pin-selectable input will be disabled.

| EXAMPLE 10-2: CONFIGURIN | G UART1 INPUT AND OUTPUT FUNCTIONS IN ASSEMBLY CODE |

|--------------------------|-----------------------------------------------------|

|--------------------------|-----------------------------------------------------|

| ;unlock    | registers                        |

|------------|----------------------------------|

| push       | wl;                              |

| push       | w2;                              |

| push       | w3;                              |

| mov        | #OSCCON, w1;                     |

| mov        | #0x46, w2;                       |

| mov        | #0x57, w3;                       |

| mov.b      | w2, [w1];                        |

| mov.b      | w3, [w1];                        |

| bclr       | OSCCON, #6;                      |

|            |                                  |

| ; Configur | e Input Functions (Table10-2)    |

| ; Assign U | 1CTS To Pin RP1, U1RX To Pin RP0 |

| mov        | #0x0100, w1;                     |

| mov        | w1,RPINR18;                      |

|            |                                  |

| ; Configur | e Output Functions (Table 10-3)  |

| ; Assign U | 1RTS TO Pin RP3, U1TX TO Pin RP2 |

| mov        | #0x0403, w1;                     |

| mov        | w1, RPOR1;                       |

|            |                                  |

| ;lock      | registers                        |

| mov        | #OSCCON, w1;                     |

| mov        | #0x46, w2;                       |

| mov        | #0x57, w3;                       |

| mov.b      | w2, [w1];                        |

| mov.b      | w3, [w1];                        |

| bset       | OSCCON, #6;                      |

| pop        | w3;                              |

|            | _                                |

| рор        | w2;                              |

| рор<br>рор | w2;<br>w1;                       |

#### EXAMPLE 10-3: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS IN 'C'

```

//unlock registers

__builtin_write_OSCCONL(OSCCON & 0xBF);

// Configure Input Functions (Table 9-1)

// Assign UIRX To Pin RP0

RPINR18bits.U1RXR = 0;

// Assign UICTS To Pin RP1

RPINR18bits.U1CTSR = 1;

// Configure Output Functions (Table 9-2)

// Assign U1TX To Pin RP2

RPOR1bits.RP2R = 3;

// Assign U1RTS To Pin RP3

RPOR1bits.RP3R = 4;

//lock registers

__builtin_write_OSCCONL(OSCCON | 0x40);

```

#### REGISTER 10-19: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0                               | U-0 | U-0              | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-----|------------------|------------------------------------|-------------------|-------|-----------------|-------|

|                                   |     | —                | RP9R4                              | RP9R3             | RP9R2 | RP9R1           | RP9R0 |

| bit 15                            |     |                  |                                    |                   |       |                 | bit 8 |

|                                   |     |                  |                                    |                   |       |                 |       |

| U-0                               | U-0 | U-0              | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |     | —                | RP8R4                              | RP8R3             | RP8R2 | RP8R1           | RP8R0 |

| bit 7                             |     |                  |                                    |                   |       |                 | bit 0 |

|                                   |     |                  |                                    |                   |       |                 |       |

| Legend:                           |     |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |     | oit              | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at I                   | POR | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

bit 15-13 Unimplemented: Read as '0'

- bit 12-8**RP9R<4:0>:** RP9 Output Pin Mapping bits<br/>Peripheral output number n is assigned to pin, RP9 (see Table 10-3 for peripheral function numbers).bit 7-5**Unimplemented:** Read as '0'bit 4-0**RP8R<4:0>:** RP8 Output Pin Mapping bits

- Peripheral output number n is assigned to pin, RP8 (see Table 10-3 for peripheral function numbers).

#### REGISTER 10-20: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** RP11 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP11 (see Table 10-3 for peripheral function numbers).

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP10R<4:0>:** RP10 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP10 (see Table 10-3 for peripheral function numbers).

## REGISTER 12-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER<sup>(3)</sup>

| R/W-0              | U-0                           | R/W-0                          | U-0   | U-0 | U-0 | U-0                           | U-0   |

|--------------------|-------------------------------|--------------------------------|-------|-----|-----|-------------------------------|-------|

| TON <sup>(1)</sup> | —                             | TSIDL <sup>(1)</sup>           | —     | —   | —   | —                             | —     |

| bit 15             |                               |                                |       |     |     |                               | bit 8 |

|                    |                               |                                |       |     |     |                               |       |

|                    |                               |                                |       |     |     |                               |       |

| U-0                | R/W-0                         | R/W-0                          | R/W-0 | U-0 | U-0 | R/W-0                         | U-0   |

| U-0                | R/W-0<br>TGATE <sup>(1)</sup> | R/W-0<br>TCKPS1 <sup>(1)</sup> |       | U-0 | U-0 | R/W-0<br>TCS <sup>(1,2)</sup> | U-0   |

| Legend:    |                                                      |                                                                                                 |                                  |                                 |  |  |  |

|------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------|--|--|--|

| R = Reada  | able bit                                             | W = Writable bit                                                                                | U = Unimplemented bit,           | read as '0'                     |  |  |  |

| -n = Value | at POR                                               | '1' = Bit is set                                                                                | '0' = Bit is cleared             | x = Bit is unknown              |  |  |  |

| bit 15     | 1 = Start                                            | nery On bit <sup>(1)</sup><br>s 16-bit Timery<br>s 16-bit Timery                                |                                  |                                 |  |  |  |

| bit 14     | Unimple                                              | Unimplemented: Read as '0'                                                                      |                                  |                                 |  |  |  |

| bit 13     | TSIDL: S                                             | top in Idle Mode bit <sup>(1)</sup>                                                             |                                  |                                 |  |  |  |

|            |                                                      | ntinue module operation whe<br>nue module operation in Idle                                     |                                  |                                 |  |  |  |

| bit 12-7   | Unimple                                              | mented: Read as '0'                                                                             |                                  |                                 |  |  |  |

| bit 6      | When TC<br>This bit is<br><u>When TC</u><br>1 = Gate | ignored.                                                                                        |                                  |                                 |  |  |  |

| bit 5-4    | TCKPS<                                               | 1:0>: Timery Input Clock Pres                                                                   | scale Select bits <sup>(1)</sup> |                                 |  |  |  |

|            | 11 = 1:25<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1       | 56                                                                                              |                                  |                                 |  |  |  |

| bit 3-2    | Unimple                                              | mented: Read as '0'                                                                             |                                  |                                 |  |  |  |

| bit 1      | 1 = Exte                                             | ery Clock Source Select bit <sup>(1</sup><br>rnal clock from pin TyCK (on<br>nal clock (Fosc/2) |                                  |                                 |  |  |  |

| bit 0      | Unimple                                              | mented: Read as '0'                                                                             |                                  |                                 |  |  |  |

| Note 1:    | operation; all                                       | timer functions are set throug                                                                  | gh T2CON and T4CON.              | e bits have no effect on Timery |  |  |  |

| 2:         | If TCS = $1, F$                                      | RPINRx (TxCK) must be conf                                                                      | igured to an available RPn pir   | a. See Section 10.4 "Peripheral |  |  |  |

**Pin Select (PPS)**" for more information.

**3:** Changing the value of TyCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

## 17.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

# EQUATION 17-1: UART BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** FCY denotes the instruction cycle clock

frequency (Fosc/2).**2:** Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 17-2: UART BAUD RATE WITH BRGH = $1^{(1,2)}$

|      |    | Baud Rate = $\frac{FCY}{4 \cdot (UxBRG + 1)}$         |

|------|----|-------------------------------------------------------|

|      |    | $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$           |

| Note | 1: | Fcy denotes the instruction cycle clock<br>frequency. |

|      | 2. | Based on $E_{CV} = E_{OSC}/2$ Doze mode               |

2: Based on FCY = FOSC/2, Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

### EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate =  | FCY/(16 (UxBRG + 1))                                                                           |

|----------------------|------------------------------------------------------------------------------------------------|

| Solving for UxBRG Va | lue:                                                                                           |

|                      | ((FCY/Desired Baud Rate)/16) – 1<br>((4000000/9600)/16) – 1<br>25                              |

|                      | 4000000/(16 (25 + 1))<br>9615                                                                  |

| =                    | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate<br>(9615 – 9600)/9600<br>0.16% |

| Note 1: Based on     | Fcy = Fosc/2, Doze mode and PLL are disabled.                                                  |

#### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0                 | R/W-0    | U-0 | R/W-0, HC | R/W-0                | R-0   | R-1   |

|----------|-----------------------|----------|-----|-----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV <sup>(1)</sup> | UTXISEL0 | —   | UTXBRK    | UTXEN <sup>(2)</sup> | UTXBF | TRMT  |

| bit 15   |                       |          |     |           |                      |       | bit 8 |

|          |                       |          |     |           |                      |       |       |

| R/W-0    | R/W-0    | R/W-0 | R-1   | R-0  | R-0  | R/C-0 | R-0   |

|----------|----------|-------|-------|------|------|-------|-------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR | FERR | OERR  | URXDA |

| bit 7    |          |       |       |      |      |       | bit 0 |

| Legend:           | C = Clearable bit | HC = Hardware Clearat  | HC = Hardware Clearable bit        |  |  |

|-------------------|-------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15,13 UTXISEL<1:0>: Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

### bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit<sup>(1)</sup>

| bit 14  | UIXINV: IrDA® Encoder Transmit Polarity Inversion bit                                                                                                                                                                                                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <u>IREN = 1:</u>                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                           |

| bit 11  | UTXBRK: Transmit Break bit                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                                                                                                                                                                                                 |

|         | 0 = Sync Break transmission disabled or completed                                                                                                                                                                                                                                                                                                                                                    |

| bit 10  | UTXEN: Transmit Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                            |

|         | 1 = Transmit enabled, UxTX pin controlled by UARTx                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>Transmit disabled, any pending transmission is aborted and the buffer is reset; UxTX pin controlled<br/>by port</li> </ul>                                                                                                                                                                                                                                                                  |

| bit 9   | UTXBF: Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                   |

|         | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = Transmit buffer is not full; at least one more character can be written                                                                                                                                                                                                                                                                                                                          |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                                                                  |

|         | 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)                                                                                                                                                                                                                                                                                              |

|         | 0 = Transmit Shift Register is not empty, a transmission is in progress or queued                                                                                                                                                                                                                                                                                                                    |

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>11 = Interrupt is set on RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

|         |                                                                                                                                                                                                                                                                                                                                                                                                      |

- Note 1: Value of bit only affects the transmit properties of the module when the IrDA encoder is enabled (IREN = 1).

- 2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

NOTES:

### 18.1.2 HOST AND OTG MODES

#### 18.1.2.1 D+ and D- Pull-down Resistors

PIC24FJ64GB004 family devices have built-in 15 kΩ pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the HOSTEN bit (U1CON<3>). If the OTGEN bit (U1OTGCON<2>) is set, then these pull-downs are enabled by setting the DPPULDWN and DMPULDWN bits (U1OTGCON<5:4>).

#### 18.1.2.2 Power Configurations

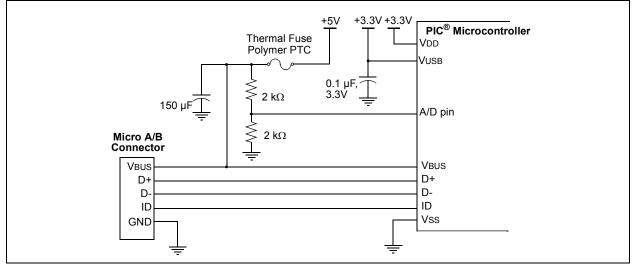

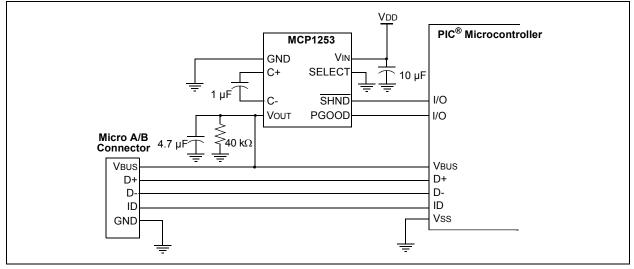

In Host mode, as well as Host mode in On-the-Go operation, the USB 2.0 specification requires that the Host application supply power on VBUS. Since the

microcontroller is running below VBUS and is not able to source sufficient current, a separate power supply must be provided.

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 18-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 18-7.

#### FIGURE 18-6: HOST INTERFACE EXAMPLE

#### FIGURE 18-7: OTG INTERFACE EXAMPLE

#### REGISTER 18-11: U1SOF: USB OTG START-OF-TOKEN THRESHOLD REGISTER (HOST MODE ONLY)

| U-0                               | U-0                                                               | U-0   | U-0   | U-0                                | U-0   | U-0   | U-0   |

|-----------------------------------|-------------------------------------------------------------------|-------|-------|------------------------------------|-------|-------|-------|

| —                                 | —                                                                 | —     | _     | —                                  | —     | —     | —     |

| bit 15                            |                                                                   |       |       |                                    |       |       | bit 8 |

|                                   |                                                                   |       |       |                                    |       |       |       |

| R/W-0                             | R/W-0                                                             | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

| CNT7                              | CNT6                                                              | CNT5  | CNT4  | CNT3                               | CNT2  | CNT1  | CNT0  |

| bit 7                             |                                                                   | •     |       |                                    |       |       | bit 0 |

|                                   |                                                                   |       |       |                                    |       |       |       |

| Legend:                           |                                                                   |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit |                                                                   |       | oit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at                     | Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unl |       | nown  |                                    |       |       |       |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: Start-of-Frame Size bits;

Value represents 10 + (packet size of n bytes). For example:

0100 1010 = 64-byte packet

0010 1010 = 32-byte packet

0001 0010 = 8-byte packet

#### REGISTER 18-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                 | U-0 | R/W-0   | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----------------------|-----|---------|-----|-----|-------|-------|

| UTEYE | UOEMON <sup>(1)</sup> | —   | USBSIDL | —   | —   | PPB1  | PPB0  |

| bit 7 | ·                     |     |         |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------|

| bit 7    | UTEYE: USB Eye Pattern Test Enable bit                                                                    |

|          | 1 = Eye pattern test is enabled                                                                           |

|          | 0 = Eye pattern test is disabled                                                                          |

| bit 6    | UOEMON: USB OE Monitor Enable bit <sup>(1)</sup>                                                          |

|          | 1 = $\overline{OE}$ signal is active; it indicates the intervals during which the D+/D- lines are driving |

|          | 0 = OE signal is inactive                                                                                 |

| bit 5    | Unimplemented: Read as '0'                                                                                |

| bit 4    | USBSIDL: USB OTG Stop in Idle Mode bit                                                                    |

|          | <ol> <li>Discontinue module operation when device enters Idle mode</li> </ol>                             |

|          | <ul> <li>0 = Continue module operation in Idle mode</li> </ul>                                            |

| bit 3-2  | Unimplemented: Read as '0'                                                                                |

**Note 1:** This bit is only active when the UTRDIS bit (U1CNFG2<0>) is set.

#### 18.7.2 USB INTERRUPT REGISTERS

#### REGISTER 18-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                            |                    |  |  |  |

|-------------------|------------------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit         | HS = Hardware Settable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                     |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                            |

|          | 1 = Change in ID state is detected                                                                                             |

|          | 0 = No ID state change                                                                                                         |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                              |

|          | 1 = The 1 millisecond timer has expired                                                                                        |

|          | 0 = The 1 millisecond timer has not expired                                                                                    |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                      |

|          | 1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different<br>from last time           |

|          | 0 = USB line state has not been stable for 1 ms                                                                                |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                             |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                            |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                         |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                    |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup>                                      |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                           |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                   |

|          | 1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup> |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                           |

| bit 1    | Unimplemented: Read as '0'                                                                                                     |

| bit 0    | VBUSVDIF A-Device VBUS Change Indicator bit                                                                                    |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the USB OTG Specification) <sup>(1)</sup> |

|          | 0 = No VBUS change on A-device is detected                                                                                     |

| Note 1:  | VBUS threshold crossings may be either rising or falling.                                                                      |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits at the moment of the write to become cleared.

| R/W-0         | U-0                                                                                            | R/W-0                               | R/W-0                                | R/W-0                  | R/W-0          | R/W-0           | R/W-0  |  |  |

|---------------|------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|------------------------|----------------|-----------------|--------|--|--|

| PMPEN         |                                                                                                | PSIDL                               | ADRMUX1 <sup>(1)</sup>               | ADRMUX0 <sup>(1)</sup> | PTBEEN         | PTWREN          | PTRDEN |  |  |

| bit 15        |                                                                                                |                                     |                                      |                        |                |                 | bit 8  |  |  |

|               |                                                                                                |                                     |                                      |                        |                |                 |        |  |  |

| R/W-0         | R/W-0                                                                                          | R/W-0 <sup>(2)</sup>                | U-0                                  | R/W-0 <sup>(2)</sup>   | R/W-0          | R/W-0           | R/W-0  |  |  |

| CSF1          | CSF0                                                                                           | ALP                                 |                                      | CS1P                   | BEP            | WRSP            | RDSP   |  |  |

| bit 7         |                                                                                                |                                     |                                      |                        |                |                 | bit (  |  |  |

| Legend:       |                                                                                                |                                     |                                      |                        |                |                 |        |  |  |

| R = Readab    | le bit                                                                                         | W = Writable                        | bit                                  | U = Unimplem           | ented bit, rea | d as '0'        |        |  |  |

| -n = Value at |                                                                                                | '1' = Bit is se                     |                                      | '0' = Bit is clea      | -              | x = Bit is unkr | nown   |  |  |

|               |                                                                                                |                                     |                                      | 0 21110 0.00           |                |                 |        |  |  |

| bit 15        | PMPEN: Para                                                                                    | allel Master Po                     | ort Enable bit                       |                        |                |                 |        |  |  |

|               | 1 = PMP is e                                                                                   | enabled                             |                                      |                        |                |                 |        |  |  |

|               | 0 = PMP is c                                                                                   | lisabled, no off                    | -chip access pe                      | erformed               |                |                 |        |  |  |

| bit 14        | Unimplemen                                                                                     | ted: Read as                        | '0'                                  |                        |                |                 |        |  |  |

| bit 13        | PSIDL: Stop                                                                                    | in Idle Mode b                      | it                                   |                        |                |                 |        |  |  |

|               |                                                                                                |                                     | eration when de<br>ation in Idle mod |                        | e mode         |                 |        |  |  |

| bit 12-11     |                                                                                                | •                                   |                                      |                        | 1)             |                 |        |  |  |

|               | ADRMUX<1:0>: Address/Data Multiplexing Selection bits <sup>(1)</sup><br>11 = Reserved          |                                     |                                      |                        |                |                 |        |  |  |

|               | 10 = All 16 k                                                                                  | oits of address                     | are multiplexed                      | l on PMD<7:0>          | pins           |                 |        |  |  |

|               | 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed or |                                     |                                      |                        |                |                 |        |  |  |

|               | PMA<1<br>00 = Addres                                                                           |                                     | pear on separat                      | e pins                 |                |                 |        |  |  |

| bit 10        |                                                                                                |                                     | Enable bit (16-                      | -                      | e)             |                 |        |  |  |

|               | 1 = PMBE po                                                                                    |                                     | ·                                    |                        |                |                 |        |  |  |

|               | 0 = PMBE po                                                                                    | ort is disabled                     |                                      |                        |                |                 |        |  |  |

| bit 9         | PTWREN: W                                                                                      | rite Enable Str                     | obe Port Enable                      | e bit                  |                |                 |        |  |  |

|               |                                                                                                | PMENB port is<br>PMENB port is      |                                      |                        |                |                 |        |  |  |

| bit 8         | PTRDEN: Re                                                                                     | ad/Write Strob                      | e Port Enable b                      | bit                    |                |                 |        |  |  |

|               | 1 = PMRD/P<br>0 = PMRD/P                                                                       | MWR port is e<br>MWR port is d      | nabled<br>isabled                    |                        |                |                 |        |  |  |

| bit 7-6       |                                                                                                | hip Select Fur                      |                                      |                        |                |                 |        |  |  |

|               | 11 = Reserve                                                                                   | -                                   |                                      |                        |                |                 |        |  |  |

|               | 10 = PMCS1                                                                                     | functions as c                      | hip set                              |                        |                |                 |        |  |  |

|               | 01 = Reserve                                                                                   |                                     |                                      |                        |                |                 |        |  |  |

|               | 00 = Reserve                                                                                   |                                     | (2)                                  |                        |                |                 |        |  |  |

| bit 5         |                                                                                                | s Latch Polarit                     | •                                    |                        |                |                 |        |  |  |

|               |                                                                                                | gh <u>(PMALL</u> an<br>w (PMALL and |                                      |                        |                |                 |        |  |  |

| bit 4         |                                                                                                | ited: Read as                       | -                                    |                        |                |                 |        |  |  |

| bit 3         |                                                                                                | Select 1 Polari                     |                                      |                        |                |                 |        |  |  |

|               | •                                                                                              | gh (PMCS1/PI                        | -                                    |                        |                |                 |        |  |  |

|               |                                                                                                | w (PMCS1/PM                         |                                      |                        |                |                 |        |  |  |

| Note 1: P     | MA<10:2> bits a                                                                                | are not availab                     | le on 28-pin dev                     | vices.                 |                |                 |        |  |  |

#### REGISTER 19-1: PMCON: PARALLEL PORT CONTROL REGISTER

**Note 1:** PMA<10:2> bits are not available on 28-pin devices.

2: These bits have no effect when their corresponding pins are used as address lines.

#### REGISTER 19-6: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                                | U-0       | U-0           | U-0 | U-0                                     | U-0                      | U-0                      | U-0    |

|------------------------------------|-----------|---------------|-----|-----------------------------------------|--------------------------|--------------------------|--------|

| —                                  | —         | —             | —   | —                                       | —                        | —                        | _      |

| bit 15                             |           |               |     |                                         |                          |                          | bit 8  |

|                                    |           |               |     |                                         |                          |                          |        |

| U-0                                | U-0       | U-0           | U-0 | U-0                                     | R/W-0                    | R/W-0                    | R/W-0  |

|                                    | _         | —             |     | _                                       | RTSECSEL1 <sup>(1)</sup> | RTSECSEL0 <sup>(1)</sup> | PMPTTL |

| bit 7                              | •         |               | •   |                                         | •                        |                          | bit 0  |

|                                    |           |               |     |                                         |                          |                          |        |

| Legend:                            |           |               |     |                                         |                          |                          |        |

| R = Readabl                        | e bit     | W = Writable  | bit | U = Unimpler                            | mented bit, read a       | as '0'                   |        |

| -n = Value at POR '1' = Bit is set |           |               | t   | '0' = Bit is cleared x = Bit is unknown |                          |                          | vn     |

|                                    |           |               |     |                                         |                          |                          |        |

| bit 15-3                           | Unimpleme | nted: Read as | '0' |                                         |                          |                          |        |

|                                    |           |               |     |                                         | (4)                      |                          |        |

- bit 2-1 RTSECSEL<1:0>: RTCC Seconds Clock Output Select bits<sup>(1)</sup>

- 11 = Reserved; do not use

- 10 = RTCC source clock is selected for the RTCC pin (clock can be LPRC or SOSC, depending on the setting of the Flash Configuration bit, RTCOSC (CW4<5>))

- 01 = RTCC seconds clock is selected for the RTCC pin

- 00 = RTCC alarm pulse is selected for the RTCC pin

#### bit 0 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffers

- Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit needs to be set.

| R/W-0         | U-0                            | R/W-0                                        | R-0                  | R-0               | R-0             | R-0              | R-0          |  |  |

|---------------|--------------------------------|----------------------------------------------|----------------------|-------------------|-----------------|------------------|--------------|--|--|

| CRCEN         | —                              | CSIDL                                        | VWORD4               | VWORD3            | VWORD2          | VWORD1           | VWORD0       |  |  |

| bit 15        |                                |                                              |                      |                   |                 |                  | bit 8        |  |  |

|               |                                |                                              |                      |                   |                 |                  |              |  |  |

| R-0, HCS      | R-1, HCS                       | R/W-0                                        | R/W-0, HC            | R/W-0             | U-0             | U-0              | U-0          |  |  |

| CRCFUL        | CRCMPT                         | CRCISEL                                      | CRCGO                | LENDIAN           | —               | —                | —            |  |  |

| bit 7         |                                |                                              |                      |                   |                 |                  | bit (        |  |  |

|               |                                |                                              | <u>Olaarahla hit</u> |                   | ara Claarabla/C | attable bit      |              |  |  |

| Legend:       | - 1-14                         | HC = Hardware                                |                      | HCS = Hardwa      |                 |                  |              |  |  |

| R = Readabl   |                                | W = Writable bit                             |                      | -                 | ented bit, read |                  |              |  |  |

| -n = Value at | POR                            | '1' = Bit is set                             |                      | '0' = Bit is clea | ared            | x = Bit is unk   | nown         |  |  |

| pit 15        | CRCEN: CR                      | C Enable bit                                 |                      |                   |                 |                  |              |  |  |

|               | 1 = Module i                   | s enabled                                    |                      |                   |                 |                  |              |  |  |

|               | 0 = Module i<br>NOT res        | s enabled. All sta<br>et                     | te machines, poi     | nters and CRCV    | VDAT/CRCDA      | T are reset; otl | her SFRs are |  |  |

| oit 14        | Unimplemen                     | ted: Read as '0'                             |                      |                   |                 |                  |              |  |  |

| oit 13        | CSIDL: CRC                     | Stop in Idle Mod                             | e bit                |                   |                 |                  |              |  |  |

|               |                                | nue module operation module operation        |                      | ce enters Idle m  | ode             |                  |              |  |  |

| oit 12-8      | VWORD<4:0                      | >: Pointer Value                             | bits                 |                   |                 |                  |              |  |  |

|               |                                | number of valid v<br>PLEN<3:0> $\leq$ 7.     | words in the FIF     | O. Has a maxim    | num value of 8  | when PLEN<       | 3:0> > 7     |  |  |

| bit 7         | CRCFUL: FI                     | FO Full bit                                  |                      |                   |                 |                  |              |  |  |

|               | 1 = FIFO is f                  |                                              |                      |                   |                 |                  |              |  |  |

|               | 0 = FIFO is r                  |                                              |                      |                   |                 |                  |              |  |  |

| bit 6         |                                | FO Empty Bit                                 |                      |                   |                 |                  |              |  |  |

|               | 1 = FIFO is e<br>0 = FIFO is r |                                              |                      |                   |                 |                  |              |  |  |

| bit 5         |                                | RC interrupt Sele                            | ection bit           |                   |                 |                  |              |  |  |

|               |                                | on FIFO is empt                              |                      | on is not compl   | ete             |                  |              |  |  |

|               |                                | on shift is compl                            |                      |                   |                 |                  |              |  |  |

| bit 4         | CRCGO: Sta                     | rt CRC bit                                   |                      |                   |                 |                  |              |  |  |

|               |                                | C serial shifter                             |                      |                   |                 |                  |              |  |  |

|               |                                | ial shifter is turne                         |                      |                   |                 |                  |              |  |  |

| bit 3         |                                | ata Shift Direction                          |                      |                   |                 |                  |              |  |  |

|               |                                | rd is shifted into t<br>rd is shifted into t |                      |                   |                 |                  |              |  |  |

| bit 2-0       |                                | ted: Read as '0'                             |                      |                   |                 |                  |              |  |  |

|               |                                |                                              |                      |                   |                 |                  |              |  |  |

### REGISTER 21-1: CRCCON1: CRC CONTROL REGISTER 1

#### 25.2 Measuring Time

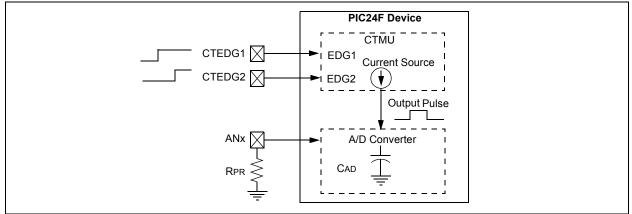

Time measurements on the pulse width can be similarly performed using the A/D module's internal capacitor (CAD) and a precision resistor for current calibration. Figure 25-2 shows the external connections used for time measurements, and how the CTMU and A/D modules are related in this application. This example also shows both edge events coming from the external CTEDG pins, but other configurations using internal edge sources are possible. For the smallest time measurements, select the internal A/D Channel 31, CH0S<4:0> = 11111. This minimizes any stray capacitance that may otherwise be associated with using an input pin, thus keeping the total capacitance to that of the A/D Converter itself (4-5 pF). A detailed discussion on measuring capacitance and time with the CTMU module is provided in the "PIC24F Family Reference Manual".

### 25.3 Pulse Generation and Delay

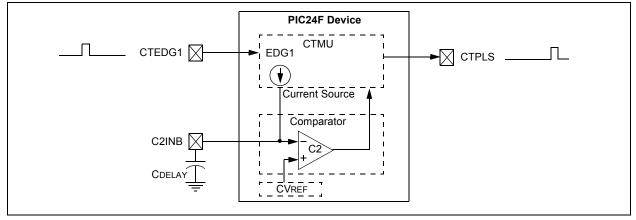

The CTMU module can also generate an output pulse with edges that are not synchronous with the device's system clock. More specifically, it can generate a pulse with a programmable delay from an edge event input to the module.

When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON<12>), the internal current source is connected to the B input of Comparator 2. A capacitor (CDELAY) is connected to the Comparator 2 pin, C2INB, and the comparator voltage reference, CVREF, is connected to C2INA. CVREF is then configured for a specific trip point. The module begins to charge CDELAY when an edge event is detected. When CDELAY charges above the CVREF trip point, a pulse is output on CTPLS. The length of the pulse delay is determined by the value of CDELAY and the CVREF trip point.

Figure 25-3 shows the external connections for pulse generation, as well as the relationship of the different analog modules required. While CTEDG1 is shown as the input pulse source, other options are available. A detailed discussion on pulse generation with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

## FIGURE 25-2: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

# FIGURE 25-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 3-2

EDG1SEL<1:0>: Edge 1 Source Select bits

11 = CTED1 pin

10 = CTED2 pin

01 = OC1 module

00 = Timer1 module

bit 1

EDG2STAT: Edge 2 Status bit

1 = Edge 2 event has occurred

0 = Edge 2 event has not occurred

bit 0