Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb004t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

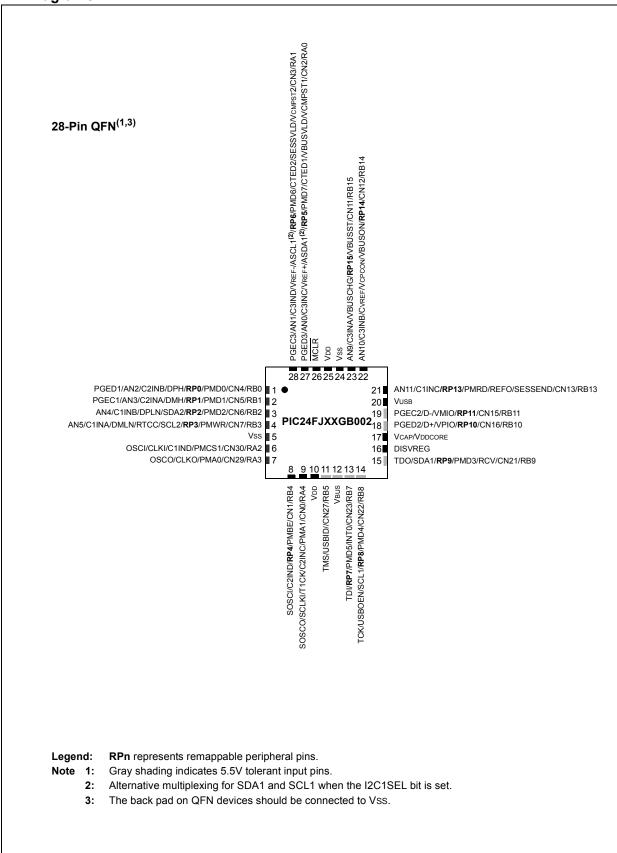

### **Pin Diagrams**

|           | Pin Number                    |               |                    |     |                 |                                                |

|-----------|-------------------------------|---------------|--------------------|-----|-----------------|------------------------------------------------|

| Function  | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                    |

| RA0       | 2                             | 27            | 19                 | I/O | ST              | PORTA Digital I/O.                             |

| RA1       | 3                             | 28            | 20                 | I/O | ST              |                                                |

| RA2       | 9                             | 6             | 30                 | I/O | ST              |                                                |

| RA3       | 10                            | 7             | 31                 | I/O | ST              |                                                |

| RA4       | 12                            | 9             | 34                 | I/O | ST              |                                                |

| RA7       | _                             |               | 13                 | I/O | ST              |                                                |

| RA8       | _                             |               | 32                 | I/O | ST              |                                                |

| RA9       | _                             |               | 35                 | I/O | ST              |                                                |

| RA10      | _                             |               | 12                 | I/O | ST              |                                                |

| RB0       | 4                             | 1             | 21                 | I/O | ST              | PORTB Digital I/O.                             |

| RB1       | 5                             | 2             | 22                 | I/O | ST              |                                                |

| RB2       | 6                             | 3             | 23                 | I/O | ST              |                                                |

| RB3       | 7                             | 4             | 24                 | I/O | ST              |                                                |

| RB4       | 11                            | 8             | 33                 | I/O | ST              |                                                |

| RB5       | 14                            | 11            | 41                 | I/O | ST              |                                                |

| RB7       | 16                            | 13            | 43                 | I/O | ST              |                                                |

| RB8       | 17                            | 14            | 44                 | I/O | ST              |                                                |

| RB9       | 18                            | 15            | 1                  | I/O | ST              |                                                |

| RB10      | 21                            | 18            | 8                  | I/O | ST              |                                                |

| RB11      | 22                            | 19            | 9                  | I/O | ST              |                                                |

| RB13      | 24                            | 21            | 11                 | I/O | ST              |                                                |

| RB14      | 25                            | 22            | 14                 | I/O | ST              |                                                |

| RB15      | 26                            | 23            | 15                 | I/O | ST              |                                                |

| RC0       | —                             | _             | 25                 | I/O | ST              | PORTC Digital I/O.                             |

| RC1       | —                             | _             | 26                 | I/O | ST              |                                                |

| RC2       | —                             | _             | 27                 | I/O | ST              |                                                |

| RC3       | _                             | _             | 36                 | I/O | ST              |                                                |

| RC4       | —                             |               | 37                 | I/O | ST              | ]                                              |

| RC5       | _                             | _             | 38                 | I/O | ST              |                                                |

| RC6       | _                             | _             | 2                  | I/O | ST              |                                                |

| RC7       | _                             |               | 3                  | I/O | ST              | ]                                              |

| RC8       | _                             | _             | 4                  | I/O | ST              | ]                                              |

| RC9       | —                             | _             | 5                  | I/O | ST              |                                                |

| RCV       | 18                            | 15            | 1                  | I   | ST              | USB Receive Input (from external transceiver). |

| REFO      | 24                            | 21            | 11                 | 0   | _               | Reference Clock Output.                        |

| Legend: 1 | TL = TTL inpu                 | t buffer      | -                  |     | ST =            | Schmitt Trigger input buffer                   |

# TABLE 1-2: PIC24FJ64GB004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{\text{TM}} = I^2C/\text{SMBus}$  input buffer

DS39940D-page 16

|  | REGISTER 3-2: | CORCON: CPU CONTROL REGISTER |

|--|---------------|------------------------------|

|--|---------------|------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0                 | U-0   | U-0 | U-0   |

|--------|-----|-----|-----|---------------------|-------|-----|-------|

|        | —   |     | _   |                     |       | —   |       |

| bit 15 |     |     |     |                     |       |     | bit 8 |

|        |     |     |     |                     |       |     |       |

| U-0    | U-0 | U-0 | U-0 | R/C-0               | R/W-0 | U-0 | U-0   |

| _      | —   | —   | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7  |     |     |     |                     |       |     | bit 0 |

|        |     |     |     |                     |       |     |       |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space visible in data space                                                                                       |

|          | 0 = Program space not visible in data space                                                                                   |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

# 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is as follows:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

# EXAMPLE 5-1: ERASING A PROGRAM MEMORY BLOCK – ASSEMBLY LANGUAGE CODE

| ; Set up | NVMCON  | I for block erase operation          |   |                                       |

|----------|---------|--------------------------------------|---|---------------------------------------|

|          | MOV     | #0x4042, W0                          | ; |                                       |

|          | MOV     | W0, NVMCON                           | ; | Initialize NVMCON                     |

| ; Init p | pointer | to row to be ERASED                  |   |                                       |

|          | MOV     | <pre>#tblpage(PROG_ADDR), W0</pre>   | ; |                                       |

|          | MOV     | W0, TBLPAG                           | ; | Initialize PM Page Boundary SFR       |

|          | MOV     | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; | Initialize in-page EA[15:0] pointer   |

|          | TBLWTL  | WO, [WO]                             | ; | Set base address of erase block       |

|          | DISI    | #5                                   | ; | Block all interrupts with priority <7 |

|          |         |                                      | ; | for next 5 instructions               |

|          | MOV     | #0x55, W0                            |   |                                       |

|          | MOV     | W0, NVMKEY                           | ; | Write the 55 key                      |

|          | MOV     | #0xAA, W1                            | ; |                                       |

|          | MOV     | W1, NVMKEY                           | ; | Write the AA key                      |

|          | BSET    | NVMCON, #WR                          | ; | Start the erase sequence              |

|          | NOP     |                                      | ; | Insert two NOPs after the erase       |

|          | NOP     |                                      | ; | command is asserted                   |

|          |         |                                      |   |                                       |

| U-0            | U-0             | R/W-0                                   | U-0             | U-0               | U-0  | R/W-0           | U-0             |  |  |

|----------------|-----------------|-----------------------------------------|-----------------|-------------------|------|-----------------|-----------------|--|--|

|                | _               | PMPIE                                   |                 | _                 |      | OC5IE           | _               |  |  |

| bit 15         |                 |                                         |                 |                   |      |                 | bit 8           |  |  |

| DAALO          | DAVA            | DAALO                                   | 11.0            |                   |      | DAMA            | DAMA            |  |  |

| R/W-0<br>IC5IE | R/W-0           | R/W-0<br>IC3IE                          | U-0             | U-0               | U-0  | R/W-0<br>SPI2IE | R/W-0<br>SPF2IE |  |  |

| bit 7          | 104IE           | ICSIE                                   | —               |                   | _    | SFIZIE          | bit C           |  |  |

|                |                 |                                         |                 |                   |      |                 |                 |  |  |

| _egend:        |                 |                                         |                 |                   |      |                 |                 |  |  |

| R = Readab     |                 | W = Writable                            | oit             | U = Unimplem      | -    | d as '0'        |                 |  |  |

| -n = Value a   | t POR           | '1' = Bit is set                        |                 | '0' = Bit is clea | ared | x = Bit is unkr | nown            |  |  |

| bit 15-14      | Unimplemen      | ted: Read as 'd                         | )'              |                   |      |                 |                 |  |  |

| bit 13         | •               | llel Master Port                        |                 | ble bit           |      |                 |                 |  |  |

|                |                 | request is enable                       | -               |                   |      |                 |                 |  |  |

|                |                 | request is not e                        |                 |                   |      |                 |                 |  |  |

| oit 12-10      | Unimplemen      | ted: Read as 'o                         | )'              |                   |      |                 |                 |  |  |

| oit 9          | OC5IE: Outpu    | ut Compare Cha                          | annel 5 Interru | upt Enable bit    |      |                 |                 |  |  |

|                |                 | request is enab<br>request is not e     |                 |                   |      |                 |                 |  |  |

| bit 8          | -               | ted: Read as '(                         |                 |                   |      |                 |                 |  |  |

| bit 7          | •               | Capture Channe                          |                 | Enable bit        |      |                 |                 |  |  |

|                |                 | request is enab                         | -               |                   |      |                 |                 |  |  |

|                | 0 = Interrupt r | request is not e                        | nabled          |                   |      |                 |                 |  |  |

| bit 6          | •               | Capture Channe                          | •               | Enable bit        |      |                 |                 |  |  |

|                |                 | request is enab<br>request is not e     |                 |                   |      |                 |                 |  |  |

| bit 5          |                 | Capture Channe                          |                 | nable bit         |      |                 |                 |  |  |

|                | -               | request is enable                       | -               |                   |      |                 |                 |  |  |

|                |                 | request is not e                        |                 |                   |      |                 |                 |  |  |

| bit 4-2        | Unimplemen      | ted: Read as 'd                         | )'              |                   |      |                 |                 |  |  |

| bit 1          | SPI2IE: SPI2    | Event Interrupt                         | Enable bit      |                   |      |                 |                 |  |  |

|                |                 | request is enab                         |                 |                   |      |                 |                 |  |  |

| -: 0           |                 | request is not e                        |                 |                   |      |                 |                 |  |  |

| oit 0          |                 | SPF2IE: SPI2 Fault Interrupt Enable bit |                 |                   |      |                 |                 |  |  |

|                | 1 - Internuct   | request is enab                         | ad              |                   |      |                 |                 |  |  |

# REGISTER 7-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

# REGISTER 7-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0              | R/W-1                                                                                      | R/W-0                                                                            | R/W-0                                 | U-0               | R/W-1            | R/W-0           | R/W-0                      |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|-------------------|------------------|-----------------|----------------------------|--|--|--|--|--|--|

| —                | T2IP2                                                                                      | T2IP1                                                                            | T2IP0                                 | —                 | OC2IP2           | OC2IP1          | OC2IP0                     |  |  |  |  |  |  |

| bit 15           |                                                                                            |                                                                                  |                                       |                   | ·                |                 | bit 8                      |  |  |  |  |  |  |

| U-0              | R/W-1                                                                                      | R/W-0                                                                            | R/W-0                                 | U-0               | U-0              | U-0             | U-0                        |  |  |  |  |  |  |

| _                | IC2IP2                                                                                     | IC2IP1                                                                           | IC2IP0                                | _                 | _                | _               | _                          |  |  |  |  |  |  |

| bit 7            |                                                                                            |                                                                                  |                                       |                   |                  |                 | bit (                      |  |  |  |  |  |  |

| Legend:          |                                                                                            |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

| R = Readab       | le bit                                                                                     | W = Writable t                                                                   | bit                                   | U = Unimple       | mented bit, read | 1 as '0'        |                            |  |  |  |  |  |  |

| -n = Value a     |                                                                                            | '1' = Bit is set                                                                 |                                       | '0' = Bit is cl   |                  | x = Bit is unkr | iown                       |  |  |  |  |  |  |

|                  |                                                                                            |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

| bit 15           | Unimpleme                                                                                  | nted: Read as '0                                                                 | 3                                     |                   |                  |                 |                            |  |  |  |  |  |  |

| bit 14-12        | T2IP<2:0>: <sup>-</sup>                                                                    | Timer2 Interrupt                                                                 | Priority bits                         |                   |                  |                 |                            |  |  |  |  |  |  |

|                  | 111 = Interru                                                                              | upt is Priority 7 (ł                                                             | nighest priorit                       | y interrupt)      |                  |                 |                            |  |  |  |  |  |  |

|                  | •                                                                                          |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

|                  | •                                                                                          |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

|                  |                                                                                            | upt is Priority 1<br>upt source is disa                                          | abled                                 |                   |                  |                 |                            |  |  |  |  |  |  |

| bit 11           | Unimpleme                                                                                  | nted: Read as '0                                                                 | ,                                     |                   |                  |                 |                            |  |  |  |  |  |  |

| bit 10-8         | OC2IP<2:0>                                                                                 | : Output Compa                                                                   | re Channel 2                          | Interrupt Priori  | ty bits          |                 |                            |  |  |  |  |  |  |

|                  | 111 = Interru                                                                              | upt is Priority 7 (I                                                             | nighest priorit                       | y interrupt)      |                  |                 |                            |  |  |  |  |  |  |

|                  | •                                                                                          |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

|                  | •                                                                                          |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

|                  | 001 = Interru                                                                              | upt is Priority 1                                                                |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

|                  | 000 = Interri                                                                              | int nouron in dia                                                                | - le l a al                           |                   |                  |                 |                            |  |  |  |  |  |  |

|                  |                                                                                            | upt source is disa                                                               | abled                                 |                   |                  |                 | Unimplemented: Read as '0' |  |  |  |  |  |  |

| bit 7            |                                                                                            |                                                                                  |                                       |                   |                  |                 |                            |  |  |  |  |  |  |

| bit 7<br>bit 6-4 | Unimpleme                                                                                  |                                                                                  | ,                                     | rrupt Priority bi | its              |                 |                            |  |  |  |  |  |  |

|                  | Unimpleme<br>IC2IP<2:0>:                                                                   | nted: Read as '0                                                                 | ,<br>hannel 2 Inte                    |                   | its              |                 |                            |  |  |  |  |  |  |

|                  | Unimpleme<br>IC2IP<2:0>:                                                                   | nted: Read as '0<br>Input Capture C                                              | ,<br>hannel 2 Inte                    |                   | its              |                 |                            |  |  |  |  |  |  |

|                  | Unimpleme<br>IC2IP<2:0>:                                                                   | nted: Read as '0<br>Input Capture C                                              | ,<br>hannel 2 Inte                    |                   | its              |                 |                            |  |  |  |  |  |  |

|                  | Unimplement<br>IC2IP<2:0>:<br>111 = Interrout<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nted: Read as '0<br>Input Capture C<br>upt is Priority 7 (h<br>upt is Priority 1 | ,<br>hannel 2 Inte<br>nighest priorit |                   | its              |                 |                            |  |  |  |  |  |  |

|                  | Unimplement<br>IC2IP<2:0>:<br>111 = Interrout<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nted: Read as '0<br>Input Capture C<br>upt is Priority 7 (h                      | ,<br>hannel 2 Inte<br>nighest priorit |                   | its              |                 |                            |  |  |  |  |  |  |

| U-0          | U-0                                                        | U-0              | U-0             | U-0                                | R/W-0   | R/W-0              | R/W-0   |  |

|--------------|------------------------------------------------------------|------------------|-----------------|------------------------------------|---------|--------------------|---------|--|

| _            | _                                                          | _                | _               |                                    | USB1IP2 | USB1IP1            | USB1IP0 |  |

| bit 15       |                                                            |                  |                 |                                    |         |                    | bit 8   |  |

|              |                                                            |                  |                 |                                    |         |                    |         |  |

| U-0          | U-0                                                        | U-0              | U-0             | U-0                                | U-0     | U-0                | U-0     |  |

|              | —                                                          | —                | —               | _                                  | —       | —                  | —       |  |

| bit 7        |                                                            |                  |                 |                                    |         |                    | bit 0   |  |

|              |                                                            |                  |                 |                                    |         |                    |         |  |

| Legend:      |                                                            |                  |                 |                                    |         |                    |         |  |

| R = Readab   | le bit                                                     | W = Writable bit |                 | U = Unimplemented bit, read as '0' |         |                    |         |  |

| -n = Value a | It POR                                                     | '1' = Bit is set |                 | '0' = Bit is cleared               |         | x = Bit is unknown |         |  |

|              |                                                            |                  |                 |                                    |         |                    |         |  |

| bit 15-11    | Unimplemen                                                 | ted: Read as '   | כ'              |                                    |         |                    |         |  |

| bit 10-8     | USB1IP<2:0>                                                | : USB Interrup   | t Priority bits |                                    |         |                    |         |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                 |                                    |         |                    |         |  |

|              | •                                                          |                  |                 |                                    |         |                    |         |  |

|              | •                                                          |                  |                 |                                    |         |                    |         |  |

|              | •                                                          |                  |                 |                                    |         |                    |         |  |

|              | 001 = Interrup                                             |                  |                 |                                    |         |                    |         |  |

|              | •                                                          | ot source is dis |                 |                                    |         |                    |         |  |

| bit 7-0      | Unimplemen                                                 | ted: Read as '   | כ'              |                                    |         |                    |         |  |

|              |                                                            |                  |                 |                                    |         |                    |         |  |

# REGISTER 7-34: IPC21: INTERRUPT PRIORITY CONTROL REGISTER 21

# 8.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- · Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The primary oscillator and FRC sources have the option of using the internal USB PLL block, which generates both the USB module clock and a separate system clock from the 96 MHz PLL. Refer to **Section 8.5 "Oscillator Modes and USB Operation"** for additional information.

The Fast Internal RC (FRC) provides an 8 MHz clock source. It can optionally be reduced by the programmable clock divider to provide a range of system clock frequencies.

The selected clock source generates the processor and peripheral clock sources. The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

# 8.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to **Section 26.1 "Configuration Bits"** for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The secondary oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, shown in Table 8-1.

### 8.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when the FCKSM<1:0> bits are both programmed ('00').

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|----------------------------------------------------|-------------------|-------------|------------|-------|

| Fast RC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| (Reserved)                                         | Internal          | xx          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                     | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator<br>(SOSC)            | Secondary         | 11          | 100        | 1     |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL) | Primary           | 01          | 011        |       |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL) | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        |       |

| Fast RC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| Fast RC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 10.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input, or two functional outputs configured as the same pin, there are no hardware enforced lock outs. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

### 10.4.3.4 PPS Mapping Exceptions for PIC24FJ64GB0 Family Devices

Although the PPS registers allow for up to 32 remappable pins, not all of these are implemented in all devices. Exceptions and unimplemented RPn pins are listed in Table 10-4.

# TABLE 10-4: REMAPPABLE PIN EXCEPTIONS FOR PIC24FJ64GB004 FAMILY DEVICES

| Device Pin | RP Pins (I/O) |                 |  |  |  |

|------------|---------------|-----------------|--|--|--|

| Count      | Total         | Unimplemented   |  |  |  |

| 28 Pins    | 15            | RP12, RP16-RP25 |  |  |  |

| 44 Pins    | 25            | RP12            |  |  |  |

### 10.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit remapping lock

# 10.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

### 10.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

# 10.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW2<4>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0                           | U-0 | U-0              | R/W-0        | R/W-0                                  | R/W-0    | R/W-0  | R/W-0  |

|-------------------------------|-----|------------------|--------------|----------------------------------------|----------|--------|--------|

| _                             | _   | —                | RP21R4       | RP21R3                                 | RP21R2   | RP21R1 | RP21R0 |

| bit 15                        |     | ·                |              | ·                                      | •        | •      | bit 8  |

|                               |     |                  |              |                                        |          |        |        |

| U-0                           | U-0 | U-0              | R/W-0        | R/W-0                                  | R/W-0    | R/W-0  | R/W-0  |

| _                             | —   | —                | RP20R4       | RP20R3                                 | RP20R2   | RP20R1 | RP20R0 |

| bit 7                         |     | ·                |              | ·                                      | •        | •      | bit 0  |

|                               |     |                  |              |                                        |          |        |        |

| Legend:                       |     |                  |              |                                        |          |        |        |

| R = Readable bit W = Writable |     | bit              | U = Unimplem | nented bit, read                       | d as '0' |        |        |

| -n = Value at POR             |     | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknow |          |        | nown   |

| bit 15-13 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 12-8  | RP21R<4:0>: RP21 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP21 (see Table 10-3 for peripheral function numbers). |

| bit 7-5   | Unimplemented: Read as '0'                                                                            |

| bit 4-0   | RP20R<4:0>: RP20 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP20 (see Table 10-3 for peripheral function numbers). |

**Note 1:** This register is unimplemented in 28-pin devices; all bits read as '0'.

# REGISTER 10-26: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | _   | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | _   | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 |

| bit 7  |     |     |        |        |        |        | bit 0  |

|        |     |     |        |        |        |        |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 RP23R<4:0>: RP23 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP23 (see Table 10-3 for peripheral function numbers).

bit 7-5 Unimplemented: Read as '0'

bit 4-0 RP22R<4:0>: RP22 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP22 (see Table 10-3 for peripheral function numbers).

Note 1: This register is unimplemented in 28-pin devices; all bits read as '0'.

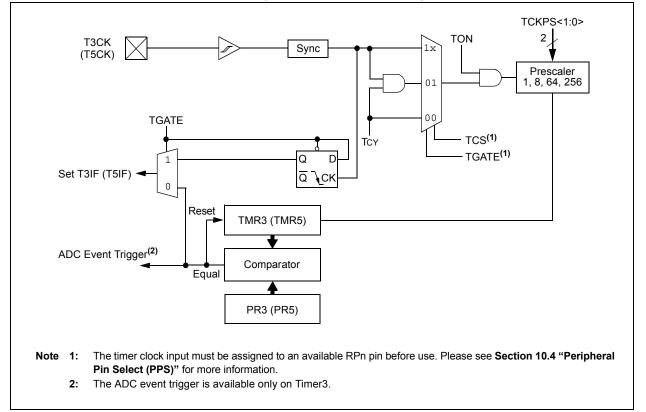

FIGURE 12-3: TIMER3 AND TIMER5 (16-BIT ASYNCHRONOUS) BLOCK DIAGRAM

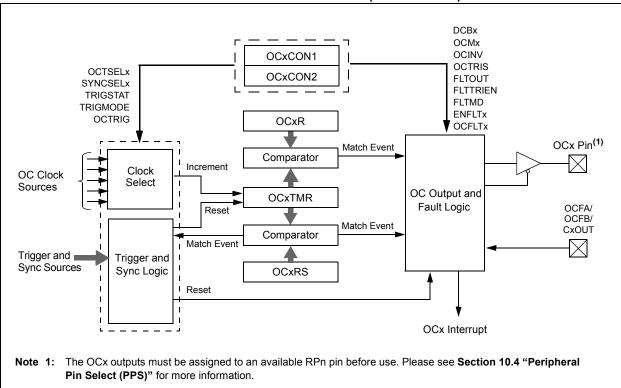

# FIGURE 14-1: OUTPUT COMPARE BLOCK DIAGRAM (16-BIT MODE)

# 14.4 Subcycle Resolution

The DCB bits (OCxCON2<10:9>) provide for resolution better than one instruction cycle. When used, they delay the falling edge generated by a match event by a portion of an instruction cycle.

For example, setting DCB<1:0> = 10 causes the falling edge to occur half way through the instruction cycle in which the match event occurs, instead of at the beginning. These bits cannot be used when OCM<2:0> = 0.01. When operating the module in PWM mode (OCM<2:0> = 110 or 111), the DCB bits will be double-buffered. The DCB bits are intended for use with a clock source identical to the system clock. When an OCx module with enabled prescaler is used, the falling edge delay caused by the DCB bits will be referenced to the system clock period, rather than the OCx module's period.

| <b>TABLE 14-1</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz) <sup>(1)</sup> |

|---------------------|--------------------------------------------------------------------------------|

|---------------------|--------------------------------------------------------------------------------|

| PWM Frequency     | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-------------------|--------|-------|--------|--------|---------|----------|---------|

| Prescaler Ratio   | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Value      | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits) | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

| <b>TABLE 14-2:</b> | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz) <sup>(1)</sup> |

|--------------------|----------------------------------------------------------------------------------|

|                    |                                                                                  |

| PWM Frequency     | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-------------------|---------|--------|--------|---------|----------|---------|---------|

| Prescaler Ratio   | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Value      | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits) | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

#### 18.7.3 USB ENDPOINT MANAGEMENT REGISTERS

| U-0                 | U-0                                                                                                                                                                                                         | U-0                                                    | U-0              | U-0               | U-0                  | U-0             | U-0    |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|-------------------|----------------------|-----------------|--------|--|--|--|--|

| _                   | —                                                                                                                                                                                                           | —                                                      | —                | —                 | —                    | —               | —      |  |  |  |  |

| bit 15              |                                                                                                                                                                                                             |                                                        |                  |                   |                      |                 | bit 8  |  |  |  |  |

| R/W-0               | R/W-0                                                                                                                                                                                                       | U-0                                                    | R/W-0            | R/W-0             | R/W-0                | R/W-0           | R/W-0  |  |  |  |  |

| LSPD <sup>(1)</sup> | RETRYDIS <sup>(1)</sup>                                                                                                                                                                                     | _                                                      | EPCONDIS         | EPRXEN            | EPTXEN               | EPSTALL         | EPHSHK |  |  |  |  |

| bit 7               |                                                                                                                                                                                                             |                                                        |                  |                   |                      |                 | bit (  |  |  |  |  |

| Legend:             |                                                                                                                                                                                                             |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| R = Readab          | ole bit                                                                                                                                                                                                     | W = Writable                                           | e bit            | U = Unimplem      | nented bit, read     | d as '0'        |        |  |  |  |  |

| -n = Value a        | at POR                                                                                                                                                                                                      | '1' = Bit is se                                        | et               | '0' = Bit is clea | ared                 | x = Bit is unkr | iown   |  |  |  |  |

|                     |                                                                                                                                                                                                             |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 15-8            | Unimplement                                                                                                                                                                                                 |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 7               | LSPD: Low-S                                                                                                                                                                                                 | peed Direct C                                          | connection Enabl | le bit (U1EP0 c   | only) <sup>(1)</sup> |                 |        |  |  |  |  |

|                     |                                                                                                                                                                                                             | 1 = Direct connection to a low-speed device is enabled |                  |                   |                      |                 |        |  |  |  |  |

|                     |                                                                                                                                                                                                             |                                                        | low-speed device |                   |                      |                 |        |  |  |  |  |

| bit 6               |                                                                                                                                                                                                             | •                                                      | bit (U1EP0 only) | (1)               |                      |                 |        |  |  |  |  |

|                     | <ul> <li>1 = Retry NAK transactions are disabled</li> <li>0 = Retry NAK transactions are enabled; retry done in hardware</li> </ul>                                                                         |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | -                                                                                                                                                                                                           |                                                        |                  | ary done in har   | dware                |                 |        |  |  |  |  |

| bit 5               | Unimplement                                                                                                                                                                                                 |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 4               | EPCONDIS: Bidirectional Endpoint Control bit                                                                                                                                                                |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | If EPTXEN and EPRXEN = 1:                                                                                                                                                                                   |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | <ul> <li>1 = Disable Endpoint n from Control transfers; only Tx and Rx transfers are allowed</li> <li>0 = Enable Endpoint n for Control (SETUP) transfers; Tx and Rx transfers also are allowed.</li> </ul> |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | For all other combinations of EPTXEN and EPRXEN:                                                                                                                                                            |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | This bit is ignored.                                                                                                                                                                                        |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 3               | EPRXEN: End                                                                                                                                                                                                 | dpoint Receiv                                          | e Enable bit     |                   |                      |                 |        |  |  |  |  |

|                     | 1 = Endpoint n receive is enabled                                                                                                                                                                           |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | 0 = Endpoint n receive is disabled                                                                                                                                                                          |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 2               | EPTXEN: Endpoint Transmit Enable bit                                                                                                                                                                        |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | 1 = Endpoint n transmit is enabled                                                                                                                                                                          |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | 0 = Endpoint n transmit is disabled                                                                                                                                                                         |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 1               | EPSTALL: Endpoint Stall Status bit                                                                                                                                                                          |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | 1 = Endpoint                                                                                                                                                                                                |                                                        |                  |                   |                      |                 |        |  |  |  |  |

|                     | 0 = Endpoint                                                                                                                                                                                                | n was not sta                                          | lled             |                   |                      |                 |        |  |  |  |  |

|                     |                                                                                                                                                                                                             |                                                        |                  |                   |                      |                 |        |  |  |  |  |

| bit 0               |                                                                                                                                                                                                             | •                                                      | hake Enable bit  |                   |                      |                 |        |  |  |  |  |

| bit 0               | 1 = Endpoint                                                                                                                                                                                                | handshake is                                           |                  |                   |                      |                 |        |  |  |  |  |

Note 1: These bits are available only for U1EP0, and only in Host mode. For all other U1EPn registers, these bits are always unimplemented and read as '0'.

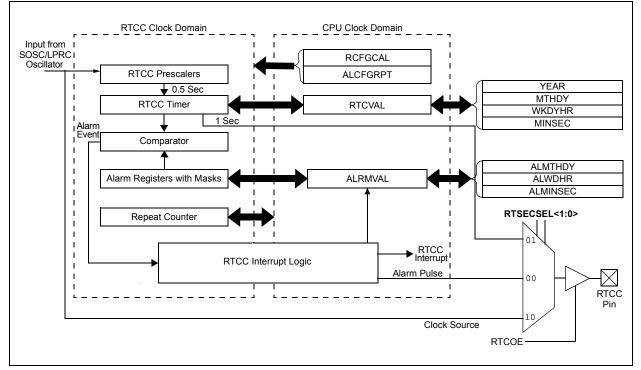

# 20.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 29. "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Deep Sleep mode

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- BCD format for smaller software overhead

- Optimized for long-term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

# 20.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator or the LPRC Low-Power Internal RC Oscillator as the clock reference for the RTCC module. This is configured using the RTCOSC (CW4<5>) Configuration bit. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

The SOSC and RTCC will both remain running while the device is held in Reset with  $\overline{\text{MCLR}}$  and will continue running after  $\overline{\text{MCLR}}$  is released.

# FIGURE 20-1: RTCC BLOCK DIAGRAM

# REGISTER 23-1: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 THROUGH 3)

|               | •                            |                                                |               | •                 |                 |                  |                  |  |  |

|---------------|------------------------------|------------------------------------------------|---------------|-------------------|-----------------|------------------|------------------|--|--|

| R/W-0         | R/W-0                        | R/W-0                                          | U-0           | U-0               | U-0             | R/W-0            | R-0              |  |  |

| CEN           | COE                          | CPOL                                           | —             | —                 | —               | CEVT             | COUT             |  |  |

| bit 15        |                              |                                                |               |                   |                 |                  | bit 8            |  |  |

|               |                              |                                                |               |                   |                 |                  |                  |  |  |

| R/W-0         | R/W-0                        | U-0                                            | R/W-0         | U-0               | U-0             | R/W-0            | R/W-0            |  |  |

| EVPOL1        | EVPOL0                       | <u> </u>                                       | CREF          |                   | <u> </u>        | CCH1             | CCH0             |  |  |

| bit 7         |                              |                                                |               |                   |                 |                  | bit 0            |  |  |

|               |                              |                                                |               |                   |                 |                  |                  |  |  |

| Legend:       |                              |                                                |               |                   |                 |                  |                  |  |  |

| R = Readabl   | e bit                        | W = Writable b                                 | it            | U = Unimplen      | nented bit, rea | d as '0'         |                  |  |  |

| -n = Value at | POR                          | '1' = Bit is set                               |               | '0' = Bit is clea | ared            | x = Bit is unkr  | nown             |  |  |

|               |                              |                                                |               |                   |                 |                  |                  |  |  |

| bit 15        | CEN: Compa                   | rator Enable bit                               |               |                   |                 |                  |                  |  |  |

|               |                              | 1 = Comparator is enabled                      |               |                   |                 |                  |                  |  |  |

|               | 0 = Compara                  | 0 = Comparator is disabled                     |               |                   |                 |                  |                  |  |  |

| bit 14        | =                            | rator Output Ena                               |               |                   |                 |                  |                  |  |  |

|               |                              | ator output is pre                             |               | xOUT pin.         |                 |                  |                  |  |  |

| 1.11.40       | •                            | ator output is inte                            | 3             | 1.11              |                 |                  |                  |  |  |

| bit 13        |                              | parator Output Po                              | •             | bit               |                 |                  |                  |  |  |

|               |                              | ator output is inve<br>ator output is not      |               |                   |                 |                  |                  |  |  |

| bit 12-10     | Unimplemen                   | ted: Read as '0                                |               |                   |                 |                  |                  |  |  |

| bit 9         | -                            | arator Event bit                               |               |                   |                 |                  |                  |  |  |

|               | •                            | ator event define                              | d by EVPOL    | <1:0> has occu    | rred; subseque  | ent triggers and | l interrupts are |  |  |

|               |                              | until the bit is cle                           |               |                   |                 |                  |                  |  |  |

|               | 0 = Compara                  | ator event has no                              | ot occurred   |                   |                 |                  |                  |  |  |

| bit 8         |                              | parator Output bi                              | t             |                   |                 |                  |                  |  |  |

|               | When CPOL                    |                                                |               |                   |                 |                  |                  |  |  |

|               | 1 = VIN+ > V<br>0 = VIN+ < V |                                                |               |                   |                 |                  |                  |  |  |

|               | When CPOL                    |                                                |               |                   |                 |                  |                  |  |  |

|               | 1 = VIN+ < V                 |                                                |               |                   |                 |                  |                  |  |  |

|               | 0 = VIN + > V                | IN-                                            |               |                   |                 |                  |                  |  |  |

| bit 7-6       | EVPOL<1:0>                   | : Trigger/Event/I                              | nterrupt Pola | rity Select bits  |                 |                  |                  |  |  |

|               |                              | /event/interrupt                               |               |                   |                 |                  | CEVT = 0)        |  |  |

|               |                              | /event/interrupt                               | -             | transition of the | e comparator c  | output:          |                  |  |  |

|               |                              | L = 0 (non-invert                              |               |                   |                 |                  |                  |  |  |

|               | -                            | o-low transition o<br>L = <u>1</u> (inverted p | -             |                   |                 |                  |                  |  |  |

|               |                              | -high transition c                             |               |                   |                 |                  |                  |  |  |

|               |                              | /event/interrupt                               |               | transition of co  | mparator outp   | ut:              |                  |  |  |

|               |                              | <u>L = 0 (non-invert</u>                       |               |                   |                 |                  |                  |  |  |

|               |                              | -high transition c                             |               |                   |                 |                  |                  |  |  |

|               |                              | L = 1 (inverted p                              |               |                   |                 |                  |                  |  |  |

|               |                              | -low transition o                              |               | disabled          |                 |                  |                  |  |  |