Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32gb004t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

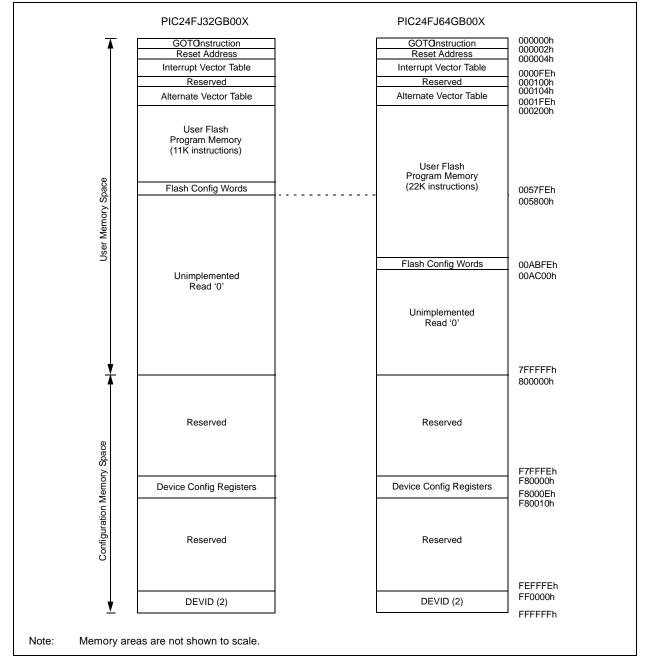

### 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and busses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the PIC24FJ64GB004 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in Section 4.3 "Interfacing Program and Data Memory Spaces" .

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ64GB004 family of devices are shown in Figure 4-1.

| FIGURE 4-1: | PROGRAM SPACE MEMORY MA P FOR PIC24FJ64GB004 FAMILY DEVICES |

|-------------|-------------------------------------------------------------|

|             |                                                             |

### TABLE 4-6: TIMER REGISTER MAP

|           | 0.   |        |        |        |        |        | -      |              | -            |               | -             |         |        |      |           |       |   |               |

|-----------|------|--------|--------|--------|--------|--------|--------|--------------|--------------|---------------|---------------|---------|--------|------|-----------|-------|---|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6 E       | Sit5 B  | t4 Bi  | t3 E | Bit 2 Bit | 1 Bit | 0 | All<br>Resets |

| TMR1      | 0100 |        |        |        |        |        |        |              | Timer1       | Register      |               |         |        |      |           |       |   | 0000          |

| PR1       | 0102 |        |        |        |        |        |        |              | Timer1 Per   | iod Registe   | r             |         |        |      |           |       |   | FFFF          |

| T1CON     | 0104 | TON    |        | TSIDL  | —      | —      | _      | —            | —            | —             | TGATE         | TCKPS1  | TCKPS0 | —    | TSYNC     | TCS   | — | 0000          |

| TMR2      | 0106 |        |        |        |        |        |        |              | Timer2       | Register      |               |         |        |      |           |       |   | 0000          |

| TMR3HLD   | 0108 |        |        |        |        |        | Time   | r3 Holding I | Register (fo | r 32-bit time | er operations | s only) |        |      |           |       |   | 0000          |

| TMR3      | 010A |        |        |        |        |        |        |              | Timer3       | Register      |               |         |        |      |           |       |   | 0000          |

| PR2       | 010C |        |        |        |        |        |        |              | Timer2 Per   | iod Registe   | r             |         |        |      |           |       |   | FFFF          |

| PR3       | 010E |        |        |        |        |        |        |              | Timer3 Per   | iod Registe   | r             |         |        |      |           |       |   | FFFF          |

| T2CON     | 0110 | TON    |        | TSIDL  | —      | —      | _      | —            | —            | —             | TGATE         | TCKPS1  | TCKPS0 | T32  | _         | TCS   | — | 0000          |

| T3CON     | 0112 | TON    | _      | TSIDL  | —      | —      | _      | —            | —            | —             | TGATE         | TCKPS1  | TCKPS0 | —    | _         | TCS   | — | 0000          |

| TMR4      | 0114 |        |        |        |        |        |        |              | Timer4       | Register      |               |         |        |      |           |       |   | 0000          |

| TMR5HLD   | 0116 |        |        |        |        |        | Tir    | mer5 Holdir  | g Register   | (for 32-bit c | perations o   | nly)    |        |      |           |       |   | 0000          |

| TMR5      | 0118 |        |        |        |        |        |        |              | Timer5       | Register      |               |         |        |      |           |       |   | 0000          |

| PR4       | 011A |        |        |        |        |        |        |              | Timer4 Per   | iod Registe   | r             |         |        |      |           |       |   | FFFF          |

| PR5       | 011C |        |        |        |        |        |        |              | Timer5 Per   | iod Registe   | r             |         |        |      |           |       |   | FFFF          |

| T4CON     | 011E | TON    |        | TSIDL  | —      | —      | _      | —            | —            |               | TGATE         | TCKPS1  | TCKPS0 | T32  |           | TCS   |   | 0000          |

| T5CON     | 0120 | TON    |        | TSIDL  | _      | _      | _      | —            | _            | -             | TGATE         | TCKPS1  | TCKPS0 | —    | —         | TCS   |   | 0000          |

PIC24FJ64GB004 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0              | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                                                                   | U-0                            | U-0               | U-0             | U-0             | U-0    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|-----------------|-----------------|--------|

| ALTIVT             | DISI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                     | _                              | —                 | —               | —               | —      |

| bit 15             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                       |                                |                   |                 |                 | bit 8  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                |                   |                 |                 |        |

| U-0                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                                                                   | U-0                            | U-0               | R/W-0           | R/W-0           | R/W-0  |

| —                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                |                   | INT2EP          | INT1EP          | INT0EP |

| bit 7              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                |                   |                 |                 | bit (  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                |                   |                 |                 |        |

| Legend:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                |                   |                 |                 |        |

| R = Readab         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable b                                                                                                        | bit                            | -                 | nented bit, rea |                 |        |

| -n = Value a       | it POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                      |                                | '0' = Bit is clea | ared            | x = Bit is unkr | iown   |

| bit 14<br>bit 13-3 | 0 = Use stand<br>DISI: DISI Ins<br>1 = DISI instr<br>0 = DISI instr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | hate Interrupt Vo<br>ard (default) In<br>struction Status<br>ruction is active<br>ruction is not ac<br>ed: Read as '0 | terrupt Vector<br>bit<br>ctive | Table (IVT)       |                 |                 |        |

| bit 2              | INT2EP: Extended in the Interrupt of the |                                                                                                                       | Edge Detect I                  | Polarity Select I | bit             |                 |        |

| bit 1              | 1 = Interrupt o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rnal Interrupt 1<br>on negative edg<br>on positive edge                                                               | e                              | Polarity Select I | bit             |                 |        |

| bit 0              | 1 = Interrupt o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rnal Interrupt 0<br>In negative edg<br>In positive edge                                                               | e                              | Polarity Select I | bit             |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

#### 10.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ64GB004 family of devices implements a total of 27 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (14)

- Output Remappable Peripheral Registers (13)

## REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0                                | U-0 | U-0 | R/W-1                                   | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|------------------------------------|-----|-----|-----------------------------------------|--------|--------|--------|--------|

| —                                  | —   | —   | INT1R4                                  | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15                             |     |     |                                         |        |        |        | bit 8  |

|                                    |     |     |                                         |        |        |        |        |

| U-0                                | U-0 | U-0 | U-0                                     | U-0    | U-0    | U-0    | U-0    |

| _                                  |     | —   | _                                       |        | _      | —      | _      |

| bit 7                              | •   |     |                                         |        |        |        | bit 0  |

|                                    |     |     |                                         |        |        |        |        |

| Legend:                            |     |     |                                         |        |        |        |        |

| R = Readable bit W = Writable bit  |     |     | U = Unimplemented bit, read as '0'      |        |        |        |        |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |        |

|                                    |     |     |                                         |        |        |        |        |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 INT1R<4:0>: Assign External Interrupt 1 (INT1) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 INT1R<4:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.4.1 "Control Register Lock" for a specific command sequence.

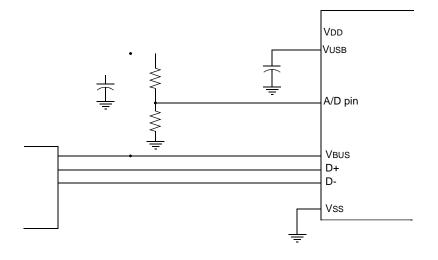

#### 18.1.2 HOST AND OTG MODES

#### 18.1.2.1 D+ and D- Pull-down Resistors

PIC24FJ64GB004 family devices have built-in 15 k : pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the HOSTEN bit (U1CON<3>). If the OTGEN bit (U1OTGCON<2>) is set, then these pull-downs are enabled by setting the DPPULDWN and DMPULDWN bits (U1OTGCON<5:4>).

#### 18.1.2.2 Power Configurations

In Host mode, as well as Host mode in On-the-Go operation, the USB 2.0 specification requires that the Host application supply power on VBUS. Since the

#### FIGURE 18-6: HOST INTERFACE EXAMPLE

microcontroller is running below VBUS and is not able to source sufficient current, a separate power supply must be provided.

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 18-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 18-7.

FIGURE 18-7: OTG INTERFACE EXAMPLE

#### 18.5.3 SEND A FULL-SPEED BULK DATA TRANSFER TO A TARGET DEVICE

- Follow the procedure described in Section 18.5.1 "Enable Host Mode and Discover a Connected Device" and Section 18.5.2 "Complete a Control Transaction to a Connected Device" to discover and configure a device.

- To enable transmit and receive transfers with handshaking enabled, write 1Dh to U1EP0. If the target device is a low-speed device, also set the LSPD bit (U1EP0<7>). If you want the hardware to automatically retry indefinitely if the target device asserts a NAK on the transfer, clear the Retry Disable bit, RETRYDIS (U1EP0<6>).

- 3. Set up the BD for the current (EVEN or ODD) Tx EP0 to transfer up to 64 bytes.

- 4. Set the USB device address of the target device in the address register (U1ADDR<6:0>).

- 5. Write an OUT token to the desired endpoint to U1TOK. This triggers the module's transmit state machines to begin transmitting the token and the data.

- 6. Wait for the Transfer Done Interrupt Flag, TRNIF. This indicates that the BD has been released back to the microprocessor, and the transfer has completed. If the retry disable bit is set, the handshake (ACK, NAK, STALL or ERROR (0Fh)) is returned in the BD PID field. If a STALL interrupt occurs, the pending packet must be dequeued and the error condition in the target device cleared. If a detach interrupt occurs (SE0 for more than 2.5 Rs), then the target has detached (U1IR<0> is set).

- 7. Once the transfer done interrupt occurs (TRNIF is set), the BD can be examined and the next data packet queued by returning to step 2.

- Note: USB speed, transceiver and pull-ups should only be configured during the module setup phase. It is not recommended to change these settings while the module is enabled.

### 18.6 OTG Operation

#### 18.6.1 SESSION REQUEST PROTOCOL (SRP)

An OTG A-device may decide to power down the VBUS supply when it is not using the USB link through the Session Request Protocol (SRP). Software may do this by clearing VBUSON (U1OTGCON<3>). When the VBUS supply is powered down, the A-device is said to have ended a USB session.

An OTG A-device or Embedded Host may re-power the VBUS supply at any time (initiate a new session). An OTG B-device may also request that the OTG A-device re-power the VBUS supply (initiate a new session). This is accomplished via Session Request Protocol (SRP).

Prior to requesting a new session, the B-device must first check that the previous session has definitely ended. To do this, the B-device must check for two conditions:

1. VBUS supply is below the Session Valid voltage, and

2. Both D+ and D- have been low for at least 2 ms.

The B-device will be notified of condition 1 by the SESENDIF (U1OTGIR<2>) interrupt. Software will have to manually check for condition 2.

| Note: | When the A-device powers down the VBUS        |

|-------|-----------------------------------------------|

|       | supply, the B-device must disconnect its      |

|       | pull-up resistor from power. If the device is |

|       | self-powered, it can do this by clearing      |

|       | DPPULUP (U1OTGCON<7>) and                     |

|       | DMPULUP (U1OTGCON<6>).                        |

The B-device may aid in achieving condition 1 by discharging the VBUS supply through a resistor. Software may do this by setting VBUSDIS (U1OTGCON<0>).

After these initial conditions are met, the B-device may begin requesting the new session. The B-device begins by pulsing the D+ data line. Software should do this by setting DPPULUP (U10TGCON<7>). The data line should be held high for 5 to 10 ms.

### 18.7.1 USB OTG MODULE CONTROL REGISTERS

#### REGISTER 18-3: U1OTGSTAT: USB OTG ST ATUS REGISTER (HOST MODE ONLY)

| U-0      | U-0 | U-0      | U-0 | U-0      | U-0      | U-0 | U-0      |

|----------|-----|----------|-----|----------|----------|-----|----------|

|          |     |          |     |          |          |     |          |

|          |     | _        | —   |          |          | —   |          |

| bit 15   |     |          |     |          |          |     | bit 8    |

|          |     |          |     |          |          |     |          |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

| ID       | —   | LSTATE   | —   | SESVD    | SESEND   | —   | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

|          |     |          |     |          |          |     |          |

| Legend:           | U = Unimplemented bit, read as '0' |                           |                    |  |  |

|-------------------|------------------------------------|---------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/C | Clearable bit      |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared      | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                            |

|          | <ul> <li>1 = No plug is attached, or a type B cable has been plugged into the USB receptacle</li> <li>0 = A type A plug has been plugged into the USB receptacle</li> </ul>               |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                   |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has NOT been stable for the previous 1 ms</li> </ul> |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_SESS_VLD (as defined in the USB OTG Specification) on the A or<br>B-device                                                                               |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                            |

| bit 2    | SESEND: B-Session End Indicator bit                                                                                                                                                       |

|          | 1 = The VBUS voltage is below VB_SESS_END (as defined in the USB OTG Specification) on the<br>B-device                                                                                    |

|          | 0 = The VBUS voltage is above VB_SESS_END on the B-device                                                                                                                                 |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 0    | VBUSVD: A-VBUS Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the USB OTG Specification) on the<br>A-device                                                                                    |

|          | 0 = The VBUS voltage is below VA_VBUS_VLD on the A-device                                                                                                                                 |

|          |                                                                                                                                                                                           |

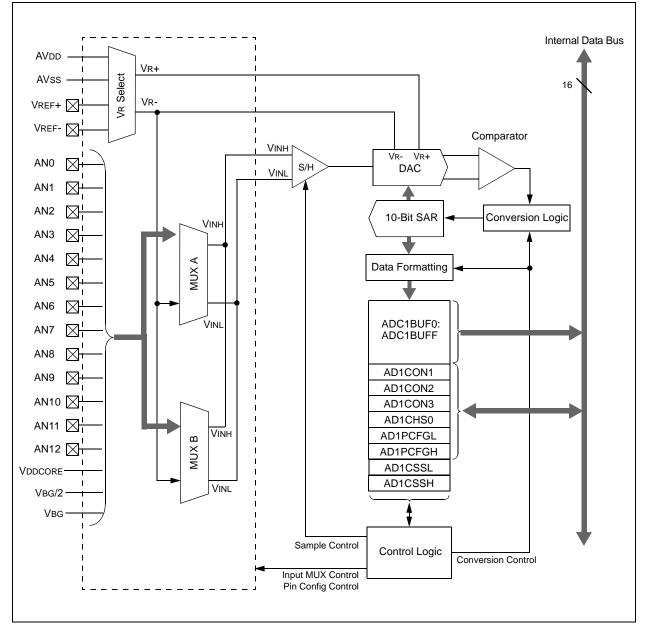

### 22.0 10-BIT HIGH-SPEED A/D CONVERTER

| Note: | This data sheet summarizes the features    |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |

|       | Section 17. "10-Bit A/D Converter"         |  |  |  |  |  |

|       | (DS39705).                                 |  |  |  |  |  |

The 10-bit A/D Converter has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 500 ksps

- 13 analog input pins

- External voltage reference input pins

- Internal band gap reference inputs

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- Selectable Buffer Fill modes

- Four result alignment options

- Operation during CPU Sleep and Idle modes

On all PIC24FJ64GB004 family devices, the 10-bit A/D Converter has 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is shown in Figure 22-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- Configure port pins as analog inputs and/or select band gap reference inputs (AD1PCFGL<15:0> and AD1PCFGH<1:0>).

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select A/D interrupt priority.

#### FIGURE 22-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

## 23.0 TRIPLE COMPARATOR MODULE

| Note: | This data sheet summarizes the features    |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |

|       | associated "PIC24F Family Reference        |  |  |  |  |  |

|       | Manual", Section 46. "Scalable             |  |  |  |  |  |

|       | Comparator Module" (DS39734).              |  |  |  |  |  |

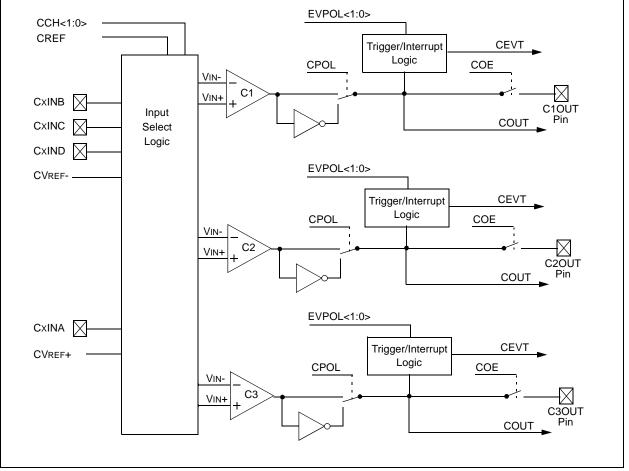

The triple comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as voltage reference inputs from the voltage reference generator and band gap reference. The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module in shown in Figure 23-1. Diagrams of the possible individual comparator configurations are shown in Figure 23-2.

Each comparator has its own control register, CMxCON (Register 23-1), for enabling and configuring its operation. The output and event status of all three comparators are provided in the CMSTAT register (Register 23-2).

## FIGURE 23-1: TRIPLE COMPARATOR MODULE BLOCK DIAGRAM

#### 29.1 DC Characteristics

#### TABLE 29-7: DC CHARACTERISTICS: POWER-DOWN PERIPHERAL MODULE ' CURRENT (IPD) (CONTINUED)

|                    | MODULE                 | CURREN       | NT (IPD) (CO                                                                                                                                                     |               |                     |                                                                                      |  |

|--------------------|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|--------------------------------------------------------------------------------------|--|

| DC CHARACTERISTICS |                        |              | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)<br>Operating temperature -40°C dTA d+85°C for Industrial<br>-40°C dTA d+125°C for Extended |               |                     |                                                                                      |  |

| Parameter<br>No.   | Typical <sup>(1)</sup> | Max          | Units                                                                                                                                                            |               | (                   | Conditions                                                                           |  |

| ' Power-Dowr       | n Current (I PE        | o): PMD Bits | are Set, PMS                                                                                                                                                     | LP Bit is ' 0 | ,(2)                |                                                                                      |  |

| DC63               | 1.8                    | 2.3          | FA                                                                                                                                                               | -40°C         |                     |                                                                                      |  |

| DC63a              | 1.8                    | 2.7          | FA                                                                                                                                                               | +25°C         | 2.0V <sup>(3)</sup> |                                                                                      |  |

| DC63i              | 1.8                    | 3.0          | FA                                                                                                                                                               | +60°C         |                     |                                                                                      |  |

| DC63b              | 1.8                    | 3.0          | FA                                                                                                                                                               | +85°C         |                     |                                                                                      |  |

| DC63m              | 2.2                    | 3.3          | FA                                                                                                                                                               | +125C         |                     |                                                                                      |  |

| DC63c              | 2                      | 2.7          | FA                                                                                                                                                               | -40°C         |                     |                                                                                      |  |

| DC63d              | 2                      | 2.9          | FA                                                                                                                                                               | +25°C         |                     | 32 kHz Crystal with RTCC,<br>DSWDT or Timer1: 'ISOSC;<br>SOSCSEL = 11 <sup>(5)</sup> |  |

| DC63j              | 2                      | 3.2          | FA                                                                                                                                                               | +60°C         | 2.5V <sup>(3)</sup> |                                                                                      |  |

| DC63e              | 2                      | 3.5          | FA                                                                                                                                                               | +85°C         |                     |                                                                                      |  |

| DC63n              | 2.5                    | 3.8          | FA                                                                                                                                                               | +125C         |                     |                                                                                      |  |

| DC63f              | 2.25                   | 3.0          | FA                                                                                                                                                               | -40°C         |                     |                                                                                      |  |

| DC63g              | 2.25                   | 3.0          | FA                                                                                                                                                               | +25°C         |                     |                                                                                      |  |

| DC63k              | 2.25                   | 3.3          | FA                                                                                                                                                               | +60°C         | 3.3V <sup>(4)</sup> |                                                                                      |  |

| DC63h              | 2.25                   | 3.5          | FA                                                                                                                                                               | +85°C         |                     |                                                                                      |  |

| DC63p              | 2.8                    | 4.0          | FA                                                                                                                                                               | +125C         |                     |                                                                                      |  |

| DC71c              | 0.001                  | 0.25         | FA                                                                                                                                                               | -40°C         |                     |                                                                                      |  |

| DC71d              | 0.03                   | 0.25         | FA                                                                                                                                                               | +25°C         |                     |                                                                                      |  |

| DC71j              | 0.05                   | 0.60         | FA                                                                                                                                                               | +60°C         | 2.5V <sup>(4)</sup> | - Deep Sleep BOR: 'IDSBOR <sup>(5)</sup>                                             |  |

| DC71e              | 0.08                   | 2.0          | FA                                                                                                                                                               | +85°C         |                     |                                                                                      |  |

| DC71a              | 3.9                    | 10           | FA                                                                                                                                                               | +125C         |                     |                                                                                      |  |

| DC71f              | 0.001                  | 0.50         | FA                                                                                                                                                               | -40°C         |                     |                                                                                      |  |

| DC71g              | 0.03                   | 0.50         | FA                                                                                                                                                               | +25°C         |                     |                                                                                      |  |

| DC71k              | 0.05                   | 0.75         | FA                                                                                                                                                               | +60°C         | 3.3V <sup>(4)</sup> |                                                                                      |  |

| DC71h              | 0.08                   | 2.5          | FA                                                                                                                                                               | +85°C         |                     |                                                                                      |  |

| DC71b              | 3.9                    | 12.5         | FA                                                                                                                                                               | +125C         |                     |                                                                                      |  |

Note 1: Data in the Typical column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Peripheral IPD deltas are measured with the device in Sleep mode (all peripherals and clocks shut down). All I/Os are configured as inputs and pulled high. Only the peripheral or clock being measured is enabled. PMSLP bit is clear and the Peripheral Module Disable bits (PMD) for all unused peripherals are set.

3: On-chip voltage regulator disabled (DISVREG tied to VDD).

4: On-chip voltage regulator enabled (DISVREG tied to Vss). Low-Voltage Detect (LVD) and Brown-out Detect (BOD) are enabled.

5: The ' current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

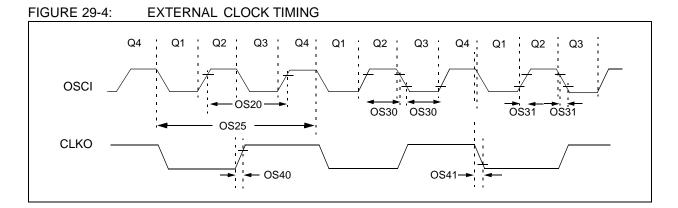

#### TABLE 29-16: EXTERNAL CLO CK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               | Standard Operating Conditions: 2.50 to 3.6V (unless otherwise stated)<br>Operating temperature -40°C dTA d+85°C for Industrial<br>-40°C dTA d+125°C for Extended |                               |                    |                                |                                        |                                                                                                                    |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|--------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym           | Characteristic                                                                                                                                                   | Min                           | Тур <sup>(1)</sup> | Max                            | Units                                  | Conditions                                                                                                         |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode)                                                                                          | DC<br>4<br>DC<br>4            |                    | 32<br>8<br>24<br>6             | MHz<br>MHz<br>MHz<br>MHz               | EC, -40°C dTA d+85°C<br>ECPLL, -40°C dTA d+85°C<br>EC, -40°C dTA d+125°C<br>ECPLL, -40°C dTA d+125°C               |

|                    |               | Oscillator Frequency                                                                                                                                             | 3<br>3<br>10<br>31<br>3<br>10 |                    | 10<br>8<br>32<br>33<br>6<br>24 | MHz<br>MHz<br>MHz<br>kHz<br>MHz<br>MHz | XT<br>XTPLL, -40°C dTA d+85°C<br>HS, -40°C dTA d+85°C<br>SOSC<br>XTPLL, -40°C dTA d+125°C<br>HS, -40°C dTA d+125°C |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                                                                                                    | —                             | —                  | —                              | —                                      | See parameter OS10<br>for Fosc value                                                                               |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                                                                                                            | 62.5                          | —                  | DC                             | ns                                     |                                                                                                                    |

| OS30               | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                                                                                                                     | 0.45 x Tosc                   | _                  | —                              | ns                                     | EC                                                                                                                 |

| OS31               | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                                                                                                                    | —                             | _                  | 20                             | ns                                     | EC                                                                                                                 |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                                                                                                                    | _                             | 6                  | 10                             | ns                                     |                                                                                                                    |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                                                                                                                    | —                             | 6                  | 10                             | ns                                     |                                                                                                                    |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TCY) and high for the Q3-Q4 period (1/2 TCY).

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Pin Count                                                                                                                                                                                                                                                                          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|