Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| 2014                       |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb002-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLE     | 4-J. |        |         | CONTR   | OLLER   | KEGI   |          | AF       |          |       |          |          |          |         |               |          |          |              |

|-----------|------|--------|---------|---------|---------|--------|----------|----------|----------|-------|----------|----------|----------|---------|---------------|----------|----------|--------------|

| File Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2         | Bit 1    | Bit 0    | All<br>Reset |

| INTCON1   | 0080 | NSTDIS | _       | _       | _       |        | _        | _        | _        | _     | _        | _        | MATHERR  | ADDRERR | STKERR        | OSCFAIL  | _        | 0000         |

| INTCON2   | 0082 | ALTIVT | DISI    | —       | _       | _      | _        | _        | —        | _     | _        | _        | _        | _       | INT2EP        | INT1EP   | INT0EP   | 0000         |

| IFS0      | 0084 | _      | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF   | SPF1IF   | T3IF     | T2IF  | OC2IF    | IC2IF    | _        | T1IF    | OC1IF         | IC1IF    | INT0IF   | 0000         |

| IFS1      | 0086 | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | OC4IF    | OC3IF    | _        | _     | _        | _        | INT1IF   | CNIF    | CMIF          | MI2C1IF  | SI2C1IF  | 0000         |

| IFS2      | 0088 | —      | —       | PMPIF   | _       | —      | —        | OC5IF    | —        | IC5IF | IC4IF    | IC3IF    | _        | _       | —             | SPI2IF   | SPF2IF   | 0000         |

| IFS3      | 008A | _      | RTCIF   | _       | _       | _      | _        |          | _        | _     | _        | _        | _        | _       | MI2C2IF       | SI2C2IF  | _        | 0000         |

| IFS4      | 008C | —      | —       | CTMUIF  | _       | _      | _        | _        | LVDIF    | _     | _        | _        | _        | CRCIF   | U2ERIF        | U1ERIF   | _        | 0000         |

| IFS5      | 008E | _      | _       | —       | _       |        | _        | _        | —        |       | USB1IF   | _        | _        | _       | —             | _        |          | 0000         |

| IEC0      | 0094 | —      | —       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE   | SPF1IE   | T3IE     | T2IE  | OC2IE    | IC2IE    | _        | T1IE    | OC1IE         | IC1IE    | INT0IE   | 0000         |

| IEC1      | 0096 | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | OC4IE    | OC3IE    | —        |       | —        | —        | INT1IE   | CNIE    | CMIE          | MI2C1IE  | SI2C1IE  | 0000         |

| IEC2      | 0098 | _      | _       | PMPIE   | _       |        | _        | OC5IE    | _        | IC5IE | IC4IE    | IC3IE    | _        | _       | —             | SPI2IE   | SPF2IE   | 0000         |

| IEC3      | 009A | _      | RTCIE   | —       | _       |        | _        | _        | _        | _     | _        | _        | _        | _       | MI2C2IE       | SI2C2IE  | _        | 0000         |

| IEC4      | 009C | _      | _       | CTMUIE  | _       |        | _        | _        | LVDIE    |       | _        | _        | _        | CRCIE   | <b>U2ERIE</b> | U1ERIE   |          | 0000         |

| IEC5      | 009E | _      | _       | _       | _       | _      | _        | _        | _        | _     | USB1IE   | _        | _        | _       | _             | _        | _        | 000          |

| IPC0      | 00A4 | _      | T1IP2   | T1IP1   | T1IP0   |        | OC1IP2   | OC1IP1   | OC1IP0   |       | IC1IP2   | IC1IP1   | IC1IP0   | _       | INT0IP2       | INT0IP1  | INT0IP0  | 4444         |

| IPC1      | 00A6 | _      | T2IP2   | T2IP1   | T2IP0   |        | OC2IP2   | OC2IP1   | OC2IP0   |       | IC2IP2   | IC2IP1   | IC2IP0   | _       | —             | _        | _        | 4440         |

| IPC2      | 00A8 | _      | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2  | SPI1IP1  | SPI1IP0  | _     | SPF1IP2  | SPF1IP1  | SPF1IP0  | _       | T3IP2         | T3IP1    | T3IP0    | 4444         |

| IPC3      | 00AA | _      | _       | —       | _       |        | _        | _        | —        |       | AD1IP2   | AD1IP1   | AD1IP0   | _       | U1TXIP2       | U1TXIP1  | U1TXIP0  | 0044         |

| IPC4      | 00AC | _      | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2    | CMIP1    | CMIP0    | _     | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2      | SI2C1IP1 | SI2C1IP0 | 4444         |

| IPC5      | 00AE | _      | _       | —       | _       | _      | _        | _        | _        | _     | _        | _        | _        | _       | INT1IP2       | INT1IP1  | INT1IP0  | 0004         |

| IPC6      | 00B0 | _      | T4IP2   | T4IP1   | T4IP0   | _      | OC4IP2   | OC4IP1   | OC4IP0   | _     | OC3IP2   | OC3IP1   | OC3IP0   | _       | —             | _        | _        | 4440         |

| IPC7      | 00B2 | _      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2  | U2RXIP1  | U2RXIP0  | _     | INT2IP2  | INT2IP1  | INT2IP0  | _       | T5IP2         | T5IP1    | T5IP0    | 4444         |

| IPC8      | 00B4 | _      | _       | _       | _       | _      | _        | _        | _        | _     | SPI2IP2  | SPI2IP1  | SPI2IP0  | _       | SPF2IP2       | SPF2IP1  | SPF2IP0  | 0044         |

| IPC9      | 00B6 | _      | IC5IP2  | IC5IP1  | IC5IP0  | _      | IC4IP2   | IC4IP1   | IC4IP0   | _     | IC3IP2   | IC3IP1   | IC3IP0   | _       | —             | _        | _        | 4440         |

| IPC10     | 00B8 | _      | _       | _       | _       | _      | _        | _        | _        | _     | OC5IP2   | OC5IP1   | OC5IP0   | _       | _             | _        | _        | 0040         |

| IPC11     | 00BA | _      | _       | _       | _       | _      | _        | _        | _        | _     | PMPIP2   | PMPIP1   | PMPIP0   | _       | _             | _        | _        | 0040         |

| IPC12     | 00BC | —      | —       | _       | -       | —      | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 |       | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       | _             | —        |          | 0440         |

| IPC15     | 00C2 | —      | —       | _       | -       | —      | RTCIP2   | RTCIP1   | RTCIP0   |       | _        | _        |          | —       | _             | —        |          | 0400         |

| IPC16     | 00C4 | —      | CRCIP2  | CRCIP1  | CRCIP0  | —      | U2ERIP2  | U2ERIP1  | U2ERIP0  |       | U1ERIP2  | U1ERIP1  | U1ERIP0  | _       | _             | _        |          | 4440         |

| IPC18     | 00C8 |        |         | _       |         |        |          |          | _        |       |          | _        | _        | _       | LVDIP2        | LVDIP1   | LVDIP0   | 0004         |

| IPC19     | 00CA | —      | _       | _       | _       | —      | _        | _        | _        |       | CTMUIP2  | CTMUIP1  | CTMUIP0  | —       |               | _        |          | 0040         |

| IPC21     | 00CE | —      | _       | _       | _       | —      | USB1IP2  | USB1IP1  | USB1IP0  | _     | _        | —        | _        | _       | _             | _        | _        | 0400         |

| INTTREG   | 00E0 | CPUIRQ | _       | VHOLD   |         | ILR3   | ILR2     | ILR1     | ILR0     |       | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2       | VECNUM1  | VECNUM0  | 0000         |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0                   | U-0                                                                                                | R/W-0                                  | U-0            | U-0               | U-0              | U-0             | R/W-0 |

|-----------------------|----------------------------------------------------------------------------------------------------|----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| _                     | —                                                                                                  | CTMUIE                                 | _              | —                 |                  | —               | LVDIE |

| bit 15                |                                                                                                    |                                        |                |                   |                  |                 | bit 8 |

|                       |                                                                                                    |                                        |                |                   |                  |                 |       |

| U-0                   | U-0                                                                                                | U-0                                    | U-0            | R/W-0             | R/W-0            | R/W-0           | U-0   |

| _                     | _                                                                                                  | —                                      |                | CRCIE             | U2ERIE           | U1ERIE          | _     |

| bit 7                 |                                                                                                    |                                        |                |                   |                  |                 | bit ( |

| Logondi               |                                                                                                    |                                        |                |                   |                  |                 |       |

| Legend:<br>R = Readab | lo hit                                                                                             | W = Writable b                         | .i+            |                   | ontod hit road   | 1 00 '0'        |       |

|                       |                                                                                                    |                                        | Л              | •                 | nented bit, read |                 | 0.475 |

| -n = Value a          | IL POR                                                                                             | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

| bit 15-14             | Unimplemen                                                                                         | ted: Read as '0                        | ,              |                   |                  |                 |       |

| bit 13                | -                                                                                                  | MU Interrupt En                        |                |                   |                  |                 |       |

|                       |                                                                                                    | request is enable                      |                |                   |                  |                 |       |

|                       |                                                                                                    | request is not er                      |                |                   |                  |                 |       |

| bit 12-9              | Unimplemen                                                                                         | ted: Read as '0                        | ,              |                   |                  |                 |       |

| bit 8                 | LVDIE: Low-\                                                                                       | Voltage Detect Ir                      | nterrupt Enabl | e bit             |                  |                 |       |

|                       |                                                                                                    | request is enable<br>request is not er |                |                   |                  |                 |       |

| bit 7-4               | Unimplemen                                                                                         | ted: Read as '0                        | ,              |                   |                  |                 |       |

| bit 3                 | CRCIE: CRC                                                                                         | Generator Inter                        | rupt Enable bi | it                |                  |                 |       |

|                       |                                                                                                    | request is enable                      |                |                   |                  |                 |       |

|                       | -                                                                                                  | request is not er                      |                |                   |                  |                 |       |

| bit 2                 |                                                                                                    | RT2 Error Interru                      | •              |                   |                  |                 |       |

|                       | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                        |                |                   |                  |                 |       |

| bit 1                 |                                                                                                    | RT1 Error Interru                      |                |                   |                  |                 |       |

|                       | 1 = Interrupt r<br>0 = Interrupt r                                                                 | request is enable                      |                |                   |                  |                 |       |

|                       |                                                                                                    | request is not er                      | labicu         |                   |                  |                 |       |

#### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0              | U-0            | U-0                | U-0              | U-0                                | R/W-0   | R/W-0              | R/W-0   |  |  |

|------------------|----------------|--------------------|------------------|------------------------------------|---------|--------------------|---------|--|--|

| _                | _              | _                  | _                |                                    | USB1IP2 | USB1IP1            | USB1IP0 |  |  |

| bit 15           |                |                    |                  |                                    |         |                    | bit 8   |  |  |

|                  |                |                    |                  |                                    |         |                    |         |  |  |

| U-0              | U-0            | U-0                | U-0              | U-0                                | U-0     | U-0                | U-0     |  |  |

|                  | —              | —                  | —                | —                                  | —       | —                  | —       |  |  |

| bit 7            |                |                    |                  |                                    |         |                    | bit 0   |  |  |

|                  |                |                    |                  |                                    |         |                    |         |  |  |

| Legend:          |                |                    |                  |                                    |         |                    |         |  |  |

| R = Readable bit |                | W = Writable       | bit              | U = Unimplemented bit, read as '0' |         |                    |         |  |  |

| -n = Value a     | It POR         | '1' = Bit is set   |                  | '0' = Bit is clea                  | ared    | x = Bit is unknown |         |  |  |

|                  |                |                    |                  |                                    |         |                    |         |  |  |

| bit 15-11        | Unimplemen     | ted: Read as '     | כ'               |                                    |         |                    |         |  |  |

| bit 10-8         | USB1IP<2:0>    | : USB Interrup     | t Priority bits  |                                    |         |                    |         |  |  |

|                  | 111 = Interrup | ot is Priority 7 ( | highest priority | interrupt)                         |         |                    |         |  |  |

|                  | •              |                    |                  |                                    |         |                    |         |  |  |

|                  | •              |                    |                  |                                    |         |                    |         |  |  |

|                  | •              |                    |                  |                                    |         |                    |         |  |  |

|                  | 001 = Interrup |                    |                  |                                    |         |                    |         |  |  |

|                  | •              | ot source is dis   |                  |                                    |         |                    |         |  |  |

| bit 7-0          | Unimplemen     | ted: Read as '     | כ'               |                                    |         |                    |         |  |  |

|                  |                |                    |                  |                                    |         |                    |         |  |  |

## REGISTER 7-34: IPC21: INTERRUPT PRIORITY CONTROL REGISTER 21

# 9.2.4.3 Exiting Deep Sleep Mode

Deep Sleep mode exits on any one of the following events:

- POR event on VDD supply. If there is no DSBOR circuit to re-arm the VDD supply POR circuit, the external VDD supply must be lowered to the natural arming voltage of the POR circuit.

- DSWDT time-out. When the DSWDT timer times out, the device exits Deep Sleep.

- RTCC alarm (if RTCEN = 1).

- Assertion ('0') of the  $\overline{\text{MCLR}}$  pin.

- Assertion of the INT0 pin (if the interrupt was enabled before Deep Sleep mode was entered). The polarity configuration is used to determine the assertion level ('0' or '1') of the pin that will cause an exit from Deep Sleep mode. Exiting from Deep Sleep mode requires a change on the INT0 pin while in Deep Sleep mode.

# **Note:** Any interrupt pending when entering Deep Sleep mode is cleared.

Exiting Deep Sleep mode generally does not retain the state of the device and is equivalent to a Power-on Reset (POR) of the device. Exceptions to this include the RTCC (if present), which remains operational through the wake-up, the DSGPRx registers and DSWDT.

Wake-up events that occur from the time Deep Sleep exits, until the time that the POR sequence completes, are ignored and are not captured in the DSWAKE register.

The sequence for exiting Deep Sleep mode is:

- 1. After a wake-up event, the device exits Deep Sleep and performs a POR. The DSEN bit is cleared automatically. Code execution resumes at the Reset vector.

- To determine if the device exited Deep Sleep, read the Deep Sleep bit, DPSLP (RCON<10>). This bit will be set if there was an exit from Deep Sleep mode. If the bit is set, clear it.

- 3. Determine the wake-up source by reading the DSWAKE register.

- Determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR bit (DSCON<1>).

- 5. If application context data has been saved, read it back from the DSGPR0 and DSGPR1 registers.

- 6. Clear the RELEASE bit (DSCON<0>).

# 9.2.4.4 Deep Sleep Wake-up Time

Since wake-up from Deep Sleep results in a POR, the wake-up time from Deep Sleep is the same as the device POR time. Also, because the internal regulator is turned off, the voltage on VCAP may drop depending on how long the device is asleep. If VCAP has dropped below 2V, then there will be additional wake-up time while the regulator charges VCAP.

Deep Sleep wake-up time is specified in **Section 29.0 "Electrical Characteristics"** as TDSWU. This specification indicates the worst case wake-up time, including the full POR Reset time (including TPOR and TRST), as well as the time to fully charge a 10  $\mu$ F capacitor on VCAP which has discharged to 0V. Wake-up may be significantly faster if VCAP has not discharged.

# 9.2.4.5 Saving Context Data with the DSGPR0/DSGPR1 Registers

As exiting Deep Sleep mode causes a POR, most Special Function Registers reset to their default POR values. In addition, because VDDCORE power is not supplied in Deep Sleep mode, information in data RAM may be lost when exiting this mode.

Applications which require critical data to be saved prior to Deep Sleep may use the Deep Sleep General Purpose registers, DSGPR0 and DSGPR1, or data EEPROM (if available). Unlike other SFRs, the contents of these registers are preserved while the device is in Deep Sleep mode. After exiting Deep Sleep, software can restore the data by reading the registers and clearing the RELEASE bit (DSCON<0>).

## 9.2.4.6 I/O Pins During Deep Sleep Mode

During Deep Sleep, the general purpose I/O pins retain their previous states and the Secondary Oscillator (SOSC) will remain running, if enabled. Pins that are configured as inputs (TRIS bit set) prior to entry into Deep Sleep remain high-impedance during Deep Sleep. Pins that are configured as outputs (TRIS bit clear) prior to entry into Deep Sleep remain as output pins during Deep Sleep. While in this mode, they continue to drive the output level determined by their corresponding LAT bit at the time of entry into Deep Sleep.

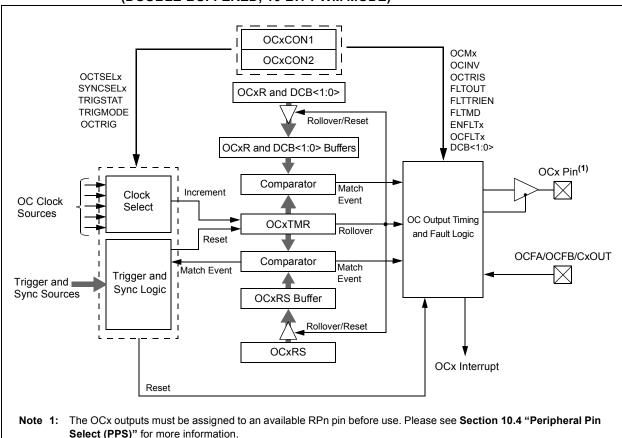

#### 14.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for edge-aligned PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- 2. Calculate the desired on-time and load it into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the synchronization source by writing 0x1F to SYNCSEL<4:0> (OCxCON2<4:0>) and '0' to OCTRIG (OCxCON2<7>).

- 5. Select a clock source by writing to the OCTSEL2<2:0> (OCxCON1<12:10>) bits.

- 6. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- 7. Select the desired PWM mode in the OCM<2:0> (OCxCON1<2:0>) bits.

- 8. If a timer is selected as a clock source, set the TMRy prescale value and enable the time base by setting the TON (TxCON<15>) bit.

- Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

## FIGURE 14-2: OUTPUT COMPARE BLOCK DIAGRAM (DOUBLE-BUFFERED, 16-BIT PWM MODE)

#### REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0                 | R/W-0  |

|--------|-----|--------|---------|---------|---------|-----------------------|--------|

| —      | —   | OCSIDL | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 <sup>(2)</sup> | ENFLT1 |

| bit 15 |     |        |         |         |         |                       | bit 8  |

| R/W-0  | R/W-0, HCS | R/W-0, HCS | R/W-0, HCS | R/W-0    | R/W-0               | R/W-0               | R/W-0               |

|--------|------------|------------|------------|----------|---------------------|---------------------|---------------------|

| ENFLT0 | OCFLT2     | OCFLT1     | OCFLT0     | TRIGMODE | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup> | OCM0 <sup>(1)</sup> |

| bit 7  |            |            |            |          |                     |                     | bit 0               |

| Legend:           | HCS = Hardware Clear | HCS = Hardware Clearable/Settable bit |                                         |  |  |  |  |  |

|-------------------|----------------------|---------------------------------------|-----------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit,                | U = Unimplemented bit, read as '0'      |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared                  | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |  |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13    | <b>OCSIDL:</b> Stop Output Compare x in Idle Mode Control bit<br>1 = Output compare x halts in CPU Idle mode<br>0 = Output compare x continues to operate in CPU Idle mode |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12-10 | OCTSEL<2:0>: Output Compare x Timer Select bits                                                                                                                            |

|           | 111 = System clock                                                                                                                                                         |

|           | 110 = Reserved                                                                                                                                                             |

|           | 101 = Reserved                                                                                                                                                             |

|           | 100 <b>= Timer1</b>                                                                                                                                                        |

|           | 011 = Timer5                                                                                                                                                               |

|           | 010 <b>= Timer4</b>                                                                                                                                                        |

|           | 001 = Timer3                                                                                                                                                               |

|           | 000 = Timer2                                                                                                                                                               |

# bit 9 ENFLT2: Comparator Fault Input Enable bit<sup>(2)</sup>

- 1 = Comparator Fault input is enabled

- 0 = Comparator Fault input is disabled

- bit 8 **ENFLT1:** OCFB Fault Input Enable bit

- 1 = OCFB Fault input is enabled

- 0 = OCFB Fault input is disabled

- bit 7 ENFLT0: OCFA Fault Input Enable bit

- 1 = OCFA Fault input is enabled

- 0 = OCFA Fault input is disabled

- bit 6 **OCFLT2:** PWM Comparator Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM comparator Fault condition has occurred (this is cleared in hardware only)

- 0 = PWM comparator Fault condition has not occurred (this bit is used only when OCM<2:0> = 111)

- bit 5 OCFLT1: PWM OCFB Fault Input Enable bit 1 = PWM OCFB Fault condition has occurred (this is cleared in hardware only)

- 0 = PWM OCFB Fault condition has not occurred (this bit is used only when OCM<2:0> = 111)

- bit 4 **OCFLT0:** PWM OCFA Fault Condition Status bit

- 1 = PWM OCFA Fault condition has occurred (this is cleared in hardware only)

- 0 = PWM OCFA Fault condition has not occurred (this bit is used only when OCM<2:0> = 111)

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is only cleared by software

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

- **2:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

| REGISTER             | 15-1: SPIx                                                                                                          | STAT: SPIx S                                                                                                                                                        | FATUS AND                                                                                                           | CONTROL R                                                                                                      | EGISTER                                                                                        |                                        |                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|

| R/W-0                | U-0                                                                                                                 | R/W-0                                                                                                                                                               | U-0                                                                                                                 | U-0                                                                                                            | R-0                                                                                            | R-0                                    | R-0             |

| SPIEN <sup>(1)</sup> |                                                                                                                     | SPISIDL                                                                                                                                                             | _                                                                                                                   | _                                                                                                              | SPIBEC2                                                                                        | SPIBEC1                                | SPIBEC0         |

| bit 15               |                                                                                                                     |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        | bit 8           |

| DA                   |                                                                                                                     |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                | DA                                     | DA              |

| R-0                  | R/C-0, HS                                                                                                           | R/W-0                                                                                                                                                               | R/W-0                                                                                                               | R/W-0                                                                                                          | R/W-0                                                                                          | R-0                                    | R-0             |

| SRMPT                | SPIROV                                                                                                              | SRXMPT                                                                                                                                                              | SISEL2                                                                                                              | SISEL1                                                                                                         | SISEL0                                                                                         | SPITBF                                 | SPIRBF<br>bit ( |

|                      |                                                                                                                     |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        | bit t           |

| Legend:              |                                                                                                                     | C = Clearable                                                                                                                                                       | bit                                                                                                                 | HS = Hardwa                                                                                                    | re Settable bit                                                                                |                                        |                 |

| R = Readab           | ole bit                                                                                                             | W = Writable                                                                                                                                                        | bit                                                                                                                 | U = Unimplen                                                                                                   | nented bit, read                                                                               | d as '0'                               |                 |

| -n = Value a         | at POR                                                                                                              | '1' = Bit is set                                                                                                                                                    |                                                                                                                     | '0' = Bit is cle                                                                                               | ared                                                                                           | x = Bit is unkr                        | iown            |

| bit 15               | <b>SPIEN:</b> SPIx<br>1 = Enables r<br>0 = Disables                                                                 | module and cor                                                                                                                                                      | figures SCKx,                                                                                                       | SDOx, SDIx a                                                                                                   | nd SSx as seria                                                                                | al port pins                           |                 |

| bit 14               | Unimplemen                                                                                                          | ted: Read as '                                                                                                                                                      | )'                                                                                                                  |                                                                                                                |                                                                                                |                                        |                 |

| bit 13               |                                                                                                                     | p in Idle Mode                                                                                                                                                      |                                                                                                                     |                                                                                                                |                                                                                                |                                        |                 |

|                      |                                                                                                                     | ue module oper<br>module operati                                                                                                                                    |                                                                                                                     |                                                                                                                | e mode                                                                                         |                                        |                 |

| bit 12-11            | Unimplemen                                                                                                          | ted: Read as '                                                                                                                                                      | )'                                                                                                                  |                                                                                                                |                                                                                                |                                        |                 |

| bit 10-8             | Master mode                                                                                                         | -                                                                                                                                                                   |                                                                                                                     | bits (valid in E                                                                                               | nhanced Buffer                                                                                 | mode)                                  |                 |

|                      | Slave mode:                                                                                                         | PI transfers pen<br>PI transfers unr                                                                                                                                | -                                                                                                                   |                                                                                                                |                                                                                                |                                        |                 |

| bit 7                |                                                                                                                     | Register (SPIx                                                                                                                                                      |                                                                                                                     | (valid in Enhar                                                                                                | nced Buffer mo                                                                                 | de)                                    |                 |

|                      | 1 = SPIx Shi                                                                                                        | ft register is em<br>ft register is not                                                                                                                             | pty and ready                                                                                                       |                                                                                                                |                                                                                                | ,                                      |                 |

| bit 6                | SPIROV: Red                                                                                                         | ceive Overflow                                                                                                                                                      | Flag bit                                                                                                            |                                                                                                                |                                                                                                |                                        |                 |

|                      | data in th                                                                                                          | rte/word is comp<br>le SPIxBUF reg<br>low has occurre                                                                                                               | ister.                                                                                                              | l and discarded                                                                                                | . The user softv                                                                               | vare has not rea                       | ad the previous |

| bit 5                |                                                                                                                     | ceive FIFO Em                                                                                                                                                       |                                                                                                                     | Enhanced But                                                                                                   | fer mode)                                                                                      |                                        |                 |

|                      |                                                                                                                     | FIFO is empty<br>FIFO is not em                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        |                 |

| bit 4-2              | SISEL<2:0>:                                                                                                         | SPIx Buffer Int                                                                                                                                                     | errupt Mode b                                                                                                       | its (valid in Enh                                                                                              | anced Buffer n                                                                                 | node)                                  |                 |

|                      | 110 = Internu<br>101 = Internu<br>100 = Internu<br>011 = Internu<br>010 = Internu<br>001 = Internu<br>000 = Internu | pt when SPIx to<br>pt when last bit<br>pt when the las<br>pt when one da<br>pt when SPIx ro<br>pt when SPIx ro<br>pt when data is<br>pt when the la<br>APT bit set) | is shifted into<br>t bit is shifted<br>ata is shifted in<br>eceive buffer is<br>eceive buffer is<br>available in re | SPIxSR; as a r<br>out of SPIxSR;<br>to the SPIxSR;<br>s full (SPIRBF I<br>s 3/4 or more fu<br>eccive buffer (S | result, the TX F<br>now the transr<br>as a result, the<br>bit is set)<br>III<br>RMPT bit is se | nit is complete<br>e TX FIFO has<br>t) |                 |

|                      | f SPIEN = 1, the<br><b>Peripheral Pin</b>                                                                           |                                                                                                                                                                     |                                                                                                                     |                                                                                                                | Pn pins before                                                                                 | use. See Sect                          | ion 10.4        |

# REGISTER 15-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

# REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (When operating as I <sup>2</sup> C master. Applicable during master receive.)                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                     |

| bit 4 | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                           |

| DIL 4 | (When operating as I <sup>2</sup> C master. Applicable during master receive.)                                                                                                   |

|       | 1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware clear at end of master Acknowledge sequence.                                     |

|       | 0 = Acknowledge sequence not in progress                                                                                                                                         |

| bit 3 | RCEN: Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                             |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receives sequence not in progress</li> </ul> |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                |

|       | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li> <li>0 = Stop condition not in progress</li> </ul>               |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enabled bit (when operating as I <sup>2</sup> C master)                                                                                    |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master<br>Repeated Start sequence                                                         |

|       | 0 = Repeated Start condition not in progress                                                                                                                                     |

| bit 0 | SEN: Start Condition Enabled bit (when operating as I <sup>2</sup> C master)                                                                                                     |

|       | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition not in progress</li> </ul>            |

NOTES:

# REGISTER 18-1: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, USB MODE (BD0STAT THROUGH BD63STAT)

| R/W-x                              | R/W-x                                                               | R/W-x                                      | R/W-x                             | R/W-x                                                   | R/W-x           | R/W-x    | R/W-x |

|------------------------------------|---------------------------------------------------------------------|--------------------------------------------|-----------------------------------|---------------------------------------------------------|-----------------|----------|-------|

| UOWN                               | DTS                                                                 | PID3                                       | PID2                              | PID1                                                    | PID0            | BC9      | BC8   |

| bit 15                             |                                                                     |                                            |                                   |                                                         |                 |          | bit 8 |

|                                    |                                                                     |                                            |                                   |                                                         |                 |          |       |

| R/W-x                              | R/W-x                                                               | R/W-x                                      | R/W-x                             | R/W-x                                                   | R/W-x           | R/W-x    | R/W-x |

| BC7                                | BC6                                                                 | BC5                                        | BC4                               | BC3                                                     | BC2             | BC1      | BC0   |

| bit 7                              |                                                                     |                                            |                                   |                                                         |                 |          | bit C |

| Legend:                            |                                                                     |                                            |                                   |                                                         |                 |          |       |

| R = Readab                         | le bit                                                              | W = Writable                               | bit                               | U = Unimplen                                            | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set |                                                                     |                                            |                                   | '0' = Bit is cleared x = Bit is unknown                 |                 |          |       |

| bit 14                             | the buffer<br><b>DTS:</b> Data To<br>1 = Data 1 pa<br>0 = Data 0 pa | ggle Packet bi<br>acket                    | t                                 |                                                         |                 |          |       |

| bit 13-10                          | <u>In Device mod</u><br>Represents th<br><u>In Host mode</u>        | <u>de:</u><br>ne PID of the re<br><u>:</u> | eceived token                     | the USB modu<br>during the last to<br>ansfer status inc | ransfer.        |          |       |

| bit 9-0                            | BC<9:0>: Byt<br>This represen<br>during a trans                     | te Count<br>its the number                 | of bytes to be<br>npletion, the t | transmitted or the oyte count is up                     | ne maximum n    |          |       |

#### 18.5.3 SEND A FULL-SPEED BULK DATA TRANSFER TO A TARGET DEVICE

- Follow the procedure described in Section 18.5.1 "Enable Host Mode and Discover a Connected Device" and Section 18.5.2 "Complete a Control Transaction to a Connected Device" to discover and configure a device.

- To enable transmit and receive transfers with handshaking enabled, write 1Dh to U1EP0. If the target device is a low-speed device, also set the LSPD bit (U1EP0<7>). If you want the hardware to automatically retry indefinitely if the target device asserts a NAK on the transfer, clear the Retry Disable bit, RETRYDIS (U1EP0<6>).

- 3. Set up the BD for the current (EVEN or ODD) Tx EP0 to transfer up to 64 bytes.

- 4. Set the USB device address of the target device in the address register (U1ADDR<6:0>).

- 5. Write an OUT token to the desired endpoint to U1TOK. This triggers the module's transmit state machines to begin transmitting the token and the data.

- 6. Wait for the Transfer Done Interrupt Flag, TRNIF. This indicates that the BD has been released back to the microprocessor, and the transfer has completed. If the retry disable bit is set, the handshake (ACK, NAK, STALL or ERROR (0Fh)) is returned in the BD PID field. If a STALL interrupt occurs, the pending packet must be dequeued and the error condition in the target device cleared. If a detach interrupt occurs (SE0 for more than 2.5 μs), then the target has detached (U1IR<0> is set).

- 7. Once the transfer done interrupt occurs (TRNIF is set), the BD can be examined and the next data packet queued by returning to step 2.

- Note: USB speed, transceiver and pull-ups should only be configured during the module setup phase. It is not recommended to change these settings while the module is enabled.

# 18.6 OTG Operation

#### 18.6.1 SESSION REQUEST PROTOCOL (SRP)

An OTG A-device may decide to power down the VBUS supply when it is not using the USB link through the Session Request Protocol (SRP). Software may do this by clearing VBUSON (U10TGCON<3>). When the VBUS supply is powered down, the A-device is said to have ended a USB session.

An OTG A-device or Embedded Host may re-power the VBUS supply at any time (initiate a new session). An OTG B-device may also request that the OTG A-device re-power the VBUS supply (initiate a new session). This is accomplished via Session Request Protocol (SRP).

Prior to requesting a new session, the B-device must first check that the previous session has definitely ended. To do this, the B-device must check for two conditions:

1. VBUS supply is below the Session Valid voltage, and

2. Both D+ and D- have been low for at least 2 ms.

The B-device will be notified of condition 1 by the SESENDIF (U1OTGIR<2>) interrupt. Software will have to manually check for condition 2.

| Note: | When the A-device powers down the VBUS        |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|

|       | supply, the B-device must disconnect its      |  |  |  |  |

|       | pull-up resistor from power. If the device is |  |  |  |  |

|       | self-powered, it can do this by clearing      |  |  |  |  |

|       | DPPULUP (U1OTGCON<7>) and                     |  |  |  |  |

|       | DMPULUP (U1OTGCON<6>).                        |  |  |  |  |

The B-device may aid in achieving condition 1 by discharging the VBUS supply through a resistor. Software may do this by setting VBUSDIS (U1OTGCON<0>).

After these initial conditions are met, the B-device may begin requesting the new session. The B-device begins by pulsing the D+ data line. Software should do this by setting DPPULUP (U10TGCON<7>). The data line should be held high for 5 to 10 ms.

The B-device then proceeds by pulsing the VBUS supply. Software should do this by setting PUVBUS (U1CNFG2<4>). When an A-device detects SRP signaling (either via the ATTACHIF (U1IR<6>) interrupt or via the SESVDIF (U1OTGIR<3>) interrupt), the A-device must restore the VBUS supply by either setting VBUSON (U1OTGCON<3>), or by setting the I/O port controlling the external power source.

The B-device should not monitor the state of the VBUS supply while performing VBUS supply pulsing. When the B-device does detect that the VBUS supply has been restored (via the SESVDIF (U10TGIR<3>) interrupt), the B-device must re-connect to the USB link by pulling up D+ or D- (via the DPPULUP or DMPULUP).

The A-device must complete the SRP by driving USB Reset signaling.

#### 18.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the *On-The-Go Supplement to the USB 2.0 Specification* for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in Suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as Host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF (U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as Host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power-down VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation, and drives Reset signaling.

# 18.6.3 EXTERNAL VBUS COMPARATORS

The external VBUS comparator option is enabled by setting the UVCMPDIS bit (U1CNFG2<1>). This disables the internal VBUS comparators, removing the need to attach VBUS to the microcontroller's VBUS pin.

The external comparator interface uses either the VCMPST1 and VCMPST2 pins, or the VBUSVLD, SESSVLD and SESSEND pins, based upon the setting of the UVCMPSEL bit (U1CNFG2<5>). These pins are digital inputs and should be set in the following patterns (see Table 18-3), based on the current level of the VBUS voltage.

## TABLE 18-3:EXTERNAL VBUS COMPARATOR STATES

| If UVCMPSEL = 0 |         |                                    |                                  |  |  |  |  |

|-----------------|---------|------------------------------------|----------------------------------|--|--|--|--|

| VCMPST1         | VCMPST2 | Bus Condition                      |                                  |  |  |  |  |

| 0               | 0       | VBUS < VB_SESS                     | VBUS < VB_SESS_END               |  |  |  |  |

| 1               | 0       | VB_SESS_END < \                    | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |  |

| 0               | 1       | VA_SESS_VLD < VBUS < VA_VBUS_VLD   |                                  |  |  |  |  |

| 1               | 1       | VBUS > VVBUS_VLD                   |                                  |  |  |  |  |

| If UVCMPSEL =   | 1       |                                    |                                  |  |  |  |  |

| VBUSVLD         | SESSVLD | SESSEND                            | Bus Condition                    |  |  |  |  |

| 0               | 0       | 1                                  | VBUS < VB_SESS_END               |  |  |  |  |

| 0               | 0       | 0                                  | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |  |

| 0               | 1       | 0 VA_SESS_VLD < VBUS < VA_VBUS_VLD |                                  |  |  |  |  |

| 1               | 1       | 0                                  | VBUS > VVBUS_VLD                 |  |  |  |  |

#### REGISTER 18-11: U1SOF: USB OTG START-OF-TOKEN THRESHOLD REGISTER (HOST MODE ONLY)

| U-0                                | U-0   | U-0   | U-0   | U-0                                     | U-0   | U-0   | U-0   |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|

| —                                  | —     | —     | —     | —                                       | —     | —     | —     |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |

|                                    |       |       |       |                                         |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

| CNT7                               | CNT6  | CNT5  | CNT4  | CNT3                                    | CNT2  | CNT1  | CNT0  |

| bit 7                              | •     |       |       |                                         | •     |       | bit 0 |

|                                    |       |       |       |                                         |       |       |       |

| Legend:                            |       |       |       |                                         |       |       |       |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **CNT<7:0>:** Start-of-Frame Size bits;

Value represents 10 + (packet size of n bytes). For example:

0100 1010 = 64-byte packet

0010 1010 = 32-byte packet

0001 0010 = 8-byte packet

# REGISTER 18-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| R/W-0 | R/W-0                 | U-0 | R/W-0   | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----------------------|-----|---------|-----|-----|-------|-------|

| UTEYE | UOEMON <sup>(1)</sup> | —   | USBSIDL | —   | —   | PPB1  | PPB0  |

| bit 7 | ·                     |     |         |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------|

| bit 7    | UTEYE: USB Eye Pattern Test Enable bit                                                                    |

|          | 1 = Eye pattern test is enabled                                                                           |

|          | 0 = Eye pattern test is disabled                                                                          |

| bit 6    | UOEMON: USB OE Monitor Enable bit <sup>(1)</sup>                                                          |

|          | 1 = $\overline{OE}$ signal is active; it indicates the intervals during which the D+/D- lines are driving |

|          | 0 = OE signal is inactive                                                                                 |

| bit 5    | Unimplemented: Read as '0'                                                                                |

| bit 4    | USBSIDL: USB OTG Stop in Idle Mode bit                                                                    |

|          | <ol> <li>Discontinue module operation when device enters Idle mode</li> </ol>                             |

|          | <ul> <li>0 = Continue module operation in Idle mode</li> </ul>                                            |

| bit 3-2  | Unimplemented: Read as '0'                                                                                |

**Note 1:** This bit is only active when the UTRDIS bit (U1CNFG2<0>) is set.

| R/W-0         | U-0                                                                                            | R/W-0                               | R/W-0                                | R/W-0                  | R/W-0          | R/W-0           | R/W-0  |  |  |

|---------------|------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|------------------------|----------------|-----------------|--------|--|--|

| PMPEN         |                                                                                                | PSIDL                               | ADRMUX1 <sup>(1)</sup>               | ADRMUX0 <sup>(1)</sup> | PTBEEN         | PTWREN          | PTRDEN |  |  |

| bit 15        |                                                                                                |                                     |                                      |                        |                |                 | bit 8  |  |  |

|               |                                                                                                |                                     |                                      |                        |                |                 |        |  |  |

| R/W-0         | R/W-0                                                                                          | R/W-0 <sup>(2)</sup>                | U-0                                  | R/W-0 <sup>(2)</sup>   | R/W-0          | R/W-0           | R/W-0  |  |  |

| CSF1          | CSF0                                                                                           | ALP                                 |                                      | CS1P                   | BEP            | WRSP            | RDSP   |  |  |

| bit 7         |                                                                                                |                                     |                                      |                        |                |                 | bit (  |  |  |

| Legend:       |                                                                                                |                                     |                                      |                        |                |                 |        |  |  |

| R = Readab    | le bit                                                                                         | W = Writable                        | bit                                  | U = Unimplem           | ented bit, rea | d as '0'        |        |  |  |

| -n = Value at |                                                                                                | '1' = Bit is se                     |                                      | '0' = Bit is clea      | -              | x = Bit is unkr | nown   |  |  |

|               |                                                                                                |                                     |                                      | 0 21110 0.00           |                |                 |        |  |  |

| bit 15        | PMPEN: Para                                                                                    | allel Master Po                     | ort Enable bit                       |                        |                |                 |        |  |  |

|               | 1 = PMP is e                                                                                   | enabled                             |                                      |                        |                |                 |        |  |  |

|               | 0 = PMP is c                                                                                   | lisabled, no off                    | -chip access pe                      | erformed               |                |                 |        |  |  |

| bit 14        | Unimplemen                                                                                     | ted: Read as                        | '0'                                  |                        |                |                 |        |  |  |

| bit 13        | PSIDL: Stop                                                                                    | in Idle Mode b                      | it                                   |                        |                |                 |        |  |  |

|               |                                                                                                |                                     | eration when de<br>ation in Idle mod |                        | e mode         |                 |        |  |  |

| bit 12-11     |                                                                                                | •                                   |                                      |                        | 1)             |                 |        |  |  |

|               | ADRMUX<1:0>: Address/Data Multiplexing Selection bits <sup>(1)</sup><br>11 = Reserved          |                                     |                                      |                        |                |                 |        |  |  |

|               | 10 = All 16 bits of address are multiplexed on PMD<7:0> pins                                   |                                     |                                      |                        |                |                 |        |  |  |

|               | 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 3 bits are multiplexed on |                                     |                                      |                        |                |                 |        |  |  |