Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

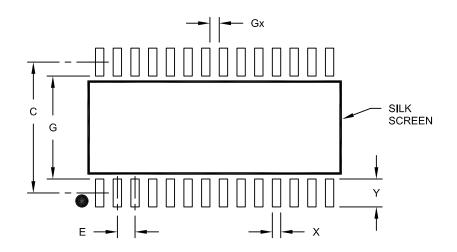

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb002-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Р                             | Pin Number                   |    |     |                  |                                                       |  |  |

|----------|-------------------------------|------------------------------|----|-----|------------------|-------------------------------------------------------|--|--|

| Function | 28-Pin<br>SPDIP/<br>SOIC/SSOP | 28-Pin 44-Pin<br>QFN QFN/TQF |    | I/O | Input<br>Buffer  | Description                                           |  |  |

| RP0      | 4                             | 1                            | 21 | I/O | ST               | Remappable Peripheral (input or output).              |  |  |

| RP1      | 5                             | 2                            | 22 | I/O | ST               |                                                       |  |  |

| RP2      | 6                             | 3                            | 23 | I/O | ST               |                                                       |  |  |

| RP3      | 7                             | 4                            | 24 | I/O | ST               |                                                       |  |  |

| RP4      | 11                            | 8                            | 33 | I/O | ST               |                                                       |  |  |

| RP5      | 2                             | 27                           | 19 | I/O | ST               |                                                       |  |  |

| RP6      | 3                             | 28                           | 20 | I/O | ST               |                                                       |  |  |

| RP7      | 16                            | 13                           | 43 | I/O | ST               |                                                       |  |  |

| RP8      | 17                            | 14                           | 44 | I/O | ST               |                                                       |  |  |

| RP9      | 18                            | 15                           | 1  | I/O | ST               |                                                       |  |  |

| RP10     | 21                            | 18                           | 8  | I/O | ST               |                                                       |  |  |

| RP11     | 22                            | 19                           | 9  | I/O | ST               |                                                       |  |  |

| RP13     | 24                            | 21                           | 11 | I/O | ST               |                                                       |  |  |

| RP14     | 25                            | 22                           | 14 | I/O | ST               |                                                       |  |  |

| RP15     | 26                            | 23                           | 15 | I/O | ST               |                                                       |  |  |

| RP16     | —                             | _                            | 25 | I/O | ST               |                                                       |  |  |

| RP17     | —                             | _                            | 26 | I/O | ST               |                                                       |  |  |

| RP18     | —                             | _                            | 27 | I/O | ST               |                                                       |  |  |

| RP19     | —                             | _                            | 36 | I/O | ST               |                                                       |  |  |

| RP20     | —                             | _                            | 37 | I/O | ST               |                                                       |  |  |

| RP21     | —                             | _                            | 38 | I/O | ST               |                                                       |  |  |

| RP22     | —                             | _                            | 2  | I/O | ST               | -                                                     |  |  |

| RP23     | —                             | _                            | 3  | I/O | ST               | -                                                     |  |  |

| RP24     | —                             | _                            | 4  | I/O | ST               | -                                                     |  |  |

| RP25     | —                             | —                            | 5  | I/O | ST               |                                                       |  |  |

| RTCC     | 7                             | 4                            | 24 | 0   | —                | Real-Time Clock Alarm/Seconds Pulse Output.           |  |  |

| SESSEND  | 24                            | 21                           | 11 | I   | ST               | USB VBUS Session End Status Input.                    |  |  |

| SESSVLD  | 3                             | 28                           | 20 | I   | ST               | USB VBUS Session Valid Status Input.                  |  |  |

| SCL1     | 17                            | 14                           | 44 | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output.           |  |  |

| SCL2     | 7                             | 4                            | 24 | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output.           |  |  |

| SDA1     | 18                            | 15                           | 1  | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                               |  |  |

| SDA2     | 6                             | 3                            | 23 | I/O | l <sup>2</sup> C | I2C2 Data Input/Output.                               |  |  |

| SOSCI    | 11                            | 8                            | 33 | I   | ANA              | Secondary Oscillator/Timer1 Clock Input.              |  |  |

| SOSCO    | 12                            | 9                            | 34 | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.             |  |  |

| T1CK     | 12                            | 9                            | 34 | I   | ST               | Timer1 Clock Input.                                   |  |  |

| ТСК      | 17                            | 14                           | 13 | I   | ST               | JTAG Test Clock Input.                                |  |  |

| TDI      | 16                            | 13                           | 35 | I   | ST               | JTAG Test Data Input.                                 |  |  |

| TDO      | 18                            | 15                           | 32 | 0   | —                | JTAG Test Data Output.                                |  |  |

| TMS      | 14                            | 11                           | 12 | I   | ST               | JTAG Test Mode Select Input.                          |  |  |

| USBID    | 14                            | 11                           | 41 | I   | ST               | USB OTG ID (OTG mode only).                           |  |  |

| USBOEN   | 17                            | 14                           | 44 | 0   | —                | USB Output Enable Control (for external transceiver). |  |  |

TABLE 1-2. PIC24F.I64GB004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer Legend:

ANA = Analog level input/output

$I^2C^{TM} = I^2C/SMBus$  input buffer

ST = Schmitt Trigger input buffer

# TABLE 4-8: OUTPUT COMPARE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8       | Bit 7        | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|--------|----------|---------|---------|---------|--------|-------------|--------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1   | 0190 | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2       | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2   | 0192 | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS     | 0194 |        |        |          |         |         |         | 0      | utput Compa | are 1 Second | ary Register |        |          |          |          |          |          | 0000          |

| OC1R      | 0196 |        |        |          |         |         |         |        | Output C    | Compare 1 R  | egister      |        |          |          |          |          |          | 0000          |

| OC1TMR    | 0198 |        |        |          |         |         |         |        | Timer       | Value 1 Reg  | ister        |        |          |          |          |          |          | xxxx          |

| OC2CON1   | 019A | —      | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2       | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2   | 019C | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS     | 019E |        |        |          |         |         |         | 0      | utput Compa | are 2 Second | ary Register |        |          |          |          |          |          | 0000          |

| OC2R      | 01A0 |        |        |          |         |         |         |        | Output C    | Compare 2 R  | egister      |        |          |          |          |          |          | 0000          |

| OC2TMR    | 01A2 |        |        |          |         |         |         |        | Timer       | Value 2 Reg  | ister        |        |          |          |          |          |          | xxxx          |

| OC3CON1   | 01A4 | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2       | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2   | 01A6 | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS     | 01A8 |        |        |          |         |         |         | 0      | utput Compa | are 3 Second | ary Register |        |          |          |          |          |          | 0000          |

| OC3R      | 01AA |        |        |          |         |         |         |        | Output C    | Compare 3 R  | egister      |        |          |          |          |          |          | 0000          |

| OC3TMR    | 01AC |        |        |          |         |         |         |        | Timer       | Value 3 Reg  | ister        |        |          |          |          |          |          | xxxx          |

| OC4CON1   | 01AE | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2       | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2   | 01B0 | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS     | 01B2 |        |        |          |         |         |         | 0      | utput Compa | are 4 Second | ary Register |        |          |          |          |          |          | 0000          |

| OC4R      | 01B4 |        |        |          |         |         |         |        | Output C    | Compare 4 R  | egister      |        |          |          |          |          |          | 0000          |

| OC4TMR    | 01B6 |        |        |          |         |         |         |        | Timer       | Value 4 Reg  | ister        |        |          |          |          |          |          | xxxx          |

| OC5CON1   | 01B8 | —      | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2       | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2   | 01BA | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS     | 01BC |        |        |          |         |         |         | 0      | utput Compa | are 5 Second | ary Register |        |          |          |          |          |          | 0000          |

| OC5R      | 01BE |        |        |          |         |         |         |        | Output C    | Compare 5 R  | egister      |        |          |          |          |          |          | 0000          |

| OC5TMR    | 01C0 |        |        |          |         |         |         |        | Timer       | Value 5 Reg  | ister        |        |          |          |          |          |          | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

PIC24FJ64GB004 FAMILY

# EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

unsigned int offset;

unsigned int i;

unsigned long progAddr = 0xXXXXX; // Address of row to write

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW]; // Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4001;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = progAddr>>16;

// Initialize PM Page Boundary SFR

offset = progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ;                                       |

| NOP  |             | ;                                       |

| BTSC | NVMCON, #15 | ; and wait for it to be                 |

| BRA  | \$-2        | ; completed                             |

|      |             |                                         |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB | C30                                                                                |

|--------------------------|------------------------------------------------------------------------------------|

| asm("DISI #5");          | <pre>// Block all interrupts with priority &lt; 7 // for next 5 instructions</pre> |

| builtin_write_NVM();     | // Perform unlock sequence and set WR                                              |

### REGISTER 7-12: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| U-0       U-0       R/W-0       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0         | R/W-0         | R/W-0                 | R/W-0                 | R/W-0          | R/W-0           | R/W-0    | U-0     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------------------|-----------------------|----------------|-----------------|----------|---------|

| U-0       U-0       RW-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U2TXIE        | U2RXIE        | INT2IE <sup>(1)</sup> | T5IE                  | T4IE           | OC4IE           | OC3IE    | —       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 15        |               |                       |                       |                |                 |          | bit 8   |

| u         u         INTTIE <sup>(1)</sup> CNE         CME         MI2CIE         SI2CIE           bit7         intrile <sup>(1)</sup> CNE         CME         MI2CIE         SI2CIE           Legend:         R = Readable bit         W = Writable bit         U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |               |                       |                       |                |                 |          |         |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' .n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 U2TXIE: UART2 Transmitter Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled                                                                                                        | U-0           | U-0           | U-0                   |                       |                | R/W-0           | R/W-0    | R/W-0   |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —             | —             | —                     | INT1IE <sup>(1)</sup> | CNIE           | CMIE            | MI2C1IE  | SI2C1IE |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       U2TXIE: UART2 Transmitter Interrupt Enable bit       1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is on tenabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 13       INT2IE: External Interrupt 2 Enable bit       1 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt reques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 7         |               |                       |                       |                |                 |          | bit 0   |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       U2TXIE: UART2 Transmitter Interrupt Enable bit       1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is on tenabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 14       U2RXIE: UART2 Receiver Interrupt Enable bit       1 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 10       OC3E: Output Compare Channel 3 Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l egend:      |               |                       |                       |                |                 |          |         |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       U2TXIE: UART2 Transmitter Interrupt Enable bit       1       Interrupt request is enabled         0 = Interrupt request is on to enabled       0 = Interrupt request is enabled       0         bit 14       U2RXIE: UART2 Receiver Interrupt Enable bit       1         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 13       INTZIE: External Interrupt 2 Enable bit <sup>(1)</sup> 1         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 12       TSIE: Timer5 Interrupt Enable bit       1         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 11       T4IE: Timer4 Interrupt Enable bit       1         1 = Interrupt request is enabled       0 = Interrupt request is enabled       0         bit 3       OC4IE: Output Compare Channel 4 Interrupt Enable bit       1         1 = Interrupt request is enabled       0 = Interrupt request is enabled       0         bit 4       INTTHE: External Interrupt 1 Enable bit <sup>(1)</sup> 1       Interrupt request is enabled         bit 4       Interrupt request is enabled       0 = Interrupt request is enabled       0         bit 4       INTHE: Exterunal Interrup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -             | ole bit       | W = Writable          | bit                   | U = Unimpler   | mented bit, rea | d as '0' |         |

| bit 15 UZTXIE: UART2 Transmitter Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>0 = Interrupt request is not enabled<br>bit 14 UZRXIE: UART2 Receiver Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>0 = Interrupt request is not enabled<br>bit 13 INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup><br>1 = Interrupt request is not enabled<br>bit 12 T5IE: Timer5 Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 12 T5IE: Timer5 Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 11 T4IE: Timer4 Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 11 T4IE: Timer4 Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 10 OC4IE: Output Compare Channel 4 Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 9 OC3IE: Output Compare Channel 3 Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 8-5 Unimplemented: Read as '0'<br>bit 4 INT1IE: External Interrupt 1 Enable bit<br>1 = Interrupt request is not enabled<br>bit 3 CNIE: Input Change Notification Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 3 CNIE: Input Change Notification Interrupt Enable bit<br>1 = Interrupt request is enabled<br>bit 2 CMIE: Comparator Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 2 CMIE: Comparator Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 1 = Interrupt request is not enabled<br>bit 2 CMIE: Comparator Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 1 MI2CIE: Master 12C1 Event Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 1 MI2CIE: Master 12C1 Event Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 1 SICIE: Save 12C1 Event Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 0 SI2CIE: Naver 12C1 Event Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 0 II Interrupt request is not enabled<br>bit 0 SI2CIE: Naver 12C1 Event Interrupt Enable bit<br>1 = Interrupt request is not enabled<br>bit 0 SI2CIE: Naver 12C1 Event Interrupt Enable bit<br>1 = Interrupt request is |               |               |                       |                       | -              |                 |          | iown    |

| 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 14       U2RXIE: UART2 Receiver Interrupt Enable bit         1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 13       INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 10       OC3IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INTIE: External Interrupt Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         bit 3       CNIE: C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |               |                       |                       |                |                 |          |         |

| 0 = Interrupt request is not enabled         bit 14       U2RXIE: UAR12 Receiver Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 13       INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 12       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 11       T4IE: Timer5 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 11       T4IE: Timer4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt I Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 15        | U2TXIE: UA    | RT2 Transmitter       | Interrupt Enal        | ble bit        |                 |          |         |

| bit 14       U2RXIE: UART2 Receiver Interrupt Enable bit         1 = Interrupt request is enabled         bit 13       INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         0 = Interrupt request is not enabled         0 = Interrupt request is enabled         0 = Interrupt request is not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | •             | •                     |                       |                |                 |          |         |

| 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 13       INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 12       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 11       T4IE: Timer4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 4       INT1IE: External Interrupt Terupt Enable bit         1 = I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | -             |                       |                       |                |                 |          |         |

| 0 = Interrupt request is not enabled         bit 13       INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled         bit 12       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 11       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 11       TAIE: Timer4 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 11       TAIE: Timer4 Interrupt Enable bit         1 = Interrupt request is not enabled         0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 14        |               |                       | •                     | e bit          |                 |          |         |

| bit 13       INT2IE: External Interrupt 2 Enable bit         1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 12       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1E: External Interrupt 1 Enable bit(1)         1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         bit 4       INT1E: External Interrupt Enable bit         1 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |               |                       |                       |                |                 |          |         |

| 1 = Interrupt request is on tenabled         bit 12       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is not enabled         0 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 11       T4IE: Timer4 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         bit 4       INT1IE: External Interrupt Enable bit         1 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         bit 4       Interrupt request is not enabled         bit 5       CMIE: Comparator Interrupt Enable bit <t< td=""><td>hit 13</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hit 13        |               |                       |                       |                |                 |          |         |

| 0 = Interrupt request is not enabled         bit 12       TSIE: Timer5 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 11       T4IE: Timer4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 4       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |               |                       |                       |                |                 |          |         |

| 1 = Interrupt request is not enabled         bit 11 <b>T4IE</b> : Timer4 Interrupt Enable bit         1 = Interrupt request is enabled         bit 10 <b>OC4IE</b> : Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled         bit 10 <b>OC3IE</b> : Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled         bit 9 <b>OC3IE</b> : Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is not enabled         bit 8-5 <b>Unimplemented</b> : Read as '0'         bit 4 <b>INT1IE</b> : External Interrupt 1 Enable bit         1 = Interrupt request is not enabled         o = Interrupt request is not enabled         bit 3 <b>CNIE</b> : Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         o = Interrupt request is not enabled         bit 3 <b>CNIE</b> : Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         o = Interrupt request is not enabled         bit 2 <b>CMIE</b> : Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       o = Interrupt request is not enabled         bit 1 <b>INTECTIE</b> : Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       o = Interrupt request is not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | •             | •                     |                       |                |                 |          |         |

| 0 = Interrupt request is not enabled         bit 11 <b>T4IE:</b> Timer4 Interrupt Enable bit         1 = Interrupt request is enabled       0         0 = Interrupt request is on the enabled       0         bit 10 <b>OC4IE:</b> Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled       0         0 = Interrupt request is not enabled       0         bit 9 <b>OC3IE:</b> Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 8-5 <b>Unimplemented:</b> Read as '0'         bit 4 <b>INT1IE:</b> External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       0         bit 3 <b>CNIE:</b> Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 2 <b>CMIE:</b> Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 1 <b>INT2C1IE:</b> Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 1 <b>MIZC1IE:</b> Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 1 <b>MIZC1IE:</b> Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 12        | T5IE: Timer5  | i Interrupt Enabl     | e bit                 |                |                 |          |         |

| bit 11 <b>T4IE:</b> Timer4 Interrupt Enable bit         1 = Interrupt request is not enabled         0 = Interrupt request is not enabled         bit 10 <b>OC4IE:</b> Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 9 <b>OC3IE:</b> Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 8-5 <b>Unimplemented:</b> Read as '0'         bit 4 <b>INT1IE:</b> External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled         0 = Interrupt request is not enabled         bit 3 <b>CNIE:</b> Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 4 <b>INT1IE:</b> External Interrupt Enable bit         1 = Interrupt request is enabled       0         0 = Interrupt request is not enabled       0         bit 3 <b>CNIE:</b> Input Change Notification Interrupt Enable bit         1 = Interrupt request is enabled       0         0 = Interrupt request is not enabled       0         bit 2 <b>CMIE:</b> Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       0         bit 1 <b>MI</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | •             | •                     |                       |                |                 |          |         |

| 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is not enabled       0 = Interrupt request is enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 1       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | -             |                       |                       |                |                 |          |         |

| 0 = Interrupt request is not enabled         bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 2       CMIE: Comparator Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 1       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 11        |               | •                     |                       |                |                 |          |         |

| bit 10       OC4IE: Output Compare Channel 4 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         0 = Interrupt request is ont enabled       0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 2       CMIE: Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 1       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | •             | •                     |                       |                |                 |          |         |

| 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INTTIE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled         bit 4       Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 4       Interrupt request is not enabled         bit 5       CMIE: Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 1       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hit 10        | -             |                       |                       | int Enable bit |                 |          |         |

| bit 9       OC3IE: Output Compare Channel 3 Interrupt Enable bit         1 = Interrupt request is enabled       1 = Interrupt request is enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 2       CMIE: Comparator Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 1       I = Interrupt request is not enabled         bit 2       CMIE: Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 1       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       I = Interrupt request is not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |               |                       |                       |                |                 |          |         |

| 1 = Interrupt request is enabled         0 = Interrupt request is not enabled         bit 8-5       Unimplemented: Read as '0'         bit 4       INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup> 1 = Interrupt request is enabled       0 = Interrupt request is not enabled         bit 3       CNIE: Input Change Notification Interrupt Enable bit         1 = Interrupt request is enabled       0 = Interrupt request is enabled         bit 2       CMIE: Comparator Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 1       MI2C1IE: Master I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled         bit 0       SI2C1IE: Slave I2C1 Event Interrupt Enable bit         1 = Interrupt request is not enabled       0 = Interrupt request is not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               | •             | •                     |                       |                |                 |          |         |