#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb002-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

## 2.1 Basic Connection Requirements

Getting started with the PIC24FJ64GB004 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG/DISVREG and VCAP/VDDCORE pins (PIC24FJ devices only) (see Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

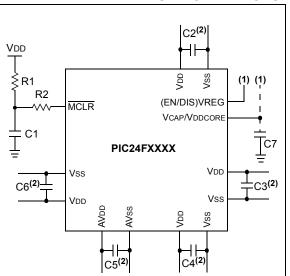

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},$  6.3V or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)" for explanation of ENVREG/DISVREG pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSs and AVDD/AVSs pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

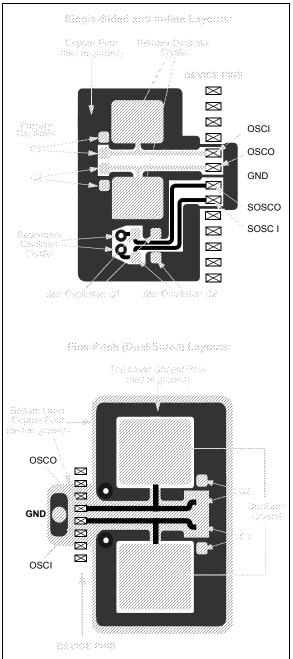

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## TABLE 4-6: TIMER REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|------|--------|------------------------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|--------|--------|-------|-------|-------|-------|

| TMR1      | 0100 |        |                        |        |        |        |        |              | Timer1 F     | Register      |              |        |        |       |       |       |       |

| PR1       | 0102 |        |                        |        |        |        |        | -            | Timer1 Peri  | od Register   |              |        |        |       |       |       |       |

| T1CON     | 0104 | TON    |                        | TSIDL  | —      |        | _      | —            |              |               | TGATE        | TCKPS1 | TCKPS0 |       | TSYNC | TCS   | -     |

| TMR2      | 0106 |        |                        |        |        |        |        |              | Timer2 F     | Register      |              |        |        |       |       |       |       |

| TMR3HLD   | 0108 |        |                        |        |        |        | Timer  | 3 Holding R  | egister (for | 32-bit time   | operations   | only)  |        |       |       |       |       |

| TMR3      | 010A |        | Timer3 Register        |        |        |        |        |              |              |               |              |        |        |       |       |       |       |

| PR2       | 010C |        | Timer2 Period Register |        |        |        |        |              |              |               |              |        |        |       |       |       |       |

| PR3       | 010E |        |                        |        |        |        |        | -            | Timer3 Peri  | od Register   |              |        |        |       |       |       |       |

| T2CON     | 0110 | TON    |                        | TSIDL  | —      |        | _      | —            |              |               | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     |

| T3CON     | 0112 | TON    |                        | TSIDL  | —      |        | _      | —            |              |               | TGATE        | TCKPS1 | TCKPS0 |       | —     | TCS   | _     |

| TMR4      | 0114 |        |                        |        |        |        |        |              | Timer4 F     | Register      |              |        |        |       |       |       |       |

| TMR5HLD   | 0116 |        |                        |        |        |        | Tin    | ner5 Holding | g Register ( | for 32-bit op | perations or | nly)   |        |       |       |       |       |

| TMR5      | 0118 |        |                        |        |        |        |        |              | Timer5 F     | Register      |              |        |        |       |       |       |       |

| PR4       | 011A |        |                        |        |        |        |        | -            | Timer4 Peri  | od Register   |              |        |        |       |       |       |       |

| PR5       | 011C |        |                        |        |        |        |        | -            | Timer5 Peri  | od Register   |              |        |        |       |       |       |       |

| T4CON     | 011E | TON    |                        | TSIDL  | —      |        | _      | —            |              |               | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | —     |

| T5CON     | 0120 | TON    |                        | TSIDL  | —      |        | _      | —            |              |               | TGATE        | TCKPS1 | TCKPS0 |       | —     | TCS   | —     |

PIC24FJ64GB004 FAMILY

All

Resets

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0, HS        | R/W-0, HS                                                                                                                                                                                   | U-0                                                    | U-0                                                       | U-0                  | R/CO-0, HS                  | R/W-0, HS        | R/W-0         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|----------------------|-----------------------------|------------------|---------------|

| TRAPR            | IOPUWR                                                                                                                                                                                      | _                                                      |                                                           | —                    | DPSLP                       | СМ               | PMSLP         |

| bit 15           |                                                                                                                                                                                             |                                                        |                                                           |                      |                             |                  | bita          |

| R/W-0, HS        | R/W-0, HS                                                                                                                                                                                   | R/W-0                                                  | R/W-0, HS                                                 | R/W-0, HS            | R/W-0, HS                   | R/W-1, HS        | R/W-1, HS     |

| EXTR             | SWR                                                                                                                                                                                         | SWDTEN <sup>(2)</sup>                                  | WDTO                                                      | SLEEP                | IDLE                        | BOR              | POR           |

| bit 7            |                                                                                                                                                                                             |                                                        |                                                           |                      |                             |                  | bit           |

| Legend:          |                                                                                                                                                                                             | CO = Clearab                                           | le Only bit                                               | HS = Hardwa          | re Settable bit             |                  |               |

| R = Readable     | e bit                                                                                                                                                                                       | W = Writable                                           | -                                                         |                      | nented bit, read            | as '0'           |               |

| -n = Value at    |                                                                                                                                                                                             | '1' = Bit is set                                       |                                                           | '0' = Bit is clea    |                             | x = Bit is unkn  | own           |

| bit 15<br>bit 14 | 1 = A Trap Co<br>0 = A Trap Co                                                                                                                                                              | Reset Flag bit<br>onflict Reset ha<br>onflict Reset ha | s occurred<br>s not occurred                              | Access Report        | Elog bit                    |                  |               |

| DIL 14           | 1 = An illegal<br>Pointer ca                                                                                                                                                                | opcode detect<br>aused a Reset                         | Uninitialized W<br>ion, an illegal ad<br>nitialized W Res | ddress mode o        | r uninitialized W           | / register used  | as an Addres  |

| bit 13-11        | •                                                                                                                                                                                           | ted: Read as '                                         |                                                           |                      |                             |                  |               |

| bit 10           | •                                                                                                                                                                                           | Sleep Mode F                                           |                                                           |                      |                             |                  |               |

|                  |                                                                                                                                                                                             | ep has occurre<br>ep has not occu                      |                                                           |                      |                             |                  |               |

| bit 9            | 1 = A Configu                                                                                                                                                                               | ration Word Mi                                         | match Reset Fl<br>smatch Reset I<br>smatch Reset I        | has occurred         | ed                          |                  |               |

| bit 8            | 1 = Program                                                                                                                                                                                 | memory bias v                                          | Power During Sl<br>oltage remains<br>oltage is powered    | powered durin        | g Sleep<br>Sleep and the vo | oltage regulator | enters Standb |

| bit 7            | 1 = A Master                                                                                                                                                                                |                                                        | R) Pin bit<br>et has occurre<br>et has not occu           |                      |                             |                  |               |

| bit 6            | <b>SWR:</b> Softwar<br>1 = A RESET i                                                                                                                                                        | re Reset (Instruinstruction has                        | uction) Flag bit<br>been executed<br>not been execu       |                      |                             |                  |               |

| bit 5            | <b>SWDTEN:</b> So<br>1 = WDT is er<br>0 = WDT is di                                                                                                                                         | nabled                                                 | Disable of WD1                                            | F bit <sup>(2)</sup> |                             |                  |               |

| bit 4            | 1 = WDT time                                                                                                                                                                                | ndog Timer Tim<br>-out has occur<br>-out has not oo    | red                                                       |                      |                             |                  |               |

| bit 3            | 1 = Device ha                                                                                                                                                                               | e From Sleep F<br>s been in Slee<br>s not been in S    | p mode                                                    |                      |                             |                  |               |

| bit 2            | <ul> <li>0 = Device has not been in Sleep mode</li> <li>IDLE: Wake-up From Idle Flag bit</li> <li>1 = Device has been in Idle mode</li> <li>0 = Device has not been in Idle mode</li> </ul> |                                                        |                                                           |                      |                             |                  |               |

#### cause a device Reset. 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Reset Type         | Clock Source | SYSRST Delay        | System Clock<br>Delay | Notes         |

|--------------------|--------------|---------------------|-----------------------|---------------|

| POR <sup>(6)</sup> | EC           | TPOR + TRST + TPWRT | _                     | 1, 2, 3       |

|                    | FRC, FRCDIV  | TPOR + TRST + TPWRT | TFRC                  | 1, 2, 3, 4    |

|                    | LPRC         | TPOR + TRST + TPWRT | TLPRC                 | 1, 2, 3, 4    |

|                    | ECPLL        | TPOR + TRST + TPWRT | Тьоск                 | 1, 2, 3, 5    |

|                    | FRCPLL       | TPOR + TRST + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4, 5 |

|                    | XT, HS, SOSC | TPOR+ TRST + TPWRT  | Tost                  | 1, 2, 3, 6    |

|                    | XTPLL, HSPLL | TPOR + TRST + TPWRT | Tost + Tlock          | 1, 2, 3, 5, 6 |

| BOR                | EC           | TRST + TPWRT        | —                     | 2, 3          |

|                    | FRC, FRCDIV  | TRST + TPWRT        | TFRC                  | 2, 3, 4       |

|                    | LPRC         | TRST + TPWRT        | TLPRC                 | 2, 3, 4       |

|                    | ECPLL        | TRST + TPWRT        | TLOCK                 | 2, 3, 5       |

|                    | FRCPLL       | TRST + TPWRT        | TFRC + TLOCK          | 2, 3, 4, 5    |

|                    | XT, HS, SOSC | TRST + TPWRT        | Tost                  | 2, 3, 6       |

|                    | XTPLL, HSPLL | TRST + TPWRT        | TFRC + TLOCK          | 2, 3, 4, 5    |

| All Others         | Any Clock    | Trst                | —                     | 2             |

**Note 1:** TPOR = Power-on Reset delay.

- **2:** TRST = Internal State Reset time.

- 3: TPWRT = 64 ms nominal if regulator is disabled (DISVREG tied to VDD).

- **4:** TFRC and TLPRC = RC Oscillator start-up times.

- **5:** TLOCK = PLL lock time.

- **6:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- 7: If Two-Speed Start-up is enabled, regardless of the primary oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 29.0 "Electrical Characteristics".

## 7.3 Interrupt Control and Status Registers

The PIC24FJ64GB004 family of devices implements the following registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS5

- IEC0 through IEC5

- IPC0 through IPC21 (except IPC13, IPC14 and IPC17)

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit which is set by the respective peripherals, or an external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 7-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>); these indicate the current CPU interrupt priority level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which, together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

The interrupt controller has the Interrupt Controller Test Register (INTTREG) that displays the status of the interrupt controller. When an interrupt request occurs, its associated vector number and the new interrupt priority level are latched into INTTREG.

This information can be used to determine a specific interrupt source if a generic ISR is used for multiple vectors – such as when ISR remapping is used in bootloader applications. It also could be used to check if another interrupt is pending while in an ISR.

All interrupt registers are described in Register 7-1 through Register 7-35, on the following pages.

| U-0         | R/W-1                              | R/W-0                                | R/W-0             | U-0                | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|-------------|------------------------------------|--------------------------------------|-------------------|--------------------|------------------|-----------------|---------|--|--|--|--|

| —           | T1IP2                              | T1IP1                                | T1IP0             |                    | OC1IP2           | OC1IP1          | OC1IP0  |  |  |  |  |

| bit 15      |                                    |                                      |                   |                    |                  |                 | bit     |  |  |  |  |

| U-0         | R/W-1                              | R/W-0                                | R/W-0             | U-0                | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

| 0-0         | IC1IP2                             | IC1IP1                               | IC1IP0            | 0-0                | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |

| <br>pit 7   | 10111 2                            |                                      |                   | _                  |                  |                 | bit     |  |  |  |  |

|             |                                    |                                      |                   |                    |                  |                 |         |  |  |  |  |

| _egend:     |                                    |                                      |                   |                    |                  |                 |         |  |  |  |  |

| R = Readab  |                                    | W = Writable                         |                   | •                  | mented bit, read |                 |         |  |  |  |  |

| n = Value a | It POR                             | '1' = Bit is set                     |                   | '0' = Bit is cle   | ared             | x = Bit is unkr | iown    |  |  |  |  |

| oit 15      | Unimplemer                         | ted: Read as '                       | 0'                |                    |                  |                 |         |  |  |  |  |

| oit 14-12   | T1IP<2:0>: ⊺                       | imer1 Interrupt                      | Priority bits     |                    |                  |                 |         |  |  |  |  |

|             | 111 = Interru                      | pt is Priority 7 (                   | highest priority  | y interrupt)       |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             |                                    | pt is Priority 1                     |                   |                    |                  |                 |         |  |  |  |  |

|             | 000 = Interrupt source is disabled |                                      |                   |                    |                  |                 |         |  |  |  |  |

| bit 11      | -                                  | nted: Read as '                      |                   |                    |                  |                 |         |  |  |  |  |

| bit 10-8    |                                    | : Output Compa                       |                   | -                  | ty bits          |                 |         |  |  |  |  |

|             | 111 = Interru                      | pt is Priority 7 (                   | nignest priority  | y interrupt)       |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             |                                    | pt is Priority 1<br>pt source is dis | abled             |                    |                  |                 |         |  |  |  |  |

| bit 7       |                                    | nted: Read as '                      |                   |                    |                  |                 |         |  |  |  |  |

| bit 6-4     | -                                  | Input Capture C                      |                   | rrupt Priority bit | s                |                 |         |  |  |  |  |

|             |                                    | pt is Priority 7 (                   |                   |                    |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •<br>001 = Interrupt is Priority 1 |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             |                                    | pt source is dis                     | abled             |                    |                  |                 |         |  |  |  |  |

| oit 3       | Unimplemer                         | nted: Read as '                      | 0'                |                    |                  |                 |         |  |  |  |  |

| oit 2-0     | INT0IP<2:0>                        | : External Inter                     | rupt 0 Priority I | bits               |                  |                 |         |  |  |  |  |

|             | 111 = Interru                      | pt is Priority 7 (                   | highest priority  | y interrupt)       |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •                                  |                                      |                   |                    |                  |                 |         |  |  |  |  |

|             | •<br>001 = Interru                 | pt is Priority 1                     |                   |                    |                  |                 |         |  |  |  |  |

## REGISTER 7-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

### REGISTER 13-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0             | U-0                                                  | U-0                      | U-0             | U-0                          | U-0               | U-0              | R/W-0             |  |

|-----------------|------------------------------------------------------|--------------------------|-----------------|------------------------------|-------------------|------------------|-------------------|--|

| —               | —                                                    | —                        |                 | —                            | —                 | _                | IC32              |  |

| bit 15          |                                                      |                          |                 |                              |                   |                  | bit 8             |  |

|                 |                                                      | 11.0                     |                 |                              |                   |                  |                   |  |

| R/W-0           | R/W-0, HS                                            | U-0                      | R/W-0           | R/W-1                        | R/W-1             | R/W-0            | R/W-1             |  |

| ICTRIG<br>bit 7 | TRIGSTAT                                             |                          | SYNCSEL4        | SYNCSEL3                     | SYNCSEL2          | SYNCSEL1         | SYNCSEL0<br>bit 0 |  |

|                 |                                                      |                          |                 |                              |                   |                  | bit 0             |  |

| Legend:         |                                                      | HS = Hardwa              | re Settable bit |                              |                   |                  |                   |  |

| R = Readable    | e bit                                                | W = Writable             | bit             | U = Unimplem                 | nented bit, read  | l as '0'         |                   |  |

| -n = Value at   | POR                                                  | '1' = Bit is set         |                 | '0' = Bit is clea            | ared              | x = Bit is unkr  | iown              |  |

|                 |                                                      |                          |                 |                              |                   |                  |                   |  |

| bit 15-9        | -                                                    | ted: Read as '           |                 |                              |                   |                  |                   |  |

| bit 8           |                                                      |                          |                 | (32-bit operation            |                   | act in both mar  |                   |  |

|                 |                                                      | ons independe            |                 | 2-bit module (th<br>t module | lis bit must be : |                  | lules)            |  |

| bit 7           | ICTRIG: ICx 1                                        | Frigger/Sync Se          | elect bit       |                              |                   |                  |                   |  |

|                 |                                                      |                          |                 | SYNCSELx bit                 |                   |                  |                   |  |

| bit 6           | -                                                    | mer Trigger Sta          | -               | d by SYNCSE                  | LX DItS           |                  |                   |  |

|                 |                                                      |                          |                 | s running (set ir            | n hardware. cai   | n be set in soft | ware)             |  |

|                 |                                                      |                          |                 | nd is being held             |                   |                  | /                 |  |

| bit 5           | Unimplement                                          | ted: Read as '           | )'              |                              |                   |                  |                   |  |

| bit 4-0         |                                                      |                          | nchronization S | Source Selectio              | n bits            |                  |                   |  |

|                 | 11111 = Rese<br>11110 = Rese                         |                          |                 |                              |                   |                  |                   |  |

|                 | 11101 <b>= Rese</b>                                  |                          |                 |                              |                   |                  |                   |  |

|                 | 11100 = CTM<br>11011 = A/D <sup>(</sup>              |                          |                 |                              |                   |                  |                   |  |

|                 | 11010 = Com                                          | parator 3 <sup>(1)</sup> |                 |                              |                   |                  |                   |  |

|                 | 11001 = Com<br>11000 = Com                           |                          |                 |                              |                   |                  |                   |  |

|                 | 10111 = Inpu                                         |                          |                 |                              |                   |                  |                   |  |

|                 | 10110 = Inpu                                         |                          |                 |                              |                   |                  |                   |  |

|                 | 10101 = Inpu<br>10100 = Inpu                         |                          |                 |                              |                   |                  |                   |  |

|                 | 10011 <b>= Res</b> e                                 | erved                    |                 |                              |                   |                  |                   |  |

|                 | 10010 = Rese<br>1000x = Rese                         |                          |                 |                              |                   |                  |                   |  |

|                 | 01111 <b>= Time</b>                                  | er5                      |                 |                              |                   |                  |                   |  |

|                 | 01110 = Time<br>01101 = Time                         |                          |                 |                              |                   |                  |                   |  |

|                 | 01100 <b>= Time</b>                                  | er2                      |                 |                              |                   |                  |                   |  |

|                 | 01011 = Time<br>01010 = Inpu                         |                          |                 |                              |                   |                  |                   |  |

|                 | 01001 = Rese                                         |                          |                 |                              |                   |                  |                   |  |

|                 | 01000 = Rese<br>00111 = Rese                         |                          |                 |                              |                   |                  |                   |  |

|                 | 00111 - Rese                                         |                          |                 |                              |                   |                  |                   |  |

|                 | 00101 = Outp                                         |                          |                 |                              |                   |                  |                   |  |

|                 | 00100 = Outp                                         |                          |                 |                              |                   |                  |                   |  |

|                 | 00011 = Output Compare 3<br>00010 = Output Compare 2 |                          |                 |                              |                   |                  |                   |  |

|                 |                                                      | out Compare 2            |                 |                              |                   |                  |                   |  |

**Note 1:** Use these inputs as trigger sources only and never as sync sources.

#### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

HS = Hardware Settable bit

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | R/W-0               | R/W-0               | R/W-0 |

|--------|--------|----------|-------|-----|---------------------|---------------------|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | —   | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32  |

| bit 15 |        |          |       |     |                     |                     | bit 8 |

| R/W-0  | R/W-0, HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|-----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT  | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |        |          |          |          |          | bit 0    |

| R = Read           | lable bit W = Writable bit                                                                     | U = Unimplemented bit                                                                        | , read as '0'                     |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| -n = Value         | e at POR '1' = Bit is set                                                                      | '0' = Bit is cleared                                                                         | x = Bit is unknown                |  |  |  |  |  |  |

|                    |                                                                                                |                                                                                              |                                   |  |  |  |  |  |  |

| bit 15             | FLTMD: Fault Mode Select bit                                                                   |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 1 = Fault mode is maintained until                                                             | the Fault source is removed and                                                              | d the corresponding OCFLT0 bit is |  |  |  |  |  |  |

|                    | cleared in software<br>0 = Fault mode is maintained until                                      | the Fault source is removed and                                                              | a new PWM period starts           |  |  |  |  |  |  |

| bit 14             | <b>FLTOUT:</b> Fault Out bit                                                                   |                                                                                              | a new r www.penou starts          |  |  |  |  |  |  |

|                    |                                                                                                | 1 = PWM output is driven high on a Fault                                                     |                                   |  |  |  |  |  |  |

|                    | 0 = PWM output is driven low on a                                                              |                                                                                              |                                   |  |  |  |  |  |  |

| bit 13             | FLTTRIEN: Fault Output State Sele                                                              | ect bit                                                                                      |                                   |  |  |  |  |  |  |

|                    | 1 = Pin is forced to an output on a                                                            |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 0 = Pin I/O condition is unaffected                                                            | by a Fault                                                                                   |                                   |  |  |  |  |  |  |

| bit 12             | OCINV: OCMP Invert bit                                                                         |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 1 = OCx output is inverted                                                                     |                                                                                              |                                   |  |  |  |  |  |  |

| bit 11             | 0 = OCx output is not inverted                                                                 |                                                                                              |                                   |  |  |  |  |  |  |

| bit 11<br>bit 10-9 | •                                                                                              | Unimplemented: Read as '0'<br>DCB<1:0>: OC Pulse-Width Least Significant bits <sup>(3)</sup> |                                   |  |  |  |  |  |  |

| DIL 10-9           | 11 = Delay OCx falling edge by 3/4                                                             |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 10 = Delay OCx falling edge by  1/2                                                            |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 01 = Delay OCx falling edge by 1/4                                                             | of the instruction cycle                                                                     |                                   |  |  |  |  |  |  |

|                    | 00 = OCx falling edge occurs at sta                                                            | -                                                                                            |                                   |  |  |  |  |  |  |

| bit 8              | OC32: Cascade Two OC Modules                                                                   | , , ,                                                                                        |                                   |  |  |  |  |  |  |

|                    | <ul> <li>1 = Cascade module operation ena</li> <li>0 = Cascade module operation dis</li> </ul> |                                                                                              |                                   |  |  |  |  |  |  |

| bit 7              | OCTRIG: OCx Trigger/Sync Select                                                                |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 1 = Trigger OCx from source desig                                                              |                                                                                              |                                   |  |  |  |  |  |  |

|                    | 0 = Synchronize OCx with source                                                                |                                                                                              |                                   |  |  |  |  |  |  |

| bit 6              | TRIGSTAT: Timer Trigger Status bi                                                              | t                                                                                            |                                   |  |  |  |  |  |  |

|                    | 1 = Timer source has been trigger                                                              | -                                                                                            |                                   |  |  |  |  |  |  |

|                    | 0 = Timer source has not been trig                                                             |                                                                                              |                                   |  |  |  |  |  |  |

| bit 5              | OCTRIS: OCx Output Pin Direction                                                               | Select bit                                                                                   |                                   |  |  |  |  |  |  |

|                    | 1 = OCx pin is tri-stated                                                                      | anneated to OCy ain                                                                          |                                   |  |  |  |  |  |  |

|                    | 0 = Output compare peripheral x co                                                             | prinected to UUX pin                                                                         |                                   |  |  |  |  |  |  |

| Note 1:            | Do not use an OC module as its own tr<br>SYNCSEL setting.                                      | igger source, either by selecting                                                            | this mode or another equivalent   |  |  |  |  |  |  |

| 2:                 | Use these inputs as trigger sources on                                                         | y and never as sync sources.                                                                 |                                   |  |  |  |  |  |  |

| 3:                 | These bits affect the rising edge when                                                         | OCINV = 1. The bits have no effe                                                             | ect when the                      |  |  |  |  |  |  |

|                    | OCM bits (OCxCON1<1:0>) = 001.                                                                 |                                                                                              |                                   |  |  |  |  |  |  |

Legend:

| REGISTER             | 15-1: SPIx                                                                                                                                          | STAT: SPIx S                                                                                                                                                        | FATUS AND                                                                                                           | CONTROL R                                                                                                      | EGISTER                                                                                        |                                        |                 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|

| R/W-0                | U-0                                                                                                                                                 | R/W-0                                                                                                                                                               | U-0                                                                                                                 | U-0                                                                                                            | R-0                                                                                            | R-0                                    | R-0             |

| SPIEN <sup>(1)</sup> |                                                                                                                                                     | SPISIDL                                                                                                                                                             | _                                                                                                                   | _                                                                                                              | SPIBEC2                                                                                        | SPIBEC1                                | SPIBEC0         |

| bit 15               |                                                                                                                                                     |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        | bit 8           |

| DA                   |                                                                                                                                                     |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                | DA                                     | DA              |

| R-0                  | R/C-0, HS                                                                                                                                           | R/W-0                                                                                                                                                               | R/W-0                                                                                                               | R/W-0                                                                                                          | R/W-0                                                                                          | R-0                                    | R-0             |

| SRMPT                | SPIROV                                                                                                                                              | SRXMPT                                                                                                                                                              | SISEL2                                                                                                              | SISEL1                                                                                                         | SISEL0                                                                                         | SPITBF                                 | SPIRBF<br>bit ( |

|                      |                                                                                                                                                     |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        | bit t           |

| Legend:              |                                                                                                                                                     | C = Clearable                                                                                                                                                       | bit                                                                                                                 | HS = Hardwa                                                                                                    | re Settable bit                                                                                |                                        |                 |

| R = Readab           | ole bit                                                                                                                                             | W = Writable                                                                                                                                                        | bit                                                                                                                 | U = Unimplen                                                                                                   | nented bit, read                                                                               | d as '0'                               |                 |

| -n = Value a         | at POR                                                                                                                                              | '1' = Bit is set                                                                                                                                                    |                                                                                                                     | '0' = Bit is cle                                                                                               | ared                                                                                           | x = Bit is unkr                        | iown            |

| bit 15               | <b>SPIEN:</b> SPIx<br>1 = Enables r<br>0 = Disables                                                                                                 | module and cor                                                                                                                                                      | figures SCKx,                                                                                                       | SDOx, SDIx a                                                                                                   | nd SSx as seria                                                                                | al port pins                           |                 |

| bit 14               | Unimplemen                                                                                                                                          | ted: Read as '                                                                                                                                                      | )'                                                                                                                  |                                                                                                                |                                                                                                |                                        |                 |

| bit 13               |                                                                                                                                                     | p in Idle Mode                                                                                                                                                      |                                                                                                                     |                                                                                                                |                                                                                                |                                        |                 |

|                      |                                                                                                                                                     | ue module oper<br>module operati                                                                                                                                    |                                                                                                                     |                                                                                                                | e mode                                                                                         |                                        |                 |

| bit 12-11            | Unimplemen                                                                                                                                          | ted: Read as '                                                                                                                                                      | )'                                                                                                                  |                                                                                                                |                                                                                                |                                        |                 |

| bit 10-8             | <b>SPIBEC&lt;2:0&gt;:</b> SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)<br><u>Master mode:</u><br>Number of SPI transfers pending. |                                                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        |                 |

|                      | Slave mode:                                                                                                                                         | Pl transfers unr                                                                                                                                                    | -                                                                                                                   |                                                                                                                |                                                                                                |                                        |                 |

| bit 7                |                                                                                                                                                     | Register (SPIx                                                                                                                                                      |                                                                                                                     | (valid in Enhar                                                                                                | nced Buffer mo                                                                                 | de)                                    |                 |

|                      | 1 = SPIx Shi                                                                                                                                        | ft register is em<br>ft register is not                                                                                                                             | pty and ready                                                                                                       |                                                                                                                |                                                                                                | ,                                      |                 |

| bit 6                | SPIROV: Red                                                                                                                                         | ceive Overflow                                                                                                                                                      | Flag bit                                                                                                            |                                                                                                                |                                                                                                |                                        |                 |

|                      | data in th                                                                                                                                          | rte/word is comp<br>le SPIxBUF reg<br>low has occurre                                                                                                               | ister.                                                                                                              | l and discarded                                                                                                | . The user softv                                                                               | vare has not rea                       | ad the previous |

| bit 5                |                                                                                                                                                     | ceive FIFO Em                                                                                                                                                       |                                                                                                                     | Enhanced But                                                                                                   | fer mode)                                                                                      |                                        |                 |

|                      |                                                                                                                                                     | FIFO is empty<br>FIFO is not em                                                                                                                                     |                                                                                                                     |                                                                                                                |                                                                                                |                                        |                 |

| bit 4-2              | SISEL<2:0>:                                                                                                                                         | SPIx Buffer Int                                                                                                                                                     | errupt Mode b                                                                                                       | its (valid in Enh                                                                                              | anced Buffer n                                                                                 | node)                                  |                 |

|                      | 110 = Internu<br>101 = Internu<br>100 = Internu<br>011 = Internu<br>010 = Internu<br>001 = Internu<br>000 = Internu                                 | pt when SPIx to<br>pt when last bit<br>pt when the las<br>pt when one da<br>pt when SPIx ro<br>pt when SPIx ro<br>pt when data is<br>pt when the la<br>APT bit set) | is shifted into<br>t bit is shifted<br>ata is shifted in<br>eceive buffer is<br>eceive buffer is<br>available in re | SPIxSR; as a r<br>out of SPIxSR;<br>to the SPIxSR;<br>s full (SPIRBF I<br>s 3/4 or more fu<br>eccive buffer (S | result, the TX F<br>now the transr<br>as a result, the<br>bit is set)<br>III<br>RMPT bit is se | nit is complete<br>e TX FIFO has<br>t) |                 |

|                      | f SPIEN = 1, the<br><b>Peripheral Pin</b>                                                                                                           |                                                                                                                                                                     |                                                                                                                     |                                                                                                                | Pn pins before                                                                                 | use. See Sect                          | ion 10.4        |

## REGISTER 15-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

### REGISTER 15-1: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = Transmit not vet started; SPIxTXB is full 0 = Transmit started; SPIxTXB is empty In Standard Buffer mode: Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR. In Enhanced Buffer mode: Automatically set in hardware when CPU writes SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write. bit 0 SPIRBF: SPIx Receive Buffer Full Status bit 1 = Receive complete, SPIxRXB is full 0 = Receive is not complete, SPIxRXB is empty In Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB. In Enhanced Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxSR to buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

- **Note 1:** If SPIEN = 1, these functions must be assigned to available RPn pins before use. See **Section 10.4** "**Peripheral Pin Select (PPS)**" for more information.

#### 18.5.2 COMPLETE A CONTROL TRANSACTION TO A CONNECTED DEVICE

- 1. Follow the procedure described in Section 18.5.1 "Enable Host Mode and Discover a Connected Device" to discover a device.

- Set up the Endpoint Control register for bidirectional control transfers by writing 0Dh to U1EP0 (this sets the EPCONDIS, EPTXEN, and EPHSHK bits).

- 3. Place a copy of the device framework setup command in a memory buffer. See Chapter 9 of the USB 2.0 specification for information on the device framework command set.

- Initialize the buffer descriptor (BD) for the current (EVEN or ODD) Tx EP0, to transfer the eight bytes of command data for a device framework command (i.e., a GET DEVICE DESCRIPTOR):

- a) Set the BD data buffer address (BD0ADR) to the starting address of the 8-byte memory buffer containing the command.

- b) Write 8008h to BD0STAT (this sets the UOWN bit, and sets a byte count of 8).

- 5. Set the USB device address of the target device in the address register (U1ADDR<6:0>). After a USB bus Reset, the device USB address will be zero. After enumeration, it will be set to another value between 1 and 127.

- 6. Write D0h to U1TOK; this is a SETUP token to Endpoint 0, the target device's default control pipe. This initiates a SETUP token on the bus, followed by a data packet. The device handshake is returned in the PID field of BD0STAT after the packets are complete. When the USB module updates BD0STAT, a transfer done interrupt is asserted (the TRNIF flag is set). This completes the setup phase of the setup transaction as referenced in Chapter 9 of the USB specification.

- 7. To initiate the data phase of the setup transaction (i.e., get the data for the GET DEVICE DESCRIPTOR command), set up a buffer in memory to store the received data.

- Initialize the current (EVEN or ODD) Rx or Tx (Rx for IN, Tx for OUT) EP0 BD to transfer the data:

- a) Write C040h to BD0STAT. This sets the UOWN, configures Data Toggle (DTS) to DATA1, and sets the byte count to the length of the data buffer (64 or 40h, in this case).

- b) Set BD0ADR to the starting address of the data buffer.

- 9. Write the token register with the appropriate IN or OUT token to Endpoint 0, the target device's default control pipe (e.g., write 90h to U1TOK for an IN token for a GET DEVICE DESCRIPTOR command). This initiates an IN token on the bus followed by a data packet from the device to the host. When the data packet completes, the BD0STAT is written and a transfer done interrupt is asserted (the TRNIF flag is set). For control transfers with a single packet data phase, this completes the data phase of the setup transaction as referenced in Chapter 9 of the USB specification. If more data needs to be transferred, return to step 8.

- 10. To initiate the status phase of the setup transaction, set up a buffer in memory to receive or send the zero length status phase data packet.

- 11. Initialize the current (even or odd) Tx EP0 BD to transfer the status data:

- a) Set the BDT buffer address field to the start address of the data buffer