Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

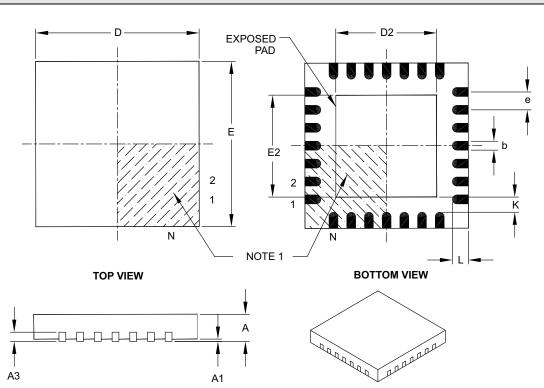

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb004-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-18: USB OTG REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12    | Bit 11    | Bit 10    | Bit 9  | Bit 8 | Bit 7               | Bit 6                   | Bit 5 | Bit 4         | Bit 3        | Bit 2   | Bit 1   | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|----------|-----------|-----------|-----------|--------|-------|---------------------|-------------------------|-------|---------------|--------------|---------|---------|--------|---------------|

| U1EP0     | 04AA | —      | —      | _        | —         | —         | _         | —      | —     | LSPD <sup>(1)</sup> | RETRYDIS <sup>(1)</sup> | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP1     | 04AC | _      | -      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP2     | 04AE | —      |        | _        | _         | —         | _         | _      | _     | —                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP3     | 04B0 | _      | -      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP4     | 04B2 | —      | Ι      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP5     | 04B4 | _      | -      | _        | _         | _         | _         | _      |       | -                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP6     | 04B6 | —      | _      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP7     | 04B8 | _      | -      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP8     | 04BA | —      | _      | _        | _         | _         | _         | _      |       | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP9     | 04BC | _      | _      | _        | _         | _         | _         | _      |       | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP10    | 04BE | _      | -      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP11    | 04C0 | —      | _      | _        | _         | _         | _         | _      |       | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP12    | 04C2 | —      | _      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP13    | 04C4 | _      | -      | _        | _         | _         | _         | _      | _     | _                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP14    | 04C6 | —      | _      | _        | _         | _         |           | —      |       |                     | —                       | -     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP15    | 04C8 | _      | _      | _        | _         | _         |           | _      |       | -                   | —                       | _     | EPCONDIS      | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1PWMRRS  | 04CC |        | U      | SB Power | Supply PV | /M Duty C | ycle Regi | ster   |       |                     |                         | USB F | ower Supply P | VM Period Re | egister |         |        | 0000          |

| U1PWMCON  | 04CE | PWMEN  | —      | _        | _         | _         |           | PWMPOL | CNTEN | _                   | —                       | _     | _             | —            | _       | -       | _      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note** 1: Alternate register or bit definitions when the module is operating in Host mode.

2: This register is available in Host mode only.

#### TABLE 4-19: PARALLEL MASTER/SLAVE PORT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                              | Bit 13 | Bit 12  | Bit 11  | Bit 10                | Bit 9                | Bit 8                | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                | Bit 2                | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|-----------------------------------------------------|--------|---------|---------|-----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------|--------|---------------|

| PMCON     | 0600 | PMPEN  | _                                                   | PSIDL  | ADRMUX1 | ADRMUX0 | PTBEEN                | PTWREN               | PTRDEN               | CSF1                 | CSF0                 | ALP                  | _                    | CS1P                 | BEP                  | WRSP   | RDSP   | 0000          |

| PMMODE    | 0602 | BUSY   | IRQM1                                               | IRQM0  | INCM1   | INCM0   | MODE16                | MODE1                | MODE0                | WAITB1               | WAITB0               | WAITM3               | WAITM2               | WAITM1               | WAITM0               | WAITE1 | WAITE0 | 0000          |

| PMADDR    | 0604 | -      | CS1                                                 | _      | _       | _       | ADDR10 <sup>(1)</sup> | ADDR9 <sup>(1)</sup> | ADDR8 <sup>(1)</sup> | ADDR7 <sup>(1)</sup> | ADDR6 <sup>(1)</sup> | ADDR5 <sup>(1)</sup> | ADDR4 <sup>(1)</sup> | ADDR3 <sup>(1)</sup> | ADDR2 <sup>(1)</sup> | ADDR1  | ADDR0  | 0000          |

| PMDOUT1   |      |        | Parallel Port Data Out Register 1 (Buffers 0 and 1) |        |         |         |                       |                      |                      |                      | 0000                 |                      |                      |                      |                      |        |        |               |

| PMDOUT2   | 0606 |        |                                                     |        |         |         | Pa                    | rallel Port D        | ata Out Reg          | gister 2 (Buf        | fers 2 and 3         | )                    |                      |                      |                      |        |        | 0000          |

| PMDIN1    | 0608 |        |                                                     |        |         |         | Pa                    | arallel Port I       | Data In Regi         | ister 1 (Buffe       | ers 0 and 1)         |                      |                      |                      |                      |        |        | 0000          |

| PMDIN2    | 060A |        |                                                     |        |         |         | Pa                    | arallel Port I       | Data In Regi         | ister 2 (Buffe       | ers 2 and 3)         |                      |                      |                      |                      |        |        | 0000          |

| PMAEN     | 060C | -      | PTEN14                                              | _      | _       | _       | PTEN10 <sup>(1)</sup> | PTEN9 <sup>(1)</sup> | PTEN8 <sup>(1)</sup> | PTEN7 <sup>(1)</sup> | PTEN6 <sup>(1)</sup> | PTEN5 <sup>(1)</sup> | PTEN4 <sup>(1)</sup> | PTEN3 <sup>(1)</sup> | PTEN2 <sup>(1)</sup> | PTEN1  | PTEN0  | 0000          |

| PMSTAT    | 060E | IBF    | IBOV                                                | _      | _       | IB3F    | IB2F                  | IB1F                 | IB0F                 | OBE                  | OBUF                 | _                    | _                    | OB3E                 | OB2E                 | OB1E   | OB0E   | 0000          |

PIC24FJ64GB004 FAMILY

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits are not available on 28-pin devices; read as '0'.

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused addresses should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

## 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

## 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

## 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### EXAMPLE 5-2: ERASING A PROGRAM MEMORY BLOCK – 'C' LANGUAGE CODE

| <pre>// C example using MPLAB C30     unsigned long progAddr = 0xXXXXXX;     unsigned int offset;</pre> | // Address of row to write                                              |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| //Set up pointer to the first memory locati                                                             | on to be written                                                        |

| TBLPAG = progAddr>>16;                                                                                  | // Initialize PM Page Boundary SFR                                      |

| offset = progAddr & 0xFFFF;                                                                             | // Initialize lower word of address                                     |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                                                              | <pre>// Set base address of erase block // with dummy latch write</pre> |

| NVMCON = $0 \times 4042$ ;                                                                              | // Initialize NVMCON                                                    |

| asm("DISI #5");                                                                                         | // Block all interrupts with priority <7                                |

|                                                                                                         | // for next 5 instructions                                              |

| builtin_write_NVM();                                                                                    | // C30 function to perform unlock                                       |

|                                                                                                         | // sequence and set WR                                                  |

|                                                                                                         |                                                                         |

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| <pre>MOV #0x4001, W0 ;<br/>MOV W0, NVMCON ; Initialize NVMCON<br/>; Set up a pointer to the first program memory location to be written<br/>; program memory selected, and writes enabled<br/>MOV #0x0000, W0 ;<br/>MOV #0x0000, W0 ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LIGW_BYTE_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TELWTH W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; Ist_program_word<br/>MOV #LIGW_WORD_1, W2 ;<br/>MOV #LIGW_BYTE_1, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; Ist_program_word<br/>MOV #LIGW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>; Ist_program_word<br/>MOV #LIGW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TELWTL W3, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch<br/>tBLWTH W3, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                            | ; Set up NVMCON for row programming oper- | ations                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------|

| <pre>; Set up a pointer to the first program memory location to be written<br/>; program memory selected, and writes enabled<br/>MOV</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MOV #0x4001, W0                           | ;                                           |

| <pre>; program memory selected, and writes enabled<br/>MOV #0x0000, W0 ;<br/>MOV W0, TBLPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x66000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>i.<br/>; 63rd_program_word<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MOV W0, NVMCON                            | ; Initialize NVMCON                         |

| <pre>MOV #0x0000, W0 ;<br/>MOV W0, TBLPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>ist_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>ist_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #LIGW_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>ist_ist_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #LIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ; Set up a pointer to the first program   | memory location to be written               |

| <pre>MOV W0, TBLPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ; program memory selected, and writes en  | abled                                       |

| <pre>MOV #0x6000, W0 ; An example program memory address ; Perform the TBLWT instructions to write the latches ; Oth_program_word     MOV #LOW_WORD_0, W2 ;     MOV #LGW_BYTE_0, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTH W3, [W0++] ; Write PM high byte into program latch ; lst_program_word     MOV #LOW_WORD_1, W2 ;     MOV #HIGH_BYTE_1, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTH W3, [W0++] ; Write PM high byte into program latch ; 2nd_program_word     MOV #HIGH_BYTE_2, W2 ;     MOV #HIGH_BYTE_2, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     rBLWTH W3, [W0++] ; Write PM low word into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM high byte into program latch     rBLWTL W2, [W0] ; Write PM low word into program latch     rBLWTL W2, [W0] ; Write PM low word into program latch     rBLWTL W2, [W0] ; Write PM low word into program latch     remove the program_word     MOV #LOW_WORD_31, W2 ;     MOV #HIGH_BYTE_31, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     remove the program latch     remove the program_word into program latch     remove the program_word into program latch     remove the program_word     MOV #LOW_WORD_31, W2 ;     MOV #HIGH_BYTE_31, W3 ;     rBLWTL W2, [W0] ; Write PM low word into program latch     remove the program latch</pre>                                                                                                                                                         | MOV #0x0000, W0                           | i                                           |

| <pre>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR           |

| <pre>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>; 63rd_program_word<br/>MOV #LOW_MORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MOV #0x6000, W0                           | ; An example program memory address         |

| <pre>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>is intermediate the program latch<br/>for the program_word into program latch<br/>is intermediate the program latch is intermediate the program latch<br/>is intermediate the program latch is intermediate t</pre> | ; Perform the TBLWT instructions to write | e the latches                               |

| <pre>MOV #HIGH_BYTE_0, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch TBLWTH W3, [W0++] ; Write PM high byte into program latch ; lst_program_word MOV #LOW_WORD_1, W2 ; MOV #HIGH_BYTE_1, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch ; 2nd_program_word MOV #LOW_WORD_2, W2 ; MOV #HIGH_BYTE_2, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch ; 63rd_program_word MOV #LOW_WORD_31, W2 ; MOV #HIGH_BYTE_31, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ; Oth_program_word                        |                                             |

| <pre>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MOV #LOW_WORD_0, W2                       | ;                                           |

| <pre>TBLWTH W3, [W0++] ; Write PM high byte into program latch ; lst_program_word MOV #LOW_WORD_1, W2 ; MOV #HIGH_BYTE_1, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch ; Znd_program_word MOV #LOW_WORD_2, W2 ; MOV #HIGH_BYTE_2, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch i tablewidth W3, [W0++] ; Write PM low word into program latch ; 63rd_program_word MOV #LOW_WORD_31, W2 ; MOV #HIGH_BYTE_31, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           | ;                                           |

| <pre>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>f63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,                                         | 1 3                                         |

| <pre>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>? 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           | ; Write PM high byte into program latch     |

| <pre>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           |                                             |

| <pre>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           | i                                           |

| <pre>TBLWTH W3, [W0++] ; Write PM high byte into program latch ; 2nd_program_word MOV #LOW_WORD_2, W2 ; MOV #HIGH_BYTE_2, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch TBLWTH W3, [W0++] ; Write PM high byte into program latch ; 63rd_program_word MOV #LOW_WORD_31, W2 ; MOV #HIGH_BYTE_31, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           | i                                           |

| <pre>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                                             |

| <pre>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ,                                         | ; Write PM high byte into program latch     |

| <pre>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                             |

| <pre>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           | i                                           |

| TBLWTH W3, [W0++] ; Write PM high byte into program latch<br>; 63rd_program_word<br>MOV #LOW_WORD_31, W2 ;<br>MOV #HIGH_BYTE_31, W3 ;<br>TBLWTL W2, [W0] ; Write PM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                             |

| •<br>•<br>•<br>; 63rd_program_word<br>MOV #LOW_WORD_31, W2 ;<br>MOV #HIGH_BYTE_31, W3 ;<br>TBLWTL W2, [W0] ; Write PM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                                             |

| MOV#LOW_WORD_31, W2;MOV#HIGH_BYTE_31, W3;TBLWTLW2, [W0];WritePM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch     |

| MOV#LOW_WORD_31, W2;MOV#HIGH_BYTE_31, W3;TBLWTLW2, [W0];WritePM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                         |                                             |

| MOV#LOW_WORD_31, W2;MOV#HIGH_BYTE_31, W3;TBLWTLW2, [W0];WritePM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                         |                                             |