#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb004-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-439-1

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

#### 3.3.2 DIVIDER

The divide block supports signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic Shift Right Source Register by One or More Bits. |

| SL          | Shift Left Source Register by One or More Bits.             |

| LSR         | Logical Shift Right Source Register by One or More Bits.    |

#### TABLE 4-20: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr | Bit 15           | Bit 14 | Bit 13      | Bit 12        | Bit 11  | Bit 10         | Bit 9         | Bit 8        | Bit 7      | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|------------------|--------|-------------|---------------|---------|----------------|---------------|--------------|------------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL   | 0620 |                  |        |             |               |         | Alarm          | Value Registe | r Window Bas | sed on ALR | MPTR<1:0  | >     |       |       |       |       |       | xxxx          |

| ALCFGRPT  | 0622 | ALRMEN           | CHIME  | AMASK3      | AMASK2        | AMASK1  | AMASK0         | ALRMPTR1      | ALRMPTR0     | ARPT7      | ARPT6     | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL    | 0624 |                  |        |             |               |         | RTCC           | Value Regist  | er Window Ba | ased on RT | CPTR<1:0> | •     |       |       |       |       |       | xxxx          |

| RCFGCAL   | 0626 | RTCEN            | _      | RTCWREN     | RTCSYNC       | HALFSEC | RTCOE          | RTCPTR1       | RTCPTR0      | CAL7       | CAL6      | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | xxxx          |

| Lenende   |      | the state of the |        | . (a) Deset | aluan ana ala |         | dia a face a f |               |              |            |           |       |       |       |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-21: CRC REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                           | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        | Bit 7        | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|----------------------------------|--------|---------|---------|---------|---------|--------------|--------------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1   | 0640 | CRCEN  | —                                | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0       | CRCFUL       | CRCMPT | CRCISEL | CRCGO | LENDIAN | —     | _     | _     | 0000          |

| CRCCON2   | 0642 | _      |                                  | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0      |              |        | _       | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL   | 0644 | X15    | X14                              | X13    | X12     | X11     | X10     | X9      | X8           | X7           | X6     | X5      | X4    | X3      | X2    | X1    | —     | 0000          |

| CRCXORH   | 0646 | X31    | X30                              | X29    | X28     | X27     | X26     | X25     | X24          | X23          | X22    | X21     | X20   | X19     | X19   | X17   | X16   | 0000          |

| CRCDATL   | 0648 |        |                                  |        |         |         |         | CRC     | Data Input F | Register Low | / Word |         |       |         |       |       |       | xxxx          |

| CRCDATH   | 064A |        |                                  |        |         |         |         | CRC     | Data Input F | egister High | n Word |         |       |         |       |       |       | xxxx          |

| CRCWDATL  | 064C |        | CRC Result Register Low Word xxx |        |         |         |         |         |              |              |        |         | xxxx  |         |       |       |       |               |

| CRCWDATH  | 064E |        | CRC Result Register High Word    |        |         |         |         |         |              |              |        |         |       |         | xxxx  |       |       |               |

| 1         |      |        |                                  |        |         |         |         |         |              |              |        |         |       |         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: COMPARATORS REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT    | 0650 | CMIDL  | _      | _      | _      | _      | C3EVT  | C2EVT   | C1EVT   | —      | _      | _     | _     | _     | C3OUT | C2OUT | C10UT | 0000          |

| CVRCON    | 0652 | _      | —      | _      | —      | _      | CVREFP | CVREFM1 | CVREFM0 | CVREN  | CVROE  | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON    | 0654 | CEN    | COE    | CPOL   | —      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | —     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM2CON    | 065C | CEN    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM3CON    | 0664 | CEN    | COE    | CPOL   | —      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred. Note that BOR is also set after a Power-on Reset.

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Setting Event                                          | Clearing Event                                                                                                                                                                                                                                                      |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trap Conflict Event                                    | POR                                                                                                                                                                                                                                                                 |

| Illegal Opcode or Uninitialized W Register Access      | POR                                                                                                                                                                                                                                                                 |

| Configuration Mismatch Reset                           | POR                                                                                                                                                                                                                                                                 |

| MCLR Reset                                             | POR                                                                                                                                                                                                                                                                 |

| RESET Instruction                                      | POR                                                                                                                                                                                                                                                                 |

| WDT Time-out                                           | PWRSAV Instruction, POR                                                                                                                                                                                                                                             |

| PWRSAV #SLEEP Instruction                              | POR                                                                                                                                                                                                                                                                 |

| PWRSAV #IDLE Instruction                               | POR                                                                                                                                                                                                                                                                 |

| POR, BOR                                               | _                                                                                                                                                                                                                                                                   |

| POR                                                    | _                                                                                                                                                                                                                                                                   |

| PWRSAV #SLEEP instruction with DSCON <dsen> set</dsen> | POR                                                                                                                                                                                                                                                                 |

|                                                        | Trap Conflict Event         Illegal Opcode or Uninitialized W Register Access         Configuration Mismatch Reset         MCLR Reset         RESET Instruction         WDT Time-out         PWRSAV #SLEEP Instruction         PWRSAV #IDLE Instruction         POR |

TABLE 6-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

#### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator configuration bits. Refer to **Section 8.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant |

|------------|--------------------------|

| POR        | FNOSC Configuration bits |

| BOR        | (CW2<10:8>)              |

| MCLR       | COSC Control bits        |

| WDTO       | (OSCCON<14:12>)          |

| SWR        |                          |

#### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the System Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| R/W-0        | U-0                 | R/W-0                              | R/W-0          | R/W-0                                  | R/W-0            | R/W-0           | R/W-0         |

|--------------|---------------------|------------------------------------|----------------|----------------------------------------|------------------|-----------------|---------------|

| ROEN         | _                   | ROSSLP                             | ROSEL          | RODIV3                                 | RODIV2           | RODIV1          | RODIV0        |

| bit 15       |                     |                                    |                |                                        |                  |                 | bit 8         |

|              |                     |                                    |                |                                        |                  |                 |               |

| U-0          | U-0                 | U-0                                | U-0            | U-0                                    | U-0              | U-0             | U-0           |

| —            | —                   | _                                  | —              | —                                      | —                | _               | _             |

| bit 7        |                     |                                    |                |                                        |                  |                 | bit (         |

| <u> </u>     |                     |                                    |                |                                        |                  |                 |               |

| Legend:      | 1- 1-14             |                                    | L :4           |                                        |                  | (O'             |               |

| R = Readab   |                     | W = Writable                       |                | -                                      | nented bit, read |                 |               |

| -n = Value a | IT POR              | '1' = Bit is set                   |                | '0' = Bit is clea                      | ared             | x = Bit is unkr | IOWN          |

| bit 15       | <b>ROFN</b> · Refer | ence Oscillator                    | Output Enabl   | e hit                                  |                  |                 |               |

|              |                     | e oscillator is er                 | •              |                                        |                  |                 |               |

|              |                     | e oscillator is di                 |                | • p                                    |                  |                 |               |

| bit 14       | Unimplemen          | ted: Read as '                     | )'             |                                        |                  |                 |               |

| bit 13       | ROSSLP: Re          | eference Oscilla                   | tor Output Sto | p in Sleep bit                         |                  |                 |               |

|              |                     | e oscillator conf                  |                |                                        |                  |                 |               |

|              |                     | e oscillator is di                 |                | •                                      |                  |                 |               |

| bit 12       |                     | erence Oscillato                   |                |                                        |                  |                 |               |

|              |                     |                                    |                | clock. Note that<br>ains the operation |                  |                 | enabled using |

|              |                     |                                    |                | base clock refle                       |                  |                 | e device      |

| bit 11-8     | -                   | : Reference Os                     |                |                                        |                  | j               |               |

|              | 1111 <b>= Base</b>  | clock value div                    | ided by 32,76  | 8                                      |                  |                 |               |

|              | 1110 <b>= Base</b>  | clock value div                    | ided by 16,384 |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div<br>clock value div |                |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div<br>clock value div | -              |                                        |                  |                 |               |

|              |                     | clock value div                    | ,              |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div                    |                |                                        |                  |                 |               |

|              |                     | clock value div                    | ided by 2      |                                        |                  |                 |               |

|              | 0000 <b>= Base</b>  |                                    |                |                                        |                  |                 |               |

| bit 7-0      | Unimplemen          | ted: Read as '                     | כ'             |                                        |                  |                 |               |

|              |                     |                                    |                |                                        |                  |                 |               |

#### **REGISTER 8-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

| REGISTER             |                                         | AKE: DEEP                          | SLEEP WAKE                                                                             | -UP SOURC              | E REGISTER            |                |                      |

|----------------------|-----------------------------------------|------------------------------------|----------------------------------------------------------------------------------------|------------------------|-----------------------|----------------|----------------------|

| U-0                  | U-0                                     | U-0                                | U-0                                                                                    | U-0                    | U-0                   | U-0            | R/W-0, HS            |

| _                    |                                         |                                    |                                                                                        |                        |                       |                | DSINT0 <sup>(1</sup> |

| oit 15               |                                         |                                    |                                                                                        |                        |                       |                | bit                  |

| R/W-0, HS            | U-0                                     | U-0                                | R/W-0, HS                                                                              | R/W-0, HS              | R/W-0, HS             | U-0            | R/W-0, HS            |

| DSFLT <sup>(1)</sup> | _                                       | _                                  | DSWDT <sup>(1)</sup>                                                                   | DSRTC <sup>(1)</sup>   | DSMCLR <sup>(1)</sup> | _              | DSPOR <sup>(2)</sup> |

| bit 7                |                                         |                                    |                                                                                        |                        | 1                     |                | bit                  |

| Legend:              |                                         | HS = Hardwa                        | are Settable bit                                                                       |                        |                       |                |                      |

| R = Readable         | e bit                                   | W = Writable                       | bit                                                                                    | U = Unimplen           | nented bit, read      | d as '0'       |                      |

| -n = Value at        | POR                                     | '1' = Bit is se                    | t                                                                                      | '0' = Bit is clea      | ared                  | x = Bit is un  | known                |

| bit 7                | DSFLT: Dee<br>1 = A Fault o<br>corrupte | p Sleep Fault I<br>occurred during | s not asserted du<br>Detected bit <sup>(1)</sup><br>g Deep Sleep ar<br>during Deep Sle | nd some Deep           |                       | ation settings | may have be          |

| bit 6-5              |                                         | nted: Read as                      |                                                                                        | eeh                    |                       |                |                      |

| bit 4                |                                         |                                    | o<br>ndog Timer Time                                                                   | out hit(1)             |                       |                |                      |

| Dit 4                | 1 = The Dee                             | p Sleep Watch                      | dog Timer timed<br>dog Timer did no                                                    | l out during De        |                       | )              |                      |

| bit 3                | DSRTC: Rea                              | al-Time Clock a                    | Ind Calendar Ala                                                                       | arm bit <sup>(1)</sup> |                       |                |                      |

|                      |                                         |                                    | nd Calendar trig<br>nd Calendar did                                                    |                        |                       |                |                      |

| bit 2                | $1 = \text{The } \overline{\text{MCL}}$ |                                    | R Event bit <sup>(1)</sup><br>erted during De<br>asserted during                       |                        |                       |                |                      |

| bit 1                |                                         | nted: Read as                      | -                                                                                      |                        |                       |                |                      |

| oit 0                | •                                       | wer-on Reset E                     |                                                                                        |                        |                       |                |                      |

|                      | 1 = The VDD                             | supply POR c                       | rcuit was active<br>rcuit was not ac                                                   |                        |                       |                | R event              |

| Note 1: Th           |                                         |                                    | e device is in D                                                                       |                        |                       |                |                      |

- **Note 1:** This bit can only be set while the device is in Deep Sleep mode.

- **2:** This bit can be set outside of Deep Sleep.

#### 10.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input, or two functional outputs configured as the same pin, there are no hardware enforced lock outs. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

#### 10.4.3.4 PPS Mapping Exceptions for PIC24FJ64GB0 Family Devices

Although the PPS registers allow for up to 32 remappable pins, not all of these are implemented in all devices. Exceptions and unimplemented RPn pins are listed in Table 10-4.

#### TABLE 10-4: REMAPPABLE PIN EXCEPTIONS FOR PIC24FJ64GB004 FAMILY DEVICES

| Device Pin |       | RP Pins (I/O)   |  |  |  |  |  |  |  |

|------------|-------|-----------------|--|--|--|--|--|--|--|

| Count      | Total | Unimplemented   |  |  |  |  |  |  |  |

| 28 Pins    | 15    | RP12, RP16-RP25 |  |  |  |  |  |  |  |

| 44 Pins    | 25    | RP12            |  |  |  |  |  |  |  |

#### 10.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit remapping lock

#### 10.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW2<4>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

#### REGISTER 10-13: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      |     |     | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 12-8  | SCK2R<4:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                         |

| bit 4-0   | SDI2R<4:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 10-14: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS2R<4:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

#### 13.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are modules 3 and 4, and so on.) The odd-numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even module (ICy) provides the Most Significant 16 bits. Wrap-arounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

### 13.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx, or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the sync source before proceeding.

- Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSEL bits (ICxCON2<4:0>) to the desired sync/trigger source.

- Set the ICTSEL bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSEL bits before the Input Capture module is enabled for proper synchronization with the desired clock source.

- 6. Set the ICI bits (ICxCON1<6:5>) to the desired interrupt frequency

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSEL bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICM bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected trigger/sync source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even-numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSEL and SYNCSEL bits for both modules to select the same sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSEL and SYNCSEL settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>); this forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICI bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the sync source as the last step. Both input capture modules are held in Reset until the sync source is enabled.

- Use the ICM bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the trigger/sync source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the lsw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (perform automatically by hardware).

### EQUATION 15-1: RELATIONSHIP BETWEEN DEVICE AND SPI CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 15-1: SAMPLE SCK FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               | Secondary Prescaler Settings |         |      |      |      |      |

|----------------------------|------------------------------|---------|------|------|------|------|

|                            | 1:1                          | 2:1     | 4:1  | 6:1  | 8:1  |      |

| Primary Prescaler Settings |                              | Invalid | 8000 | 4000 | 2667 | 2000 |

|                            | 4:1                          | 4000    | 2000 | 1000 | 667  | 500  |

|                            | 16:1                         | 1000    | 500  | 250  | 167  | 125  |

|                            | 64:1                         | 250     | 125  | 63   | 42   | 31   |

| Fcy = 5 MHz                |                              |         |      |      |      |      |

| Primary Prescaler Settings | 1:1                          | 5000    | 2500 | 1250 | 833  | 625  |

|                            | 4:1                          | 1250    | 625  | 313  | 208  | 156  |

|                            | 16:1                         | 313     | 156  | 78   | 52   | 39   |

|                            | 64:1                         | 78      | 39   | 20   | 13   | 10   |

**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

2: SCKx frequencies shown in kHz.

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC                                                                                                                                                                                                                                                                                                                                   |                                                                                           | U-0                                              | U-0                                            | U-0                            |                                      |                                                     |                      |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------------------|--------------------------------------|-----------------------------------------------------|----------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                            | R-0, HSC                                                                                  | 0-0                                              | 0-0                                            | 0-0                            | R/C-0, HS                            | R-0, HSC                                            | R-0, HSC             |  |  |  |

| ACKSTAT                                                                                                                                                                                                                                                                                                                                    | TRSTAT                                                                                    |                                                  | —                                              | —                              | BCL                                  | GCSTAT                                              | ADD10                |  |  |  |

| bit 15                                                                                                                                                                                                                                                                                                                                     |                                                                                           |                                                  |                                                |                                |                                      |                                                     | bit                  |  |  |  |

| R/C-0, HS                                                                                                                                                                                                                                                                                                                                  | R/C-0, HS                                                                                 | R-0, HSC                                         | R/C-0, HSC                                     | R/C-0, HSC                     | R-0, HSC                             | R-0, HSC                                            | R-0, HSC             |  |  |  |

| IWCOL                                                                                                                                                                                                                                                                                                                                      | I2COV                                                                                     | D/A                                              | Р                                              | S                              | R/W                                  | RBF                                                 | TBF                  |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                      |                                                                                           |                                                  |                                                |                                | 1                                    | l                                                   | bit                  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            |                                                                                           |                                                  |                                                |                                |                                      |                                                     |                      |  |  |  |

| Legend:                                                                                                                                                                                                                                                                                                                                    | <b>I</b> : C = Clearable bit HS = Hardware Settable bit HSC = Hardware Settable/Clearable |                                                  |                                                |                                |                                      |                                                     |                      |  |  |  |

| R = Readal                                                                                                                                                                                                                                                                                                                                 | ble bit                                                                                   | W = Writabl                                      | e bit                                          | U = Unimpleme                  | ented bit, read a                    | s '0'                                               |                      |  |  |  |

| -n = Value a                                                                                                                                                                                                                                                                                                                               | at POR                                                                                    | '1' = Bit is se                                  | et                                             | '0' = Bit is clear             | ed                                   | x = Bit is unknown                                  |                      |  |  |  |

| bit 15                                                                                                                                                                                                                                                                                                                                     | 1 = NACK<br>0 = ACK w<br>Hardware s                                                       |                                                  | d last<br>last<br>at the end of <i>l</i>       | Acknowledge.                   |                                      |                                                     |                      |  |  |  |

| bit 14 <b>TRSTAT:</b> Transmit Status bit<br>(When operating as I <sup>2</sup> C master. Applicable to master transmit operation.)<br>1 = Master transmit is in progress (8 bits + ACK)<br>0 = Master transmit is not in progress<br>Hardware set at the beginning of master transmission. Hardware clear at the end of slave Acknowledge. |                                                                                           |                                                  |                                                |                                |                                      |                                                     |                      |  |  |  |

| bit 13-11                                                                                                                                                                                                                                                                                                                                  | Unimplem                                                                                  | ented: Read                                      | <b>d as</b> '0'                                |                                |                                      |                                                     |                      |  |  |  |

| bit 10                                                                                                                                                                                                                                                                                                                                     | BCL: Mast                                                                                 | er Bus Collis                                    | sion Detect b                                  | it                             |                                      |                                                     |                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            | 0 = No coll                                                                               | ision                                            | been detecte                                   | ed during a mas<br>Ilision.    | ster operation                       |                                                     |                      |  |  |  |

| bit 9                                                                                                                                                                                                                                                                                                                                      |                                                                                           | General Call                                     |                                                |                                |                                      |                                                     |                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            | 0 = Genera                                                                                | al call addres                                   | ss was receiv<br>ss was not re<br>dress matche | ceived                         | all address. Ha                      | rdware clear at the S                               | Stop detection.      |  |  |  |

| bit 8                                                                                                                                                                                                                                                                                                                                      | ADD10: 10                                                                                 | )-Bit Address                                    | s Status bit                                   |                                |                                      |                                                     |                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            | 0 = 10-bit a                                                                              |                                                  | not matched                                    |                                | ed 10-bit addres                     | ss. Hardware clear a                                | t the Stop detectior |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                      |                                                                                           | rite Collisior                                   |                                                |                                |                                      |                                                     |                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            | 0 = No coll                                                                               | ision                                            |                                                | -                              |                                      | I <sup>2</sup> C module is busy<br>ed by software). |                      |  |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                                      |                                                                                           | ceive Overfl                                     |                                                |                                | ,                                    | ,                                                   |                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            | 1 = A byte<br>0 = No ove                                                                  | was receive<br>erflow                            | d while the I2                                 | -                              | er was still holdi<br>CxRCV (cleared | ng the previous byte<br>I by software).             |                      |  |  |  |

| bit 5                                                                                                                                                                                                                                                                                                                                      | D/A: Data/                                                                                | Address bit                                      | when operat                                    | ing as I <sup>2</sup> C slave  | e)                                   | ·                                                   |                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                            | 1 = Indicate<br>0 = Indicate                                                              | es that the la<br>es that the la<br>clear occurs | ast byte recei<br>ast byte recei               | ved was data<br>ved was the de | vice address                         | er a transmission finis                             | shes or at receptio  |  |  |  |

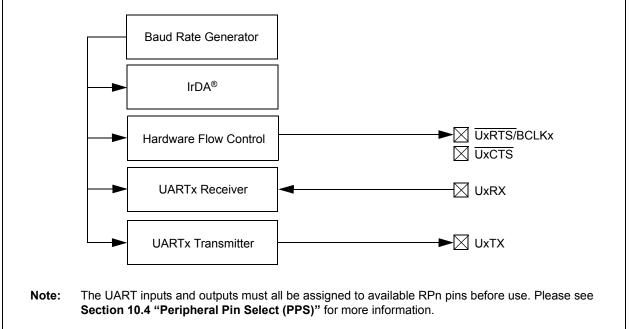

### 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features    |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |

|       | Section 21. "UART" (DS39708).              |  |  |  |  |  |  |

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 17-1. The UART module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

REGISTER 17-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                     | R/W-0                                        | R/W-0                | R/W-0              | U-0              | R/W-0            | R/W-0           |

|-----------------------|-------------------------|----------------------------------------------|----------------------|--------------------|------------------|------------------|-----------------|

| UARTEN <sup>(1)</sup> |                         | USIDL                                        | IREN <sup>(2)</sup>  | RTSMD              | —                | UEN1             | UEN0            |

| bit 15                |                         |                                              |                      |                    |                  |                  | bit 8           |

|                       |                         |                                              |                      |                    |                  |                  |                 |

| R/W-0, HC             | R/W-0                   | R/W-0, HC                                    | R/W-0                | R/W-0              | R/W-0            | R/W-0            | R/W-0           |

| WAKE                  | LPBACK                  | ABAUD                                        | RXINV                | BRGH               | PDSEL1           | PDSEL0           | STSEL           |

| bit 7                 |                         |                                              |                      |                    |                  |                  | bit             |

| <u> </u>              |                         |                                              | <u> </u>             |                    |                  |                  |                 |

| Legend:               |                         | HC = Hardware                                |                      |                    |                  |                  |                 |

| R = Readabl           |                         | W = Writable bi                              | t                    | -                  | nented bit, read |                  |                 |

| -n = Value at         | POR                     | '1' = Bit is set                             |                      | '0' = Bit is cle   | ared             | x = Bit is unkn  | own             |

| 6:4 <i>4</i> <b>5</b> |                         | ARTx Enable bit                              | (1)                  |                    |                  |                  |                 |

| bit 15                |                         |                                              |                      | a antrollad by LL  |                  |                  |                 |

|                       |                         | s enabled; all U/<br>s disabled; all UA      |                      |                    |                  |                  |                 |

| bit 14                |                         | nted: Read as '0                             | •                    |                    |                  |                  |                 |

| bit 13                | -                       | in Idle Mode bit                             |                      |                    |                  |                  |                 |

|                       | -                       | nue module ope                               | ration when the      | e device enters    | Idle mode        |                  |                 |

|                       |                         | e module operati                             |                      |                    |                  |                  |                 |

| bit 12                | IREN: IrDA <sup>®</sup> | Encoder and De                               | coder Enable         | bit <sup>(2)</sup> |                  |                  |                 |

|                       |                         | coder and decod                              |                      |                    |                  |                  |                 |

|                       |                         | coder and decod                              |                      |                    |                  |                  |                 |

| bit 11                |                         | de Selection for                             |                      |                    |                  |                  |                 |

|                       |                         | pin in Simplex m<br>pin in Flow Conti        |                      |                    |                  |                  |                 |

| bit 10                | -                       | nted: Read as '0                             |                      |                    |                  |                  |                 |

| bit 9-8               | -                       | JARTx Enable b                               |                      |                    |                  |                  |                 |

|                       | 11 = UxTX,              | UxRX and BCLI                                | Xx pins are enabled. | abled and used     | ; UxCTS pin co   | ntrolled by port | latches         |

|                       |                         | UxRX, UxCTS a                                |                      |                    |                  |                  |                 |

|                       |                         | UxRX and UxR <sup>*</sup><br>and UxRX pins a |                      |                    | · ·              |                  |                 |

|                       | latches                 |                                              | ale ellableu all     |                    |                  | CLKX pills con   | li olleu by pol |

| bit 7                 | WAKE: Wak               | e-up on Start Bit                            | Detect During        | Sleep Mode Er      | nable bit        |                  |                 |

|                       | 1 = UARTx               | will continue to s                           | ample the UxR        | X pin; interrupt   | generated on f   | alling edge; bit | cleared in      |

|                       |                         | e on following ris                           | sing edge            |                    |                  |                  |                 |

|                       | 0 = No wake             | •                                            |                      | .,                 |                  |                  |                 |

| bit 6                 |                         | ARTx Loopback                                | Mode Select b        | It                 |                  |                  |                 |

|                       |                         | Loopback mode<br>ok mode is disab            | ed                   |                    |                  |                  |                 |

| bit 5                 | -                       | o-Baud Enable I                              |                      |                    |                  |                  |                 |

|                       |                         | baud rate measu                              |                      | next characte      | r – requires rea | ception of a Syr | nc field (55h)  |

|                       | cleared                 | in hardware upo                              | n completion         |                    |                  | , ,              | <b>`</b>        |

|                       |                         | te measurement                               |                      | mpleted            |                  |                  |                 |

| bit 4                 |                         | eive Polarity Inve                           | ersion bit           |                    |                  |                  |                 |

|                       | 1 = UxRX Id             | le state is '0'<br>le state is '1'           |                      |                    |                  |                  |                 |

|                       |                         |                                              |                      |                    |                  |                  |                 |

|                       |                         | the peripheral ir                            |                      |                    |                  | vailable RPn pi  | n. See          |

| S                     |                         | Peripheral Pin S                             |                      |                    | ation.           |                  |                 |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

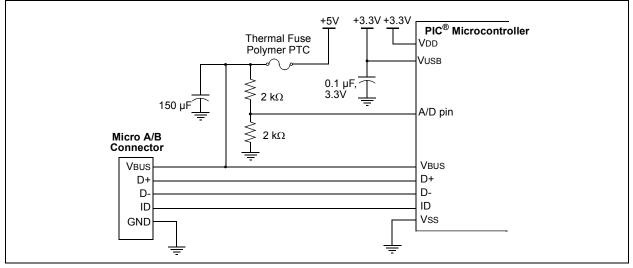

### 18.1.2 HOST AND OTG MODES

#### 18.1.2.1 D+ and D- Pull-down Resistors

PIC24FJ64GB004 family devices have built-in 15 kΩ pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the HOSTEN bit (U1CON<3>). If the OTGEN bit (U1OTGCON<2>) is set, then these pull-downs are enabled by setting the DPPULDWN and DMPULDWN bits (U1OTGCON<5:4>).

#### 18.1.2.2 Power Configurations

In Host mode, as well as Host mode in On-the-Go operation, the USB 2.0 specification requires that the Host application supply power on VBUS. Since the

microcontroller is running below VBUS and is not able to source sufficient current, a separate power supply must be provided.

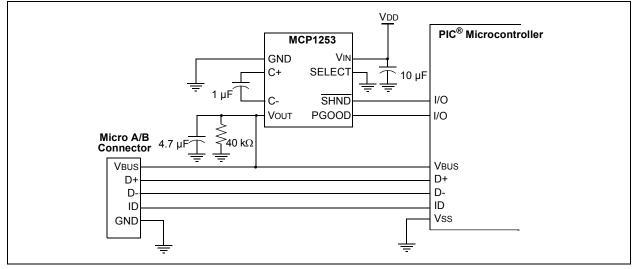

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 18-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 18-7.

#### FIGURE 18-6: HOST INTERFACE EXAMPLE

#### FIGURE 18-7: OTG INTERFACE EXAMPLE

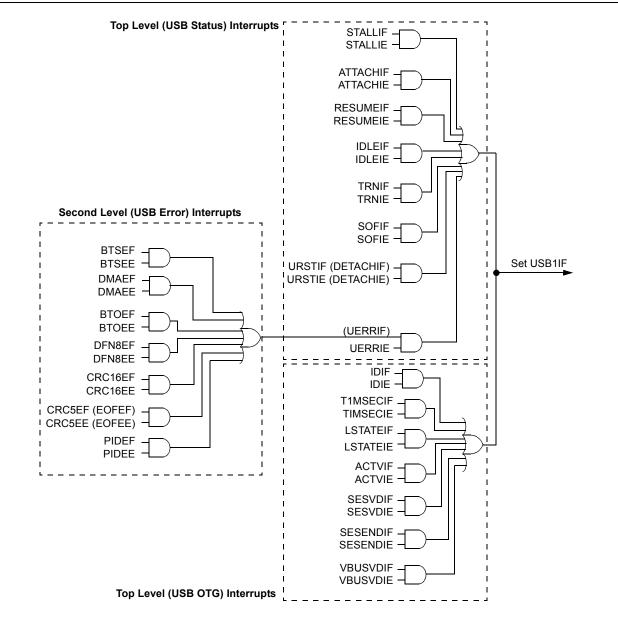

#### 18.3 USB Interrupts

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 18-9 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second

#### FIGURE 18-9: USB OTG INTERRUPT FUNNEL