#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2455-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.4.2 OSCILLATOR TRANSITIONS

PIC18F2455/2550/4455/4550 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the

sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

#### REGISTER 2-2: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0 | R/W-1 | R/W-0 | R/W-0 | R <sup>(1)</sup> | R-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------------|------|-------|-------|

| IDLEN | IRCF2 | IRCF1 | IRCF0 | OSTS             | IOFS | SCS1  | SCS0  |

| bit 7 |       |       |       |                  |      |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7     | IDLEN: Idle Enable bit                                                             |

|-----------|------------------------------------------------------------------------------------|

|           | 1 = Device enters Idle mode on <b>SLEEP</b> instruction                            |

|           | 0 = Device enters Sleep mode on SLEEP instruction                                  |

| bit 6-4   | IRCF2:IRCF0: Internal Oscillator Frequency Select bits                             |

|           | 111 = 8 MHz (INTOSC drives clock directly)                                         |

|           | 110 <b>= 4 MHz</b>                                                                 |

|           | 101 = 2  MHz                                                                       |

|           | $100 = 1 \text{ MHz}^{(3)}$                                                        |

|           | 011 = 500 kHz<br>010 = 250 kHz                                                     |

|           | 0.10 = 250  kHz                                                                    |

|           | 000 = 31  kHz (from either INTOSC/256 or INTRC directly) <sup>(2)</sup>            |

| bit 3     | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup>                |

|           | 1 = Oscillator Start-up Timer time-out has expired; primary oscillator is running  |

|           | 0 = Oscillator Start-up Timer time-out is running; primary oscillator is not ready |

| bit 2     | IOFS: INTOSC Frequency Stable bit                                                  |

|           | 1 = INTOSC frequency is stable                                                     |

|           | 0 = INTOSC frequency is not stable                                                 |

| bit 1-0   | SCS1:SCS0: System Clock Select bits                                                |

|           | 1x = Internal oscillator                                                           |

|           | 01 = Timer1 oscillator                                                             |

|           | 00 = Primary oscillator                                                            |

| Note 1: D | epends on the state of the IESO Configuration bit.                                 |

- 2: Source selected by the INTSRC bit (OSCTUNE<7>), see text.

- 3: Default output frequency of INTOSC on Reset.

| File Name            | Bit 7                | Bit 6                 | Bit 5              | Bit 4              | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Value on<br>POR, BOR | Details<br>on page |

|----------------------|----------------------|-----------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------|--------------------|

| EEADR                | EEPROM Ad            | dress Register        |                    |                    |                    |                    |                    |                    | 0000 0000            | 55, 91             |

| EEDATA               | EEPROM Da            | ita Register          |                    |                    |                    |                    |                    |                    | 0000 0000            | 55, 91             |

| EECON2               | EEPROM Co            | ntrol Register        | 2 (not a physic    | cal register)      |                    |                    |                    |                    | 0000 0000            | 55, 82             |

| EECON1               | EEPGD                | CFGS                  | _                  | FREE               | WRERR              | WREN               | WR                 | RD                 | xx-0 x000            | 55, 83             |

| IPR2                 | OSCFIP               | CMIP                  | USBIP              | EEIP               | BCLIP              | HLVDIP             | TMR3IP             | CCP2IP             | 1111 1111            | 56, 109            |

| PIR2                 | OSCFIF               | CMIF                  | USBIF              | EEIF               | BCLIF              | HLVDIF             | TMR3IF             | CCP2IF             | 0000 0000            | 56, 105            |

| PIE2                 | OSCFIE               | CMIE                  | USBIE              | EEIE               | BCLIE              | HLVDIE             | TMR3IE             | CCP2IE             | 0000 0000            | 56, 107            |

| IPR1                 | SPPIP <sup>(3)</sup> | ADIP                  | RCIP               | TXIP               | SSPIP              | CCP1IP             | TMR2IP             | TMR1IP             | 1111 1111            | 56, 108            |

| PIR1                 | SPPIF <sup>(3)</sup> | ADIF                  | RCIF               | TXIF               | SSPIF              | CCP1IF             | TMR2IF             | TMR1IF             | 0000 0000            | 56, 104            |

| PIE1                 | SPPIE <sup>(3)</sup> | ADIE                  | RCIE               | TXIE               | SSPIE              | CCP1IE             | TMR2IE             | TMR1IE             | 0000 0000            | 56, 106            |

| OSCTUNE              | INTSRC               | _                     | _                  | TUN4               | TUN3               | TUN2               | TUN1               | TUN0               | 00 0000              | 56, 28             |

| TRISE <sup>(3)</sup> | _                    | _                     | _                  | _                  | _                  | TRISE2             | TRISE1             | TRISE0             | 111                  | 56, 126            |

| TRISD <sup>(3)</sup> | TRISD7               | TRISD6                | TRISD5             | TRISD4             | TRISD3             | TRISD2             | TRISD1             | TRISD0             | 1111 1111            | 56, 124            |

| TRISC                | TRISC7               | TRISC6                | _                  | _                  | _                  | TRISC2             | TRISC1             | TRISC0             | 11111                | 56, 121            |

| TRISB                | TRISB7               | TRISB6                | TRISB5             | TRISB4             | TRISB3             | TRISB2             | TRISB1             | TRISB0             | 1111 1111            | 56, 118            |

| TRISA                | _                    | TRISA6 <sup>(4)</sup> | TRISA5             | TRISA4             | TRISA3             | TRISA2             | TRISA1             | TRISA0             | -111 1111            | 56, 115            |

| LATE <sup>(3)</sup>  | _                    | _                     | _                  | _                  | _                  | LATE2              | LATE1              | LATE0              | xxx                  | 56, 126            |

| LATD <sup>(3)</sup>  | LATD7                | LATD6                 | LATD5              | LATD4              | LATD3              | LATD2              | LATD1              | LATD0              | XXXX XXXX            | 56, 124            |

| LATC                 | LATC7                | LATC6                 | _                  | _                  | _                  | LATC2              | LATC1              | LATC0              | xxxxx                | 56, 121            |

| LATB                 | LATB7                | LATB6                 | LATB5              | LATB4              | LATB3              | LATB2              | LATB1              | LATB0              | XXXX XXXX            | 56, 118            |

| LATA                 | _                    | LATA6 <sup>(4)</sup>  | LATA5              | LATA4              | LATA3              | LATA2              | LATA1              | LATA0              | -xxx xxxx            | 56, 115            |

| PORTE                | RDPU <sup>(3)</sup>  | _                     | _                  | _                  | RE3 <sup>(5)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | 0 x000               | 56, 125            |

| PORTD <sup>(3)</sup> | RD7                  | RD6                   | RD5                | RD4                | RD3                | RD2                | RD1                | RD0                | XXXX XXXX            | 56, 124            |

| PORTC                | RC7                  | RC6                   | RC5 <sup>(6)</sup> | RC4 <sup>(6)</sup> | _                  | RC2                | RC1                | RC0                | xxxx -xxx            | 56, 121            |

| PORTB                | RB7                  | RB6                   | RB5                | RB4                | RB3                | RB2                | RB1                | RB0                | XXXX XXXX            | 56, 118            |

| PORTA                | _                    | RA6 <sup>(4)</sup>    | RA5                | RA4                | RA3                | RA2                | RA1                | RA0                | -x0x 0000            | 56, 115            |

| UEP15                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP14                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP13                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP12                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP11                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP10                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP9                 |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP8                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP7                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP6                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP5                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP4                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP3                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP2                 | _                    |                       |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP1                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP0                 |                      |                       |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

|                      |                      |                       |                    |                    |                    |                    |                    |                    |                      |                    |

| TABLE 5-2: | REGISTER | FILE SUMMARY | (CONTINUED) |

|------------|----------|--------------|-------------|

|            |          |              |             |

Legend:

x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

Bit 21 of the TBLPTRU allows access to the device Configuration bits.

Note 1:

2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

7:  $I^2C^{TM}$  Slave mode only.

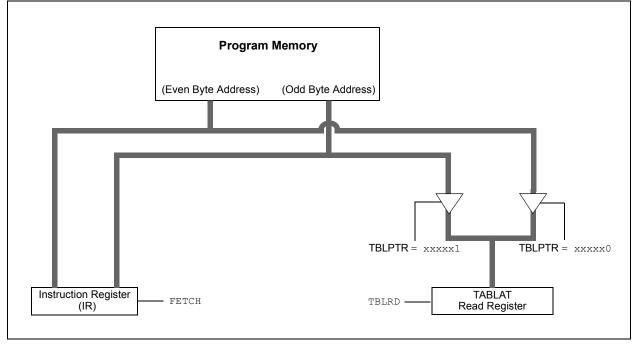

#### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVWF<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | oad TBLPTR with<br>ddress of the wo |               |

|-----------|-------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------|---------------|

| READ WORD |                                           |                                                                                     |                                     |               |

| —         | TBLRD*+                                   |                                                                                     | ead into TABLAT                     | and increment |

|           | MOVF                                      | TABLAT, W                                                                           | et data                             |               |

|           | MOVWF                                     | WORD_EVEN                                                                           |                                     |               |

|           | TBLRD*+                                   |                                                                                     | ead into TABLAT                     | and increment |

|           | MOVF                                      | TABLAT, W                                                                           | et data                             |               |

|           | MOVF                                      | WORD_ODD                                                                            |                                     |               |

|           |                                           |                                                                                     |                                     |               |

#### 10.3 PORTC, TRISC and LATC Registers

PORTC is a 7-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The RC3 pin is not implemented in these devices.

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is primarily multiplexed with serial communication modules, including the EUSART, MSSP module and the USB module (Table 10-5). Except for RC4 and RC5, PORTC uses Schmitt Trigger input buffers.

Pins RC4 and RC5 are multiplexed with the USB module. Depending on the configuration of the module, they can serve as the differential data lines for the onchip USB transceiver, or the data inputs from an external USB transceiver. Both RC4 and RC5 have TTL input buffers instead of the Schmitt Trigger buffers on the other pins.

Unlike other PORTC pins, RC4 and RC5 do not have TRISC bits associated with them. As digital ports, they can only function as digital inputs. When configured for USB operation, the data direction is determined by the configuration and status of the USB module at a given time. If an external transceiver is used, RC4 and RC5 always function as inputs from the transceiver. If the on-chip transceiver is used, the data direction is determined by the operation being performed by the module at that time.

When the external transceiver is enabled, RC2 also serves as the output enable control to the transceiver. Additional information on configuring USB options is provided in Section 17.2.2.2 "External Transceiver".

When enabling peripheral functions on PORTC pins other than RC4 and RC5, care should be taken in defining the TRIS bits. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

| Note: | On a Power-on Reset, these pins, except |

|-------|-----------------------------------------|

|       | RC4 and RC5, are configured as digital  |

|       | inputs. To use pins RC4 and RC5 as      |

|       | digital inputs, the USB module must be  |

|       | disabled (UCON<3> = 0) and the on-chip  |

|       | USB transceiver must be disabled        |

|       | (UCFG<3> = 1).                          |

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 10-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by |

|-------|-------|-----------------------|

|       |       | ; clearing output     |

|       |       | ; data latches        |

| CLRF  | LATC  | ; Alternate method    |

|       |       | ; to clear output     |

|       |       | ; data latches        |

| MOVLW | 07h   | ; Value used to       |

|       |       | ; initialize data     |

|       |       | ; direction           |

| MOVWF | TRISC | ; RC<5:0> as outputs  |

|       |       | ; RC<7:6> as inputs   |

|       |       |                       |

| Pin                 | Function            | TRIS<br>Setting | I/O | I/O Type | Description                                                                                                                               |  |  |

|---------------------|---------------------|-----------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RC0/T1OSO/          | RC0                 | 0               | OUT | DIG      | LATC<0> data output.                                                                                                                      |  |  |

| T13CKI              |                     | 1               | IN  | ST       | PORTC<0> data input.                                                                                                                      |  |  |

|                     | T10S0               | x               | OUT | ANA      | Timer1 oscillator output; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                |  |  |

|                     | T13CKI              | 1               | IN  | ST       | Timer1/Timer3 counter input.                                                                                                              |  |  |

| RC1/T <u>10SI</u> / | RC1                 | 0               | OUT | DIG      | LATC<1> data output.                                                                                                                      |  |  |

| CCP2/UOE            |                     | 1               | IN  | ST       | PORTC<1> data input.                                                                                                                      |  |  |

|                     | T10SI               | х               | IN  | ANA      | Timer1 oscillator input; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                 |  |  |

|                     | CCP2 <sup>(1)</sup> | 0               | OUT | DIG      | CCP2 compare and PWM output; takes priority over port data.                                                                               |  |  |

|                     |                     | 1               | IN  | ST       | CCP2 capture input.                                                                                                                       |  |  |

|                     | UOE                 | 0               | OUT | DIG      | External USB transceiver OE output.                                                                                                       |  |  |

| RC2/CCP1/           | RC2                 | 0               | OUT | DIG      | LATC<2> data output.                                                                                                                      |  |  |

| P1A                 |                     | 1               | IN  | ST       | PORTC<2> data input.                                                                                                                      |  |  |

|                     | CCP1                | 0               | OUT | DIG      | ECCP1 compare and PWM output; takes priority over port data.                                                                              |  |  |

|                     |                     | 1               | IN  | ST       | ECCP1 capture input.                                                                                                                      |  |  |

|                     | P1A <sup>(3)</sup>  | 0               | OUT | DIG      | ECCP1 Enhanced PWM output, Channel A; takes priority over port data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |

| RC4/D-/VM           | RC4                 | (2)             | IN  | TTL      | PORTC<4> data input; disabled when USB module or on-chip transceiver are enabled.                                                         |  |  |

|                     | D-                  | (2)             | OUT | XCVR     | USB bus differential minus line output (internal transceiver).                                                                            |  |  |

|                     |                     | (2)             | IN  | XCVR     | USB bus differential minus line input (internal transceiver).                                                                             |  |  |

|                     | VM                  | (2)             | IN  | TTL      | External USB transceiver VM input.                                                                                                        |  |  |

| RC5/D+/VP           | RC5                 | (2)             | IN  | TTL      | PORTC<5> data input; disabled when USB module or on-chip transceiver are enabled.                                                         |  |  |

|                     | D+                  | (2)             | OUT | XCVR     | USB bus differential plus line output (internal transceiver).                                                                             |  |  |

|                     |                     | (2)             | IN  | XCVR     | USB bus differential plus line input (internal transceiver).                                                                              |  |  |

|                     | VP                  | (2)             | IN  | TTL      | External USB transceiver VP input.                                                                                                        |  |  |

| RC6/TX/CK           | RC6                 | 0               | OUT | DIG      | LATC<6> data output.                                                                                                                      |  |  |

|                     |                     | 1               | IN  | ST       | PORTC<6> data input.                                                                                                                      |  |  |

|                     | TX                  | 0               | OUT | DIG      | Asynchronous serial transmit data output (EUSART module); takes priority over port data. User must configure as output.                   |  |  |

|                     | СК                  | 0               | OUT | DIG      | Synchronous serial clock output (EUSART module); takes priority over port data.                                                           |  |  |

|                     |                     | 1               | IN  | ST       | Synchronous serial clock input (EUSART module).                                                                                           |  |  |

### TABLE 10-5: PORTC I/O SUMMARY

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input,

TTL = TTL Buffer Input, XCVR = USB transceiver, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: Default pin assignment. Alternate pin assignment is RB3 (when CCP2MX = 0).

2: RC4 and RC5 do not have corresponding TRISC bits. In Port mode, these pins are input only. USB data direction is determined by the USB configuration.

3: 40/44-pin devices only.

| Pin              | Function | TRIS<br>Setting | I/O | I/О Туре | Description                                                                                              |  |  |

|------------------|----------|-----------------|-----|----------|----------------------------------------------------------------------------------------------------------|--|--|

| RE0/AN5/         | RE0      | 0               | OUT | DIG      | LATE<0> data output; not affected by analog input.                                                       |  |  |

| CK1SPP           |          | 1               | IN  | ST       | PORTE<0> data input; disabled when analog input enabled.                                                 |  |  |

|                  | AN5      | 1               | IN  | ANA      | A/D Input Channel 5; default configuration on POR.                                                       |  |  |

|                  | CK1SPP   | 0               | OUT | DIG      | SPP clock 1 output (SPP enabled).                                                                        |  |  |

| RE1/AN6/         | RE1      | 0               | OUT | DIG      | LATE<1> data output; not affected by analog input.                                                       |  |  |

| CK2SPP           |          | 1               | IN  | ST       | PORTE<1> data input; disabled when analog input enabled.                                                 |  |  |

|                  | AN6      | 1               | IN  | ANA      | A/D Input Channel 6; default configuration on POR.                                                       |  |  |

|                  | CK2SPP   | 0               | OUT | DIG      | SPP clock 2 output (SPP enabled).                                                                        |  |  |

| RE2/AN7/         | RE2      | 0               | OUT | DIG      | LATE<2> data output; not affected by analog input.                                                       |  |  |

| OESPP            |          | 1               | IN  | ST       | PORTE<2> data input; disabled when analog input enabled.                                                 |  |  |

|                  | AN7      | 1               | IN  | ANA      | A/D Input Channel 7; default configuration on POR.                                                       |  |  |

|                  | OESPP    | 0               | OUT | DIG      | SPP enable output (SPP enabled).                                                                         |  |  |

| MCLR/VPP/<br>RE3 | MCLR     | _(1)            | IN  | ST       | External Master Clear input; enabled when MCLRE Configuration bit is set.                                |  |  |

|                  | VPP      | (1)             | IN  | ANA      | High-voltage detection, used for ICSP™ mode entry detection.<br>Always available regardless of pin mode. |  |  |

|                  | RE3      | (1)             | IN  | ST       | PORTE<3> data input; enabled when MCLRE Configuration bit is clear.                                      |  |  |

#### TABLE 10-9: PORTE I/O SUMMARY

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input

**Note 1:** RE3 does not have a corresponding TRISE<3> bit. This pin is always an input regardless of mode.

| Name                  | Bit 7               | Bit 6   | Bit 5 | Bit 4  | Bit 3                | Bit 2              | Bit 1              | Bit 0              | Reset<br>Values<br>on page |

|-----------------------|---------------------|---------|-------|--------|----------------------|--------------------|--------------------|--------------------|----------------------------|

| PORTE                 | RDPU <sup>(3)</sup> |         | _     | _      | RE3 <sup>(1,2)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | 56                         |

| LATE <sup>(3)</sup>   | _                   | _       |       | _      | _                    | LATE2              | LATE1              | LATE0              | 56                         |

| TRISE <sup>(3)</sup>  | —                   | _       | —     | —      | _                    | TRISE2             | TRISE1             | TRISE0             | 56                         |

| ADCON1                | —                   | _       | VCFG1 | VCFG0  | PCFG3                | PCFG2              | PCFG1              | PCFG0              | 54                         |

| CMCON                 | C2OUT               | C10UT   | C2INV | C1INV  | CIS                  | CM2                | CM1                | CM0                | 55                         |

| SPPCON <sup>(3)</sup> | _                   | _       |       | _      | _                    | _                  | SPPOWN             | SPPEN              | 57                         |

| SPPCFG <sup>(3)</sup> | CLKCFG1             | CLKCFG0 | CSEN  | CLK1EN | WS3                  | WS2                | WS1                | WS0                | 57                         |

#### TABLE 10-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTE.

Note 1: Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

2: RE3 is the only PORTE bit implemented on both 28-pin and 40/44-pin devices. All other bits are implemented only when PORTE is implemented (i.e., 40/44-pin devices).

3: These registers or bits are unimplemented on 28-pin devices.

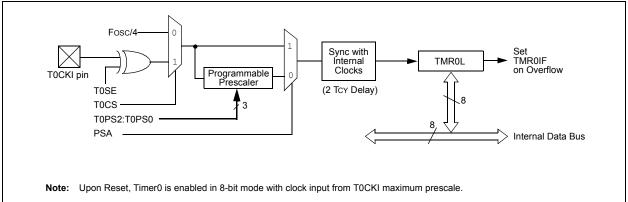

#### 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected by clearing the T0CS bit (T0CON<5>). In Timer mode, the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In Counter mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI/C1OUT/ RCV. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

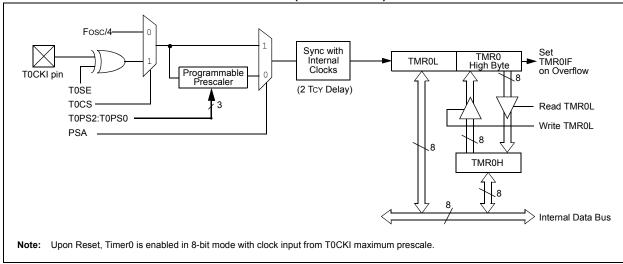

#### 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### FIGURE 11-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

#### 12.7 Considerations in Asynchronous Counter Mode

Following a Timer1 interrupt and an update to the TMR1 registers, the Timer1 module uses a falling edge on its clock source to trigger the next register update on the rising edge. If the update is completed after the clock input has fallen, the next rising edge will not be counted.

If the application can reliably update TMR1 before the timer input goes low, no additional action is needed. Otherwise, an adjusted update can be performed

following a later Timer1 increment. This can be done by monitoring TMR1L within the interrupt routine until it increments, and then updating the TMR1H:TMR1L register pair while the clock is low, or one-half of the period of the clock source. Assuming that Timer1 is being used as a Real-Time Clock, the clock source is a 32.768 kHz crystal oscillator; in this case, one-half period of the clock is 15.25  $\mu$ s.

The Real-Time Clock application code in Example 12-1 shows a typical ISR for Timer1, as well as the optional code required if the update cannot be done reliably within the required interval.

#### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                                               |

|---------|--------|--------------|---------------------------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                                       |

|         | CLRF   | TMR1L        |                                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator                 |

|         | CLRF   | secs         | ; Initialize timekeeping registers                            |

|         | CLRF   | mins         | ;                                                             |

|         | MOVLW  | .12          |                                                               |

|         | MOVWF  | hours        |                                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timerl interrupt                                     |

|         | RETURN |              |                                                               |

| RTCisr  |        |              |                                                               |

|         |        |              | ; Insert the next 4 lines of code when TMR1                   |

|         |        |              | ; can not be reliably updated before clock pulse goes low     |

|         | BTFSC  | TMR1L,0      | ; wait for TMR1L to become clear                              |

|         | BRA    | \$-2         | ; (may already be clear)                                      |

|         | BTFSS  | TMR1L,0      | ; wait for TMR1L to become set                                |

|         | BRA    | \$-2         | ; TMR1 has just incremented                                   |

|         |        |              | ; If TMR1 update can be completed before clock pulse goes low |

|         |        |              | ; Start ISR here                                              |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                                        |

|         | INCF   | secs, F      | ; Increment seconds                                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                         |

|         | CPFSGT | secs         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | secs         | ; Clear seconds                                               |

|         | INCF   | mins, F      | ; Increment minutes                                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                         |

|         | CPFSGT | mins         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | mins         | ; clear minutes                                               |

|         | INCF   | hours, F     | ; Increment hours                                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                           |

|         | CPFSGT | hours        |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | hours        | ; Reset hours                                                 |

|         | RETURN |              | ; Done                                                        |

|         |        |              |                                                               |

#### 17.2.2.8 Internal Regulator

The PIC18FX455/X550 devices have a built-in 3.3V regulator to provide power to the internal transceiver and provide a source for the internal/external pull-ups. An external 220 nF (±20%) capacitor is required for stability.

| Note: | The drive from VUSB is sufficient to only    |

|-------|----------------------------------------------|

|       | drive an external pull-up in addition to the |

|       | internal transceiver.                        |

The regulator can be enabled or disabled through the VREGEN Configuration bit. When enabled, the voltage is visible on pin VUSB whenever the USBEN bit is also set. When the regulator is disabled (VREGEN = 0), a 3.3V source must be provided through the VUSB pin for the internal transceiver.

- **Note 1:** Do not enable the internal regulator if an external regulator is connected to VUSB.

- 2: VDD must be equal to or greater than VUSB at all times, even with the regulator disabled.

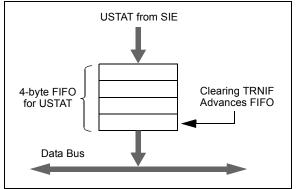

#### 17.2.3 USB STATUS REGISTER (USTAT)

The USB Status register reports the transaction status within the SIE. When the SIE issues a USB transfer complete interrupt, USTAT should be read to determine the status of the transfer. USTAT contains the transfer endpoint number, direction and Ping-Pong Buffer Pointer value (if used).

| Note: | The data in the USB Status register is valid |

|-------|----------------------------------------------|

|       | only when the TRNIF interrupt flag is        |

|       | asserted.                                    |

The USTAT register is actually a read window into a four-byte status FIFO, maintained by the SIE. It allows the microcontroller to process one transfer while the

SIE processes additional endpoints (Figure 17-4). When the SIE completes using a buffer for reading or writing data, it updates the USTAT register. If another USB transfer is performed before a transaction complete interrupt is serviced, the SIE will store the status of the next transfer into the status FIFO.

Clearing the transfer complete flag bit, TRNIF, causes the SIE to advance the FIFO. If the next data in the FIFO holding register is valid, the SIE will reassert the interrupt within 5 TCY of clearing TRNIF. If no additional data is present, TRNIF will remain clear; USTAT data will no longer be reliable.

Note: If an endpoint request is received while the USTAT FIFO is full, the SIE will automatically issue a NAK back to the host.

#### FIGURE 17-4: USTAT FIFO

#### 17.6 USB Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are Bus Power Only, Self-Power Only and Dual Power with Self-Power Dominance. The most common cases are presented here.

#### 17.6.1 BUS POWER ONLY

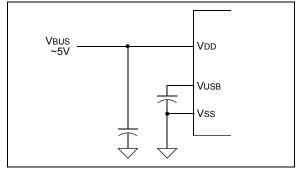

In Bus Power Only mode, all power for the application is drawn from the USB (Figure 17-10). This is effectively the simplest power method for the device.

In order to meet the inrush current requirements of the USB 2.0 specifications, the total effective capacitance appearing across VBUS and ground must be no more than 10  $\mu$ F. If not, some kind of inrush limiting is required. For more details, see Section 7.2.4 of the USB 2.0 specification.

According to the USB 2.0 specification, all USB devices must also support a Low-Power Suspend mode. In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable.

The host signals the USB device to enter the Suspend mode by stopping all USB traffic to that device for more than 3 ms. This condition will cause the IDLEIF bit in the UIR register to become set.

During the USB Suspend mode, the D+ or D- pull-up resistor must remain active, which will consume some of the allowed suspend current: 2.5 mA budget.

#### FIGURE 17-10: BUS POWER ONLY

#### 17.6.2 SELF-POWER ONLY

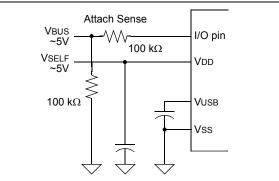

In Self-Power Only mode, the USB application provides its own power, with very little power being pulled from the USB. Figure 17-11 shows an example. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

In order to meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

#### FIGURE 17-11: SELF-POWER ONLY

## 17.6.3 DUAL POWER WITH SELF-POWER DOMINANCE

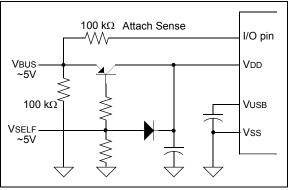

Some applications may require a dual power option. This allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Figure 17-12 shows a simple Dual Power with Self-Power Dominance example, which automatically switches between Self-Power Only and USB Bus Power Only modes.

Dual power devices also must meet all of the special requirements for inrush current and Suspend mode current and must not enable the USB module until VBUS is driven high. For descriptions of those requirements, see Section 17.6.1 "Bus Power Only" and Section 17.6.2 "Self-Power Only".

Additionally, dual power devices must never source current onto the 5V VBUS pin of the USB cable.

#### FIGURE 17-12: DUAL POWER EXAMPLE

Note: Users should keep in mind the limits for devices drawing power from the USB. According to USB specification 2.0, this cannot exceed 100 mA per low-power device or 500 mA per high-power device.

## PIC18F2455/2550/4455/4550

| Name  | Bit 7  | Bit 6  | Bit 5   | Bit 4  | Bit 3    | Bit 2   | Bit 1  | Bit 0   | Details on page |

|-------|--------|--------|---------|--------|----------|---------|--------|---------|-----------------|

| PIE2  | OSCFIE | CMIE   | USBIE   | EEIE   | BCLIE    | HLVDIE  | TMR3IE | CCP2IE  | 56              |

| UCON  | _      | PPBRST | SE0     | PKTDIS | USBEN    | RESUME  | SUSPND | _       | 57              |

| UCFG  | UTEYE  | UOEMON | _       | UPUEN  | UTRDIS   | FSEN    | PPB1   | PPB0    | 57              |

| USTAT | —      | ENDP3  | ENDP2   | ENDP1  | ENDP0    | DIR     | PPBI   | —       | 57              |

| UADDR | _      | ADDR6  | ADDR5   | ADDR4  | ADDR3    | ADDR2   | ADDR1  | ADDR0   | 57              |

| UFRML | FRM7   | FRM6   | FRM5    | FRM4   | FRM3     | FRM2    | FRM1   | FRM0    | 57              |

| UFRMH | —      | —      | _       | _      | —        | FRM10   | FRM9   | FRM8    | 57              |

| UIR   | _      | SOFIF  | STALLIF | IDLEIF | TRNIF    | ACTVIF  | UERRIF | URSTIF  | 57              |

| UIE   | —      | SOFIE  | STALLIE | IDLEIE | TRNIE    | ACTVIE  | UERRIE | URSTIE  | 57              |

| UEIR  | BTSEF  | —      | _       | BTOEF  | DFN8EF   | CRC16EF | CRC5EF | PIDEF   | 57              |

| UEIE  | BTSEE  | —      | _       | BTOEE  | DFN8EE   | CRC16EE | CRC5EE | PIDEE   | 57              |

| UEP0  | —      | _      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP1  | —      | _      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP2  | —      | _      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP3  | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP4  | —      | _      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP5  | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP6  | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP7  | —      | _      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP8  | —      | _      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP9  | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP10 | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP11 | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP12 | —      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP13 | _      | —      | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP14 | _      | _      |         | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

| UEP15 | —      | —      | —       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 57              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the USB module.

**Note 1:** This table includes only those hardware mapped SFRs located in Bank 15 of the data memory space. The Buffer Descriptor registers, which are mapped into Bank 4 and are not true SFRs, are listed separately in Table 17-5.

#### EXAMPLE 20-1: CALCULATING BAUD RATE ERROR

| For a device with FOSC | of   | 6 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|------------------------|------|-----------------------------------------------------------------|

| Desired Baud Rate      | =    | Fosc/(64 ([SPBRGH:SPBRG] + 1))                                  |

| Solving for SPBRGH:S   | SPBI | RG:                                                             |

| Х                      | =    | ((FOSC/Desired Baud Rate)/64) – 1                               |

|                        | =    | ((16000000/9600)/64) - 1                                        |

|                        | =    | [25.042] = 25                                                   |

| Calculated Baud Rate   | =    | 1600000/(64 (25 + 1))                                           |

|                        | =    | 9615                                                            |

| Error                  | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate    |

|                        | =    | (9615 - 9600)/9600 = 0.16%                                      |

|                        |      |                                                                 |

#### TABLE 20-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7                                         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on page |

|---------|-----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------------------------|

| TXSTA   | CSRC                                          | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 55                      |

| RCSTA   | SPEN                                          | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 55                      |

| BAUDCON | ABDOVF                                        | RCIDL | RXDTP | TXCKP | BRG16 | —     | WUE   | ABDEN | 55                      |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |       |       |       |       |       |       |       |                         |

| SPBRG   | EUSART B                                      |       | 55    |       |       |       |       |       |                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

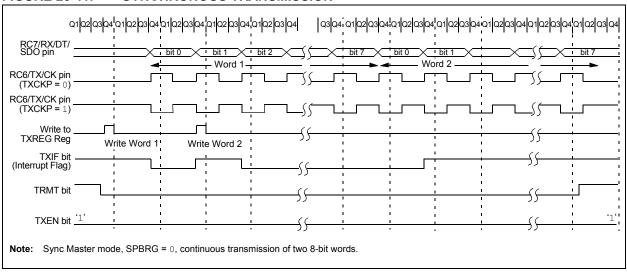

#### 20.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line.

Clock polarity (CK) is selected with the TXCKP bit (BAUDCON<4>). Setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. Data polarity (DT) is selected with the RXDTP bit (BAUDCON<5>). Setting RXDTP sets the Idle state on DT as high, while clearing the bit sets the Idle state as low. DT is sampled when CK returns to its idle state. This option is provided to support Microwire devices with this module.

#### 20.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 20-11: SYNCHRONOUS TRANSMISSION

### 24.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F2455/2550/4455/4550 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt. The High/Low-Voltage Detect Control register (Register 24-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 24-1.

#### REGISTER 24-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

|                 |                     |                  | 5               | 5444                  |                       | 5444                  | <b>-</b>              |

|-----------------|---------------------|------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/W-0           | U-0                 | R-0              | R/W-0           | R/W-0                 | R/W-1                 | R/W-0                 | R/W-1                 |

| VDIRMAG         | VDIRMAG — IRVS      |                  | HLVDEN          | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7           |                     |                  |                 |                       |                       |                       | bit 0                 |

|                 |                     |                  |                 |                       |                       |                       |                       |

| Legend:         |                     |                  |                 |                       |                       |                       |                       |

| R = Readable b  | oit                 | W = Writable     | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at P | OR                  | '1' = Bit is set |                 | '0' = Bit is cle      | ared                  | x = Bit is unkr       | nown                  |

|                 |                     |                  |                 |                       |                       |                       |                       |

| bit 7           | VDIRMAG: V          | oltage Directio  | n Magnitude S   | Select bit            |                       |                       |                       |

|                 | 1 = Event occ       | urs when volta   | ige equals or   | exceeds trip po       | oint (HLVDL3:HI       | LDVL0)                |                       |

|                 | 0 = Event occ       | urs when volta   | ige equals or   | falls below trip      | point (HLVDL3:        | HLVDL0)               |                       |

| bit 6           | Unimplemen          | ted: Read as '   | 0'              |                       |                       |                       |                       |

| bit 5           | IRVST: Interna      | al Reference V   | oltage Stable   | Flag bit              |                       |                       |                       |

|                 | 1 = Indicates       | that the voltag  | e detect logic  | will generate th      | e interrupt flag      | at the specified      | voltage range         |

|                 |                     |                  |                 | -                     | ate the interrup      | t flag at the spe     | ecified voltage       |

|                 | 0                   |                  | •               | not be enabled        | 1                     |                       |                       |

| bit 4           | 0                   | h/Low-Voltage    | Detect Powe     | r Enable bit          |                       |                       |                       |

|                 | 1 = HLVD ent        |                  |                 |                       |                       |                       |                       |

|                 | 0 = HLVD dis        |                  |                 | (1)                   |                       |                       |                       |

| bit 3-0         |                     | DL0: Voltage [   |                 |                       |                       |                       |                       |

|                 |                     | 0 1              | it is used (inp | ut comes from         | the HLVDIN pin        | 1)                    |                       |

|                 | 1110 <b>= Maxin</b> | num setting      |                 |                       |                       |                       |                       |

|                 | •                   |                  |                 |                       |                       |                       |                       |

|                 |                     |                  |                 |                       |                       |                       |                       |

|                 | 0000 <b>= Minim</b> | um setting       |                 |                       |                       |                       |                       |

|                 |                     |                  |                 |                       |                       |                       |                       |

Note 1: See Table 28-6 in Section 28.0 "Electrical Characteristics" for specifications.

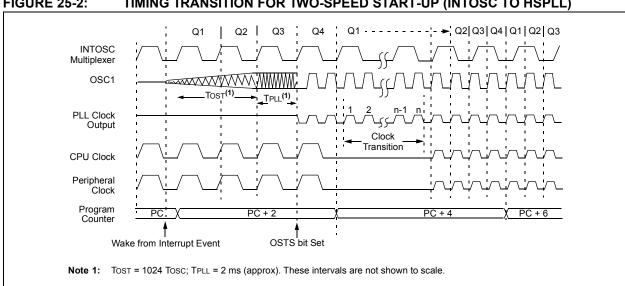

#### 25.3 **Two-Speed Start-up**

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is XT, HS, XTPLL or HSPLL (Crystal-Based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI RUN mode.

Because the OSCCON register is cleared on Reset events, the INTOSC (or postscaler) clock source is not initially available after a Reset event; the INTRC clock is used directly at its base frequency. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF2:IRCF0, immediately after

Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IRCF2:IRCF0 prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 25.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to Section 3.1.4 "Multiple Sleep Commands"). In practice, this means that user code can change the SCS1:SCS0 bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

#### **FIGURE 25-2:** TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

## PIC18F2455/2550/4455/4550

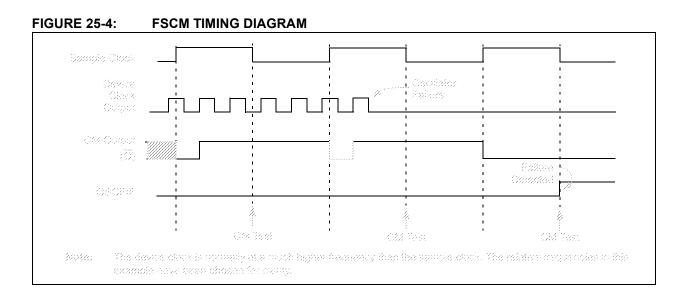

#### 25.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Clock Monitoring of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

### 25.4.4 POR OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is either EC or INTRC, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscilla-<br>tor failure interrupts on POR or wake from<br>Sleep will also prevent the detection of the<br>oscillator's failure to start at all following<br>these events. This can be avoided by<br>monitoring the OSTS bit and using a<br>timing routine to determine if the oscillator<br>is taking too long to start. Even so, no |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | oscillator failure interrupt will be flagged.                                                                                                                                                                                                                                                                                                                           |

As noted in Section 25.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled. 28.2

#### DC Characteristics: Power-Down and Supply Current PIC18F2455/2550/4455/4550 (Industrial) PIC18LF2455/2550/4455/4550 (Industrial) (Continued)

| (Industrial)<br>PIC18F2455/2550/4455/4550 |  |                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrialStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |    |       |            |                |  |  |  |

|-------------------------------------------|--|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|-------|------------|----------------|--|--|--|

|                                           |  |                                     |                                                                                                                                                                                                                                                                      |     |    |       |            |                |  |  |  |

|                                           |  | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                                                                                                                                      |     |    |       |            |                |  |  |  |

|                                           |  | PIC18LFX455/X550                    | 2.9                                                                                                                                                                                                                                                                  | 8   | μA | -40°C |            |                |  |  |  |

|                                           |  |                                     | 3.1                                                                                                                                                                                                                                                                  | 8   | μA | +25°C | VDD = 2.0V |                |  |  |  |

|                                           |  |                                     | 3.6                                                                                                                                                                                                                                                                  | 11  | μA | +85°C |            |                |  |  |  |

|                                           |  | PIC18LFX455/X550                    | 4.5                                                                                                                                                                                                                                                                  | 11  | μΑ | -40°C |            | Fosc = 31 kHz  |  |  |  |

|                                           |  |                                     | 4.8                                                                                                                                                                                                                                                                  | 11  | μΑ | +25°C | VDD = 3.0V | (RC_IDLE mode, |  |  |  |

|                                           |  |                                     | 5.8                                                                                                                                                                                                                                                                  | 15  | μΑ | +85°C |            | INTRC source)  |  |  |  |

|                                           |  | All devices                         | 9.2                                                                                                                                                                                                                                                                  | 16  | μΑ | -40°C |            |                |  |  |  |

|                                           |  |                                     | 9.8                                                                                                                                                                                                                                                                  | 16  | μA | +25°C | VDD = 5.0V |                |  |  |  |

|                                           |  |                                     | 11.4                                                                                                                                                                                                                                                                 | 36  | μΑ | +85°C |            |                |  |  |  |

|                                           |  | PIC18LFX455/X550                    | 165                                                                                                                                                                                                                                                                  | 350 | μA | -40°C |            |                |  |  |  |

|                                           |  |                                     | 175                                                                                                                                                                                                                                                                  | 350 | μΑ | +25°C | VDD = 2.0V |                |  |  |  |