Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2550-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0         | R/W-1 <sup>(1)</sup>                                                                                  | U-0                             | R/W-1                     | R-1                | R-1             | R/W-0 <sup>(2)</sup> | R/W-0        |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------|--------------------|-----------------|----------------------|--------------|--|--|--|--|

| IPEN          | SBOREN                                                                                                | _                               | RI                        | TO                 | PD              | POR                  | BOR          |  |  |  |  |

| oit 7         | •                                                                                                     |                                 |                           | •                  |                 |                      | bit          |  |  |  |  |

|               |                                                                                                       |                                 |                           |                    |                 |                      |              |  |  |  |  |

| Legend:       |                                                                                                       |                                 | . 1. 1                    |                    |                 |                      |              |  |  |  |  |

| R = Readable  |                                                                                                       | W = Writable                    |                           | -                  | mented bit, rea |                      |              |  |  |  |  |

| -n = Value at | POR                                                                                                   | '1' = Bit is se                 | et                        | '0' = Bit is cle   | eared           | x = Bit is unkn      | own          |  |  |  |  |

| bit 7         | IPEN: Interru                                                                                         | pt Priority Ena                 | able bit                  |                    |                 |                      |              |  |  |  |  |

|               | 1 = Enable pr                                                                                         |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               |                                                                                                       |                                 |                           | IC16CXXX Co        | mpatibility mod | de)                  |              |  |  |  |  |

| bit 6         | SBOREN: BO                                                                                            | OR Software E                   | Enable bit <sup>(1)</sup> |                    |                 |                      |              |  |  |  |  |

|               | If BOREN1:B                                                                                           |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | 1 = BOR is er                                                                                         |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | 0 = BOR is di                                                                                         | sabled                          |                           |                    |                 |                      |              |  |  |  |  |

|               | If BOREN1:BOREN0 = 00, 10 or 11:                                                                      |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | Bit is disabled                                                                                       | d and read as                   | ʻ0'.                      |                    |                 |                      |              |  |  |  |  |

| bit 5         | Unimplemen                                                                                            | ted: Read as                    | '0'                       |                    |                 |                      |              |  |  |  |  |

| bit 4         | RI: RESET Instruction Flag bit                                                                        |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | 1 = The RESET instruction was not executed (set by firmware only)                                     |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               |                                                                                                       | ET instruction<br>ut Reset occu |                           | d causing a de     | evice Reset (m  | nust be set in so    | ftware after |  |  |  |  |

| bit 3         |                                                                                                       |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | <b>TO:</b> Watchdog Time-out Flag bit<br>1 = Set by power-up, CLRWDT instruction or SLEEP instruction |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | 0 = A WDT time-out occurred                                                                           |                                 |                           |                    |                 |                      |              |  |  |  |  |

| bit 2         | PD: Power-D                                                                                           | own Detectior                   | n Flag bit                |                    |                 |                      |              |  |  |  |  |

|               | 1 = Set by power-up or by the CLRWDT instruction                                                      |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | 0 = Set by ex                                                                                         | kecution of the                 | e SLEEP instru            | ction              |                 |                      |              |  |  |  |  |

| bit 1         | <b>POR:</b> Power-on Reset Status bit <sup>(2)</sup>                                                  |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               |                                                                                                       |                                 |                           | (set by firmwar    |                 |                      |              |  |  |  |  |

|               | 0 = A Power                                                                                           | -on Reset occ                   | urred (must be            | e set in softwar   | e after a Powe  | r-on Reset occur     | s)           |  |  |  |  |

| bit 0         | BOR: Brown-                                                                                           | out Reset Sta                   | itus bit                  |                    |                 |                      |              |  |  |  |  |

|               | 1 = A Brown-out Reset has not occurred (set by firmware only)                                         |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               | 0 = A Brown                                                                                           | -out Reset oc                   | curred (must b            | e set in softwa    | re after a Brow | n-out Reset occu     | urs)         |  |  |  |  |

| Note 1: If    | SBOREN is enal                                                                                        | bled, its Rese                  | t state is '1'; of        | therwise, it is 'd | )'.             |                      |              |  |  |  |  |

|               |                                                                                                       |                                 |                           |                    |                 | See the notes foll   | owing this   |  |  |  |  |

|               | gister and Section                                                                                    |                                 |                           |                    |                 |                      | -            |  |  |  |  |

| Note 1: It    | is recommended                                                                                        | d that the $\overline{POF}$     | R bit be set aft          | er a Power-on      | Reset has bee   | n detected so that   | at subseque  |  |  |  |  |

|               | ower-on Resets                                                                                        |                                 |                           |                    |                 |                      |              |  |  |  |  |

|               |                                                                                                       |                                 |                           |                    |                 |                      |              |  |  |  |  |

### REGISTER 4-1: RCON: RESET CONTROL REGISTER

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after POR).

## 5.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 6.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 7.0 "Data EEPROM Memory"**.

### 5.1 Program Memory Organization

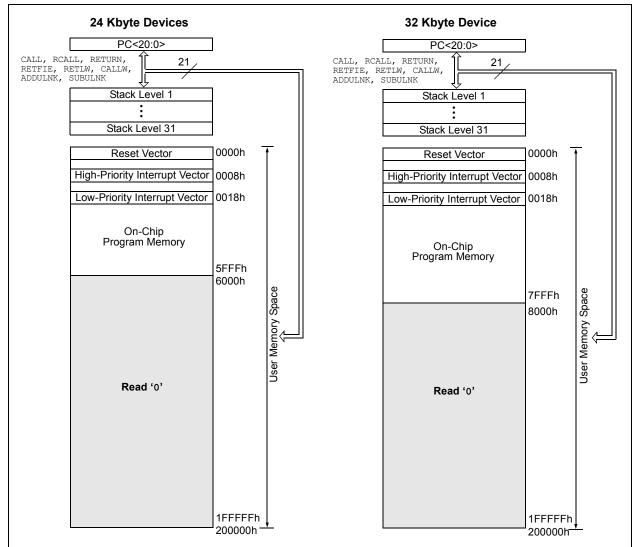

PIC18 microcontrollers implement a 21-bit program counter which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2455 and PIC18F4455 each have 24 Kbytes of Flash memory and can store up to 12,288 single-word instructions. The PIC18F2550 and PIC18F4550 each have 32 Kbytes of Flash memory and can store up to 16,384 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory maps for PIC18FX455 and PIC18FX550 devices are shown in Figure 5-1.

FIGURE 5-1: PROGRAM MEMORY MAP AND STACK

## 5.4.3.1 FSR Registers and the INDF Operand

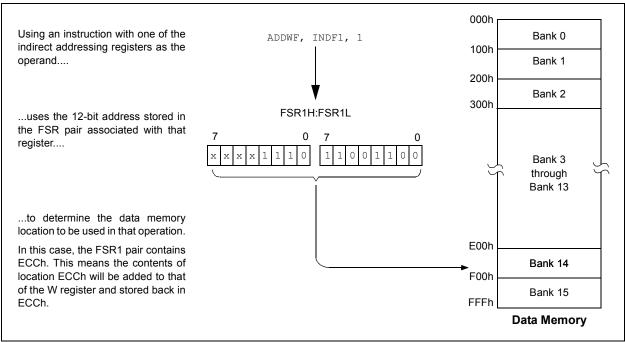

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers: FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers; they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### FIGURE 5-7: INDIRECT ADDRESSING

### 9.2 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0       | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0         | R/W-x               |  |  |  |

|-------------|-----------|--------|--------|-------|--------|---------------|---------------------|--|--|--|

| GIE/GIEH    | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF <sup>(1)</sup> |  |  |  |

| bit 7 bit 0 |           |        |        |       |        |               |                     |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | GIE/GIEH: Global Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br><u>When IPEN = 1:</u> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables all high-priority interrupts</li> <li>0 = Disables all interrupts</li> </ul>                                                             |

| bit 6   | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                                    |

|         | <u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                             |

|         | <u>When IPEN = 1:</u><br>1 = Enables all low-priority peripheral interrupts (if GIE/GIEH = 1)<br>0 = Disables all low-priority peripheral interrupts          |

| bit 5   | <b>TMR0IE:</b> TMR0 Overflow Interrupt Enable bit                                                                                                             |

|         | <ul> <li>1 = Enables the TMR0 overflow interrupt</li> <li>0 = Disables the TMR0 overflow interrupt</li> </ul>                                                 |

| bit 4   | INT0IE: INT0 External Interrupt Enable bit                                                                                                                    |

|         | <ul> <li>1 = Enables the INT0 external interrupt</li> <li>0 = Disables the INT0 external interrupt</li> </ul>                                                 |

| bit 3   | RBIE: RB Port Change Interrupt Enable bit                                                                                                                     |

|         | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul>                                               |

| bit 2   | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                      |

|         | <ul> <li>1 = TMR0 register has overflowed (must be cleared in software)</li> <li>0 = TMR0 register did not overflow</li> </ul>                                |

| bit 1   | INT0IF: INT0 External Interrupt Flag bit                                                                                                                      |

|         | <ul> <li>1 = The INT0 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT0 external interrupt did not occur</li> </ul>             |

| bit 0   | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                                                 |

|         | <ul> <li>1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)</li> <li>0 = None of the RB7:RB4 pins have changed state</li> </ul> |

| N - 4 - |                                                                                                                                                               |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB, and then waiting one additional instruction cycle, will end the mismatch condition and allow the bit to be cleared.

### 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-2 increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

### 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name    | Bit 7      | Bit 6                 | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------|-----------------------|---------|---------|--------|--------|--------|--------|----------------------------|

| TMR0L   | Timer0 Reg | ister Low By          | te      |         |        |        |        |        | 54                         |

| TMR0H   | Timer0 Reg | ister High By         | /te     |         |        |        |        |        | 54                         |

| INTCON  | GIE/GIEH   | PEIE/GIEL             | TMR0IE  | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 53                         |

| INTCON2 | RBPU       | INTEDG0               | INTEDG1 | INTEDG2 | _      | TMR0IP | —      | RBIP   | 53                         |

| T0CON   | TMR0ON     | T08BIT                | TOCS    | T0SE    | PSA    | T0PS2  | T0PS1  | T0PS0  | 54                         |

| TRISA   | _          | TRISA6 <sup>(1)</sup> | TRISA5  | TRISA4  | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 56                         |

Legend: — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

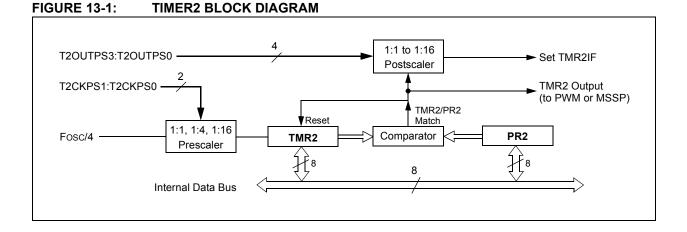

## 13.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS3:T2OUTPS0 (T2CON<6:3>).

## 13.3 TMR2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 19.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6       | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |  |

|--------|----------------------|-------------|----------|----------|----------|--------|---------|---------|----------------------------|--|

| INTCON | GIE/GIEH             | PEIE/GIEL   | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 53                         |  |

| PIR1   | SPPIF <sup>(1)</sup> | ADIF        | RCIF     | TXIF     | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 56                         |  |

| PIE1   | SPPIE <sup>(1)</sup> | ADIE        | RCIE     | TXIE     | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 56                         |  |

| IPR1   | SPPIP <sup>(1)</sup> | ADIP        | RCIP     | TXIP     | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 56                         |  |

| TMR2   | Timer2 Register      |             |          |          |          |        |         |         |                            |  |

| T2CON  | _                    | T2OUTPS3    | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 54                         |  |

| PR2    | Timer2 Peri          | od Register |          |          |          |        |         |         | 54                         |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

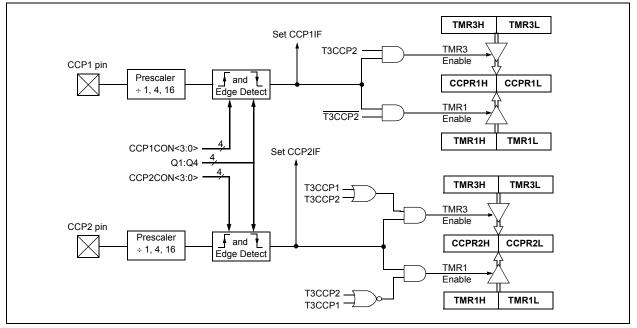

### 15.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding CCPx pin. An event is defined as one of the following:

- · every falling edge

- · every rising edge

- every 4th rising edge

- · every 16th rising edge

The event is selected by the mode select bits, CCPxM3:CCPxM0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit, CCPxIF, is set; it must be cleared in software. If another capture occurs before the value in register CCPRx is read, the old captured value is overwritten by the new captured value.

#### 15.2.1 CCP PIN CONFIGURATION

In Capture mode, the appropriate CCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If RB3/CCP2 or RC1/CCP2 is configured       |

|-------|---------------------------------------------|

|       | as an output, a write to the port can cause |

|       | a capture condition.                        |

#### 15.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation will not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 15.1.1 "CCP Modules and Timer Resources").

#### 15.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

#### 15.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCPxM3:CCPxM0). Whenever the CCP module is turned off or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 15-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS (CCP2 SHOWN)

| CLRF  | CCP2CON     | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP2CON     | ; | Load CCP2CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

#### FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

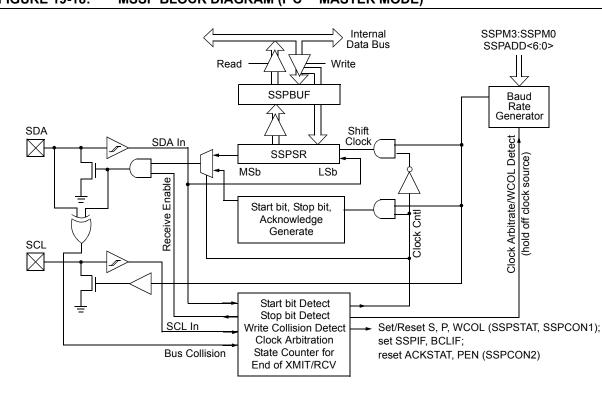

### 19.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\sf I}^2{\sf C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options:

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (and MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

## FIGURE 19-18: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

| Name                 | Bit 7                | Bit 6                        | Bit 5       | Bit 4  | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------------------|----------------------|------------------------------|-------------|--------|----------|--------|--------|--------|----------------------------|

| INTCON               | <b>GIE/GIEH</b>      | PEIE/GIEL                    | TMR0IE      | INT0IE | RBIE     | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR1                 | SPPIF <sup>(1)</sup> | ADIF                         | RCIF        | TXIF   | SSPIF    | CCP1IF | TMR2IF | TMR1IF | 56                         |

| PIE1                 | SPPIE <sup>(1)</sup> | ADIE                         | RCIE        | TXIE   | SSPIE    | CCP1IE | TMR2IE | TMR1IE | 56                         |

| IPR1                 | SPPIP <sup>(1)</sup> | ADIP                         | RCIP        | TXIP   | SSPIP    | CCP1IP | TMR2IP | TMR1IP | 56                         |

| PIR2                 | OSCFIF               | CMIF                         | USBIF       | EEIF   | BCLIF    | HLVDIF | TMR3IF | CCP2IF | 56                         |

| PIE2                 | OSCFIE               | CMIE                         | USBIE       | EEIE   | BCLIE    | HLVDIE | TMR3IE | CCP2IE | 56                         |

| IPR2                 | OSCFIP               | CMIP                         | USBIP       | EEIP   | BCLIP    | HLVDIP | TMR3IP | CCP2IP | 56                         |

| TRISC                | TRISC7               | TRISC6                       | _           | _      | _        | TRISC2 | TRISC1 | TRISC0 | 56                         |

| TRISD <sup>(1)</sup> | TRISD7               | TRISD6                       | TRISD5      | TRISD4 | TRISD3   | TRISD2 | TRISD1 | TRISD0 | 56                         |

| SSPBUF               | MSSP Rec             | eive Buffer/T                | ransmit Reg | gister |          |        |        |        | 54                         |

| SSPADD               |                      | ress Registe<br>d Rate Reloa |             |        | er mode. |        |        |        | 54                         |

| TMR2                 | Timer2 Reg           | gister                       |             |        |          |        |        |        | 54                         |

| PR2                  | Timer2 Per           | iod Register                 |             |        |          |        |        |        | 54                         |

| SSPCON1              | WCOL                 | SSPOV                        | SSPEN       | CKP    | SSPM3    | SSPM2  | SSPM1  | SSPM0  | 54                         |

| SSPCON2              | GCEN                 | ACKSTAT                      | ACKDT       | ACKEN  | RCEN     | PEN    | RSEN   | SEN    | 54                         |

| SSPSTAT              | SMP                  | CKE                          | D/A         | Р      | S        | R/W    | UA     | BF     | 54                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in  $I^2C^{TM}$  mode.

Note 1: These registers or bits are not implemented in 28-pin devices.

#### 20.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 20-8) and asynchronously, if the device is in Sleep mode (Figure 20-9). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

## 20.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false End-Of-

Character and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 20.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

| FIGURE 20-8: | AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION |

|--------------|--------------------------------------------------------|

|--------------|--------------------------------------------------------|

|            | (edoziesios    |                                       | lados(ados)                           | e doziecijos                          | jagacjada.                            | (orioriori | nejorijosijo | sjekjonjenjes                             | iedodosiosia                                     | ados(ociosias)  |

|------------|----------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------|--------------|-------------------------------------------|--------------------------------------------------|-----------------|

| OSC:       | punununu       | punununu                              | pununuru                              | ww.                                   | yndhumum.                             | inon indi  | upunun.      | ing ang ang ang ang ang ang ang ang ang a | nyununun                                         | upununun.       |

| 12.        | ) – Stalest by | 2000 ·····                            | · · · · · · · · · · · · · · · · · · · | , , , , , , , , , , , , , , , , , , , | 2                                     |            | 4<br>4       | * :<br>* :                                | 1                                                | nijjelennet 👘 🗍 |

| Vece ber   | (<br>(         | · · · · · · · · · · · · · · · · · · · | 2                                     | ,                                     | 2 1<br>2 1                            |            |              | × 3<br>× 3                                |                                                  |                 |

| ANAT USA   | <u>.</u>       |                                       |                                       |                                       | · · · · · · · · · · · · · · · · · · · | 1          | 5            |                                           | jegekonen on |                 |

|            |                |                                       |                                       | 3000000000<br>:                       | 9770a                                 |            | ····à·····   |                                           |                                                  |                 |

| 340.041    | ;<br>;         |                                       | ;                                     |                                       |                                       |            |              | ······                                    |                                                  | ····\$          |

| l          |                |                                       |                                       |                                       | <                                     |            | Affecter 33  | a saillean saon                           | Ge∰CR€C →                                        | ······<br>* :   |

| Mada 31 Ma | SECENSION      | Deste di Fact                         | Andre son SVAR                        | E Ros de la const                     |                                       |            | *            |                                           | ,                                                | ,               |

### FIGURE 20-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

## 25.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction, with the TBLPTR pointing to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File    | Name     | Bit 7 | Bit 6 | Bit 5                | Bit 4   | Bit 3                | Bit 2   | Bit 1   | Bit 0   | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|----------------------|---------|----------------------|---------|---------|---------|-----------------------------------|

| 300000h | CONFIG1L |       | _     | USBDIV               | CPUDIV1 | CPUDIV0              | PLLDIV2 | PLLDIV1 | PLLDIV0 | 00 0000                           |

| 300001h | CONFIG1H | IESO  | FCMEN | —                    | _       | FOSC3                | FOSC2   | FOSC1   | FOSC0   | 00 0101                           |

| 300002h | CONFIG2L | _     | _     | VREGEN               | BORV1   | BORV0                | BOREN1  | BOREN0  | PWRTEN  | 01 1111                           |

| 300003h | CONFIG2H | _     | _     | _                    | WDTPS3  | WDTPS2               | WDTPS1  | WDTPS0  | WDTEN   | 1 1111                            |

| 300005h | CONFIG3H | MCLRE | _     | _                    | _       | _                    | LPT1OSC | PBADEN  | CCP2MX  | 1011                              |

| 300006h | CONFIG4L | DEBUG | XINST | ICPRT <sup>(3)</sup> | _       | _                    | LVP     |         | STVREN  | 1001-1                            |

| 300008h | CONFIG5L | _     |       | _                    |         | CP3 <sup>(1)</sup>   | CP2     | CP1     | CP0     | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | _                    | _       | _                    | —       | —       | _       | 11                                |

| 30000Ah | CONFIG6L | _     | _     | —                    | _       | WRT3 <sup>(1)</sup>  | WRT2    | WRT1    | WRT0    | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC                 | _       | _                    | —       |         | _       | 111                               |

| 30000Ch | CONFIG7L | —     | _     | —                    | _       | EBTR3 <sup>(1)</sup> | EBTR2   | EBTR1   | EBTR0   | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | —                    | _       | —                    | —       | —       | _       | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0                 | REV4    | REV3                 | REV2    | REV1    | REV0    | ×××× ×××××(2)                     |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8                 | DEV7    | DEV6                 | DEV5    | DEV4    | DEV3    | 0001 0010(2)                      |

#### TABLE 25-1: CONFIGURATION BITS AND DEVICE IDs

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented in PIC18FX455 devices; maintain this bit set.

2: See Register 25-13 and Register 25-14 for DEVID values. DEVID registers are read-only and cannot be programmed by the user.

3: Available only on PIC18F4455/4550 devices in 44-pin TQFP packages. Always leave this bit clear in all other devices.

## REGISTER 25-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0          | U-0                         | R/P-0                             | R/P-1                | R/P-1                    | R/P-1                 | R/P-1                 | R/P-1                 |

|--------------|-----------------------------|-----------------------------------|----------------------|--------------------------|-----------------------|-----------------------|-----------------------|

| _            | _                           | VREGEN                            | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup>     | BOREN1 <sup>(2)</sup> | BOREN0 <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7        | ŀ                           |                                   | •                    |                          |                       | •                     | bit 0                 |

|              |                             |                                   |                      |                          |                       |                       |                       |

| Legend:      |                             |                                   |                      |                          |                       |                       |                       |

| R = Readab   | le bit                      | P = Program                       | nable bit            | U = Unimpler             | nented bit, read      | l as '0'              |                       |

| -n = Value w | hen device is un            | orogrammed                        |                      | u = Unchang              | ed from progran       | nmed state            |                       |

|              |                             |                                   |                      |                          |                       |                       |                       |

| bit 7-6      | Unimplemen                  | ted: Read as '                    | 0'                   |                          |                       |                       |                       |

| bit 5        | VREGEN: US                  | B Internal Volt                   | age Regulato         | r Enable bit             |                       |                       |                       |

|              |                             | age regulator e                   |                      |                          |                       |                       |                       |

|              |                             | age regulator d                   |                      |                          |                       |                       |                       |

| bit 4-3      | BORV1:BOR                   | V0: Brown-out                     | Reset Voltage        | e bits <sup>(1)</sup>    |                       |                       |                       |

|              | 11 <b>= Minimun</b>         | n setting                         |                      |                          |                       |                       |                       |

|              | •                           |                                   |                      |                          |                       |                       |                       |

|              | •                           |                                   |                      |                          |                       |                       |                       |

|              | 00 <b>= Maximu</b>          | m setting                         |                      |                          |                       |                       |                       |

| bit 2-1      | BOREN1:BO                   | REN0: Brown-                      | out Reset Ena        | able bits <sup>(2)</sup> |                       |                       |                       |

|              | 11 = Brown-c                | out Reset enab                    | led in hardwai       | re only (SBOR            | EN is disabled)       |                       |                       |

|              |                             |                                   |                      | •                        | abled in Sleep r      | •                     | N is disabled)        |

|              |                             | out Reset enab<br>out Reset disab |                      |                          | re (SBOREN is         | enabled)              |                       |

| bit 0        |                             | ower-up Timer                     |                      | Te and soltwar           | e                     |                       |                       |

|              | 1 = PWRT dis                | •                                 |                      |                          |                       |                       |                       |

|              | 1 = PWRT dis<br>0 = PWRT en |                                   |                      |                          |                       |                       |                       |

|              |                             |                                   |                      |                          |                       |                       |                       |

| Note 1: S    | ee Section 28.0             | "Electrical Ch                    | aracteristics        | " for the specif         | ications.             |                       |                       |

**2:** The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

## REGISTER 25-7: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| U-0                       | U-0 | U-0           | U-0 | R/C-1              | R/C-1            | R/C-1    | R/C-1 |

|---------------------------|-----|---------------|-----|--------------------|------------------|----------|-------|

| —                         | —   | —             | —   | CP3 <sup>(1)</sup> | CP2              | CP1      | CP0   |

| bit 7                     |     |               |     |                    |                  |          | bit 0 |

|                           |     |               |     |                    |                  |          |       |

|                           |     |               |     |                    |                  |          |       |

| Legend:                   |     |               |     |                    |                  |          |       |

| Legend:<br>R = Readable I | bit | C = Clearable | bit | U = Unimplem       | nented bit, reac | l as '0' |       |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | CP3: Code Protection bit <sup>(1)</sup>                                                                                        |

|         | <ul> <li>1 = Block 3 (006000-007FFFh) is not code-protected</li> <li>0 = Block 3 (006000-007FFFh) is code-protected</li> </ul> |

| bit 2   | CP2: Code Protection bit                                                                                                       |

|         | <ul> <li>1 = Block 2 (004000-005FFFh) is not code-protected</li> <li>0 = Block 2 (004000-005FFFh) is code-protected</li> </ul> |

| bit 1   | CP1: Code Protection bit                                                                                                       |

|         | <ul><li>1 = Block 1 (002000-003FFFh) is not code-protected</li><li>0 = Block 1 (002000-003FFFh) is code-protected</li></ul>    |

| bit 0   | CP0: Code Protection bit                                                                                                       |

|         | 1 = Block 0 (000800-001FFFh) is not code-protected<br>0 = Block 0 (000800-001FFFh) is code-protected                           |

Note 1: Unimplemented in PIC18FX455 devices; maintain this bit set.

## REGISTER 25-8: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | СРВ   | —   | _   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                      |                   |                                     |

|------------------------------|-------------------|-------------------------------------|

| R = Readable bit             | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is un | programmed        | u = Unchanged from programmed state |

| bit 7   | CPD: Data EEPROM Code Protection bit                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Data EEPROM is not code-protected                                                                                                |

|         | 0 = Data EEPROM is code-protected                                                                                                    |

| bit 6   | CPB: Boot Block Code Protection bit                                                                                                  |

|         | <ul> <li>1 = Boot block (000000-0007FFh) is not code-protected</li> <li>0 = Boot block (000000-0007FFh) is code-protected</li> </ul> |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                           |

| BNOV                                                                       | Branch if N                                                            | Not Overflow                                                                        |                                                                        | BNZ          |                                                            | Branch if I                                                              | Not Zero                                                                            |                                         |  |  |

|----------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| Syntax:                                                                    | BNOV n                                                                 |                                                                                     |                                                                        | Synta        | ax:                                                        | BNZ n                                                                    |                                                                                     |                                         |  |  |

| Operands:                                                                  | -128 ≤ n ≤ ′                                                           | 127                                                                                 |                                                                        | Oper         | ands:                                                      | -128 ≤ n ≤                                                               | $-128 \le n \le 127$                                                                |                                         |  |  |

| Operation:                                                                 |                                                                        | if Overflow bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                           |                                                                        | Oper         | ation:                                                     |                                                                          | if Zero bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                               |                                         |  |  |

| Status Affected:                                                           | None                                                                   |                                                                                     | Statu                                                                  | s Affected:  | None                                                       |                                                                          |                                                                                     |                                         |  |  |

| Encoding:                                                                  | 1110 0101 nnnn nnnn                                                    |                                                                                     | Enco                                                                   | ding:        | 1110                                                       | 0001 nr                                                                  | inn nnnn                                                                            |                                         |  |  |

| Description:                                                               | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | , then the Description:<br>Imber '2n' is<br>the PC will have<br>e next |              | ription:                                                   | will branch.<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement nun<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | nber '2n' is<br>ne PC will have<br>next |  |  |

| Words:                                                                     | 1                                                                      |                                                                                     |                                                                        | Word         | ls:                                                        | 1                                                                        |                                                                                     |                                         |  |  |

| Cycles:                                                                    | 1(2)                                                                   |                                                                                     |                                                                        | Cycle        | es:                                                        | 1(2)                                                                     |                                                                                     |                                         |  |  |

| Q Cycle Activity<br>If Jump:                                               |                                                                        |                                                                                     |                                                                        | Q C<br>If Ju | ycle Activity:<br>mp:                                      |                                                                          |                                                                                     |                                         |  |  |

| Q1                                                                         | Q2                                                                     | Q3                                                                                  | Q4                                                                     |              | Q1                                                         | Q2                                                                       | Q3                                                                                  | Q4                                      |  |  |

| Decode                                                                     | Read literal<br>'n'                                                    | Process<br>Data                                                                     | Write to PC                                                            |              | Decode                                                     | Read literal<br>'n'                                                      | Process<br>Data                                                                     | Write to PC                             |  |  |

| No<br>operation                                                            | No<br>operation                                                        | No<br>operation                                                                     | No<br>operation                                                        |              | No<br>operation                                            | No<br>operation                                                          | No<br>operation                                                                     | No<br>operation                         |  |  |

| If No Jump:                                                                |                                                                        |                                                                                     |                                                                        | lf No        | o Jump:                                                    |                                                                          |                                                                                     |                                         |  |  |

| Q1                                                                         | Q2                                                                     | Q3                                                                                  | Q4                                                                     |              | Q1                                                         | Q2                                                                       | Q3                                                                                  | Q4                                      |  |  |

| Decode                                                                     | Read literal<br>'n'                                                    | Process<br>Data                                                                     | No<br>operation                                                        |              | Decode                                                     | Read literal<br>'n'                                                      | Process<br>Data                                                                     | No<br>operation                         |  |  |

| Example:<br>Before Instr<br>PC<br>After Instruc<br>If Over<br>P<br>If Over | = ad<br>tion<br>flow = 0;<br>C = ad                                    | BNOV Jump<br>dress (HERE<br>dress (Jump                                             | )                                                                      |              | nple:<br>PC<br>PC<br>After Instructi<br>If Zero<br>If Zero | = ad<br>on<br>= 0;                                                       | BNZ Jump<br>dress (HERE                                                             | )                                       |  |  |

| BRA         |                                          | onal Bran                                                                                | ch                                                  |                                   |              |  |  |  |

|-------------|------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|--------------|--|--|--|

| Synta       | ax:                                      | BRA n                                                                                    |                                                     |                                   |              |  |  |  |

| Oper        | ands:                                    | -1024 ≤ n ≤                                                                              | 1023                                                |                                   |              |  |  |  |

| Oper        | ation:                                   | (PC) + 2 + 2                                                                             | $2n \rightarrow PC$                                 |                                   |              |  |  |  |

| Statu       | s Affected:                              | None                                                                                     |                                                     |                                   |              |  |  |  |

| Enco        | ding:                                    | 1101                                                                                     | 0nnn                                                | nnnn                              | nnnn         |  |  |  |

| Desc        | ription:                                 | Add the 2's<br>the PC. Sin<br>incrementer<br>instruction,<br>PC + 2 + 2r<br>two-cycle in | ce the PC<br>d to fetch<br>the new a<br>n. This ins | will have<br>the next<br>ddress v | e<br>vill be |  |  |  |

| Word        | ls:                                      | 1                                                                                        | 1                                                   |                                   |              |  |  |  |

| Cycle       | es:                                      | 2                                                                                        | 2                                                   |                                   |              |  |  |  |

| QC          | ycle Activity:                           |                                                                                          |                                                     |                                   |              |  |  |  |

|             | Q1                                       | Q2                                                                                       | Q3                                                  |                                   | Q4           |  |  |  |

|             | Decode                                   | Read literal<br>'n'                                                                      | Proces<br>Data                                      | s Wr                              | ite to PC    |  |  |  |

|             | No                                       | No                                                                                       | No                                                  |                                   | No           |  |  |  |

|             | operation                                | operation                                                                                | operatio                                            | on op                             | peration     |  |  |  |

| <u>Exan</u> | nple:                                    | HERE                                                                                     | BRA J                                               | ump                               |              |  |  |  |

|             | Before Instruc<br>PC<br>After Instructio | = ad                                                                                     | dress (HI                                           | ERE)                              |              |  |  |  |

|             | PC                                       | = ad                                                                                     | dress (J                                            | ump)                              |              |  |  |  |

| BSF                                                       | Bit Set f                                                                                                                                                                           |                                                                                                                               |                                                                                                              |                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Syntax:                                                   | BSF f, b {                                                                                                                                                                          | ,a}                                                                                                                           |                                                                                                              |                                                                           |

| Operands:                                                 | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                  |                                                                                                                               |                                                                                                              |                                                                           |

| Operation:                                                | $1 \rightarrow f \le b >$                                                                                                                                                           |                                                                                                                               |                                                                                                              |                                                                           |

| Status Affected:                                          | None                                                                                                                                                                                |                                                                                                                               |                                                                                                              |                                                                           |

| Encoding:                                                 | 1000                                                                                                                                                                                | bbba                                                                                                                          | ffff                                                                                                         | ffff                                                                      |

| Description:                                              | Bit 'b' in reg<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank (<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 26<br>Bit-Oriente<br>Literal Offs | he Acces<br>he BSR i<br>(default).<br>nd the ex<br>ed, this i<br>Literal Of<br>Literal Of<br>ever f ≤<br>.2.3 "By<br>d Instru | ss Bank is<br>s used to a<br>ktended in<br>nstruction<br>ffset Addre<br>95 (5Fh).<br>te-Oriente<br>ctions in | select the<br>struction<br>operates<br>essing<br>See<br>ed and<br>Indexed |

| Words:                                                    | 1                                                                                                                                                                                   |                                                                                                                               |                                                                                                              |                                                                           |

| Cycles:                                                   | 1                                                                                                                                                                                   |                                                                                                                               |                                                                                                              |                                                                           |

| Q Cycle Activity:                                         |                                                                                                                                                                                     |                                                                                                                               |                                                                                                              |                                                                           |

| Q1                                                        | Q2                                                                                                                                                                                  | Q3                                                                                                                            |                                                                                                              | Q4                                                                        |