#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2550-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F2455 PIC18LF2455

- PIC18F2550

PIC18LF2550

- PIC18F4455 PIC18LF4455

- PIC18F4550 PIC18LF4550

This family of devices offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Enhanced Flash program memory. In addition to these features, the PIC18F2455/2550/4455/4550 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

# 1.1 New Core Features

### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2455/2550/4455/4550 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4%, of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 28.0 "Electrical Characteristics" for values.

### 1.1.2 UNIVERSAL SERIAL BUS (USB)

Devices in the PIC18F2455/2550/4455/4550 family incorporate a fully featured Universal Serial Bus communications module that is compliant with the USB Specification Revision 2.0. The module supports both low-speed and full-speed communication for all supported data transfer types. It also incorporates its own on-chip transceiver and 3.3V regulator and supports the use of external transceivers and voltage regulators.

## 1.1.3 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2455/2550/4455/4550 family offer twelve different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes using crystals or ceramic resonators.

- Four External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- An internal oscillator block which provides an 8 MHz clock (±2% accuracy) and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of 6 user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. This option frees an oscillator pin for use as an additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and External Oscillator modes, which allows a wide range of clock speeds from 4 MHz to 48 MHz.

- Asynchronous dual clock operation, allowing the USB module to run from a high-frequency oscillator while the rest of the microcontroller is clocked from an internal low-power oscillator.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

| Dia Nama                                                       | Pin Number |     |      | Pin Buffer                  | Departuration                        |                                                                                                                                                                                    |

|----------------------------------------------------------------|------------|-----|------|-----------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                       | PDIP       | QFN | TQFP | Туре                        | Туре                                 | Description                                                                                                                                                                        |

| RB0/AN12/INT0/<br>FLT0/SDI/SDA<br>RB0                          | 33         | 9   | 8    | I/O                         | TTL                                  | PORTB is a bidirectional I/O port. PORTB can be softwa<br>programmed for internal weak pull-ups on all inputs.<br>Digital I/O.                                                     |

| AN12<br>INTO<br>FLTO<br>SDI<br>SDA                             |            |     |      | 0<br>  <br>  1<br>  0       | Analog<br>ST<br>ST<br>ST<br>ST<br>ST | Analog input 12.<br>External interrupt 0.<br>Enhanced PWM Fault input (ECCP1 module).<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                               |

| RB1/AN10/INT1/SCK/<br>SCL<br>RB1<br>AN10<br>INT1<br>SCK<br>SCL | 34         | 10  | 9    | I/O<br>I<br>I<br>I/O<br>I/O | TTL<br>Analog<br>ST<br>ST<br>ST      | Digital I/O.<br>Analog input 10.<br>External interrupt 1.<br>Synchronous serial clock input/output for SPI mode<br>Synchronous serial clock input/output for I <sup>2</sup> C mode |

| RB2/AN8/INT2/VMO<br>RB2<br>AN8<br>INT2<br>VMO                  | 35         | 11  | 10   | I/O<br>I<br>I<br>O          | TTL<br>Analog<br>ST<br>—             | Digital I/O.<br>Analog input 8.<br>External interrupt 2.<br>External USB transceiver VMO output.                                                                                   |

| RB3/AN9/CCP2/VPO<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup><br>VPO   | 36         | 12  | 11   | I/O<br>I<br>I/O<br>O        | TTL<br>Analog<br>ST<br>—             | Digital I/O.<br>Analog input 9.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>External USB transceiver VPO output.                                                           |

| RB4/AN11/KBI0/CSSPP<br>RB4<br>AN11<br>KBI0<br>CSSPP            | 37         | 14  | 14   | I/O<br>I<br>I<br>O          | TTL<br>Analog<br>TTL<br>—            | Digital I/O.<br>Analog input 11.<br>Interrupt-on-change pin.<br>SPP chip select control output.                                                                                    |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                             | 38         | 15  | 15   | I/O<br>I<br>I/O             | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                                                                                              |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                             | 39         | 16  | 16   | I/O<br>I<br>I/O             | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock p                                                                                       |

| RB7/KBI3/PGD<br>RB7<br>KBI3                                    | 40         | 17  | 17   | I/O<br>I<br>I/O             | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pi                                                                                       |

# TABLE 1-3: PIC18F4455/4550 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared.

2: Default assignment for CCP2 when CCP2MX Configuration bit is set.

**3:** These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

# 3.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer; the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between the PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended.

This mode is entered by setting SCS1 to '1'. Although it is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 3-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST.

If the IRCF bits were previously at a non-zero value or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set.

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

# 5.2 PIC18 Instruction Cycle

### 5.2.1 CLOCKING SCHEME

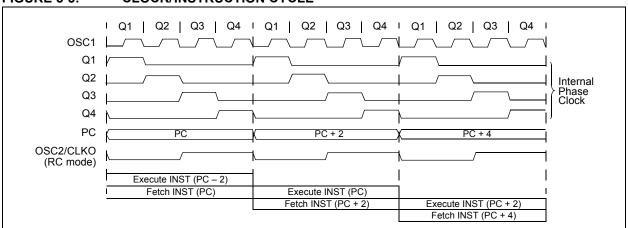

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the Instruction Register (IR) during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-3.

## 5.2.2 INSTRUCTION FLOW/PIPELINING

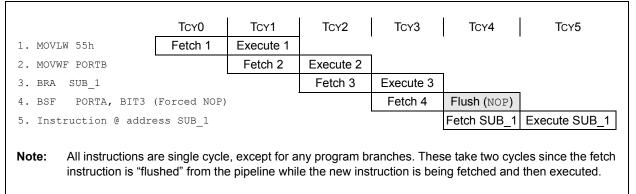

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 5-3: CLOCK/INSTRUCTION CYCLE

## EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

## 5.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on it stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by '1' afterwards

- POSTINC: accesses the FSR value, then automatically increments it by '1' afterwards

- PREINC: increments the FSR value by '1', then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register, from FFh to 00h, carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

# 5.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of INDF1, using INDF0 as an operand, will return 00h. Attempts to write to INDF1, using INDF0 as the operand, will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 32 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A Bulk Erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

## 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

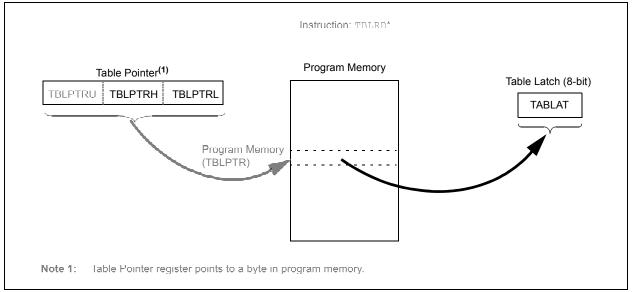

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.5 "Writing to Flash Program Memory"**. Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 6-1: TABLE READ OPERATION

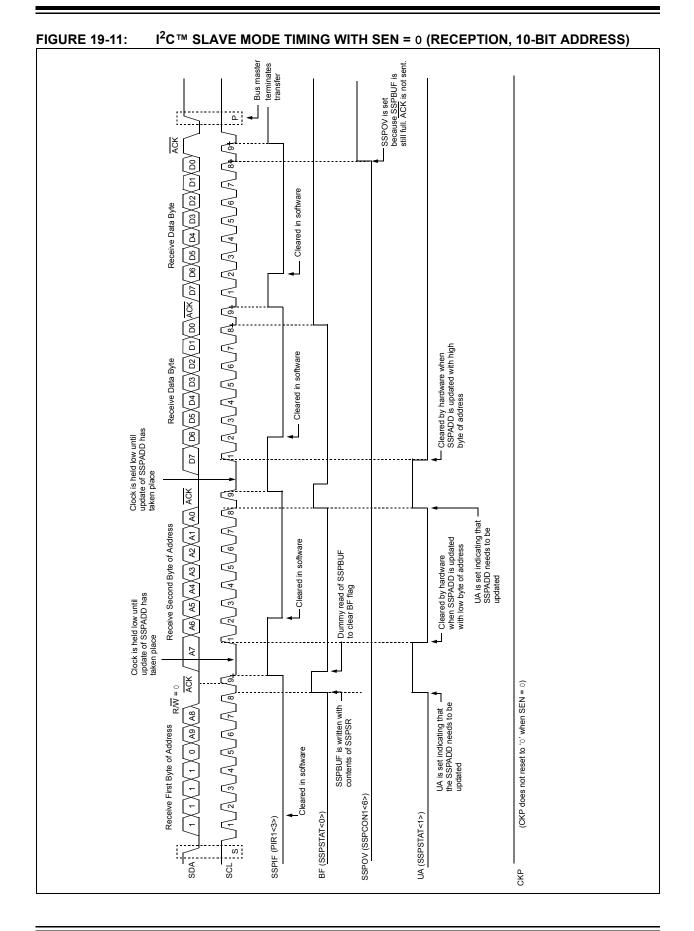

### 19.4.3.2 Address Masking

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which makes it possible to Acknowledge up to 31 addresses in 7-bit mode and up to 63 addresses in 10-bit mode (see Example 19-3).

The  $l^2C$  Slave behaves the same way whether address masking is used or not. However, when address masking is used, the  $l^2C$  slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking SSPBUF.

In 7-Bit Address mode, address mask bits ADMSK<5:1> (SSPCON2<5:1>) mask the corresponding address bits in the SSPADD register. For any ADMSK bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

In 10-Bit Address mode, bits ADMSK<5:2> mask the corresponding address bits in the SSPADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPADD<1:0>). For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SSPADD<n> = x). Also note that although in 10-Bit Addressing mode, the upper address bits reuse part of the SSPADD register bits, the address mask bits do not interact with those bits. They only affect the lower address bits.

- Note 1: ADMSK1 masks the two Least Significant bits of the address.

- The two Most Significant bits of the address are not affected by address masking.

# EXAMPLE 19-3: ADDRESS MASKING EXAMPLES

#### 7-bit addressing:

SSPADD<7:1> = A0h (1010000) (SSPADD<0> is assumed to be '0')

ADMSK<5:1> = 00111

Addresses Acknowledged : A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### 10-bit addressing:

SSPADD<7:0> = A0h (10100000) (The two MSbs of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

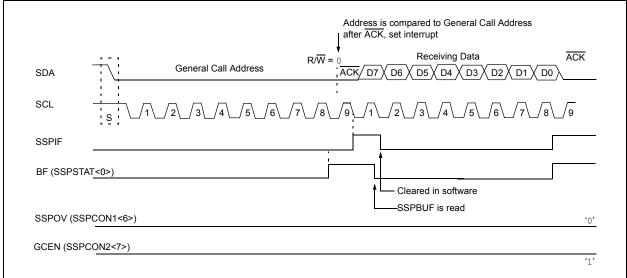

#### 19.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable (GCEN) bit is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware. If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 19-17).

# 20.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

The EUSART can be configured in the following modes:

- · Asynchronous (full-duplex) with:

- Auto-wake-up on Break signal

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT/SDO as an EUSART:

- SPEN bit (RCSTA<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be set (= 1)

| EUSARI | control  | WIII                   | automatically               |

|--------|----------|------------------------|-----------------------------|

|        | pin from | inpi                   | ut to output as             |

| )      |          | configure the pin from | configure the pin from inpu |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- · Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 20-1, Register 20-2 and Register 20-3, respectively.

| R/W-0                  | R/W-0                                      | R/W-0                                                               | R/W-0                                                   | R/W-0             | R-0              | R-0                             | R-x     |

|------------------------|--------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-------------------|------------------|---------------------------------|---------|

| SPEN                   | RX9                                        | SREN                                                                | CREN                                                    | ADDEN             | FERR             | OERR                            | RX9D    |

| bit 7                  |                                            |                                                                     | ·                                                       | · · · · · ·       |                  |                                 | bit     |

| Lonordi                |                                            |                                                                     |                                                         |                   |                  |                                 |         |

| Legend:<br>R = Readabl | a hit                                      | \// = \//ritabla                                                    | hit                                                     |                   | aantad hit raa   | d aa (0)                        |         |

|                        |                                            | W = Writable<br>'1' = Bit is se                                     |                                                         | -                 | nented bit, read |                                 | 0000    |

| -n = Value at          | PUR                                        | I = DILIS SE                                                        | L                                                       | '0' = Bit is clea | areu             | x = Bit is unkr                 | IOWI    |

| bit 7                  | SPEN: Seria                                | l Port Enable b                                                     | it                                                      |                   |                  |                                 |         |

|                        |                                            | rt enabled (con<br>rt disabled (hel                                 |                                                         | Г and TX/CK pir   | ns as serial po  | rt pins)                        |         |

| bit 6                  | <b>RX9:</b> 9-Bit R                        | eceive Enable                                                       | bit                                                     |                   |                  |                                 |         |

|                        |                                            | -bit reception<br>-bit reception                                    |                                                         |                   |                  |                                 |         |

| bit 5                  | SREN: Single                               | e Receive Ena                                                       | ble bit                                                 |                   |                  |                                 |         |

|                        | <u>Asynchronou</u><br>Don't care.          | <u>is mode:</u>                                                     |                                                         |                   |                  |                                 |         |

|                        | 1 = Enables<br>0 = Disables                | mode – Maste<br>single receive<br>single receive<br>ared after rece |                                                         | lete.             |                  |                                 |         |

|                        |                                            | mode – Slave                                                        |                                                         |                   |                  |                                 |         |

| bit 4                  | CREN: Conti                                | nuous Receive                                                       | Enable bit                                              |                   |                  |                                 |         |

|                        | Asynchronou<br>1 = Enables<br>0 = Disables | receiver                                                            |                                                         |                   |                  |                                 |         |

|                        | Synchronous                                | mode:                                                               |                                                         | ble bit CREN is   | cleared (CREN    | l overrides SRE                 | EN)     |

| bit 3                  |                                            | Iress Detect Er                                                     |                                                         |                   |                  |                                 |         |

|                        | Asynchronou<br>1 = Enables<br>0 = Disables | <u>is mode 9-bit (F</u><br>address detec                            | <u>RX9 = 1):</u><br>tion, enables i<br>ction, all bytes |                   |                  | buffer when R<br>be used as par |         |

| bit 2                  |                                            | error (can be u                                                     | pdated by rea                                           | ding RCREG re     | egister and rec  | eiving next valic               | l byte) |

| bit 1                  | 0 = No framir<br>OERR: Over                | -                                                                   |                                                         |                   |                  |                                 |         |

|                        |                                            | error (can be c                                                     | leared by clea                                          | ring bit CREN)    |                  |                                 |         |

| bit 0                  |                                            | t of Received E                                                     | Data                                                    |                   |                  |                                 |         |

|                        |                                            |                                                                     |                                                         |                   | alculated by u   |                                 |         |

# REGISTER 20-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

# 20.3 EUSART Synchronous Master Mode

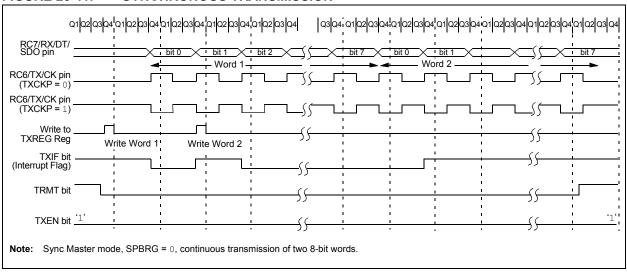

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line.

Clock polarity (CK) is selected with the TXCKP bit (BAUDCON<4>). Setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. Data polarity (DT) is selected with the RXDTP bit (BAUDCON<5>). Setting RXDTP sets the Idle state on DT as high, while clearing the bit sets the Idle state as low. DT is sampled when CK returns to its idle state. This option is provided to support Microwire devices with this module.

#### 20.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 20-11: SYNCHRONOUS TRANSMISSION

# 21.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option to use an automatically determined acquisition time.

Acquisition time may be set with the ACQT2:ACQT0 bits (ADCON2<5:3>) which provide a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition is selected when ACQT2:ACQT0 = 000. When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This option is also the default Reset state of the ACQT2:ACQT0 bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

# 21.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible but greater than the minimum TAD (see parameter 130 in Table 28-29 for more information).

Table 21-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| AD Clock          | AD Clock Source (TAD) |                         |  |  |  |

|-------------------|-----------------------|-------------------------|--|--|--|

| Operation         | ADCS2:ADCS0           | Maximum Fosc            |  |  |  |

| 2 Tosc            | 000                   | 2.50 MHz                |  |  |  |

| 4 Tosc            | 100                   | 5.00 MHz                |  |  |  |

| 8 Tosc            | 001                   | 10.00 MHz               |  |  |  |

| 16 Tosc           | 101                   | 20.00 MHz               |  |  |  |

| 32 Tosc           | 010                   | 40.00 MHz               |  |  |  |

| 64 Tosc           | 110                   | 48.00 MHz               |  |  |  |

| RC <sup>(2)</sup> | x11                   | 1.00 MHz <sup>(1)</sup> |  |  |  |

## TABLE 21-1: TAD vs. DEVICE OPERATING FREQUENCIES

Note 1: The RC source has a typical TAD time of  $2.5 \ \mu s$ .

2: For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or a Fosc divider should be used instead. Otherwise, the A/D accuracy may be out of specification.

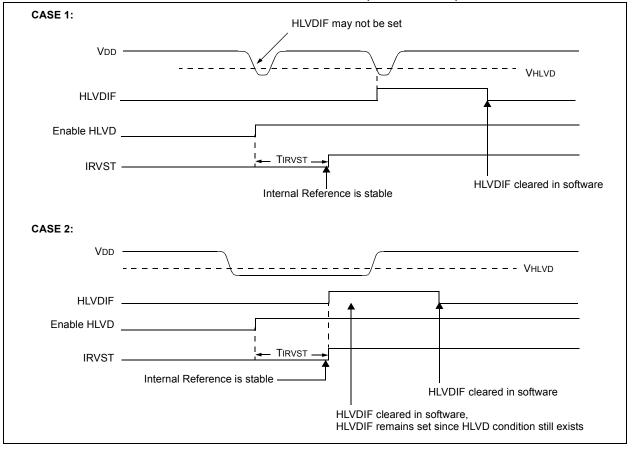

# 24.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- 1. Disable the module by clearing the HLVDEN bit (HLVDCON<4>).

- 2. Write the value to the HLVDL3:HLVDL0 bits that selects the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 4. Enable the HLVD module by setting the HLVDEN bit.

- Clear the HLVD Interrupt Flag, HLVDIF (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt, if interrupts are desired, by setting the HLVDIE and GIE/GIEH bits (PIE2<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

# 24.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022 (Section 28.2 "DC Characteristics"). Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

# 24.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420 (see Table 28-6 in **Section 28.0 "Electrical Characteristics"**), may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36 (Table 28-12).

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval. Refer to Figure 24-2 or Figure 24-3.

# 25.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction, with the TBLPTR pointing to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File    | Name     | Bit 7 | Bit 6 | Bit 5                | Bit 4   | Bit 3                | Bit 2   | Bit 1   | Bit 0   | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|----------------------|---------|----------------------|---------|---------|---------|-----------------------------------|

| 300000h | CONFIG1L |       | _     | USBDIV               | CPUDIV1 | CPUDIV0              | PLLDIV2 | PLLDIV1 | PLLDIV0 | 00 0000                           |

| 300001h | CONFIG1H | IESO  | FCMEN | —                    | _       | FOSC3                | FOSC2   | FOSC1   | FOSC0   | 00 0101                           |

| 300002h | CONFIG2L | _     | _     | VREGEN               | BORV1   | BORV0                | BOREN1  | BOREN0  | PWRTEN  | 01 1111                           |

| 300003h | CONFIG2H | _     | _     | _                    | WDTPS3  | WDTPS2               | WDTPS1  | WDTPS0  | WDTEN   | 1 1111                            |

| 300005h | CONFIG3H | MCLRE | _     | _                    | _       | _                    | LPT1OSC | PBADEN  | CCP2MX  | 1011                              |

| 300006h | CONFIG4L | DEBUG | XINST | ICPRT <sup>(3)</sup> | _       | _                    | LVP     |         | STVREN  | 1001-1                            |

| 300008h | CONFIG5L | _     |       | _                    |         | CP3 <sup>(1)</sup>   | CP2     | CP1     | CP0     | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | _                    | _       | _                    | —       | _       | _       | 11                                |

| 30000Ah | CONFIG6L | —     | _     | —                    | _       | WRT3 <sup>(1)</sup>  | WRT2    | WRT1    | WRT0    | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC                 | _       | _                    | —       |         | _       | 111                               |

| 30000Ch | CONFIG7L | —     | _     | —                    | _       | EBTR3 <sup>(1)</sup> | EBTR2   | EBTR1   | EBTR0   | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | —                    | _       | —                    | —       | _       | _       | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0                 | REV4    | REV3                 | REV2    | REV1    | REV0    | ×××× ×××××(2)                     |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8                 | DEV7    | DEV6                 | DEV5    | DEV4    | DEV3    | 0001 0010(2)                      |

### TABLE 25-1: CONFIGURATION BITS AND DEVICE IDs

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented in PIC18FX455 devices; maintain this bit set.

2: See Register 25-13 and Register 25-14 for DEVID values. DEVID registers are read-only and cannot be programmed by the user.

3: Available only on PIC18F4455/4550 devices in 44-pin TQFP packages. Always leave this bit clear in all other devices.

# 26.0 INSTRUCTION SET SUMMARY

PIC18F2455/2550/4455/4550 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of eight new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

# 26.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits) but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 26-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 26-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 26-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The instruction set summary, shown in Table 26-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 26.1.1 "Standard Instruction Set" provides a description of each instruction.

| INCFSZ Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |                                                     |                    |                          |                       |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------|--------------------|--------------------------|-----------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ax:                   | INCFSZ f                                            | INCFSZ f {,d {,a}} |                          |                       |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ands:                 | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | d ∈ [0,1]          |                          |                       |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ation:                | (f) + 1 $\rightarrow$ de skip if resul              |                    |                          |                       |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | s Affected:           | None                                                |                    |                          |                       |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | oding:                | 0011                                                | 11da               | ffff                     | ffff                  |  |  |  |  |

| Description:<br>The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. (default)<br>If the result is '0', the next instruction,<br>which is already fetched, is discarded<br>and a NOP is executed instead, makin<br>it a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selecter<br>If 'a' is '1', the BSR is used to select th<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operater<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexee<br>Literal Offset Mode" for details. |                       |                                                     |                    |                          |                       |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ls:                   | 1                                                   |                    |                          |                       |  |  |  |  |

| Cycle<br>Q C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | es:<br>ycle Activity: | 1(2)<br><b>Note:</b> 3 cy<br>by a                   |                    | p and foll<br>nstruction |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q1                    | Q2                                                  | Q3                 |                          | Q4                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Decode                | Read<br>register 'f'                                | Proce:<br>Data     |                          | Vrite to<br>stination |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ip:                   |                                                     |                    |                          |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q1                    | Q2                                                  | Q3                 |                          | Q4                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                    | No                                                  | No                 |                          | No                    |  |  |  |  |

| lfek                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation             | operation                                           |                    | operation operation      |                       |  |  |  |  |

| 11 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q1                    | Q2                                                  | Q3                 |                          |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                    | No                                                  | No                 |                          | No                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | operation             | operation                                           | operati            | on op                    | peration              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                    | No                                                  | No                 |                          | No                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | operation             | operation                                           | operati            | on op                    | peration              |  |  |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CNT,                  | 1, 0                                                |                    |                          |                       |  |  |  |  |

| Before Instruction<br>PC = Address (HERE)<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |                                                     |                    |                          |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CNT<br>If CNT<br>PC   | = CNT +<br>= 0;<br>= Address                        |                    | )                        |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | If CNT<br>PC          | ≠ 0;<br>= Address                                   | S (NZER            | 0)                       |                       |  |  |  |  |

| INFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NZ                                       | Increment                                           | f, Skip if Not                                                            | 0                     |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ax:                                      | INFSNZ f                                            | {,d {,a}}                                                                 |                       |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ands:                                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | $d \in [0,1]$                                                             |                       |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ation:                                   | (f) + 1 $\rightarrow$ de skip if result             |                                                                           |                       |  |  |  |  |