Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4455-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome                                        | Pi         | n Numl          | ber   | Pin Buffer    | Description       |                                                                                                           |

|-------------------------------------------------|------------|-----------------|-------|---------------|-------------------|-----------------------------------------------------------------------------------------------------------|

| Pin Name                                        | PDIP       | QFN             | TQFP  | Туре          | Туре              | Description                                                                                               |

|                                                 |            |                 |       |               |                   | PORTE is a bidirectional I/O port.                                                                        |

| RE0/AN5/CK1SPP<br>RE0<br>AN5<br>CK1SPP          | 8          | 25              | 25    | I/O<br>I<br>O | ST<br>Analog      | Digital I/O.<br>Analog input 5.<br>SPP clock 1 output.                                                    |

| RE1/AN6/CK2SPP<br>RE1<br>AN6<br>CK2SPP          | 9          | 26              | 26    | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 6.<br>SPP clock 2 output.                                                    |

| RE2/AN7/OESPP<br>RE2<br>AN7<br>OESPP            | 10         | 27              | 27    | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 7.<br>SPP output enable output.                                              |

| RE3                                             | _          | _               | _     |               | _                 | See MCLR/VPP/RE3 pin.                                                                                     |

| Vss                                             | 12, 31     | 6, 30,<br>31    | 6, 29 | Ρ             | _                 | Ground reference for logic and I/O pins.                                                                  |

| Vdd                                             | 11, 32     | 7, 8,<br>28, 29 | 7, 28 | Р             | —                 | Positive supply for logic and I/O pins.                                                                   |

| Vusb                                            | 18         | 37              | 37    | Р             | —                 | Internal USB 3.3V voltage regulator output, positive supply for the USB transceiver.                      |

| NC/ICCK/ICPGC <sup>(3)</sup><br>ICCK<br>ICPGC   | -          | —               | 12    | I/O<br>I/O    | ST<br>ST          | No Connect or dedicated ICD/ICSP™ port clock.<br>In-Circuit Debugger clock.<br>ICSP programming clock.    |

| NC/ICDT/ICPGD <sup>(3)</sup><br>ICDT<br>ICPGD   | -          | —               | 13    | I/O<br>I/O    | ST<br>ST          | No Connect or dedicated ICD/ICSP port clock.<br>In-Circuit Debugger data.<br>ICSP programming data.       |

| NC/ICRST/ICVPP <sup>(3)</sup><br>ICRST<br>ICVPP | -          |                 | 33    | I<br>P        | _                 | No Connect or dedicated ICD/ICSP port Reset.<br>Master Clear (Reset) input.<br>Programming voltage input. |

| NC/ICPORTS <sup>(3)</sup><br>ICPORTS            | —          | —               | 34    | Ρ             | —                 | No Connect or 28-pin device emulation.<br>Enable 28-pin device emulation when connected<br>to Vss.        |

| NC                                              |            | 13              |       |               |                   | No Connect.                                                                                               |

| Legend: TTL = TTL o<br>ST = Schn<br>O = Outp    | nitt Trigg |                 |       | /IOS le       |                   | MOS = CMOS compatible input or output<br>= Input<br>= Power                                               |

#### TABLE 1-3: PIC18F4455/4550 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared.

2: Default assignment for CCP2 when CCP2MX Configuration bit is set.

**3:** These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

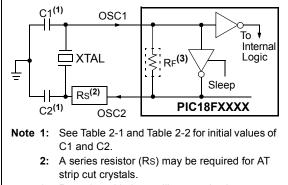

## 2.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In HS, HSPLL, XT and XTPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-2 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

| Note: | Use of a series cut crystal may give a fre-<br>quency out of the crystal manufacturer's |

|-------|-----------------------------------------------------------------------------------------|

|       | specifications.                                                                         |

#### FIGURE 2-2: CRYSTAL/CERAMIC RESONATOR OPERATION (XT, HS OR HSPLL CONFIGURATION)

3: RF varies with the oscillator mode chosen.

## TABLE 2-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| -    | Typical Capacitor Values Used: |                |                |  |  |  |  |  |  |

|------|--------------------------------|----------------|----------------|--|--|--|--|--|--|

| Mode | Freq                           | Freq OSC1 OSC2 |                |  |  |  |  |  |  |

| XT   | 4.0 MHz                        | 33 pF          | 33 pF          |  |  |  |  |  |  |

| HS   | 8.0 MHz<br>16.0 MHz            | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |  |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 2-2 for additional information.

| Resonators Used: |

|------------------|

| 4.0 MHz          |

| 8.0 MHz          |

| 16.0 MHz         |

When using ceramic resonators with frequencies above 3.5 MHz, HS mode is recommended over XT mode. HS mode may be used at any VDD for which the controller is rated. If HS is selected, the gain of the oscillator may overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of RS is  $330 \Omega$ .

### 3.0 POWER-MANAGED MODES

PIC18F2455/2550/4455/4550 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- · Sleep mode

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 3.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS1:SCS0 bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

### 3.1.1 CLOCK SOURCES

The SCS1:SCS0 bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock, as defined by the FOSC3:FOSC0 Configuration bits

- The secondary clock (the Timer1 oscillator)

- The internal oscillator block (for RC modes)

#### 3.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 3.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| TADLE 3-1. | E 3-1. FOWER-MANAGED MODES |            |         |             |                                                                                  |  |  |  |  |  |

|------------|----------------------------|------------|---------|-------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Mode -     | osco                       | CON<7,1:0> | Modul   | e Clocking  | Augilable Cleak and Casillater Source                                            |  |  |  |  |  |

|            | IDLEN <sup>(1)</sup>       | SCS1:SCS0  | CPU     | Peripherals | Available Clock and Oscillator Source                                            |  |  |  |  |  |

| Sleep      | 0                          | N/A        | Off     | Off         | None – all clocks are disabled                                                   |  |  |  |  |  |

| PRI_RUN    | N/A                        | 00         | Clocked | Clocked     | Primary – all oscillator modes.<br>This is the normal full-power execution mode. |  |  |  |  |  |

| SEC_RUN    | N/A                        | 01         | Clocked | Clocked     | Secondary – Timer1 oscillator                                                    |  |  |  |  |  |

| RC_RUN     | N/A                        | lx         | Clocked | Clocked     | Internal oscillator block <sup>(2)</sup>                                         |  |  |  |  |  |

| PRI_IDLE   | 1                          | 00         | Off     | Clocked     | Primary – all oscillator modes                                                   |  |  |  |  |  |

| SEC_IDLE   | 1                          | 01         | Off     | Clocked     | Secondary – Timer1 oscillator                                                    |  |  |  |  |  |

| RC_IDLE    | 1                          | lx         | Off     | Clocked     | Internal oscillator block <sup>(2)</sup>                                         |  |  |  |  |  |

TABLE 3-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

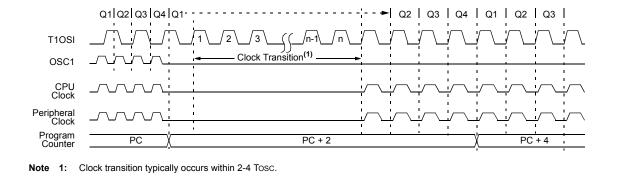

SEC\_RUN mode is entered by setting the SCS1:SCS0 bits to '01'. The device clock source is switched to the Timer1 oscillator (see Figure 3-1), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

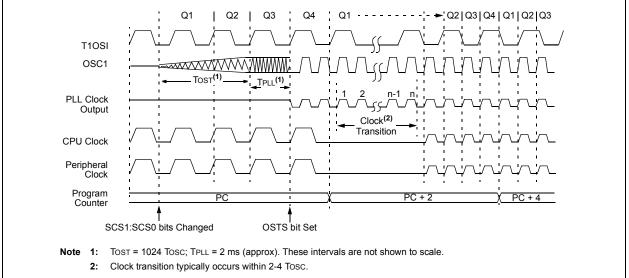

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS1:SCS0 bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result. On transitions from SEC\_RUN mode to PRI\_RUN, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-2). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

| File Name | Bit 7                                                                                                                                                                                                         | Bit 6          | Bit 5                 | Bit 4          | Bit 3          | Bit 2          | Bit 1           | Bit 0        | Value on<br>POR, BOR | Details<br>on page |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|----------------|----------------|----------------|-----------------|--------------|----------------------|--------------------|

| TOSU      | _                                                                                                                                                                                                             | _              | _                     | Top-of-Stack   | Upper Byte (T  | OS<20:16>)     |                 |              | 0 0000               | 53, 60             |

| TOSH      | Top-of-Stack                                                                                                                                                                                                  | High Byte (TO  | S<15:8>)              |                |                |                |                 |              | 0000 0000            | 53, 60             |

| TOSL      | Top-of-Stack                                                                                                                                                                                                  | Low Byte (TO   | 6<7:0>)               |                |                |                |                 |              | 0000 0000            | 53, 60             |

| STKPTR    | STKFUL                                                                                                                                                                                                        | STKUNF         | _                     | SP4            | SP3            | SP2            | SP1             | SP0          | 00-0 0000            | 53, 61             |

| PCLATU    | _                                                                                                                                                                                                             | -              | _                     | Holding Regi   | ster for PC<20 | :16>           | •               | •            | 0 0000               | 53, 60             |

| PCLATH    | Holding Regis                                                                                                                                                                                                 | ster for PC<15 | :8>                   |                |                |                |                 |              | 0000 0000            | 53, 60             |

| PCL       | PC Low Byte                                                                                                                                                                                                   | (PC<7:0>)      |                       |                |                |                |                 |              | 0000 0000            | 53, 60             |

| TBLPTRU   | —                                                                                                                                                                                                             | —              | bit 21 <sup>(1)</sup> | Program Mer    | nory Table Poi | nter Upper By  | te (TBLPTR<2    | 20:16>)      | 00 0000              | 53, 84             |

| TBLPTRH   | Program Men                                                                                                                                                                                                   | nory Table Poi | nter High Byte        | e (TBLPTR<15   | :8>)           |                |                 |              | 0000 0000            | 53, 84             |

| TBLPTRL   | Program Men                                                                                                                                                                                                   | nory Table Poi | nter Low Byte         | (TBLPTR<7:0    | )>)            |                |                 |              | 0000 0000            | 53, 84             |

| TABLAT    | AT Program Memory Table Latch                                                                                                                                                                                 |                |                       |                |                |                |                 |              | 0000 0000            | 53, 84             |

| PRODH     | Product Register High Byte                                                                                                                                                                                    |                |                       |                |                |                |                 |              | XXXX XXXX            | 53, 97             |

| PRODL     | Product Regi                                                                                                                                                                                                  | ster Low Byte  |                       |                |                |                |                 |              | XXXX XXXX            | 53, 97             |

| INTCON    | GIE/GIEH                                                                                                                                                                                                      | PEIE/GIEL      | TMR0IE                | INT0IE         | RBIE           | TMR0IF         | <b>INT0IF</b>   | RBIF         | 0000 000x            | 53, 101            |

| INTCON2   | RBPU                                                                                                                                                                                                          | INTEDG0        | INTEDG1               | INTEDG2        | _              | TMR0IP         | _               | RBIP         | 1111 -1-1            | 53, 102            |

| INTCON3   | INT2IP                                                                                                                                                                                                        | INT1IP         | _                     | INT2IE         | INT1IE         | _              | INT2IF          | INT1IF       | 11-0 0-00            | 53, 103            |

| INDF0     | Uses content                                                                                                                                                                                                  | s of FSR0 to a | ddress data m         | nemory – value | e of FSR0 not  | changed (not a | a physical regi | ster)        | N/A                  | 53, 75             |

| POSTINC0  | Uses contents of FSR0 to address data memory – value of FSR0 not changed (not a physical register)<br>Uses contents of FSR0 to address data memory – value of FSR0 post-incremented (not a physical register) |                |                       |                |                |                |                 |              | N/A                  | 53, 76             |

| POSTDEC0  | Uses contents of FSR0 to address data memory – value of FSR0 post-decremented (not a physical register)                                                                                                       |                |                       |                |                |                |                 | al register) | N/A                  | 53, 76             |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)                                                                                                        |                |                       |                |                |                |                 | register)    | N/A                  | 53, 76             |

| PLUSW0    | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W                                                                            |                |                       |                |                |                | register) –     | N/A          | 53, 76               |                    |

| FSR0H     | — — — Indirect Data Memory Address Pointer 0 High Byte                                                                                                                                                        |                |                       |                |                |                | High Byte       | 0000         | 53, 75               |                    |

| FSR0L     | Indirect Data Memory Address Pointer 0 Low Byte                                                                                                                                                               |                |                       |                |                |                |                 |              | XXXX XXXX            | 53, 75             |

| WREG      | Working Regi                                                                                                                                                                                                  | ster           |                       |                |                |                |                 |              | XXXX XXXX            | 53                 |

| INDF1     | Uses contents                                                                                                                                                                                                 | s of FSR1 to a | ddress data m         | nemory – value | e of FSR1 not  | changed (not a | a physical regi | ster)        | N/A                  | 53, 75             |

| POSTINC1  | Uses contents                                                                                                                                                                                                 | s of FSR1 to a | ddress data m         | nemory – value | e of FSR1 post | -incremented   | (not a physica  | l register)  | N/A                  | 53, 76             |

| POSTDEC1  | Uses contents                                                                                                                                                                                                 | s of FSR1 to a | ddress data m         | nemory – value | e of FSR1 post | -decremented   | (not a physica  | al register) | N/A                  | 53, 76             |

| PREINC1   | Uses contents                                                                                                                                                                                                 | s of FSR1 to a | ddress data m         | nemory – value | e of FSR1 pre- | incremented (  | not a physical  | register)    | N/A                  | 53, 76             |

| PLUSW1    | Uses contents<br>value of FSR                                                                                                                                                                                 |                | ddress data m         | nemory – value | e of FSR1 pre- | incremented (  | not a physical  | register) –  | N/A                  | 53, 76             |

| FSR1H     | —                                                                                                                                                                                                             | _              | —                     | —              | Indirect Data  | Memory Addr    | ess Pointer 1 I | High Byte    | 0000                 | 53, 75             |

| FSR1L     | Indirect Data                                                                                                                                                                                                 | Memory Addre   | ess Pointer 1 L       | _ow Byte       |                |                |                 |              | XXXX XXXX            | 53, 75             |

| BSR       | —                                                                                                                                                                                                             | _              | _                     | _              | Bank Select F  | Register       |                 |              | 0000                 | 54, 65             |

| INDF2     | Uses contents                                                                                                                                                                                                 | s of FSR2 to a | ddress data m         | nemory – value | e of FSR2 not  | changed (not a | a physical regi | ster)        | N/A                  | 54, 75             |

| POSTINC2  | Uses contents                                                                                                                                                                                                 | s of FSR2 to a | ddress data m         | nemory – value | e of FSR2 post | -incremented   | (not a physica  | l register)  | N/A                  | 54, 76             |

| POSTDEC2  | Uses contents                                                                                                                                                                                                 | s of FSR2 to a | ddress data m         | nemory – value | e of FSR2 post | t-decremented  | (not a physica  | al register) | N/A                  | 54, 76             |

| PREINC2   | Uses contents                                                                                                                                                                                                 | s of FSR2 to a | ddress data m         | nemory – value | e of FSR2 pre- | incremented (  | not a physical  | register)    | N/A                  | 54, 76             |

| PLUSW2    | Uses contents<br>value of FSR                                                                                                                                                                                 |                | ddress data m         | nemory – value | e of FSR2 pre- | incremented (  | not a physical  | register) –  | N/A                  | 54, 76             |

| FSR2H     | —                                                                                                                                                                                                             | —              | —                     | —              | Indirect Data  | Memory Addr    | ess Pointer 2 I | High Byte    | 0000                 | 54, 75             |

| FSR2L     | Indirect Data                                                                                                                                                                                                 | Memory Addre   | ess Pointer 2 l       | _ow Byte       | 1              | 1              | 1               |              | XXXX XXXX            | 54, 75             |

| STATUS    | —                                                                                                                                                                                                             | —              | _                     | Ν              | OV             | Z              | DC              | С            | x xxxx               | 54, 73             |

| TMR0H     | Timer0 Regis                                                                                                                                                                                                  | ter High Byte  |                       |                |                |                |                 |              | 0000 0000            | 54, 129            |

| TMR0L     | Timer0 Regis                                                                                                                                                                                                  | ter Low Byte   |                       |                |                |                |                 |              | XXXX XXXX            | 54, 129            |

|           |                                                                                                                                                                                                               |                |                       |                |                |                |                 |              |                      |                    |

#### DECISTED EILE SLIMMADY

Note 1: Bit 21 of the TBLPTRU allows access to the device Configuration bits.

The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'. 2:

3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

7: I<sup>2</sup>C<sup>™</sup> Slave mode only.

### 13.0 TIMER2 MODULE

The Timer2 module timer incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- · Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP module

The module is controlled through the T2CON register (Register 13-1) which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 13-1.

### 13.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 2-bit counter/prescaler on the clock input gives direct input, divide-by-4 and divide-by-16 prescale options. These are selected by the prescaler control bits, T2CKPS1:T2CKPS0 (T2CON<1:0>). The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 13.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| Unimplemented: Read as '0'                             |

|--------------------------------------------------------|

| T2OUTPS3:T2OUTPS0: Timer2 Output Postscale Select bits |

| 0000 = 1:1 Postscale                                   |

| 0001 = 1:2 Postscale                                   |

| •                                                      |

| •                                                      |

| •                                                      |

| 1111 = 1:16 Postscale                                  |

| TMR2ON: Timer2 On bit                                  |

| 1 = Timer2 is on                                       |

| 0 = Timer2 is off                                      |

| T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits     |

| 00 = Prescaler is 1                                    |

| 01 = Prescaler is 4                                    |

| 1x = Prescaler is 16                                   |

|                                                        |

| Name     | Bit 7                                    | Bit 6                 | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1                 | Bit 0                 | Reset<br>Values<br>on page |

|----------|------------------------------------------|-----------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|----------------------------|

| INTCON   | GIE/GIEH                                 | PEIE/GIEL             | TMR0IE              | INT0IE              | RBIE                | TMR0IF              | INT0IF                | RBIF                  | 53                         |

| RCON     | IPEN                                     | SBOREN <sup>(1)</sup> | _                   | RI                  | TO                  | PD                  | POR                   | BOR                   | 54                         |

| PIR1     | SPPIF <sup>(2)</sup>                     | ADIF                  | RCIF                | TXIF                | SSPIF               | CCP1IF              | TMR2IF                | TMR1IF                | 56                         |

| PIE1     | SPPIE <sup>(2)</sup>                     | ADIE                  | RCIE                | TXIE                | SSPIE               | CCP1IE              | TMR2IE                | TMR1IE                | 56                         |

| IPR1     | SPPIP <sup>(2)</sup>                     | ADIP                  | RCIP                | TXIP                | SSPIP               | CCP1IP              | TMR2IP                | TMR1IP                | 56                         |

| TRISB    | TRISB7                                   | TRISB6                | TRISB5              | TRISB4              | TRISB3              | TRISB2              | TRISB1                | TRISB0                | 56                         |

| TRISC    | TRISC7                                   | TRISC6                | _                   | _                   | _                   | TRISC2              | TRISC1                | TRISC0                | 56                         |

| TMR2     | Timer2 Reg                               | jister                |                     |                     |                     |                     |                       |                       | 54                         |

| PR2      | Timer2 Peri                              | iod Register          |                     |                     |                     |                     |                       |                       | 54                         |

| T2CON    | —                                        | T2OUTPS3              | T2OUTPS2            | T2OUTPS1            | T2OUTPS0            | TMR2ON              | T2CKPS1               | T2CKPS0               | 54                         |

| CCPR1L   | Capture/Co                               | mpare/PWM             | Register 1 L        | ow Byte             |                     |                     |                       |                       | 55                         |

| CCPR1H   | Capture/Co                               | mpare/PWM             | Register 1 H        | ligh Byte           |                     |                     |                       |                       | 55                         |

| CCP1CON  | P1M1 <sup>(2)</sup>                      | P1M0 <sup>(2)</sup>   | DC1B1               | DC1B0               | CCP1M3              | CCP1M2              | CCP1M1                | CCP1M0                | 55                         |

| CCPR2L   | Capture/Co                               | mpare/PWM             | Register 2 l        | ow Byte             |                     |                     |                       |                       | 55                         |

| CCPR2H   | Capture/Compare/PWM Register 2 High Byte |                       |                     |                     |                     |                     |                       |                       |                            |

| CCP2CON  | —                                        | _                     | DC2B1               | DC2B0               | CCP2M3              | CCP2M2              | CCP2M1                | CCP2M0                | 55                         |

| ECCP1AS  | ECCPASE                                  | ECCPAS2               | ECCPAS1             | ECCPAS0             | PSSAC1              | PSSAC0              | PSSBD1 <sup>(2)</sup> | PSSBD0 <sup>(2)</sup> | 55                         |

| ECCP1DEL | PRSEN                                    | PDC6 <sup>(2)</sup>   | PDC5 <sup>(2)</sup> | PDC4 <sup>(2)</sup> | PDC3 <sup>(2)</sup> | PDC2 <sup>(2)</sup> | PDC1 <sup>(2)</sup>   | PDC0 <sup>(2)</sup>   | 55                         |

#### TABLE 15-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

**Note 1:** The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

2: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

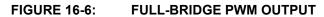

#### 16.4.5 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 16-6. P1A, P1B, P1C and P1D outputs are multiplexed with the PORTC<2>, PORTD<5>, PORTD<6> and PORTD<7> data latches. The TRISC<2>, TRISD<5>, TRISD<6> and TRISD<7> bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs.

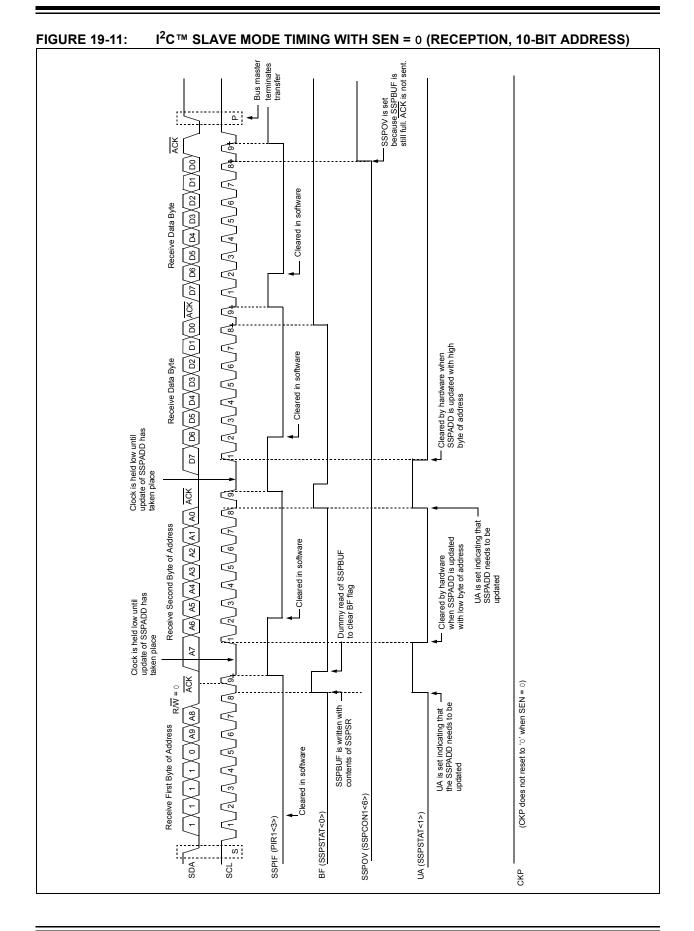

#### 19.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into an inactive state (Figure 19-25).

#### 19.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

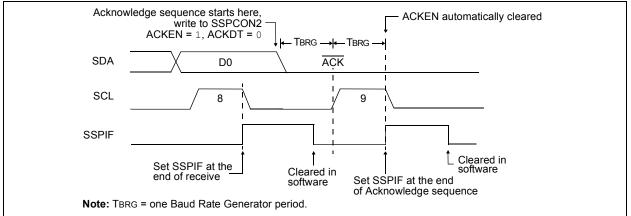

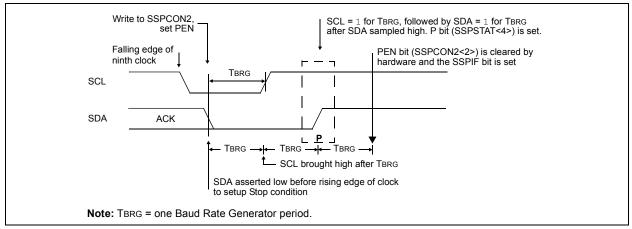

#### 19.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Enable bit, PEN (SSPCON2<2>). At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 19-26).

#### 19.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 19-25: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 19-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

| R/W-0         | R-1                                                                                                          | R/W-0                                                                                           | R/W-0                          | R/W-0                 | U-0             | R/W-0             | R/W-0           |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|-----------------|-------------------|-----------------|--|--|

| ABDOVF        | RCIDL                                                                                                        | RXDTP                                                                                           | TXCKP                          | BRG16                 |                 | WUE               | ABDEN           |  |  |

| bit 7         | •                                                                                                            |                                                                                                 |                                |                       |                 |                   | bit             |  |  |

| Legend:       |                                                                                                              |                                                                                                 |                                |                       |                 |                   |                 |  |  |

| R = Readable  | e bit                                                                                                        | W = Writable                                                                                    | bit                            | U = Unimple           | emented bit, re | ad as '0'         |                 |  |  |

| -n = Value at | POR                                                                                                          | '1' = Bit is se                                                                                 | t                              | '0' = Bit is c        | leared          | x = Bit is unk    | nown            |  |  |

| bit 7         | 1 = A BRG                                                                                                    | Auto-Baud Acqu<br>rollover has oc<br>G rollover has o                                           | curred during                  |                       | te Detect mode  | e (must be cleare | ed in software  |  |  |

| bit 6         | RCIDL: Receive Operation Idle Status bit<br>1 = Receive operation is Idle<br>0 = Receive operation is active |                                                                                                 |                                |                       |                 |                   |                 |  |  |

| bit 5         | Asynchrono<br>1 = RX data<br>0 = RX data<br>Synchrono<br>1 = Receive                                         | a is inverted<br>a received is not                                                              | inverted                       | tate is a low l       |                 |                   |                 |  |  |

| bit 4         | <b>TXCKP</b> : Cle<br><u>Asynchrono</u><br>1 = TX data<br>0 = TX data<br><u>Synchrono</u><br>1 = Clock (f    | ock and Data Po<br>ous mode:<br>a is inverted<br>a is not inverted                              | larity Select b                | it<br>high level.     |                 |                   |                 |  |  |

| bit 3         | <b>BRG16:</b> 16<br>1 = 16-bit E                                                                             | -Bit Baud Rate I<br>Baud Rate Gene                                                              | Register Enab<br>rator – SPBR0 | le bit<br>GH and SPBR | G               | BRGH value ign    | ored            |  |  |

| bit 2         | Unimplem                                                                                                     | ented: Read as                                                                                  | <b>'</b> 0 <b>'</b>            |                       | -               | -                 |                 |  |  |

| bit 1         | Asynchrono<br>1 = EUSAF<br>hardwa                                                                            | RT will continue<br>are on following<br>not monitored o<br>us mode:                             | rising edge                    | -                     | errupt generate | d on falling edge | ; bit cleared i |  |  |

| bit 0         | ABDEN: Au<br>Asynchrono<br>1 = Enable<br>cleared                                                             | uto-Baud Detect<br>ous mode:<br>baud rate mea<br>d in hardware up<br>ate measuremen<br>us mode: | surement on t                  | I.                    | cter. Requires  | reception of a Sy | /nc field (55h  |  |  |

### REGISTER 20-3: BAUDCON: BAUD RATE CONTROL REGISTER

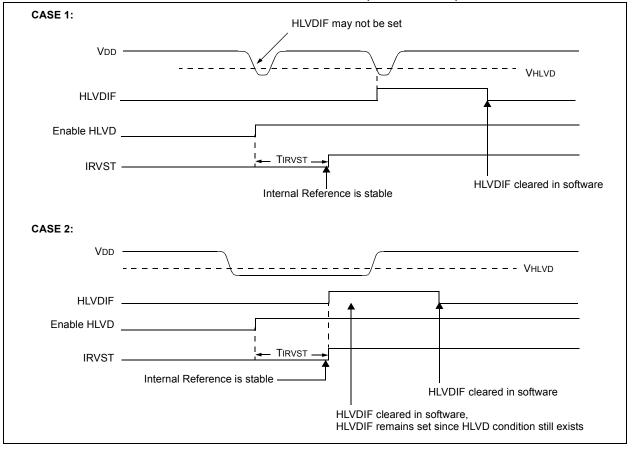

### 24.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- 1. Disable the module by clearing the HLVDEN bit (HLVDCON<4>).

- 2. Write the value to the HLVDL3:HLVDL0 bits that selects the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 4. Enable the HLVD module by setting the HLVDEN bit.

- Clear the HLVD Interrupt Flag, HLVDIF (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt, if interrupts are desired, by setting the HLVDIE and GIE/GIEH bits (PIE2<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

#### 24.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022 (Section 28.2 "DC Characteristics"). Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

### 24.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420 (see Table 28-6 in **Section 28.0 "Electrical Characteristics"**), may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36 (Table 28-12).

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval. Refer to Figure 24-2 or Figure 24-3.

| ANDWF                   | AND W wi                                                                                                                                                                                               | th f                                                                                                                                                                                   |                                                                                                                                                                     | BC    |                                                     | Branch if (                                                                                                               | Carry                                                           |                                             |                              |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|------------------------------|

| Syntax:                 | ANDWF                                                                                                                                                                                                  | f {,d {,a}}                                                                                                                                                                            |                                                                                                                                                                     | Synta | ax:                                                 | BC n                                                                                                                      |                                                                 |                                             |                              |

| Operands:               | $0 \leq f \leq 255$                                                                                                                                                                                    |                                                                                                                                                                                        |                                                                                                                                                                     | Oper  | ands:                                               | -128 ≤ n ≤                                                                                                                | 127                                                             |                                             |                              |

|                         | $\begin{array}{l} d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                                              |                                                                                                                                                                                        |                                                                                                                                                                     | Oper  | ation:                                              | if Carry bit<br>(PC) + 2 +                                                                                                |                                                                 |                                             |                              |

| Operation:              | (W) .AND.                                                                                                                                                                                              | (f) $\rightarrow$ dest                                                                                                                                                                 |                                                                                                                                                                     | Statu | s Affected:                                         | None                                                                                                                      |                                                                 |                                             |                              |

| Status Affected         | : N, Z                                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                     | Enco  | oding:                                              | 1110                                                                                                                      | 0010                                                            | nnnn                                        | nnnn                         |

| Encoding:               | 0001                                                                                                                                                                                                   | 01da ff                                                                                                                                                                                | ff ffff                                                                                                                                                             |       | cription:                                           | If the Carry                                                                                                              |                                                                 |                                             |                              |

| Description:            | register f <sup>2</sup> .<br>in W. If 'd' i<br>in register<br>If 'a' is '0',<br>If 'a' is '1', f<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 26<br>Bit-Oriente | f' (default).<br>the Access Ba<br>the BSR is use<br>(default).<br>and the extend<br>led, this instruct<br>Literal Offset A<br>never $f \le 95$ (5)<br>5.2.3 "Byte-Or<br>ed Instruction | result is stored<br>is stored back<br>is stored back<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>iented and<br>s in Indexed |       |                                                     | will branch.<br>The 2's cor<br>added to th<br>incremente<br>instruction,<br>PC + 2 + 2<br>two-cycle in<br>1<br>1(2)<br>Q2 | mplement<br>e PC. Sin<br>d to fetch<br>the new a<br>n. This ins | ce the F<br>the nex<br>address<br>structior | PC will have<br>t<br>will be |

| Words:                  |                                                                                                                                                                                                        | set Mode" for                                                                                                                                                                          | detalls.                                                                                                                                                            |       | Decode                                              | Read literal                                                                                                              | Proces                                                          |                                             | /rite to PC                  |

|                         | 1                                                                                                                                                                                                      |                                                                                                                                                                                        |                                                                                                                                                                     |       | Nia                                                 | ʻn'                                                                                                                       | Data                                                            |                                             | Nie                          |

| Cycles:                 | 1                                                                                                                                                                                                      |                                                                                                                                                                                        |                                                                                                                                                                     |       | No<br>operation                                     | No<br>operation                                                                                                           | No<br>operati                                                   | on                                          | No<br>operation              |

| Q Cycle Activi<br>Q1    | uy.<br>Q2                                                                                                                                                                                              | Q3                                                                                                                                                                                     | Q4                                                                                                                                                                  | lf No | Jump:                                               | 1 1                                                                                                                       |                                                                 |                                             |                              |

| Decode                  |                                                                                                                                                                                                        | Process                                                                                                                                                                                | Write to                                                                                                                                                            |       | Q1                                                  | Q2                                                                                                                        | Q3                                                              |                                             | Q4                           |

|                         | register 'f'                                                                                                                                                                                           | Data                                                                                                                                                                                   | destination                                                                                                                                                         |       | Decode                                              | Read literal<br>'n'                                                                                                       | Proces<br>Data                                                  |                                             | No<br>operation              |

| Example:                | ANDWF                                                                                                                                                                                                  | REG, 0, 0                                                                                                                                                                              |                                                                                                                                                                     | Exan  | nnle <sup>.</sup>                                   | HERE                                                                                                                      | BC 5                                                            |                                             |                              |

| Before Ins<br>W<br>REG  | = 17h<br>= C2h                                                                                                                                                                                         |                                                                                                                                                                                        |                                                                                                                                                                     |       | Before Instruc<br>PC                                | ction<br>= ad                                                                                                             | dress (H                                                        |                                             |                              |

| After Instr<br>W<br>REG | = 02h                                                                                                                                                                                                  |                                                                                                                                                                                        |                                                                                                                                                                     |       | After Instructi<br>If Carry<br>PC<br>If Carry<br>PC | = 1;<br>= ad<br>= 0;                                                                                                      | dress (H                                                        |                                             | ,                            |

| BCF                                  | Bit Clear f                                                                                                                                                                                                                                                                            |                                                                               | BN                                                             | Branch if M                                                            | legative                                                                             |                                                        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|

| Syntax:                              | BCF f, b {,a}                                                                                                                                                                                                                                                                          |                                                                               | Syntax:                                                        | BN n                                                                   |                                                                                      |                                                        |

| Operands:                            | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                    |                                                                               | Operands:                                                      | -128 ≤ n ≤ ′                                                           | 127                                                                                  |                                                        |

|                                      | $0 \le b \le 7$<br>a $\in [0,1]$                                                                                                                                                                                                                                                       |                                                                               | Operation:                                                     | if Negative<br>(PC) + 2 +                                              |                                                                                      |                                                        |

| Operation:                           | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                              |                                                                               | Status Affected:                                               | None                                                                   |                                                                                      |                                                        |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                   |                                                                               | Encoding:                                                      | 1110                                                                   | 0110 nn                                                                              | nn nnnn                                                |

| Encoding:<br>Description:            | 1001bbbaffffBit 'b' in register 'f' is clearedIf 'a' is '0', the Access Bank iIf 'a' is '1', the BSR is used toGPR bank (default).If 'a' is '0' and the extended iset is enabled, this instructioin Indexed Literal Offset Addmode whenever $f \le 95$ (5Fh)Section 26.2.3 "Byte-Orien | is selected.<br>o select the<br>instruction<br>n operates<br>ressing<br>. See | Description:<br>Words:                                         | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addro<br>n. This instruc | nber '2n' is<br>ne PC will have<br>next<br>ess will be |

|                                      | Bit-Oriented Instructions in                                                                                                                                                                                                                                                           |                                                                               | Cycles:                                                        | 1(2)                                                                   |                                                                                      |                                                        |

| Words:                               | Literal Offset Mode" for det<br>1                                                                                                                                                                                                                                                      | tails.                                                                        | Q Cycle Activity<br>If Jump:                                   | :                                                                      |                                                                                      |                                                        |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                      |                                                                               | Q1                                                             | Q2                                                                     | Q3                                                                                   | Q4                                                     |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                        |                                                                               | Decode                                                         | Read literal<br>'n'                                                    | Process<br>Data                                                                      | Write to PC                                            |

| Q1<br>Decode                         | Q2 Q3<br>Read Process                                                                                                                                                                                                                                                                  | Q4<br>Write                                                                   | No<br>operation                                                | No<br>operation                                                        | No<br>operation                                                                      | No<br>operation                                        |