#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 24KB (12K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4455t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Dia News                                                       | Pin Number    |    |      | Pin Buffer                  | Buffer                               | Departuration                                                                                                                                                                      |  |  |

|----------------------------------------------------------------|---------------|----|------|-----------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                       | PDIP QFN TQFP |    | Туре | Туре                        | Description                          |                                                                                                                                                                                    |  |  |

| RB0/AN12/INT0/<br>FLT0/SDI/SDA<br>RB0                          | 33            | 9  | 8    | 1/0                         | TTL                                  | PORTB is a bidirectional I/O port. PORTB can be softwa<br>programmed for internal weak pull-ups on all inputs.<br>Digital I/O.                                                     |  |  |

| AN12<br>INTO<br>FLTO<br>SDI<br>SDA                             |               |    |      | /O                          | Analog<br>ST<br>ST<br>ST<br>ST<br>ST | Analog input 12.<br>External interrupt 0.<br>Enhanced PWM Fault input (ECCP1 module).<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                               |  |  |

| RB1/AN10/INT1/SCK/<br>SCL<br>RB1<br>AN10<br>INT1<br>SCK<br>SCL | 34            | 10 | 9    | I/O<br>I<br>I<br>I/O<br>I/O | TTL<br>Analog<br>ST<br>ST<br>ST      | Digital I/O.<br>Analog input 10.<br>External interrupt 1.<br>Synchronous serial clock input/output for SPI mode<br>Synchronous serial clock input/output for I <sup>2</sup> C mode |  |  |

| RB2/AN8/INT2/VMO<br>RB2<br>AN8<br>INT2<br>VMO                  | 35            | 11 | 10   | I/O<br>I<br>I<br>O          | TTL<br>Analog<br>ST<br>—             | Digital I/O.<br>Analog input 8.<br>External interrupt 2.<br>External USB transceiver VMO output.                                                                                   |  |  |

| RB3/AN9/CCP2/VPO<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup><br>VPO   | 36            | 12 | 11   | I/O<br>I<br>I/O<br>O        | TTL<br>Analog<br>ST<br>—             | Digital I/O.<br>Analog input 9.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>External USB transceiver VPO output.                                                           |  |  |

| RB4/AN11/KBI0/CSSPP<br>RB4<br>AN11<br>KBI0<br>CSSPP            | 37            | 14 | 14   | I/O<br>I<br>I<br>O          | TTL<br>Analog<br>TTL<br>—            | Digital I/O.<br>Analog input 11.<br>Interrupt-on-change pin.<br>SPP chip select control output.                                                                                    |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                             | 38            | 15 | 15   | I/O<br>I<br>I/O             | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                                                                                              |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                             | 39            | 16 | 16   | I/O<br>I<br>I/O             | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock p                                                                                       |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3                                    | 40            | 17 | 17   | I/O<br>I<br>I/O             | TTL<br>TTL<br>ST                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pi                                                                                       |  |  |

#### TABLE 1-3: PIC18F4455/4550 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared.

2: Default assignment for CCP2 when CCP2MX Configuration bit is set.

**3:** These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

#### 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 28-12). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 25.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

#### 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 25.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 25.4 "Fail-Safe Clock Monitor"**) is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

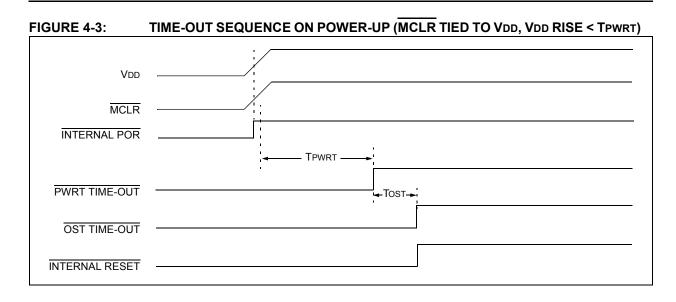

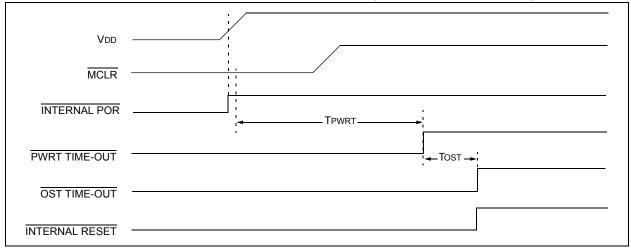

#### FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

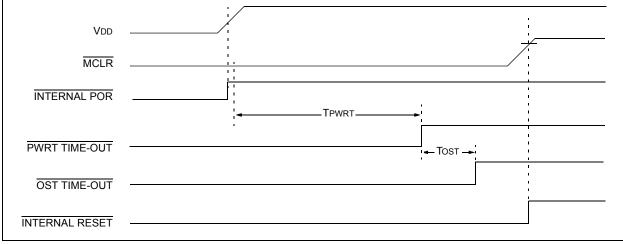

### FIGURE 4-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset. Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

| TABLE 4-3: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION |

|------------|------------------------------------------------------------------|

|            | FOR RCON REGISTER                                                |

| Condition                                                    | Program               |    | RCO | N Reg |     | STKPTR Register |        |        |

|--------------------------------------------------------------|-----------------------|----|-----|-------|-----|-----------------|--------|--------|

| Condition                                                    | Counter               | RI | то  | PD    | POR | BOR             | STKFUL | STKUNF |

| Power-on Reset                                               | 0000h                 | 1  | 1   | 1     | 0   | 0               | 0      | 0      |

| RESET instruction                                            | 0000h                 | 0  | u   | u     | u   | u               | u      | u      |

| Brown-out Reset                                              | 0000h                 | 1  | 1   | 1     | u   | 0               | u      | u      |

| MCLR Reset during power-managed Run modes                    | 0000h                 | u  | 1   | u     | u   | u               | u      | u      |

| MCLR Reset during power-managed Idle modes and Sleep mode    | 0000h                 | u  | 1   | 0     | u   | u               | u      | u      |

| WDT time-out during full power or<br>power-managed Run modes | 0000h                 | u  | 0   | u     | u   | u               | u      | u      |

| MCLR Reset during full-power execution                       | 0000h                 | u  | u   | u     | u   | u               | u      | u      |

| Stack Full Reset (STVREN = 1)                                | 0000h                 | u  | u   | u     | u   | u               | 1      | u      |

| Stack Underflow Reset (STVREN = 1)                           | 0000h                 | u  | u   | u     | u   | u               | u      | 1      |

| Stack Underflow Error (not an actual Reset,<br>STVREN = 0)   | 0000h                 | u  | u   | u     | u   | u               | u      | 1      |

| WDT time-out during power-managed Idle or Sleep modes        | PC + 2                | u  | 0   | 0     | u   | u               | u      | u      |

| Interrupt exit from power-managed modes                      | PC + 2 <sup>(1)</sup> | u  | u   | 0     | u   | u               | u      | u      |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

| TABLE 4-4:          | INIT | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |      |      |                                    |                                                                  |                                 |  |  |  |  |  |  |

|---------------------|------|---------------------------------------------------------|------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|

| Register Appli      |      | plicable Devices                                        |      |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |  |

| INDF2               | 2455 | 2550                                                    | 4455 | 4550 | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| POSTINC2            | 2455 | 2550                                                    | 4455 | 4550 | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| POSTDEC2            | 2455 | 2550                                                    | 4455 | 4550 | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| PREINC2             | 2455 | 2550                                                    | 4455 | 4550 | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| PLUSW2              | 2455 | 2550                                                    | 4455 | 4550 | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| FSR2H               | 2455 | 2550                                                    | 4455 | 4550 | 0000                               | 0000                                                             | uuuu                            |  |  |  |  |  |  |

| FSR2L               | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| STATUS              | 2455 | 2550                                                    | 4455 | 4550 | x xxxx                             | u uuuu                                                           | u uuuu                          |  |  |  |  |  |  |

| TMR0H               | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| TMR0L               | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| T0CON               | 2455 | 2550                                                    | 4455 | 4550 | 1111 1111                          | 1111 1111                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| OSCCON              | 2455 | 2550                                                    | 4455 | 4550 | 0100 q000                          | 0100 00q0                                                        | uuuu uuqu                       |  |  |  |  |  |  |

| HLVDCON             | 2455 | 2550                                                    | 4455 | 4550 | 0-00 0101                          | 0-00 0101                                                        | u-uu uuuu                       |  |  |  |  |  |  |

| WDTCON              | 2455 | 2550                                                    | 4455 | 4550 | 0                                  | 0                                                                | u                               |  |  |  |  |  |  |

| RCON <sup>(4)</sup> | 2455 | 2550                                                    | 4455 | 4550 | 0q-1 11q0                          | 0q-q qquu                                                        | uq-u qquu                       |  |  |  |  |  |  |

| TMR1H               | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| TMR1L               | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| T1CON               | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | u0uu uuuu                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| TMR2                | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| PR2                 | 2455 | 2550                                                    | 4455 | 4550 | 1111 1111                          | 1111 1111                                                        | 1111 1111                       |  |  |  |  |  |  |

| T2CON               | 2455 | 2550                                                    | 4455 | 4550 | -000 0000                          | -000 0000                                                        | -uuu uuuu                       |  |  |  |  |  |  |

| SSPBUF              | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | uuuu uuuu                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| SSPADD              | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| SSPSTAT             | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| SSPCON1             | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| SSPCON2             | 2455 | 2550                                                    | 4455 | 4550 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| ADRESH              | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | սսսս սսսս                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| ADRESL              | 2455 | 2550                                                    | 4455 | 4550 | XXXX XXXX                          | սսսս սսսս                                                        | սսսս սսսս                       |  |  |  |  |  |  |

| ADCON0              | 2455 | 2550                                                    | 4455 | 4550 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |  |  |  |  |  |

| ADCON1              | 2455 | 2550                                                    | 4455 | 4550 | 00 0qqq                            | 00 0qqq                                                          | uu uuuu                         |  |  |  |  |  |  |

| ADCON2              | 2455 | 2550                                                    | 4455 | 4550 | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |  |  |  |  |  |  |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **4:** See Table 4-3 for Reset value for specific condition.

**5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

#### 6.5 Writing to Flash Program Memory

The minimum programming block is 16 words or 32 bytes. Word or byte programming is not supported.

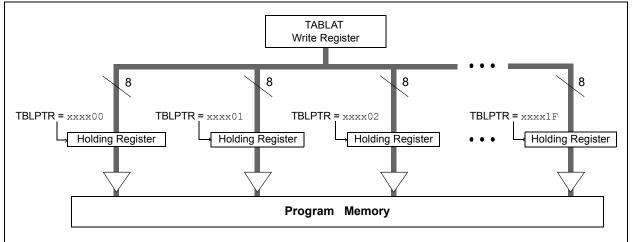

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 32 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 32 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 32 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 32 holding registers before executing a write operation.

#### 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the Row Erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write 32 bytes into the holding registers with auto-increment.

- Set the EECON1 register for the write operation:

set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Repeat steps 6 through 14 once more to write 64 bytes.

- 15. Verify the memory (table read).

This procedure will require about 8 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 6-3.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 32 bytes in the holding register.

### 9.0 INTERRUPTS

The PIC18F2455/2550/4455/4550 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 000008h and the low-priority interrupt vector is at 000018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

| Note: | Do not use the MOVFF instruction to modify   |

|-------|----------------------------------------------|

|       | any of the interrupt control registers while |

|       | any interrupt is enabled. Doing so may       |

|       | cause erratic microcontroller behavior.      |

#### 9.1 USB Interrupts

Unlike other peripherals, the USB module is capable of generating a wide range of interrupts for many types of events. These include several types of normal communication and status events and several module level error events.

To handle these events, the USB module is equipped with its own interrupt logic. The logic functions in a manner similar to the microcontroller level interrupt funnel, with each interrupt source having separate flag and enable bits. All events are funneled to a single device level interrupt, USBIF (PIR2<5>). Unlike the device level interrupt logic, the individual USB interrupt events cannot be individually assigned their own priority. This is determined at the device level interrupt funnel for all USB events by the USBIP bit.

For additional details on USB interrupt logic, refer to **Section 17.5 "USB Interrupts"**.

| TABLE 10-7:  | -7: PORTD I/O SUMMARY |                 |     |          |                                                                                             |  |  |  |

|--------------|-----------------------|-----------------|-----|----------|---------------------------------------------------------------------------------------------|--|--|--|

| Pin          | Function              | TRIS<br>Setting | I/O | I/О Туре | Description                                                                                 |  |  |  |

| RD0/SPP0     | RD0                   | 0               | OUT | DIG      | LATD<0> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<0> data input.                                                                        |  |  |  |

|              | SPP0                  | 1               | OUT | DIG      | SPP<0> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<0> input data.                                                                          |  |  |  |

| RD1/SPP1     | RD1                   | 0               | OUT | DIG      | LATD<1> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<1> data input.                                                                        |  |  |  |

|              | SPP1                  | 1               | OUT | DIG      | SPP<1> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<1> input data.                                                                          |  |  |  |

| RD2/SPP2     | RD2                   | 0               | OUT | DIG      | LATD<2> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<2> data input.                                                                        |  |  |  |

|              | SPP2                  | 1               | OUT | DIG      | SPP<2> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<2> input data.                                                                          |  |  |  |

| RD3/SPP3     | RD3                   | 0               | OUT | DIG      | LATD<3> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<3> data input.                                                                        |  |  |  |

|              | SPP3                  | 1               | OUT | DIG      | SPP<3> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<3> input data.                                                                          |  |  |  |

| RD4/SPP4     | RD4                   | 0               | OUT | DIG      | LATD<4> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<4> data input.                                                                        |  |  |  |

|              | SPP4                  | 1               | OUT | DIG      | SPP<4> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<4> input data.                                                                          |  |  |  |

| RD5/SPP5/P1B | RD5                   | 0               | OUT | DIG      | LATD<5> data output                                                                         |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<5> data input                                                                         |  |  |  |

|              | SPP5                  | 1               | OUT | DIG      | SPP<5> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<5> input data.                                                                          |  |  |  |

|              | P1B                   | 0               | OUT | DIG      | ECCP1 Enhanced PWM output, Channel B; takes priority over port and SPP data. <sup>(1)</sup> |  |  |  |

| RD6/SPP6/P1C | RD6                   | 0               | OUT | DIG      | LATD<6> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<6> data input.                                                                        |  |  |  |

|              | SPP6                  | 1               | OUT | DIG      | SPP<6> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<6> input data.                                                                          |  |  |  |

|              | P1C                   | 0               | OUT | DIG      | ECCP1 Enhanced PWM output, Channel C; takes priority over port and SPP data. <sup>(1)</sup> |  |  |  |

| RD7/SPP7/P1D | RD7                   | 0               | OUT | DIG      | LATD<7> data output.                                                                        |  |  |  |

|              |                       | 1               | IN  | ST       | PORTD<7> data input.                                                                        |  |  |  |

|              | SPP7                  | 1               | OUT | DIG      | SPP<7> output data; takes priority over port data.                                          |  |  |  |

|              |                       | 1               | IN  | TTL      | SPP<7> input data.                                                                          |  |  |  |

|              | P1D                   | 0               | OUT | DIG      | ECCP1 Enhanced PWM output, Channel D; takes priority over port and SPP data. <sup>(1)</sup> |  |  |  |

TABLE 10-7: PORTD I/O SUMMARY

Legend: OUT = Output, IN = Input, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input

Note 1: May be configured for tri-state during Enhanced PWM shutdown events.

| <b>TABLE 10-8</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|---------------------|--------------------------------------------|

|---------------------|--------------------------------------------|

| Name                  | Bit 7               | Bit 6               | Bit 5  | Bit 4  | Bit 3                | Bit 2              | Bit 1              | Bit 0              | Reset<br>Values<br>on page |

|-----------------------|---------------------|---------------------|--------|--------|----------------------|--------------------|--------------------|--------------------|----------------------------|

| PORTD <sup>(3)</sup>  | RD7                 | RD6                 | RD5    | RD4    | RD3                  | RD2                | RD1                | RD0                | 56                         |

| LATD <sup>(3)</sup>   | LATD7               | LATD6               | LATD5  | LATD4  | LATD3                | LATD2              | LATD1              | LATD0              | 56                         |

| TRISD <sup>(3)</sup>  | TRISD7              | TRISD6              | TRISD5 | TRISD4 | TRISD3               | TRISD2             | TRISD1             | TRISD0             | 56                         |

| PORTE                 | RDPU <sup>(3)</sup> | _                   | _      | _      | RE3 <sup>(1,2)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | 56                         |

| CCP1CON               | P1M1 <sup>(3)</sup> | P1M0 <sup>(3)</sup> | DC1B1  | DC1B0  | CCP1M3               | CCP1M2             | CCP1M1             | CCP1M0             | 55                         |

| SPPCON <sup>(3)</sup> | _                   | —                   | —      | —      | —                    | —                  | SPPOWN             | SPPEN              | 57                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

2: RE3 is the only PORTE bit implemented on both 28-pin and 40/44-pin devices. All other bits are implemented only when PORTE is implemented (i.e., 40/44-pin devices).

3: These registers and/or bits are unimplemented on 28-pin devices.

| Name     | Bit 7                | Bit 6                 | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1                 | Bit 0                 | Reset<br>Values<br>on page |

|----------|----------------------|-----------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|----------------------------|

| INTCON   | GIE/GIEH             | PEIE/GIEL             | TMR0IE              | INT0IE              | RBIE                | TMR0IF              | INT0IF                | RBIF                  | 53                         |

| RCON     | IPEN                 | SBOREN <sup>(1)</sup> | _                   | RI                  | TO                  | PD                  | POR                   | BOR                   | 54                         |

| PIR1     | SPPIF <sup>(2)</sup> | ADIF                  | RCIF                | TXIF                | SSPIF               | CCP1IF              | TMR2IF                | TMR1IF                | 56                         |

| PIE1     | SPPIE <sup>(2)</sup> | ADIE                  | RCIE                | TXIE                | SSPIE               | CCP1IE              | TMR2IE                | TMR1IE                | 56                         |

| IPR1     | SPPIP <sup>(2)</sup> | ADIP                  | RCIP                | TXIP                | SSPIP               | CCP1IP              | TMR2IP                | TMR1IP                | 56                         |

| TRISB    | TRISB7               | TRISB6                | TRISB5              | TRISB4              | TRISB3              | TRISB2              | TRISB1                | TRISB0                | 56                         |

| TRISC    | TRISC7               | TRISC6                | _                   | _                   | _                   | TRISC2              | TRISC1                | TRISC0                | 56                         |

| TMR2     | Timer2 Reg           | jister                |                     |                     |                     |                     |                       |                       | 54                         |

| PR2      | Timer2 Peri          | iod Register          |                     |                     |                     |                     |                       |                       | 54                         |

| T2CON    | —                    | T2OUTPS3              | T2OUTPS2            | T2OUTPS1            | T2OUTPS0            | TMR2ON              | T2CKPS1               | T2CKPS0               | 54                         |

| CCPR1L   | Capture/Co           | mpare/PWM             | Register 1 L        | ow Byte             |                     |                     |                       |                       | 55                         |

| CCPR1H   | Capture/Co           | mpare/PWM             | Register 1 H        | ligh Byte           |                     |                     |                       |                       | 55                         |

| CCP1CON  | P1M1 <sup>(2)</sup>  | P1M0 <sup>(2)</sup>   | DC1B1               | DC1B0               | CCP1M3              | CCP1M2              | CCP1M1                | CCP1M0                | 55                         |

| CCPR2L   | Capture/Co           | mpare/PWM             | Register 2 l        | ow Byte             |                     |                     |                       |                       | 55                         |

| CCPR2H   | Capture/Co           | mpare/PWM             | Register 2 H        | High Byte           |                     |                     |                       |                       | 55                         |

| CCP2CON  | —                    | _                     | DC2B1               | DC2B0               | CCP2M3              | CCP2M2              | CCP2M1                | CCP2M0                | 55                         |

| ECCP1AS  | ECCPASE              | ECCPAS2               | ECCPAS1             | ECCPAS0             | PSSAC1              | PSSAC0              | PSSBD1 <sup>(2)</sup> | PSSBD0 <sup>(2)</sup> | 55                         |

| ECCP1DEL | PRSEN                | PDC6 <sup>(2)</sup>   | PDC5 <sup>(2)</sup> | PDC4 <sup>(2)</sup> | PDC3 <sup>(2)</sup> | PDC2 <sup>(2)</sup> | PDC1 <sup>(2)</sup>   | PDC0 <sup>(2)</sup>   | 55                         |

#### TABLE 15-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

**Note 1:** The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

2: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

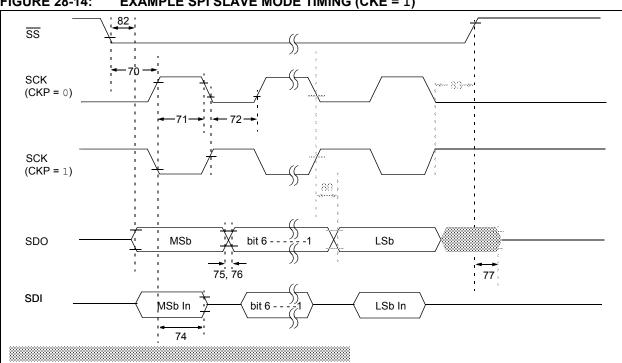

#### 19.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

#### 19.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a

transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When     | the SF    | Pl mod          | ule is in Sl  | ave mode  |

|---------|----------|-----------|-----------------|---------------|-----------|

|         | with     | SS        | pin             | control       | enabled   |

|         | (SSPC    | ON1<3     | 3:0> = C        | 100), the S   | PI module |

|         | will res | et if the | e <u>SS</u> pii | n is set to V | DD.       |

2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

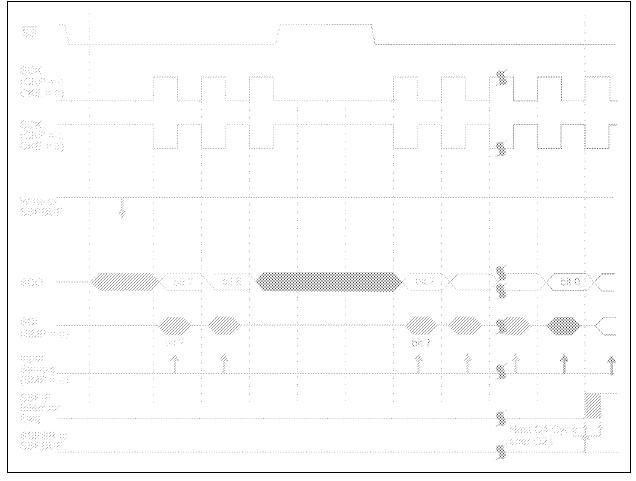

#### FIGURE 19-4: SLAVE SYNCHRONIZATION WAVEFORM

| R/W-0        | R/W-0                            | R/W-0                               | R/W-0                | R/W-0                 | R/W-0               | R/W-0               | R/W-0              |

|--------------|----------------------------------|-------------------------------------|----------------------|-----------------------|---------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                          | ACKDT <sup>(1)</sup>                | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>   | PEN <sup>(2)</sup>  | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7        |                                  |                                     | ·                    |                       |                     |                     | bit (              |

| Legend:      |                                  |                                     |                      |                       |                     |                     |                    |

| R = Readab   | le bit                           | W = Writable                        | bit                  | U = Unimpler          | nented bit, rea     | d as '0'            |                    |

| -n = Value a | t POR                            | '1' = Bit is set                    |                      | '0' = Bit is cle      | ared                | x = Bit is unkn     | iown               |

| bit 7        | GCEN: Gene                       | ral Call Enable                     | bit (Slave mo        | de only)              |                     |                     |                    |

|              | Unused in Ma                     | aster mode.                         |                      |                       |                     |                     |                    |

| bit 6        | ACKSTAT: A                       | cknowledge Sta                      | atus bit (Maste      | er Transmit mo        | de only)            |                     |                    |

|              |                                  | dge was not re<br>dge was receiv    |                      |                       |                     |                     |                    |

| bit 5        |                                  | nowledge Data                       |                      |                       | nly) <sup>(1)</sup> |                     |                    |

|              | 1 = Not Ackn                     | owledge                             | ,                    |                       |                     |                     |                    |

| L:1 4        | 0 = Acknowle                     | age<br>nowledge Sequ                | ianaa Frahla         | L:4(2)                |                     |                     |                    |

| bit 4        |                                  | •                                   |                      |                       | s and transmit      | ACKDT data bit.     | Automatical        |

|              | cleared b                        | by hardware.<br>edge sequence       |                      |                       |                     |                     |                    |

| bit 3        |                                  | ve Enable bit (                     |                      | e mode only)          | 2)                  |                     |                    |

| bit 5        |                                  | Receive mode                        |                      | e mode only).         |                     |                     |                    |

|              | 0 = Receive I                    |                                     |                      |                       |                     |                     |                    |

| bit 2        | PEN: Stop Co                     | ondition Enable                     | e bit <sup>(2)</sup> |                       |                     |                     |                    |

|              | 1 = Initiate St<br>0 = Stop cond | op condition or<br>lition Idle      | SDA and SC           | L pins. Automa        | atically cleared    | by hardware.        |                    |

| bit 1        | RSEN: Repea                      | ated Start Cond                     | dition Enable b      | <sub>oit</sub> (2)    |                     |                     |                    |

|              |                                  | epeated Start o<br>d Start conditio |                      | DA and SCL p          | ins. Automatica     | ally cleared by h   | ardware.           |

| bit 0        | SEN: Start Co                    | ondition Enable                     | /Stretch Enab        | le bit <sup>(2)</sup> |                     |                     |                    |

|              |                                  | art condition or                    |                      |                       | atically cleared    | by hardware.        |                    |

| Note 1: V    | alue that will be t              | ransmitted whe                      | en the user init     | iates an Ackno        | wledge seque        | nce at the end c    | of a receive.      |

### REGISTER 19-5: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

- **Note 1:** Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

- 2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

#### 19.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 19.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 19.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- · Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

#### 19.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

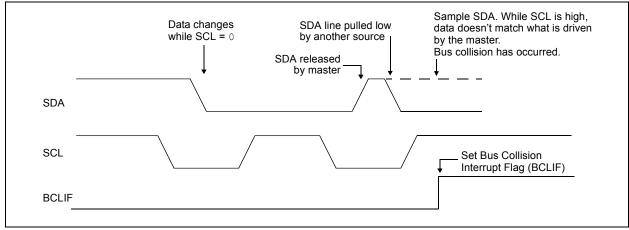

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 19-27).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF bit will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 19-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

#### 20.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line.

Clock polarity (CK) is selected with the TXCKP bit (BAUDCON<4>). Setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. Data polarity (DT) is selected with the RXDTP bit (BAUDCON<5>). Setting RXDTP sets the Idle state on DT as high, while clearing the bit sets the Idle state as low. DT is sampled when CK returns to its idle state. This option is provided to support Microwire devices with this module.

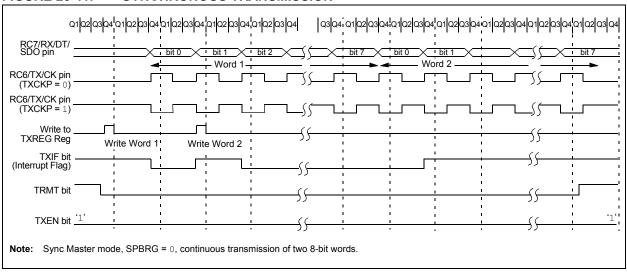

#### 20.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 20-11: SYNCHRONOUS TRANSMISSION

#### REGISTER 25-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

|              |                                                                                                          |                                              |                 |                 | · ·               |                 | ,       |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|-----------------|-------------------|-----------------|---------|--|--|

| U-0          | U-0                                                                                                      | R/P-0                                        | R/P-0           | R/P-0           | R/P-0             | R/P-0           | R/P-0   |  |  |

| _            |                                                                                                          | USBDIV                                       | CPUDIV1         | CPUDIV0         | PLLDIV2           | PLLDIV1         | PLLDIV0 |  |  |

| bit 7        |                                                                                                          |                                              |                 |                 |                   |                 | bit C   |  |  |

|              |                                                                                                          |                                              |                 |                 |                   |                 |         |  |  |

| Legend:      |                                                                                                          |                                              |                 |                 |                   |                 |         |  |  |

| R = Readabl  |                                                                                                          | P = Programr                                 | nable bit       | -               | nented bit, read  |                 |         |  |  |

| -n = Value w | hen device is unp                                                                                        | programmed                                   |                 | u = Unchange    | ed from progran   | nmed state      |         |  |  |

|              |                                                                                                          |                                              |                 |                 |                   |                 |         |  |  |

| bit 7-6      | -                                                                                                        | ted: Read as '                               |                 |                 |                   |                 |         |  |  |

| bit 5        |                                                                                                          |                                              |                 | •               | SB mode only; I   | JCFG:FSEN =     | 1)      |  |  |

|              |                                                                                                          |                                              |                 | MHz PLL divide  |                   |                 | _       |  |  |

| h:+ 4 0      |                                                                                                          |                                              | -               |                 | scillator block w | ith no posiscal | 5       |  |  |

| bit 4-3      |                                                                                                          |                                              |                 | caler Selection | DIIS              |                 |         |  |  |

|              | For XT, HS, EC and ECIO Oscillator modes:<br>11 = Primary oscillator divided by 4 to derive system clock |                                              |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          |                                              |                 | ive system cloc |                   |                 |         |  |  |

|              |                                                                                                          |                                              |                 | ive system cloc |                   |                 |         |  |  |

|              | 00 = Primary                                                                                             | oscillator used                              | directly for sy | stem clock (no  | postscaler)       |                 |         |  |  |

|              |                                                                                                          |                                              |                 | scillator modes | <u>s:</u>         |                 |         |  |  |

|              |                                                                                                          | PLL divided by                               |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          | PLL divided by<br>PLL divided by             |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          | PLL divided by                               |                 |                 |                   |                 |         |  |  |

| bit 2-0      |                                                                                                          | .DIV0: PLL Pre                               | •               |                 |                   |                 |         |  |  |

|              | 111 = Divide I                                                                                           | 111 = Divide by 12 (48 MHz oscillator input) |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          | by 10 (40 MHz                                |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          | by 6 (24 MHz o                               |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          | by 5 (20 MHz o                               |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          | by 4 (16 MHz o<br>by 3 (12 MHz o             |                 |                 |                   |                 |         |  |  |

|              |                                                                                                          |                                              |                 | .)              |                   |                 |         |  |  |

|              |                                                                                                          | by 2 (8 MHz os                               | •               | :)              |                   |                 |         |  |  |

| BRA                                                                                                                                                                                                                           | BRA Unconditional Branch                 |                     |                |       |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------|----------------|-------|-------------|--|--|

| Synta                                                                                                                                                                                                                         | ax:                                      | BRA n               |                |       |             |  |  |

| $\label{eq:operands} Operands:  -1024 \leq n \leq 1023$                                                                                                                                                                       |                                          |                     |                |       |             |  |  |

| Operation: $(PC) + 2 + 2n \rightarrow PC$                                                                                                                                                                                     |                                          |                     |                |       |             |  |  |

| Statu                                                                                                                                                                                                                         | s Affected:                              | None                |                |       |             |  |  |

| Enco                                                                                                                                                                                                                          | ding:                                    | 1101                | 0nnn           | nnnr  | n nnnn      |  |  |

| Description: Add the 2's complement number '2n' to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction. |                                          |                     |                |       |             |  |  |

| Word                                                                                                                                                                                                                          | s:                                       | 1                   | 1              |       |             |  |  |

| Cycle                                                                                                                                                                                                                         | es:                                      | 2                   | 2              |       |             |  |  |

| QC                                                                                                                                                                                                                            | ycle Activity:                           |                     |                |       |             |  |  |

|                                                                                                                                                                                                                               | Q1                                       | Q2                  | Q3             |       | Q4          |  |  |

|                                                                                                                                                                                                                               | Decode                                   | Read literal<br>'n' | Proces<br>Data |       | Write to PC |  |  |

|                                                                                                                                                                                                                               | No                                       | No                  | No             |       | No          |  |  |

|                                                                                                                                                                                                                               | operation                                | operation           | operati        | on    | operation   |  |  |

| <u>Exan</u>                                                                                                                                                                                                                   | <u>nple:</u>                             | HERE                | BRA J          | Jump  |             |  |  |

|                                                                                                                                                                                                                               | Before Instruc<br>PC<br>After Instructio | = ad                | dress (H       | IERE) |             |  |  |

|                                                                                                                                                                                                                               | PC                                       | = ad                | dress (J       | ſump) |             |  |  |

| BSF                                                                         | Bit Set f                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                     |  |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|--|--|--|