Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 24KB (12K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2455-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### Pin Number Pin Buffer Pin Name Description Туре Type PDIP. SOIC PORTC is a bidirectional I/O port. RC0/T10SO/T13CKI 11 I/O Digital I/O. RC0 ST **T10S0** Timer1 oscillator output. Ο T13CKI ST Timer1/Timer3 external clock input. I RC1/T1OSI/CCP2/UOE 12 I/O Digital I/O. RC1 ST T10SI Timer1 oscillator input. T CMOS CCP2<sup>(2)</sup> Capture 2 input/Compare 2 output/PWM2 output. I/O ST UOE External USB transceiver OE output. 0 RC2/CCP1 13 I/O ST Digital I/O. RC2 CCP1 Capture 1 input/Compare 1 output/PWM1 output. I/O ST RC4/D-/VM 15 RC4 T TTL Digital input. D-I/O USB differential minus line (input/output). TTL External USB transceiver VM input. VM T RC5/D+/VP 16 RC5 TTL Digital input. I I/O USB differential plus line (input/output). D+ VP TTL External USB transceiver VP input. 0 RC6/TX/CK 17 I/O ST Digital I/O. RC6 EUSART asynchronous transmit. TΧ 0 CK I/O ST EUSART synchronous clock (see RX/DT). RC7/RX/DT/SDO 18 I/O ST RC7 Digital I/O. RX EUSART asynchronous receive. ST Ι DT I/O ST EUSART synchronous data (see TX/CK). SDO SPI data out. 0 \_\_\_\_ RE3 See MCLR/VPP/RE3 pin. **VUSB** 14 Ρ Internal USB 3.3V voltage regulator output, positive supply for internal USB transceiver. Vss 8, 19 Ρ Ground reference for logic and I/O pins. Vdd 20 Ρ Positive supply for logic and I/O pins. Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels = Input Т

### TABLE 1-2: PIC18F2455/2550 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output P = Power

**Note 1:** Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared.

2: Default assignment for CCP2 when CCP2MX Configuration bit is set.

## 2.2.5.4 Compensating for INTOSC Drift

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made and in some cases, how large a change is needed. When using the EUSART, for example, an adjustment may be required when it begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

It is also possible to verify device clock speed against a reference clock. Two timers may be used: one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator. Both timers are cleared but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register. Finally, a CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

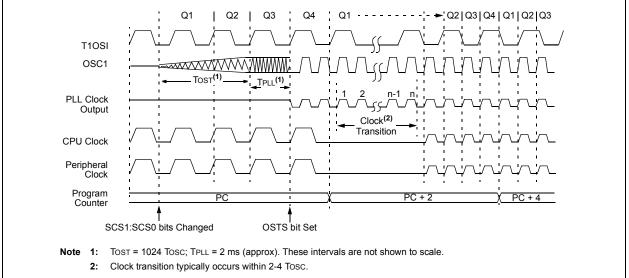

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register. SEC\_RUN mode is entered by setting the SCS1:SCS0 bits to '01'. The device clock source is switched to the Timer1 oscillator (see Figure 3-1), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

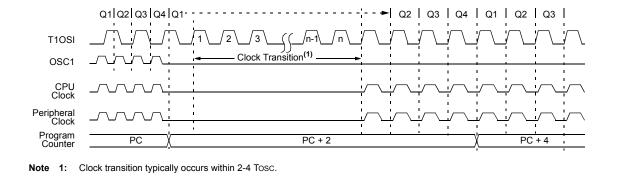

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS1:SCS0 bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result. On transitions from SEC\_RUN mode to PRI\_RUN, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-2). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

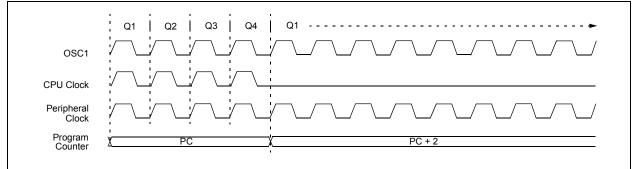

## 3.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes in that it does not disable the primary device clock. For timing sensitive applications, this allows for the fastest resumption of device operation, with its more accurate primary clock source, since the clock source does not have to "warm up" or transition from another oscillator.

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC3:FOSC0 Configuration bits. The OSTS bit remains set (see Figure 3-7).

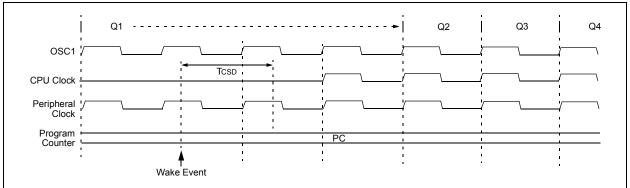

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 3-8).

## 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then set SCS1:SCS0 to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 3-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

## FIGURE 3-7: TRANSITION TIMING FOR ENTRY TO IDLE MODE

### FIGURE 3-8: TRANSITION TIMING FOR WAKE FROM IDLE TO RUN MODE

NOTES:

| Pin        | Function | TRIS<br>Setting | I/O | I/O Type | Description                                                                            |  |  |  |  |

|------------|----------|-----------------|-----|----------|----------------------------------------------------------------------------------------|--|--|--|--|

| RC7/RX/DT/ | RC7      | 0               | OUT | DIG      | LATC<7> data output.                                                                   |  |  |  |  |

| SDO        |          | 1               | IN  | ST       | PORTC<7> data input.                                                                   |  |  |  |  |

|            | RX       | 1               | IN  | ST       | Asynchronous serial receive data input (EUSART module).                                |  |  |  |  |

|            | DT       | 1               | OUT | DIG      | Synchronous serial data output (EUSART module); takes priority over SPI and port data. |  |  |  |  |

|            |          | 1               | IN  | ST       | Synchronous serial data input (EUSART module). User must configure as an input.        |  |  |  |  |

|            | SDO      | 0               | OUT | DIG      | SPI data output (MSSP module); takes priority over port data.                          |  |  |  |  |

## TABLE 10-5: PORTC I/O SUMMARY (CONTINUED)

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input,

TTL = TTL Buffer Input, XCVR = USB transceiver, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: Default pin assignment. Alternate pin assignment is RB3 (when CCP2MX = 0).

2: RC4 and RC5 do not have corresponding TRISC bits. In Port mode, these pins are input only. USB data direction is determined by the USB configuration.

**3:** 40/44-pin devices only.

### TABLE 10-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7  | Bit 6  | Bit 5              | Bit 4              | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|-------|--------|--------|--------------------|--------------------|-------|--------|--------|--------|----------------------------|

| PORTC | RC7    | RC6    | RC5 <sup>(1)</sup> | RC4 <sup>(1)</sup> |       | RC2    | RC1    | RC0    | 56                         |

| LATC  | LATC7  | LATC6  | _                  | —                  | _     | LATC2  | LATC1  | LATC0  | 56                         |

| TRISC | TRISC7 | TRISC6 |                    | _                  | —     | TRISC2 | TRISC1 | TRISC0 | 56                         |

| UCON  | _      | PPBRST | SE0                | PKTDIS             | USBEN | RESUME | SUSPND | _      | 57                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTC.

Note 1: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

| Name   | Bit 7                           | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|---------------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                        | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR1   | SPPIF <sup>(1)</sup>            | ADIF      | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 56                         |

| PIE1   | SPPIE <sup>(1)</sup>            | ADIE      | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 56                         |

| IPR1   | SPPIP <sup>(1)</sup>            | ADIP      | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 56                         |

| TMR1L  | TMR1L Timer1 Register Low Byte  |           |         |         |         |        |        |        |                            |

| TMR1H  | TMR1H TImer1 Register High Byte |           |         |         |         |        |        |        |                            |

| T1CON  | RD16                            | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 54                         |

## TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

The BDnSTAT byte of the BDT should always be the last byte updated when preparing to arm an endpoint. The SIE will clear the UOWN bit when a transaction has completed. The only exception to this is when KEN is enabled and/or BSTALL is enabled.

No hardware mechanism exists to block access when the UOWN bit is set. Thus, unexpected behavior can occur if the microcontroller attempts to modify memory when the SIE owns it. Similarly, reading such memory may produce inaccurate data until the USB peripheral returns ownership to the microcontroller.

### 17.4.1.2 BDnSTAT Register (CPU Mode)

When UOWN = 0, the microcontroller core owns the BD. At this point, the other seven bits of the register take on control functions.

The Keep Enable bit, KEN (BDnSTAT<5>), determines if a BD stays enabled. If the bit is set, once the UOWN bit is set, it will remain owned by the SIE independent of the endpoint activity. This prevents the USTAT FIFO from being updated, as well as the transaction complete interrupt from being set for the endpoint. This feature should only be enabled when the Streaming Parallel Port is selected as the data I/O channel instead of USB RAM.

The Address Increment Disable bit, INCDIS (BDnSTAT<4>), controls the SIE's automatic address increment function. Setting INCDIS disables the auto-increment of the buffer address by the SIE for each byte transmitted or received. This feature should only be enabled when using the Streaming Parallel Port, where each data byte is processed to or from the same memory location.

The Data Toggle Sync Enable bit, DTSEN (BDnSTAT<3>), controls data toggle parity checking. Setting DTSEN enables data toggle synchronization by

the SIE. When enabled, it checks the data packet's parity against the value of DTS (BDnSTAT<6>). If a packet arrives with an incorrect synchronization, the data will essentially be ignored. It will not be written to the USB RAM and the USB transfer complete interrupt flag will not be set. The SIE will send an ACK token back to the host to Acknowledge receipt, however. The effects of the DTSEN bit on the SIE are summarized in Table 17-3.

The Buffer Stall bit, BSTALL (BDnSTAT<2>), provides support for control transfers, usually one-time stalls on Endpoint 0. It also provides support for the SET\_FEATURE/CLEAR\_FEATURE commands specified in Chapter 9 of the USB specification; typically, continuous STALLs to any endpoint other than the default control endpoint.

The BSTALL bit enables buffer stalls. Setting BSTALL causes the SIE to return a STALL token to the host if a received token would use the BD in that location. The EPSTALL bit in the corresponding UEPn control register is set and a STALL interrupt is generated when a STALL is issued to the host. The UOWN bit remains set and the BDs are not changed unless a SETUP token is received. In this case, the STALL condition is cleared and the ownership of the BD is returned to the microcontroller core.

The BD9:BD8 bits (BDnSTAT<1:0>) store the two most significant digits of the SIE byte count; the lower 8 digits are stored in the corresponding BDnCNT register. See **Section 17.4.2 "BD Byte Count"** for more information.

| OUT Packet         | BDnSTAT | Settings | ſ         | Device Response after Receiving Packet |       |                          |  |  |

|--------------------|---------|----------|-----------|----------------------------------------|-------|--------------------------|--|--|

| from Host          | DTSEN   | DTS      | Handshake | UOWN                                   | TRNIF | BDnSTAT and USTAT Status |  |  |

| DATA0              | 1       | 0        | ACK       | 0                                      | 1     | Updated                  |  |  |

| DATA1              | 1       | 0        | ACK       | 1                                      | 0     | Not Updated              |  |  |

| DATA1              | 1       | 1        | ACK       | 0                                      | 1     | Updated                  |  |  |

| DATA0              | 1       | 1        | ACK       | 1                                      | 0     | Not Updated              |  |  |

| Either             | 0       | х        | ACK       | 0                                      | 1     | Updated                  |  |  |

| Either, with error | х       | Х        | NAK       | 1                                      | 0     | Not Updated              |  |  |

## TABLE 17-3: EFFECT OF DTSEN BIT ON ODD/EVEN (DATA0/DATA1) PACKET RECEPTION

**Legend:** x = don't care

## 18.0 STREAMING PARALLEL PORT

| Note: | The   | Streaming    | Parallel   | Port | is | only |

|-------|-------|--------------|------------|------|----|------|

|       | avail | able on 40/4 | 4-pin devi | ces. |    |      |

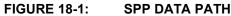

PIC18F4455/4550 USB devices provide a Streaming Parallel Port as a high-speed interface for moving data to and from an external system. This parallel port operates as a master port, complete with chip select and clock outputs to control the movement of data to slave devices. Data can be channelled either directly to the USB SIE or to the microprocessor core. Figure 18-1 shows a block view of the SPP data path.

In addition, the SPP can provide time multiplexed addressing information along with the data by using the second strobe output. Thus, the USB endpoint number can be written in conjunction with the data for that endpoint.

## 18.1 SPP Configuration

The operation of the SPP is controlled by two registers: SPPCON and SPPCFG. The SPPCON register (Register 18-1) controls the overall operation of the parallel port and determines if it operates under USB or microcontroller control. The SPPCFG register (Register 18-2) controls timing configuration and pin outputs.

### 18.1.1 ENABLING THE SPP

To enable the SPP, set the SPPEN bit (SPPCON<0>). In addition, the TRIS bits for the corresponding SPP pins must be properly configured. At a minimum:

- Bits TRISD<7:0> must be set (= 1)

- Bits TRISE<2:1> must be cleared (= 0)

- If CK1SPP is to be used:

- Bit TRISE<0> must be cleared (= 0)

- If CSPP is to be used:

- Bit TRISB<4> must be cleared (= 0)

## REGISTER 18-1: SPPCON: SPP CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0 |

|-------|-----|-----|-----|-----|-----|--------|-------|

| —     | —   | —   | —   | —   | —   | SPPOWN | SPPEN |

| bit 7 |     |     |     |     |     |        | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| Unimplemented: Read as '0'                                                                                  |

|-------------------------------------------------------------------------------------------------------------|

| SPPOWN: SPP Ownership bit                                                                                   |

| <ul><li>1 = USB peripheral controls the SPP</li><li>0 = Microcontroller directly controls the SPP</li></ul> |

| SPPEN: SPP Enable bit                                                                                       |

| 1 = SPP is enabled<br>0 = SPP is disabled                                                                   |

|                                                                                                             |

| R/W-0           | R/W-0                                            | R/W-0                                                                 | R/W-0          | R/W-0            | R/W-0            | R/W-0             | R/W-0              |

|-----------------|--------------------------------------------------|-----------------------------------------------------------------------|----------------|------------------|------------------|-------------------|--------------------|

| GCEN            | ACKSTAT                                          | ADMSK5                                                                | ADMSK4         | ADMSK3           | ADMSK2           | ADMSK1            | SEN <sup>(1)</sup> |

| bit 7           |                                                  |                                                                       |                |                  |                  |                   | bit (              |

| Legend:         |                                                  |                                                                       |                |                  |                  |                   |                    |

| R = Readable    | bit                                              | W = Writable                                                          | bit            | U = Unimpler     | nented bit, read | as '0'            |                    |

| -n = Value at F | POR                                              | '1' = Bit is set                                                      |                | '0' = Bit is cle |                  | x = Bit is unkn   | own                |

| bit 7           | 1 = Enable int                                   | al Call Enable<br>errupt when a<br>all address dis                    | general call a | 37               | ) is received in | the SSPSR         |                    |

| bit 6           | ACKSTAT: Ac<br>Unused in Sla                     | knowledge Sta                                                         | atus bit       |                  |                  |                   |                    |

| bit 5-2         | 1 = Masking o                                    | MSK2: Slave A<br>of correspondir<br>of correspondir                   | ig bits of SSP | ADD enabled      |                  |                   |                    |

| bit 1           | In 7-Bit Addre                                   | ave Address M<br><u>ssing mode:</u><br>of SPADD<1> o<br>of SPADD<1> o | only enabled   |                  |                  |                   |                    |

|                 |                                                  | <u>essing mode:</u><br>of SSPADD<1:0<br>of SSPADD<1:0                 |                |                  |                  |                   |                    |

| bit 0           | SEN: Stretch<br>1 = Clock stre<br>0 = Clock stre | tching is enab                                                        |                | ave transmit ar  | id slave receive | e (stretch enable | ed)                |

## REGISTER 19-6: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> SLAVE MODE)

**Note 1:** If the I<sup>2</sup>C module is active, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

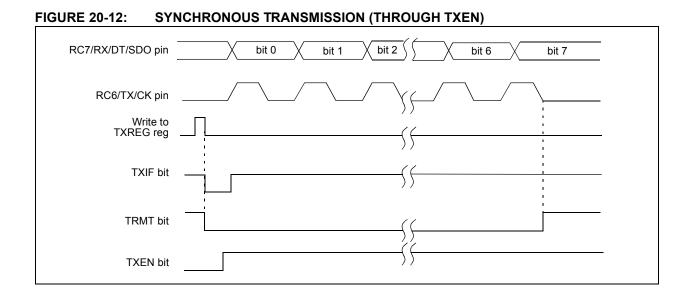

### TABLE 20-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name                                                 | Bit 7                | Bit 6       | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|------------------------------------------------------|----------------------|-------------|-------------|------------|-------|--------|--------|--------|----------------------------|

| INTCON                                               | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR1                                                 | SPPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIF       | SSPIF | CCP1IF | TMR2IF | TMR1IF | 56                         |

| PIE1                                                 | SPPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE       | SSPIE | CCP1IE | TMR2IE | TMR1IE | 56                         |

| IPR1                                                 | SPPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP       | SSPIP | CCP1IP | TMR2IP | TMR1IP | 56                         |

| RCSTA                                                | SPEN                 | RX9         | SREN        | CREN       | ADDEN | FERR   | OERR   | RX9D   | 55                         |

| TXREG                                                | EUSART T             | ransmit Reg | ister       |            |       |        |        |        | 55                         |

| TXSTA                                                | CSRC                 | TX9         | TXEN        | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 55                         |

| BAUDCON                                              | ABDOVF               | RCIDL       | RXDTP       | TXCKP      | BRG16 | —      | WUE    | ABDEN  | 55                         |

| SPBRGH EUSART Baud Rate Generator Register High Byte |                      |             |             |            |       |        |        |        | 55                         |

| SPBRG                                                | EUSART E             | aud Rate G  | enerator Re | gister Low | Byte  |        |        |        | 55                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** Reserved in 28-pin devices; always maintain these bits clear.

## 23.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 23-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

## 23.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be

used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR3:CVR0), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = ((CVR3:CVR0)/24) x CVRSRC <u>If CVRR = 0:</u> CVREF = (CVRSRC/4) + (((CVR3:CVR0)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 28-3 in **Section 28.0 "Electrical Characteristics"**).

## **REGISTER 23-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

| R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------------------|-------|-------|-------|-------|-------|-------|

| CVREN | CVROE <sup>(1)</sup> | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 |                      |       |       |       |       |       | bit 0 |

| Legend:           |                                                                    |                      |                    |  |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |  |

| CVREN: Comparator Voltage Reference Enable bit                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = CVREF circuit powered on</li> <li>0 = CVREF circuit powered down</li> </ul>                                                                                                                                           |

| CVROE: Comparator VREF Output Enable bit <sup>(1)</sup>                                                                                                                                                                            |

| <ul> <li>1 = CVREF voltage level is also output on the RA2/AN2/VREF-/CVREF pin</li> <li>0 = CVREF voltage is disconnected from the RA2/AN2/VREF-/CVREF pin</li> </ul>                                                              |

| CVRR: Comparator VREF Range Selection bit                                                                                                                                                                                          |

| <ul> <li>1 = 0 to 0.667 CVRSRC, with CVRSRC/24 step size (low range)</li> <li>0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size (high range)</li> </ul>                                                                     |

| CVRSS: Comparator VREF Source Selection bit                                                                                                                                                                                        |

| <ul> <li>1 = Comparator reference source, CVRSRC = (VREF+) – (VREF-)</li> <li>0 = Comparator reference source, CVRSRC = VDD – VSS</li> </ul>                                                                                       |

| <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits ( $0 \le (CVR3:CVR0) \le 15$ )<br><u>When CVRR = 1:</u><br>CVREF = ((CVR3:CVR0)/24) • (CVRSRC)<br><u>When CVRR = 0:</u><br>CVREF = (CVRSRC/4) + ((CVR3:CVR0)/32) • (CVRSRC) |

|                                                                                                                                                                                                                                    |

Note 1: CVROE overrides the TRISA<2> bit setting.

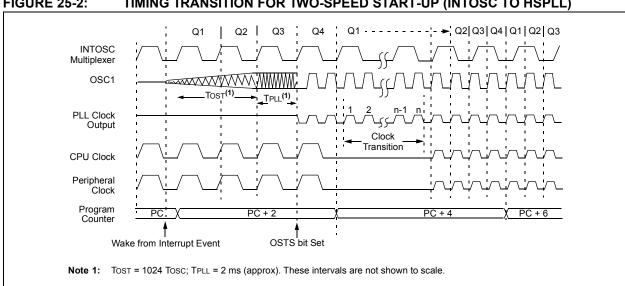

#### 25.3 **Two-Speed Start-up**

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is XT, HS, XTPLL or HSPLL (Crystal-Based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI RUN mode.

Because the OSCCON register is cleared on Reset events, the INTOSC (or postscaler) clock source is not initially available after a Reset event; the INTRC clock is used directly at its base frequency. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF2:IRCF0, immediately after

Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IRCF2:IRCF0 prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 25.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to Section 3.1.4 "Multiple Sleep Commands"). In practice, this means that user code can change the SCS1:SCS0 bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

#### **FIGURE 25-2:** TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

| LFSF                                                                                              | र                                               |            | Load FSR                                                           |                 |   |             |                             |  |  |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|--------------------------------------------------------------------|-----------------|---|-------------|-----------------------------|--|--|

| Synta                                                                                             | ax:                                             |            | LFSR f, l                                                          | ĸ               |   |             |                             |  |  |

| Oper                                                                                              | ands:                                           |            | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | 95              |   |             |                             |  |  |

| Operation:                                                                                        |                                                 | $k\toFSRf$ |                                                                    |                 |   |             |                             |  |  |

| Statu                                                                                             | s Affected:                                     |            | None                                                               |                 |   |             |                             |  |  |

| Enco                                                                                              | ding:                                           |            | 1110<br>1111                                                       | 1110<br>0000    | - | Off<br>7kkk | k <sub>11</sub> kkk<br>kkkk |  |  |

| Description: The 12-bit literal 'k' is loaded into the<br>File Select Register pointed to by 'f'. |                                                 |            |                                                                    |                 |   |             |                             |  |  |

| Words: 2                                                                                          |                                                 |            |                                                                    |                 |   |             |                             |  |  |

| Cycles: 2                                                                                         |                                                 |            |                                                                    |                 |   |             |                             |  |  |

| QC                                                                                                | ycle Activity:                                  |            |                                                                    |                 |   |             |                             |  |  |

|                                                                                                   | Q1                                              |            | Q2                                                                 | Q3              |   |             | Q4                          |  |  |

|                                                                                                   | Decode                                          |            | ad literal<br>k' MSB                                               | Process<br>Data | 3 | literal     | /rite<br>'k' MSB<br>'SRfH   |  |  |

|                                                                                                   | Decode                                          |            | ad literal<br>k' LSB                                               | Process<br>Data |   |             | literal 'k'<br>SRfL         |  |  |

|                                                                                                   |                                                 | I          | N LOD                                                              | Daid            |   | ισr         | JIVIE                       |  |  |

|                                                                                                   | Example: LFSR 2, 3ABh                           |            |                                                                    |                 |   |             |                             |  |  |

|                                                                                                   | After Instruction<br>FSR2H = 03h<br>FSR2L = ABh |            |                                                                    |                 |   |             |                             |  |  |

| MOVF                                       | Move f                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Syntax:                                    | MOVF f{,                                                                                                                                                                                                        | d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |  |  |  |  |  |

| Operands:                                  | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                             | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |  |  |  |  |  |

| Operation:                                 | $f \to \text{dest}$                                                                                                                                                                                             | $f \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |  |  |  |  |  |

| Status Affected:                           | N, Z                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

| Encoding:                                  | 0101                                                                                                                                                                                                            | 00da ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ff ffff |  |  |  |  |  |

|                                            | placed in W<br>placed back<br>Location 'f'<br>256-byte ba<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank (<br>If 'a' is '0' al<br>set is enabl<br>in Indexed I<br>mode when<br>Section 26<br>Bit-Oriente | a destination dependent upon the<br>status of 'd'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>Location 'f' can be anywhere in the<br>256-byte bank.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |         |  |  |  |  |  |

| Words:                                     | 1                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

| Cycles:                                    | 1                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

| Q Cycle Activity:                          |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

| Q1                                         | Q2                                                                                                                                                                                                              | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q4      |  |  |  |  |  |

| Decode                                     | Read<br>register 'f'                                                                                                                                                                                            | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Write W |  |  |  |  |  |

| Example:                                   | MOVF RE                                                                                                                                                                                                         | EG, 0, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |  |  |  |  |  |

| Before Instruction<br>REG = 22h<br>W = FFh |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

= = 22h 22h

After Instruction REG W

| MOVFF                                                | Move f to                                                                                                                                                                                                                | f                                                                                                                                                                                  |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| Syntax:                                              | MOVFF f                                                                                                                                                                                                                  | MOVFF f <sub>s</sub> ,f <sub>d</sub>                                                                                                                                               |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 40 \\ 0 \leq f_d \leq 40 \end{array}$                                                                                                                                                  |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Operation:                                           | $(f_{\text{s}}) \rightarrow f_{\text{d}}$                                                                                                                                                                                |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                                     |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                             | ffff<br>ffff                                                                                                                                                                       | ffff<br>ffff                                                                                                                                                 | ffff <sub>s</sub><br>ffff <sub>d</sub>                                                                                                      |   |  |  |  |

| Description:                                         | The conter<br>moved to a<br>Location o<br>in the 4096<br>FFFh) and<br>can also b<br>FFFh.<br>Either sou<br>(a useful s<br>MOVFF is p<br>transferrin<br>peripheral<br>buffer or a<br>The MOVFT<br>PCL, TOS<br>destinatior | destinatio<br>f source "<br>6-byte dat<br>l location<br>e anywhe<br>rce or des<br>pecial situ<br>particularly<br>g a data n<br>register (s<br>n I/O port<br>F instructi<br>U, TOSH | n register<br>$f_s$ ' can be<br>a space (<br>of destina<br>re from 0<br>stination c<br>uation).<br>y useful for<br>hemory lo<br>such as th<br>).<br>on canno | 'f <sub>d</sub> '.<br>anywhere<br>000h to<br>tition 'f <sub>d</sub> '<br>00h to<br>an be W<br>or<br>cation to a<br>he transmit<br>t use the |   |  |  |  |

| Words:                                               | 2                                                                                                                                                                                                                        |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Cycles:                                              | 2                                                                                                                                                                                                                        |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                          |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |  |  |  |

| Q1                                                   | Q2                                                                                                                                                                                                                       | Q3                                                                                                                                                                                 | 8                                                                                                                                                            | Q4                                                                                                                                          | 7 |  |  |  |

| Decode                                               | Read                                                                                                                                                                                                                     | Droce                                                                                                                                                                              |                                                                                                                                                              | No                                                                                                                                          |   |  |  |  |

| MOVLB                                    | Move Liter                                            | al to Lo               | w Nibl            | ble i           | n BSR                 |  |  |  |

|------------------------------------------|-------------------------------------------------------|------------------------|-------------------|-----------------|-----------------------|--|--|--|

| Syntax:                                  | MOVLW k                                               | Ι.                     |                   |                 |                       |  |  |  |

| Operands:                                | $0 \le k \le 255$                                     | $0 \leq k \leq 255$    |                   |                 |                       |  |  |  |

| Operation:                               | $k \rightarrow BSR$                                   |                        |                   |                 |                       |  |  |  |

| Status Affected:                         | None                                                  |                        |                   |                 |                       |  |  |  |

| Encoding:                                | 0000 0001 kkkk kkkk                                   |                        |                   |                 |                       |  |  |  |

| Description:                             | The eight-b<br>Bank Selec<br>of BSR<7:4<br>regardless | t Registe<br>I> always | er (BSF<br>s rema | R). T<br>ains ' | <b>he value</b><br>0' |  |  |  |

| Words:                                   | 1                                                     | 1                      |                   |                 |                       |  |  |  |

| Cycles:                                  | 1                                                     |                        |                   |                 |                       |  |  |  |

| Q Cycle Activity:                        |                                                       |                        |                   |                 |                       |  |  |  |

| Q1                                       | Q2                                                    | Q3                     |                   |                 | Q4                    |  |  |  |

| Decode                                   | Read<br>literal 'k'                                   | Proce<br>Data          |                   |                 | te literal<br>to BSR  |  |  |  |

| Example:                                 | MOVLB                                                 | 5                      |                   |                 |                       |  |  |  |

| Before Instruction<br>BSR Register = 02h |                                                       |                        |                   |                 |                       |  |  |  |

05h

After Instruction

BSR Register =

| Q1     | Q2                                  | Q3              | Q4                              |

|--------|-------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)       | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

| Example:    | MOVFF     | REG1, | REG2 |

|-------------|-----------|-------|------|

| Externiorer | 110 1 1 1 | imor, | 1000 |

| Before Instruction |   |     |

|--------------------|---|-----|

| REG1               | = | 33h |

| REG2               | = | 11h |

| After Instruction  |   |     |

| REG1               | = | 33h |

| REG2               | = | 33h |

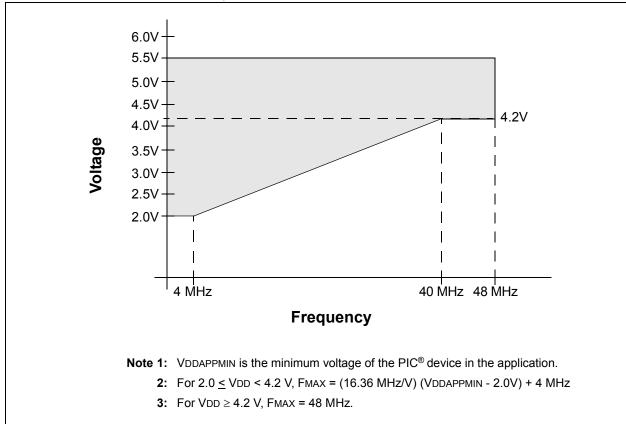

## FIGURE 28-2: PIC18LF2455/2550/4455/4550 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL LOW VOLTAGE)

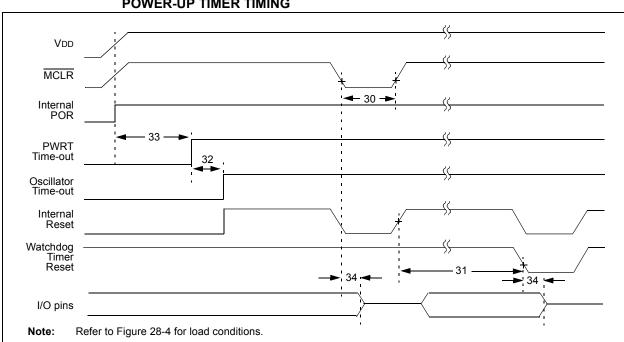

# FIGURE 28-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

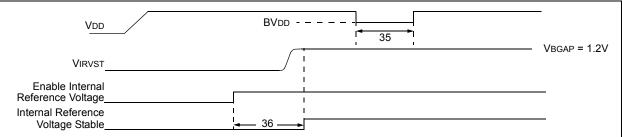

## FIGURE 28-8: BROWN-OUT RESET TIMING

## TABLE 28-12:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                              | Min       | Тур  | Мах       | Units | Conditions                    |

|---------------|--------|-------------------------------------------------------------|-----------|------|-----------|-------|-------------------------------|

| 30            | TmcL   | MCLR Pulse Width (low)                                      | 2         | _    | _         | μS    |                               |

| 31            | Twdt   | Watchdog Timer Time-out Period<br>(no postscaler)           | 3.5       | 4.1  | 4.8       | ms    |                               |

| 32            | Tost   | Oscillator Start-up Timer Period                            | 1024 Tosc |      | 1024 Tosc | —     | Tosc = OSC1 period            |

| 33            | TPWRT  | Power-up Timer Period                                       | 57.0      | 65.5 | 77.1      | ms    |                               |

| 34            | Tioz   | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset | _         | 2    | _         | μS    |                               |

| 35            | TBOR   | Brown-out Reset Pulse Width                                 | 200       |      | —         | μS    | $VDD \le BVDD$ (see D005)     |

| 36            | TIRVST | Time for Internal Reference<br>Voltage to become Stable     | —         | 20   | 50        | μS    |                               |

| 37            | Tlvd   | Low-Voltage Detect Pulse Width                              | 200       | _    | _         | μS    | $V\text{DD} \leq V\text{LVD}$ |

| 38            | TCSD   | CPU Start-up Time                                           | 5         | _    | 10        | μS    |                               |

| 39            | TIOBST | Time for INTOSC to Stabilize                                | —         | 1    | —         | ms    |                               |

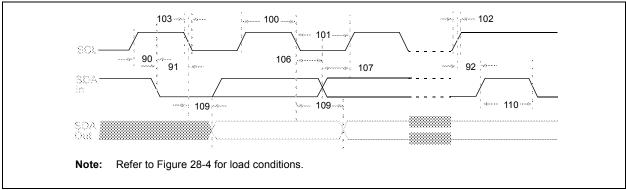

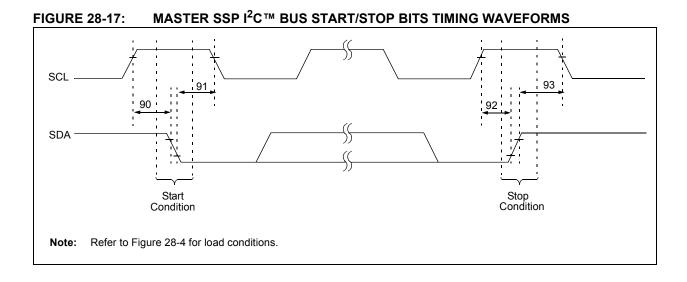

TABLE 28-21: MASTER SSP I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Characteristic  |                           | Min              | Max | Units | Conditions             |

|---------------|---------|-----------------|---------------------------|------------------|-----|-------|------------------------|

| 90            | Tsu:sta | Start Condition | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    | Only relevant for      |

|               |         | Setup Time      | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       | Repeated Start         |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       | condition              |

| 91            | THD:STA | Start Condition | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    | After this period, the |

|               |         | Hold Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) |     |       | first clock pulse is   |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |     |       | generated              |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                        |

|               |         | Setup Time      | 400 kHz mode              | 2(Tosc)(BRG + 1) |     |       |                        |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       |                        |

| 93            | THD:STO | Stop Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                        |

|               |         | Hold Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) |     | 1     |                        |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |     |       |                        |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins.

## FIGURE 28-18: MASTER SSP I<sup>2</sup>C™ BUS DATA TIMING