#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 24KB (12K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2455-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nama                           | Pin Number |     |      | Pin Buffer      | Description |                                                                                                                                               |

|------------------------------------|------------|-----|------|-----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                           | PDIP       | QFN | TQFP | Туре            | Туре        | Description                                                                                                                                   |

|                                    |            |     |      |                 |             | PORTD is a bidirectional I/O port or a Streaming<br>Parallel Port (SPP). These pins have TTL input buffers<br>when the SPP module is enabled. |

| RD0/SPP0<br>RD0<br>SPP0            | 19         | 38  | 38   | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.                                                                                                 |

| RD1/SPP1<br>RD1<br>SPP1            | 20         | 39  | 39   | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.                                                                                                 |

| RD2/SPP2<br>RD2<br>SPP2            | 21         | 40  | 40   | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.                                                                                                 |

| RD3/SPP3<br>RD3<br>SPP3            | 22         | 41  | 41   | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.                                                                                                 |

| RD4/SPP4<br>RD4<br>SPP4            | 27         | 2   | 2    | I/O<br>I/O      | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.                                                                                                 |

| RD5/SPP5/P1B<br>RD5<br>SPP5<br>P1B | 28         | 3   | 3    | I/O<br>I/O<br>O | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.<br>Enhanced CCP1 PWM output, channel B.                                                         |

| RD6/SPP6/P1C<br>RD6<br>SPP6<br>P1C | 29         | 4   | 4    | I/O<br>I/O<br>O | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.<br>Enhanced CCP1 PWM output, channel C.                                                         |

| RD7/SPP7/P1D<br>RD7<br>SPP7<br>P1D | 30         | 5   | 5    | I/O<br>I/O<br>O | ST<br>TTL   | Digital I/O.<br>Streaming Parallel Port data.<br>Enhanced CCP1 PWM output, channel D.                                                         |

#### TABLE 1-3: PIC18F4455/4550 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared.

= Output

0

2: Default assignment for CCP2 when CCP2MX Configuration bit is set.

**3:** These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

Р

= Power

NOTES:

NOTES:

### 15.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP2 pin is multiplexed with a PORTB or PORTC data latch, the appropriate TRIS bit must be cleared to make the CCP2 pin an output.

| Note: | Clearing the CCP2CON register will force<br>the RB3 or RC1 output latch (depending<br>on device configuration) to the default low |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

|       | level. This is not the PORTB or PORTC<br>I/O data latch.                                                                          |

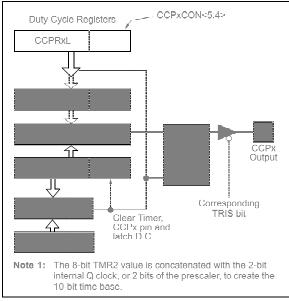

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.4.4** "Setup for PWM Operation".

#### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

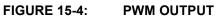

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 15-1:

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set (exception: if PWM duty cycle = 0%, the CCPx pin will not be set)

- The PWM duty cycle is latched from CCPRxL into CCPRxH

### 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> bits contain the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 15-2:**

```

PWM Duty Cycle = (CCPRxL:CCPxCON<5:4>) •

Tosc • (TMR2 Prescale Value)

```

CCPRxL and CCPxCON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPRxH until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

#### 16.4.6 PROGRAMMABLE DEAD-BAND DELAY

| Note: | Programmable | de  | ad-band | delay   | is | not  |

|-------|--------------|-----|---------|---------|----|------|

|       | implemented  | in  | 28-pin  | devices | 5  | with |

|       | standard CCP | moc | lules.  |         |    |      |

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 16-4 for illustration. Bits PDC6:PDC0 of the ECCP1DEL register (Register 16-2) set the delay period in terms of microcontroller instruction cycles (TCY or 4 TOSC). These bits are not available on 28-pin devices, as the standard CCP module does not support half-bridge operation.

#### 16.4.7 ENHANCED PWM AUTO-SHUTDOWN

When ECCP is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the comparator modules, a low level on the RB0/AN12/INT0/FLT0/SDI/SDA pin, or any combination of these three sources. The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a digital signal on the INT0 pin can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS2:ECCPAS0 bits (bits<6:4> of the ECCP1AS register).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits (ECCP1AS3:ECCP1AS0). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

| R/W-0                             | R/W-0                                                                                  | R/W-0                                            | R/W-0                                                               | R/W-0                                                    | R/W-0               | R/W-0               | R/W-0               |  |

|-----------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------|---------------------|---------------------|---------------------|--|

| PRSEN                             | PDC6 <sup>(1)</sup>                                                                    | PDC5 <sup>(1)</sup>                              | PDC4 <sup>(1)</sup>                                                 | PDC3 <sup>(1)</sup>                                      | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |  |

| bit 7                             |                                                                                        |                                                  |                                                                     |                                                          |                     |                     | bit (               |  |

|                                   |                                                                                        |                                                  |                                                                     |                                                          |                     |                     |                     |  |

| Legend:                           |                                                                                        |                                                  |                                                                     |                                                          |                     |                     |                     |  |

| R = Readable bit W = Writable bit |                                                                                        |                                                  |                                                                     | U = Unimplem                                             | nented bit, read    | as '0'              |                     |  |

| -n = Value at P                   | -n = Value at POR '1' = Bit is set                                                     |                                                  |                                                                     | '0' = Bit is cleared x = Bit is unknown                  |                     |                     |                     |  |

| bit 7<br>bit 6-0                  | <ul> <li>1 = Upon aut<br/>the PWM</li> <li>0 = Upon aut</li> <li>PDC6:PDC0:</li> </ul> | l restarts autom<br>o-shutdown, E<br>PWM Delay C | e ECCPASE to<br>natically<br>CCPASE mus<br>ount bits <sup>(1)</sup> | bit clears autom<br>st be cleared in<br>) cycles, betwee | software to res     | tart the PWM        |                     |  |

#### REGISTER 16-2: ECCP1DEL: PWM DEAD-BAND DELAY REGISTER

**Note 1:** Reserved on 28-pin devices; maintain these bits clear.

| R/W-0           | R/W-0                                                    | R/W-0                                                                 | R/W-0          | R/W-0            | R/W-0            | R/W-0             | R/W-0              |  |  |

|-----------------|----------------------------------------------------------|-----------------------------------------------------------------------|----------------|------------------|------------------|-------------------|--------------------|--|--|

| GCEN            | ACKSTAT                                                  | ADMSK5                                                                | ADMSK4         | ADMSK3           | ADMSK2           | ADMSK1            | SEN <sup>(1)</sup> |  |  |

| bit 7           |                                                          |                                                                       |                |                  |                  |                   | bit (              |  |  |

| Legend:         |                                                          |                                                                       |                |                  |                  |                   |                    |  |  |

| R = Readable    | bit                                                      | W = Writable                                                          | bit            | U = Unimpler     | nented bit, read | as '0'            |                    |  |  |

| -n = Value at F | POR                                                      | '1' = Bit is set                                                      |                | '0' = Bit is cle |                  | x = Bit is unkn   | own                |  |  |

| bit 7           | 1 = Enable int                                           | al Call Enable<br>errupt when a<br>all address dis                    | general call a | 37               | ) is received in | the SSPSR         |                    |  |  |

| bit 6           | ACKSTAT: Acknowledge Status bit<br>Unused in Slave mode. |                                                                       |                |                  |                  |                   |                    |  |  |

| bit 5-2         | 1 = Masking o                                            | MSK2: Slave A<br>of correspondir<br>of correspondir                   | ig bits of SSP | ADD enabled      |                  |                   |                    |  |  |

| bit 1           | In 7-Bit Addre                                           | ave Address M<br><u>ssing mode:</u><br>of SPADD<1> o<br>of SPADD<1> o | only enabled   |                  |                  |                   |                    |  |  |

|                 |                                                          | <u>essing mode:</u><br>of SSPADD<1:0<br>of SSPADD<1:0                 |                |                  |                  |                   |                    |  |  |

| bit 0           | SEN: Stretch<br>1 = Clock stre<br>0 = Clock stre         | tching is enab                                                        |                | ave transmit ar  | id slave receive | e (stretch enable | ed)                |  |  |

## REGISTER 19-6: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> SLAVE MODE)

**Note 1:** If the I<sup>2</sup>C module is active, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

© 2009 Microchip Technology Inc.

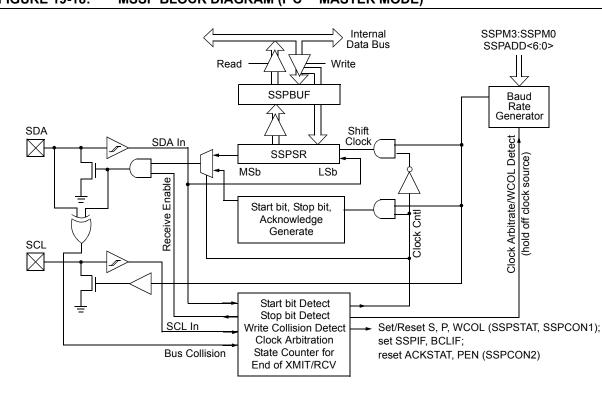

#### 19.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\sf I}^2{\sf C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options:

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (and MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

### FIGURE 19-18: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

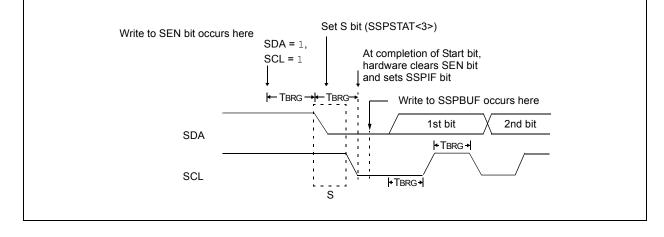

### 19.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 19.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing to the lower five bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 19-21: FIRST START BIT TIMING

#### 19.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 19-23).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 19.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 19.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL is clear after each write to SSPBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

#### 19.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

### 19.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The MSSP module must be in an Idle state   |

|-------|--------------------------------------------|

|       | before the RCEN bit is set or the RCEN bit |

|       | will be disregarded.                       |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 19.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 19.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 19.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### 25.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction, with the TBLPTR pointing to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File    | Name     | Bit 7 | Bit 6 | Bit 5                | Bit 4   | Bit 3                | Bit 2   | Bit 1   | Bit 0   | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|----------------------|---------|----------------------|---------|---------|---------|-----------------------------------|

| 300000h | CONFIG1L | -     | _     | USBDIV               | CPUDIV1 | CPUDIV0              | PLLDIV2 | PLLDIV1 | PLLDIV0 | 00 0000                           |

| 300001h | CONFIG1H | IESO  | FCMEN | —                    | _       | FOSC3                | FOSC2   | FOSC1   | FOSC0   | 00 0101                           |

| 300002h | CONFIG2L | _     | _     | VREGEN               | BORV1   | BORV0                | BOREN1  | BOREN0  | PWRTEN  | 01 1111                           |

| 300003h | CONFIG2H | _     | _     | _                    | WDTPS3  | WDTPS2               | WDTPS1  | WDTPS0  | WDTEN   | 1 1111                            |

| 300005h | CONFIG3H | MCLRE | _     | _                    | _       | _                    | LPT1OSC | PBADEN  | CCP2MX  | 1011                              |

| 300006h | CONFIG4L | DEBUG | XINST | ICPRT <sup>(3)</sup> | _       | _                    | LVP     |         | STVREN  | 1001-1                            |

| 300008h | CONFIG5L | _     |       | _                    |         | CP3 <sup>(1)</sup>   | CP2     | CP1     | CP0     | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | _                    | _       | _                    | —       | _       | _       | 11                                |

| 30000Ah | CONFIG6L | —     | _     | —                    | _       | WRT3 <sup>(1)</sup>  | WRT2    | WRT1    | WRT0    | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC                 | _       | _                    | —       |         | _       | 111                               |

| 30000Ch | CONFIG7L | —     | _     | —                    | _       | EBTR3 <sup>(1)</sup> | EBTR2   | EBTR1   | EBTR0   | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | —                    | _       | —                    | —       | _       | _       | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0                 | REV4    | REV3                 | REV2    | REV1    | REV0    | ×××× ×××××(2)                     |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8                 | DEV7    | DEV6                 | DEV5    | DEV4    | DEV3    | 0001 0010(2)                      |

#### TABLE 25-1: CONFIGURATION BITS AND DEVICE IDs

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented in PIC18FX455 devices; maintain this bit set.

2: See Register 25-13 and Register 25-14 for DEVID values. DEVID registers are read-only and cannot be programmed by the user.

3: Available only on PIC18F4455/4550 devices in 44-pin TQFP packages. Always leave this bit clear in all other devices.

#### REGISTER 25-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| R/P-0         | R/P-0                                                                                                               | U-0                                  | U-0             | R/P-0                | R/P-1                | R/P-0                | R/P-1                |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

| IESO          | FCMEN                                                                                                               |                                      |                 | FOSC3 <sup>(1)</sup> | FOSC2 <sup>(1)</sup> | FOSC1 <sup>(1)</sup> | FOSC0 <sup>(1)</sup> |  |  |  |

| bit 7         | ·                                                                                                                   |                                      |                 |                      |                      |                      | bit                  |  |  |  |

|               |                                                                                                                     |                                      |                 |                      |                      |                      |                      |  |  |  |

| Legend:       |                                                                                                                     |                                      |                 |                      |                      |                      |                      |  |  |  |

| R = Readable  | e bit                                                                                                               | P = Programn                         | nable bit       | U = Unimplen         | nented bit, read     | as '0'               |                      |  |  |  |

| -n = Value wl | nen device is un                                                                                                    | orogrammed                           |                 | u = Unchange         | ed from progran      | nmed state           |                      |  |  |  |

|               |                                                                                                                     |                                      |                 |                      |                      |                      |                      |  |  |  |

| bit 7         | IESO: Interna                                                                                                       | al/External Osci                     | llator Switcho  | over bit             |                      |                      |                      |  |  |  |

|               |                                                                                                                     | Switchover mo                        |                 |                      |                      |                      |                      |  |  |  |

|               |                                                                                                                     | Switchover mo                        |                 |                      |                      |                      |                      |  |  |  |

| bit 6         | FCMEN: Fail-Safe Clock Monitor Enable bit                                                                           |                                      |                 |                      |                      |                      |                      |  |  |  |

|               | 1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled                                         |                                      |                 |                      |                      |                      |                      |  |  |  |

|               |                                                                                                                     |                                      |                 |                      |                      |                      |                      |  |  |  |

| bit 5-4       | •                                                                                                                   | ted: Read as '                       |                 | 1)                   |                      |                      |                      |  |  |  |

| bit 3-0       |                                                                                                                     | C0: Oscillator S                     |                 |                      |                      |                      |                      |  |  |  |

|               | 111x = HS o<br>110x = HS o                                                                                          | scillator, PLL er                    | habled (HSPL    | _L)                  |                      |                      |                      |  |  |  |

|               |                                                                                                                     | • •                                  | S oscillator us | sed by USB (IN       | THS)                 |                      |                      |  |  |  |

|               | 1011 = Internal oscillator, HS oscillator used by USB (INTHS)<br>1010 = Internal oscillator, XT used by USB (INTXT) |                                      |                 |                      |                      |                      |                      |  |  |  |

|               | 1001 = Internal oscillator, CLKO function on RA6, EC used by USB (INTCKO)                                           |                                      |                 |                      |                      |                      |                      |  |  |  |

|               |                                                                                                                     | · •                                  |                 |                      | by USB (INTIC        | D)                   |                      |  |  |  |

|               |                                                                                                                     | scillator, PLL er                    |                 |                      | · · · ·              |                      |                      |  |  |  |

|               |                                                                                                                     | scillator, PLL er<br>scillator, CLKO |                 |                      | (ECPIO)              |                      |                      |  |  |  |

|               |                                                                                                                     | scillator, port fu                   |                 |                      |                      |                      |                      |  |  |  |

|               | 001x = XT os                                                                                                        |                                      |                 |                      |                      |                      |                      |  |  |  |

|               |                                                                                                                     |                                      |                 | L)                   |                      |                      |                      |  |  |  |

**Note 1:** The microcontroller and USB module both use the selected oscillator as their clock source in XT, HS and EC modes. The USB module uses the indicated XT, HS or EC oscillator as its clock source whenever the microcontroller uses the internal oscillator.

### REGISTER 25-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0          | U-0                         | R/P-0                                                                                                                                                           | R/P-1                | R/P-1                    | R/P-1                 | R/P-1                 | R/P-1                 |  |  |  |  |

|--------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| _            | _                           | VREGEN                                                                                                                                                          | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup>     | BOREN1 <sup>(2)</sup> | BOREN0 <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |  |  |  |  |

| bit 7        | ŀ                           |                                                                                                                                                                 | •                    |                          |                       | •                     | bit 0                 |  |  |  |  |

|              |                             |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

| Legend:      |                             |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

| R = Readab   | le bit                      | P = Program                                                                                                                                                     | nable bit            | U = Unimpler             | nented bit, read      | l as '0'              |                       |  |  |  |  |

| -n = Value w | hen device is un            | orogrammed                                                                                                                                                      |                      | u = Unchang              | ed from progran       | nmed state            |                       |  |  |  |  |

|              |                             |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

| bit 7-6      | Unimplemen                  | ted: Read as '                                                                                                                                                  | 0'                   |                          |                       |                       |                       |  |  |  |  |

| bit 5        | VREGEN: US                  | B Internal Volt                                                                                                                                                 | age Regulato         | r Enable bit             |                       |                       |                       |  |  |  |  |

|              |                             | age regulator e                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

|              |                             | age regulator d                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

| bit 4-3      | BORV1:BOR                   | V0: Brown-out                                                                                                                                                   | Reset Voltage        | e bits <sup>(1)</sup>    |                       |                       |                       |  |  |  |  |

|              | 11 <b>= Minimun</b>         | n setting                                                                                                                                                       |                      |                          |                       |                       |                       |  |  |  |  |

|              | •                           |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

|              | •                           |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

|              | 00 <b>= Maximu</b>          | m setting                                                                                                                                                       |                      |                          |                       |                       |                       |  |  |  |  |

| bit 2-1      | BOREN1:BO                   | REN0: Brown-                                                                                                                                                    | out Reset Ena        | able bits <sup>(2)</sup> |                       |                       |                       |  |  |  |  |

|              | 11 = Brown-c                | out Reset enab                                                                                                                                                  | led in hardwai       | re only (SBOR            | EN is disabled)       |                       |                       |  |  |  |  |

|              |                             | 10 = Brown-out Reset enabled in hardware only and disabled in Sleep mode (SBOREN is disabled)                                                                   |                      |                          |                       |                       |                       |  |  |  |  |

|              |                             | <ul> <li>01 = Brown-out Reset enabled and controlled by software (SBOREN is enabled)</li> <li>00 = Brown-out Reset disabled in hardware and software</li> </ul> |                      |                          |                       |                       |                       |  |  |  |  |

| bit 0        |                             | ower-up Timer                                                                                                                                                   |                      | Te and soltwar           | e                     |                       |                       |  |  |  |  |

|              | 1 = PWRT dis                | •                                                                                                                                                               |                      |                          |                       |                       |                       |  |  |  |  |

|              | 1 = PWRT dis<br>0 = PWRT en |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

|              |                             |                                                                                                                                                                 |                      |                          |                       |                       |                       |  |  |  |  |

| Note 1: S    | ee Section 28.0             | "Electrical Ch                                                                                                                                                  | aracteristics        | " for the specif         | ications.             |                       |                       |  |  |  |  |

**2:** The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

#### REGISTER 25-11: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch)

| U-0        | U-0                                             | U-0            | U-0                    | R/C-1                | R/C-1            | R/C-1          | R/C-1 |

|------------|-------------------------------------------------|----------------|------------------------|----------------------|------------------|----------------|-------|

| _          | —                                               | —              | _                      | EBTR3 <sup>(1)</sup> | EBTR2            | EBTR1          | EBTR0 |

| bit 7      |                                                 |                |                        |                      |                  |                | bit 0 |

|            |                                                 |                |                        |                      |                  |                |       |

| Legend:    |                                                 |                |                        |                      |                  |                |       |

| R = Reada  | able bit                                        | C = Clearable  | e bit                  | U = Unimpler         | nented bit, read | as '0'         |       |

| -n = Value | when device is unp                              | programmed     |                        | u = Unchang          | ed from progran  | nmed state     |       |

|            |                                                 |                |                        |                      |                  |                |       |

| bit 7-4    | Unimplement                                     | ted: Read as ' | 0'                     |                      |                  |                |       |

| bit 3      | EBTR3: Table                                    | e Read Protect | ion bit <sup>(1)</sup> |                      |                  |                |       |

|            |                                                 |                |                        |                      | reads executed   |                |       |

|            | 0 = Block 3 (0                                  | 06000-007FFF   | h) protected           | from table read      | is executed in o | ther blocks    |       |

| bit 2      | EBTR2: Table                                    | Read Protect   | ion bit                |                      |                  |                |       |

|            |                                                 |                |                        |                      | reads executed   |                |       |

|            |                                                 |                |                        | from table read      | is executed in o | ther blocks    |       |

| bit 1      |                                                 | Read Protect   |                        |                      |                  |                |       |

|            |                                                 |                |                        |                      | e reads execute  |                | (S    |

|            |                                                 |                |                        | d from table re      | ads executed ir  | other blocks   |       |

| bit 0      |                                                 | Read Protect   |                        |                      |                  |                |       |

|            | •                                               |                | · ·                    |                      | le reads execut  |                | ks    |

|            | $\cup - \operatorname{BIOCK} \cup (\mathbf{U})$ |                | rii) is protecte       |                      | eads executed in | I OTHER DIOCKS |       |

| Note 1:    | Unimplemented in                                | PIC18FX455 c   | levices; maint         | ain this bit set.    |                  |                |       |

#### REGISTER 25-12: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

| U-0   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| —     | EBTRB | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                   |                   |                                     |

|---------------------------|-------------------|-------------------------------------|

| R = Readable bit          | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is | s unprogrammed    | u = Unchanged from programmed state |

bit 7 Unimplemented: Read as '0'

bit 6 **EBTRB:** Boot Block Table Read Protection bit

- 1 = Boot block (000000-0007FFh) is not protected from table reads executed in other blocks

- 0 = Boot block (000000-0007FFh) is protected from table reads executed in other blocks

- bit 5-0 Unimplemented: Read as '0'

#### TABLE 26-2: PIC18FXXXX INSTRUCTION SET

| Mnemonic,<br>Operands    |                                 | Description                              | Quality    | 16-Bit Instruction Word |      |      |      | Status                               | Nataa      |

|--------------------------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|------|--------------------------------------|------------|

|                          |                                 | Description                              | Cycles     | MSb                     |      |      | LSb  | Affected                             | Notes      |

| BYTE-ORIENTED OPERATIONS |                                 |                                          |            |                         |      |      |      |                                      |            |

| ADDWF                    | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N                      | 1, 2       |

| ADDWFC                   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N                      | 1, 2       |

| ANDWF                    | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff | Z, N                                 | 1,2        |

| CLRF                     | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff | Z                                    | 2          |

| COMF                     | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff | Z, N                                 | 1, 2       |

| CPFSEQ                   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff | None                                 | 4          |

| CPFSGT                   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff | None                                 | 4          |

| CPFSLT                   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff | None                                 | 1, 2       |

| DECF                     | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff | C, DC, Z, OV, N                      | 1, 2, 3, 4 |

| DECFSZ                   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff | None                                 | 1, 2, 3, 4 |

| DCFSNZ                   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff | None                                 | 1, 2       |

| INCF                     | f, d, a                         | Increment f                              | 1 .        | 0010                    | 10da | ffff | ffff | C, DC, Z, OV, N                      | 1, 2, 3, 4 |

| INCFSZ                   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff | None                                 | 4          |

| INFSNZ                   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff | None                                 | 1, 2       |

| IORWF                    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da | ffff | ffff | Z, N                                 | 1, 2       |

| MOVF                     | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff | Z, N                                 | 1          |

| MOVFF                    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff | ffff | ffff | None                                 |            |

|                          | U U                             | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff | ffff | ffff |                                      |            |

| MOVWF                    | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff | None                                 |            |

| MULWF                    | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff | None                                 | 1, 2       |

| NEGF                     | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff | C, DC, Z, OV, N                      |            |

| RLCF                     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff | C, Z, N                              | 1, 2       |

| RLNCF                    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff | Z, N                                 |            |

| RRCF                     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff | C, Z, N                              |            |

| RRNCF                    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff | Z, N                                 |            |

| SETF                     | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff | None                                 | 1, 2       |

| SUBFWB                   | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da | ffff | ffff | C, DC, Z, OV, N                      |            |

| SUBWF                    | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff | C, DC, Z, OV, N                      | 1, 2       |

| SUBWFB                   | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff | ffff | C, DC, Z, OV, N                      |            |

|                          | ,, <b>.</b> .                   | Borrow                                   |            |                         |      |      |      | -,, -, -, -, -, -, -, -, -, -, -, -, |            |

| SWAPF                    | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da | ffff | ffff | None                                 | 4          |

| TSTFSZ                   | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff | None                                 | 1, 2       |

| XORWF                    | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da | ffff | ffff |                                      |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| MULLW                                                                                                                                                                                                                                                                                                                                           | Multiply Litera           | l with W                         |                                  | MULWF                                                                                                                                                                                                                                                                                                                                                                          |             | Multiply V                                                                             | V with f                                                                                                          |                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Syntax:                                                                                                                                                                                                                                                                                                                                         | MULLW k                   |                                  |                                  | Syntax:                                                                                                                                                                                                                                                                                                                                                                        |             | MULWF                                                                                  | f {,a}                                                                                                            |                                                             |

| Operands:                                                                                                                                                                                                                                                                                                                                       | $0 \leq k \leq 255$       |                                  |                                  | Operands                                                                                                                                                                                                                                                                                                                                                                       | s:          | $0 \le f \le 25$                                                                       | 5                                                                                                                 |                                                             |

| Operation:                                                                                                                                                                                                                                                                                                                                      | (W) x k $\rightarrow$ PRO | DH:PRODL                         |                                  |                                                                                                                                                                                                                                                                                                                                                                                |             | a ∈ [0,1]                                                                              |                                                                                                                   |                                                             |

| Status Affected:                                                                                                                                                                                                                                                                                                                                | None                      | None                             |                                  |                                                                                                                                                                                                                                                                                                                                                                                | Operation:  | (W) x (f) $\rightarrow$ PRODH:PRODL                                                    |                                                                                                                   |                                                             |

| Encoding:                                                                                                                                                                                                                                                                                                                                       | 0000 110                  | )1 kkkk                          | kkkk                             | Status Af                                                                                                                                                                                                                                                                                                                                                                      | fected:     | None                                                                                   |                                                                                                                   |                                                             |

| Description:                                                                                                                                                                                                                                                                                                                                    | An unsigned mu            | ultiplication is ca              | arried                           | Encoding                                                                                                                                                                                                                                                                                                                                                                       | J:          | 0000                                                                                   | 001a f                                                                                                            | fff fff                                                     |

| out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in PRODH:PRODL register pair.<br>PRODH contains the high byte.<br>W is unchanged.<br>None of the Status flags are affected.<br>Note that neither Overflow nor Carry is<br>possible in this operation. A zero result<br>is possible but not detected. |                           | Descriptio                       | on:                              | An unsigned multiplication is carried<br>out between the contents of W and the<br>register file location 'f'. The 16-bit<br>result is stored in the PRODH:PRODI<br>register pair. PRODH contains the<br>high byte. Both W and 'f' are<br>unchanged.<br>None of the Status flags are affected.<br>Note that neither Overflow nor Carry is<br>possible in this operation. A Zero |             |                                                                                        |                                                                                                                   |                                                             |

| Words:                                                                                                                                                                                                                                                                                                                                          | 1                         |                                  |                                  |                                                                                                                                                                                                                                                                                                                                                                                |             | •                                                                                      | ossible but no                                                                                                    |                                                             |

| Cycles:                                                                                                                                                                                                                                                                                                                                         | 1                         |                                  |                                  |                                                                                                                                                                                                                                                                                                                                                                                |             |                                                                                        | the Access I                                                                                                      |                                                             |

| Q Cycle Activity:<br>Q1                                                                                                                                                                                                                                                                                                                         | Q2                        | Q3                               | Q4                               |                                                                                                                                                                                                                                                                                                                                                                                |             |                                                                                        | lf 'a' is '1', the<br>he GPR bank                                                                                 |                                                             |

| Decode<br>Example:                                                                                                                                                                                                                                                                                                                              | Read Pr                   | rocess W<br>Data reg<br>PR<br>PR | Vrite<br>jisters<br>ODH:<br>RODL |                                                                                                                                                                                                                                                                                                                                                                                |             | set is ena<br>operates i<br>Addressin<br>f ≤ 95 (5Fl<br><b>"Byte-Ori</b><br>Instructio | and the exter<br>bled, this inst<br>n Indexed Lit<br>g mode wher<br>n). See Secti<br>ented and Bi<br>ns in Indexe | ruction<br>eral Offset<br>never<br>on 26.2.3<br>it-Oriented |