#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2550t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset. Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

| TABLE 4-3: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION |

|------------|------------------------------------------------------------------|

|            | FOR RCON REGISTER                                                |

| Condition                                                    | Program               |    | RCO | N Reg | ister |     | STKPTR | Register |

|--------------------------------------------------------------|-----------------------|----|-----|-------|-------|-----|--------|----------|

| Condition                                                    | Counter               | RI | то  | PD    | POR   | BOR | STKFUL | STKUNF   |

| Power-on Reset                                               | 0000h                 | 1  | 1   | 1     | 0     | 0   | 0      | 0        |

| RESET instruction                                            | 0000h                 | 0  | u   | u     | u     | u   | u      | u        |

| Brown-out Reset                                              | 0000h                 | 1  | 1   | 1     | u     | 0   | u      | u        |

| MCLR Reset during power-managed Run modes                    | 0000h                 | u  | 1   | u     | u     | u   | u      | u        |

| MCLR Reset during power-managed Idle modes and Sleep mode    | 0000h                 | u  | 1   | 0     | u     | u   | u      | u        |

| WDT time-out during full power or<br>power-managed Run modes | 0000h                 | u  | 0   | u     | u     | u   | u      | u        |

| MCLR Reset during full-power execution                       | 0000h                 | u  | u   | u     | u     | u   | u      | u        |

| Stack Full Reset (STVREN = 1)                                | 0000h                 | u  | u   | u     | u     | u   | 1      | u        |

| Stack Underflow Reset (STVREN = 1)                           | 0000h                 | u  | u   | u     | u     | u   | u      | 1        |

| Stack Underflow Error (not an actual Reset,<br>STVREN = 0)   | 0000h                 | u  | u   | u     | u     | u   | u      | 1        |

| WDT time-out during power-managed Idle or Sleep modes        | PC + 2                | u  | 0   | 0     | u     | u   | u      | u        |

| Interrupt exit from power-managed modes                      | PC + 2 <sup>(1)</sup> | u  | u   | 0     | u     | u   | u      | u        |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

| IABLE 4-4:                  |      |      |                                    |                                                  |                                 | MCLR Resets, |           |

|-----------------------------|------|------|------------------------------------|--------------------------------------------------|---------------------------------|--------------|-----------|

| Register Applicable Devices |      | ces  | Power-on Reset,<br>Brown-out Reset | WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |              |           |

| UEP15                       | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP14                       | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP13                       | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP12                       | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP11                       | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP10                       | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP9                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP8                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP7                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP6                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP5                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP4                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP3                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP2                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP1                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UEP0                        | 2455 | 2550 | 4455                               | 4550                                             | 0 0000                          | 0 0000       | u uuuu    |

| UCFG                        | 2455 | 2550 | 4455                               | 4550                                             | 00-0 0000                       | 00-0 0000    | uu-u uuuu |

| UADDR                       | 2455 | 2550 | 4455                               | 4550                                             | -000 0000                       | -000 0000    | -uuu uuuu |

| UCON                        | 2455 | 2550 | 4455                               | 4550                                             | -0x0 000-                       | -0x0 000-    | -uuu uuu- |

| USTAT                       | 2455 | 2550 | 4455                               | 4550                                             | -XXX XXX-                       | -xxx xxx-    | -uuu uuu- |

| UEIE                        | 2455 | 2550 | 4455                               | 4550                                             | 00 0000                         | 00 0000      | uu uuuu   |

| UEIR                        | 2455 | 2550 | 4455                               | 4550                                             | 00 0000                         | 00 0000      | uu uuuu   |

| UIE                         | 2455 | 2550 | 4455                               | 4550                                             | -000 0000                       | -000 0000    | -uuu uuuu |

| UIR                         | 2455 | 2550 | 4455                               | 4550                                             | -000 0000                       | -000 0000    | -uuu uuuu |

| UFRMH                       | 2455 | 2550 | 4455                               | 4550                                             | xxx                             | xxx          | uuu       |

| UFRML                       | 2455 | 2550 | 4455                               | 4550                                             | XXXX XXXX                       | XXXX XXXX    | սսսս սսսս |

| SPPCON                      | 2455 | 2550 | 4455                               | 4550                                             | 00                              | 00           | uu        |

| SPPEPS                      | 2455 | 2550 | 4455                               | 4550                                             | 00-0 0000                       | 00-0 0000    | uu-u uuuu |

| SPPCFG                      | 2455 | 2550 | 4455                               | 4550                                             | 0000 0000                       | 0000 0000    | սսսս սսսս |

| SPPDATA                     | 2455 | 2550 | 4455                               | 4550                                             | 0000 0000                       | 0000 0000    | սսսս սսսս |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 4: See Table 4-3 for Reset value for specific condition.

- **5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

| File Name            | Bit 7                | Bit 6                 | Bit 5              | Bit 4              | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Value on<br>POR, BOR | Details<br>on page |

|----------------------|----------------------|-----------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------|--------------------|

| EEADR                | EEPROM Ad            | dress Register        |                    |                    |                    |                    |                    |                    | 0000 0000            | 55, 91             |

| EEDATA               | EEPROM Da            | ita Register          |                    |                    |                    |                    |                    |                    | 0000 0000            | 55, 91             |

| EECON2               | EEPROM Co            | ntrol Register        | 2 (not a physic    | cal register)      |                    |                    |                    |                    | 0000 0000            | 55, 82             |

| EECON1               | EEPGD                | CFGS                  | _                  | FREE               | WRERR              | WREN               | WR                 | RD                 | xx-0 x000            | 55, 83             |

| IPR2                 | OSCFIP               | CMIP                  | USBIP              | EEIP               | BCLIP              | HLVDIP             | TMR3IP             | CCP2IP             | 1111 1111            | 56, 109            |

| PIR2                 | OSCFIF               | CMIF                  | USBIF              | EEIF               | BCLIF              | HLVDIF             | TMR3IF             | CCP2IF             | 0000 0000            | 56, 105            |

| PIE2                 | OSCFIE               | CMIE                  | USBIE              | EEIE               | BCLIE              | HLVDIE             | TMR3IE             | CCP2IE             | 0000 0000            | 56, 107            |

| IPR1                 | SPPIP <sup>(3)</sup> | ADIP                  | RCIP               | TXIP               | SSPIP              | CCP1IP             | TMR2IP             | TMR1IP             | 1111 1111            | 56, 108            |

| PIR1                 | SPPIF <sup>(3)</sup> | ADIF                  | RCIF               | TXIF               | SSPIF              | CCP1IF             | TMR2IF             | TMR1IF             | 0000 0000            | 56, 104            |

| PIE1                 | SPPIE <sup>(3)</sup> | ADIE                  | RCIE               | TXIE               | SSPIE              | CCP1IE             | TMR2IE             | TMR1IE             | 0000 0000            | 56, 106            |

| OSCTUNE              | INTSRC               | _                     | _                  | TUN4               | TUN3               | TUN2               | TUN1               | TUN0               | 00 0000              | 56, 28             |

| TRISE <sup>(3)</sup> | _                    | _                     | _                  | _                  | _                  | TRISE2             | TRISE1             | TRISE0             | 111                  | 56, 126            |

| TRISD <sup>(3)</sup> | TRISD7               | TRISD6                | TRISD5             | TRISD4             | TRISD3             | TRISD2             | TRISD1             | TRISD0             | 1111 1111            | 56, 124            |

| TRISC                | TRISC7               | TRISC6                | _                  | _                  | _                  | TRISC2             | TRISC1             | TRISC0             | 11111                | 56, 121            |

| TRISB                | TRISB7               | TRISB6                | TRISB5             | TRISB4             | TRISB3             | TRISB2             | TRISB1             | TRISB0             | 1111 1111            | 56, 118            |

| TRISA                | _                    | TRISA6 <sup>(4)</sup> | TRISA5             | TRISA4             | TRISA3             | TRISA2             | TRISA1             | TRISA0             | -111 1111            | 56, 115            |

| LATE <sup>(3)</sup>  | _                    | _                     | _                  | _                  | _                  | LATE2              | LATE1              | LATE0              | xxx                  | 56, 126            |

| LATD <sup>(3)</sup>  | LATD7                | LATD6                 | LATD5              | LATD4              | LATD3              | LATD2              | LATD1              | LATD0              | XXXX XXXX            | 56, 124            |

| LATC                 | LATC7                | LATC6                 | _                  | _                  | _                  | LATC2              | LATC1              | LATC0              | xxxxx                | 56, 121            |

| LATB                 | LATB7                | LATB6                 | LATB5              | LATB4              | LATB3              | LATB2              | LATB1              | LATB0              | XXXX XXXX            | 56, 118            |

| LATA                 | _                    | LATA6 <sup>(4)</sup>  | LATA5              | LATA4              | LATA3              | LATA2              | LATA1              | LATA0              | -xxx xxxx            | 56, 115            |

| PORTE                | RDPU <sup>(3)</sup>  | _                     | _                  | _                  | RE3 <sup>(5)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | 0 x000               | 56, 125            |

| PORTD <sup>(3)</sup> | RD7                  | RD6                   | RD5                | RD4                | RD3                | RD2                | RD1                | RD0                | XXXX XXXX            | 56, 124            |

| PORTC                | RC7                  | RC6                   | RC5 <sup>(6)</sup> | RC4 <sup>(6)</sup> | _                  | RC2                | RC1                | RC0                | xxxx -xxx            | 56, 121            |

| PORTB                | RB7                  | RB6                   | RB5                | RB4                | RB3                | RB2                | RB1                | RB0                | XXXX XXXX            | 56, 118            |

| PORTA                | _                    | RA6 <sup>(4)</sup>    | RA5                | RA4                | RA3                | RA2                | RA1                | RA0                | -x0x 0000            | 56, 115            |

| UEP15                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP14                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP13                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP12                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP11                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP10                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP9                 |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP8                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP7                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP6                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP5                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP4                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP3                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP2                 | _                    |                       |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP1                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP0                 |                      |                       |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

|                      |                      |                       |                    |                    |                    |                    |                    |                    |                      |                    |

| TABLE 5-2: | REGISTER | FILE SUMMARY | (CONTINUED) |

|------------|----------|--------------|-------------|

|            |          |              |             |

Legend:

x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

Bit 21 of the TBLPTRU allows access to the device Configuration bits.

Note 1:

2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

7:  $I^2C^{TM}$  Slave mode only.

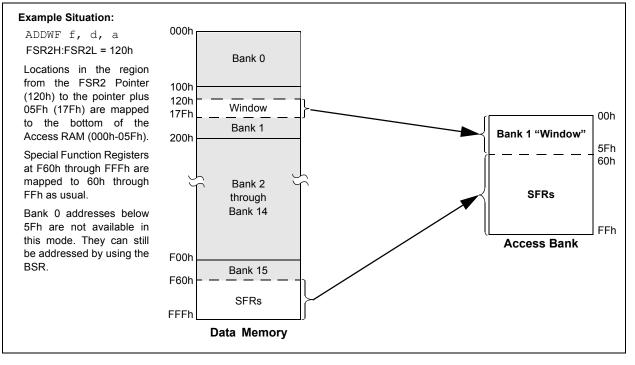

# 5.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower portion of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom half of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 5.3.3 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 5-9. Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before. Any indirect or indexed operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

# 5.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

#### FIGURE 5-9: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

| Name   | Bit 7                  | Bit 6        | Bit 5          | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|------------------------|--------------|----------------|--------------|--------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL    | TMR0IE         | INT0IE       | RBIE   | TMR0IF | INT0IF | RBIF   | 53                         |

| EEADR  | EEPROM A               | ddress Regi  | ster           |              |        |        |        |        | 55                         |

| EEDATA | A EEPROM Data Register |              |                |              |        |        |        |        | 55                         |

| EECON2 | EEPROM C               | ontrol Regis | ter 2 (not a p | ohysical reg | ister) |        |        |        | 55                         |

| EECON1 | EEPGD                  | CFGS         | _              | FREE         | WRERR  | WREN   | WR     | RD     | 55                         |

| IPR2   | OSCFIP                 | CMIP         | USBIP          | EEIP         | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 56                         |

| PIR2   | OSCFIF                 | CMIF         | USBIF          | EEIF         | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 56                         |

| PIE2   | OSCFIE                 | CMIE         | USBIE          | EEIE         | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 56                         |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

### 9.5 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1 and IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

### REGISTER 9-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                | R/W-1                                                                                                | R/W-1                  | R/W-1            | R/W-1             | R/W-1                    | R/W-1           | R/W-1  |

|----------------------|------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------------|--------------------------|-----------------|--------|

| SPPIP <sup>(1)</sup> | ADIP                                                                                                 | RCIP                   | TXIP             | SSPIP             | CCP1IP                   | TMR2IP          | TMR1IP |

| bit 7                |                                                                                                      |                        |                  |                   |                          |                 | bit 0  |

|                      |                                                                                                      |                        |                  |                   |                          |                 |        |

| Legend:              |                                                                                                      |                        |                  |                   |                          |                 |        |

| R = Readable         |                                                                                                      | W = Writable           |                  | -                 | mented bit, read         |                 |        |

| -n = Value at I      | POR                                                                                                  | '1' = Bit is set       |                  | '0' = Bit is cle  | eared                    | x = Bit is unkr | nown   |

| bit 7                | SPPIP: Stream                                                                                        | ming Parallel F        | Port Read/Wri    | te Interrupt Pric | prity bit <sup>(1)</sup> |                 |        |

|                      | 1 = High prio<br>0 = Low prior                                                                       | rity                   |                  |                   | ,                        |                 |        |

| bit 6                | <b>ADIP:</b> A/D Co<br>1 = High prio<br>0 = Low prior                                                |                        | ipt Priority bit |                   |                          |                 |        |

| bit 5                | RCIP: EUSAF<br>1 = High prio<br>0 = Low prior                                                        |                        | errupt Priority  | bit               |                          |                 |        |

| bit 4                | TXIP: EUSAR                                                                                          | RT Transmit Inf        | errupt Priority  | ' bit             |                          |                 |        |

|                      | 1 = High prio<br>0 = Low prior                                                                       | •                      |                  |                   |                          |                 |        |

| bit 3                | SSPIP: Maste<br>1 = High prio<br>0 = Low prior                                                       | rity                   | s Serial Port I  | nterrupt Priority | / bit                    |                 |        |

| bit 2                | 1 = High prio                                                                                        |                        | ority bit        |                   |                          |                 |        |

| bit 1                | <ul> <li>0 = Low prior</li> <li>TMR2IP: TMF</li> <li>1 = High prio</li> <li>0 = Low prior</li> </ul> | R2 to PR2 Mat<br>rity  | ch Interrupt P   | riority bit       |                          |                 |        |

| bit 0                |                                                                                                      | R1 Overflow In<br>rity | terrupt Priority | y bit             |                          |                 |        |

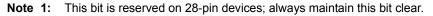

# 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The Data Latch register (LATA) is useful for readmodify-write operations on the value driven by the I/O pins.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

FIGURE 10-1: GENERIC I/O PORT

# 10.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register reads the status of the pins; writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA6 pin is multiplexed with the main oscillator pin; it is enabled as an oscillator or I/O pin by the selection of the main oscillator in Configuration Register 1H (see **Section 25.1 "Configuration Bits**" for details). When not used as a port pin, RA6 and its associated TRIS and LAT bits are read as '0'.

RA4 is also multiplexed with the USB module; it serves as a receiver input from an external USB transceiver. For details on configuration of the USB module, see **Section 17.2 "USB Status and Control"**.

Several PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA5 and RA3:RA0 as A/D converter inputs is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register 1).

| Note: | On a Power-on Reset, RA5 and RA3:RA0          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMP | LE 10-1 | : INITIALIZING PORTA    |

|-------|---------|-------------------------|

| CLRF  | PORTA   | ; Initialize PORTA by   |

|       |         | ; clearing output       |

|       |         | ; data latches          |

| CLRF  | LATA    | ; Alternate method      |

|       |         | ; to clear output       |

|       |         | ; data latches          |

| MOVLW | OFh     | ; Configure A/D         |

| MOVWF | ADCON1  | ; for digital inputs    |

| MOVLW | 07h     | ; Configure comparators |

| MOVWF | CMCON   | ; for digital input     |

| MOVLW | OCFh    | ; Value used to         |

|       |         | ; initialize data       |

|       |         | ; direction             |

| MOVWF | TRISA   | ; Set RA<3:0> as inputs |

|       |         | ; RA<5:4> as outputs    |

|       |         |                         |

# PIC18F2455/2550/4455/4550

| Name                 | Bit 7                | Bit 6                 | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1                 | Bit 0                 | Reset<br>Values<br>on page |

|----------------------|----------------------|-----------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|----------------------------|

| INTCON               | GIE/GIEH             | PEIE/GIEL             | TMR0IE              | INT0IE              | RBIE                | TMR0IF              | <b>INT0IF</b>         | RBIF                  | 53                         |

| RCON                 | IPEN                 | SBOREN <sup>(1)</sup> | -                   | RI                  | TO                  | PD                  | POR                   | BOR                   | 54                         |

| IPR1                 | SPPIP <sup>(2)</sup> | ADIP                  | RCIP                | TXIP                | SSPIP               | CCP1IP              | TMR2IP                | TMR1IP                | 56                         |

| PIR1                 | SPPIF <sup>(2)</sup> | ADIF                  | RCIF                | TXIF                | SSPIF               | CCP1IF              | TMR2IF                | TMR1IF                | 56                         |

| PIE1                 | SPPIE <sup>(2)</sup> | ADIE                  | RCIE                | TXIE                | SSPIE               | CCP1IE              | TMR2IE                | TMR1IE                | 56                         |

| IPR2                 | OSCFIP               | CMIP                  | USBIP               | EEIP                | BCLIP               | HLVDIP              | TMR3IP                | CCP2IP                | 56                         |

| PIR2                 | OSCFIF               | CMIF                  | USBIF               | EEIF                | BCLIF               | HLVDIF              | TMR3IF                | CCP2IF                | 56                         |

| PIE2                 | OSCFIE               | CMIE                  | USBIE               | EEIE                | BCLIE               | HLVDIE              | TMR3IE                | CCP2IE                | 56                         |

| TRISB                | TRISB7               | TRISB6                | TRISB5              | TRISB4              | TRISB3              | TRISB2              | TRISB1                | TRISB0                | 56                         |

| TRISC                | TRISC7               | TRISC6                | _                   | _                   | —                   | TRISC2              | TRISC1                | TRISC0                | 56                         |

| TRISD <sup>(2)</sup> | TRISD7               | TRISD6                | TRISD5              | TRISD4              | TRISD3              | TRISD2              | TRISD1                | TRISD0                | 56                         |

| TMR1L                | Timer1 Reg           | ister Low Byte        | e                   |                     |                     |                     |                       |                       | 54                         |

| TMR1H                | Timer1 Reg           | jister High Byt       | e                   |                     |                     |                     |                       |                       | 54                         |

| T1CON                | RD16                 | T1RUN                 | T1CKPS1             | T1CKPS0             | T1OSCEN             | T1SYNC              | TMR1CS                | TMR10N                | 54                         |

| TMR2                 | Timer2 Mod           | dule Register         |                     |                     |                     |                     |                       |                       | 54                         |

| T2CON                | —                    | T2OUTPS3              | T2OUTPS2            | T2OUTPS1            | T2OUTPS0            | TMR2ON              | T2CKPS1               | T2CKPS0               | 54                         |

| PR2                  | Timer2 Per           | iod Register          |                     |                     |                     |                     |                       |                       | 54                         |

| TMR3L                | Timer3 Reg           | ister Low Byte        | Э                   |                     |                     |                     |                       |                       | 55                         |

| TMR3H                | Timer3 Reg           | jister High Byt       | е                   |                     |                     |                     |                       |                       | 55                         |

| T3CON                | RD16                 | T3CCP2                | T3CKPS1             | T3CKPS0             | T3CCP1              | T3SYNC              | TMR3CS                | TMR3ON                | 55                         |

| CCPR1L               | Capture/Co           | mpare/PWM I           | Register 1 (LS      | B)                  |                     |                     |                       |                       | 55                         |

| CCPR1H               | Capture/Co           | mpare/PWM I           | Register 1 (MS      | SB)                 |                     |                     |                       |                       | 55                         |

| CCP1CON              | P1M1 <sup>(2)</sup>  | P1M0 <sup>(2)</sup>   | DC1B1               | DC1B0               | CCP1M3              | CCP1M2              | CCP1M1                | CCP1M0                | 55                         |

| ECCP1AS              | ECCPASE              | ECCPAS2               | ECCPAS1             | ECCPAS0             | PSSAC1              | PSSAC0              | PSSBD1 <sup>(2)</sup> | PSSBD0 <sup>(2)</sup> | 55                         |

| ECCP1DEL             | PRSEN                | PDC6 <sup>(2)</sup>   | PDC5 <sup>(2)</sup> | PDC4 <sup>(2)</sup> | PDC3 <sup>(2)</sup> | PDC2 <sup>(2)</sup> | PDC1 <sup>(2)</sup>   | PDC0 <sup>(2)</sup>   | 55                         |

#### TABLE 16-3: REGISTERS ASSOCIATED WITH ECCP MODULE AND TIMER1 TO TIMER3

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during ECCP operation.

Note 1: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

2: These bits or registers are unimplemented in 28-pin devices; always maintain these bits clear.

#### 17.5.1 USB INTERRUPT STATUS REGISTER (UIR)

The USB Interrupt Status register (Register 17-7) contains the flag bits for each of the USB status interrupt sources. Each of these sources has a corresponding interrupt enable bit in the UIE register. All of the USB status flags are ORed together to generate the USBIF interrupt flag for the microcontroller's interrupt funnel.

Once an interrupt bit has been set by the SIE, it must be cleared by software by writing a '0'. The flag bits can also be set in software which can aid in firmware debugging. When the USB module is in the Low-Power Suspend mode (UCON<1> = 1), the SIE does not get clocked. When in this state, the SIE cannot process packets, and therefore, cannot detect new interrupt conditions other than the Activity Detect Interrupt, ACTVIF. The ACTVIF bit is typically used by USB firmware to detect when the microcontroller should bring the USB module out of the Low-Power Suspend mode (UCON<1> = 0).

# REGISTER 17-7: UIR: USB INTERRUPT STATUS REGISTER

| U-0   | R/W-0 | R/W-0   | R/W-0                 | R/W-0                | R/W-0                 | R-0                   | R/W-0  |

|-------|-------|---------|-----------------------|----------------------|-----------------------|-----------------------|--------|

| —     | SOFIF | STALLIF | IDLEIF <sup>(1)</sup> | TRNIF <sup>(2)</sup> | ACTVIF <sup>(3)</sup> | UERRIF <sup>(4)</sup> | URSTIF |

| bit 7 |       |         |                       |                      |                       |                       | bit 0  |

| Legend:           |          |                                                                                                    |                                                                    |                                                   |  |  |  |  |  |

|-------------------|----------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| R = Reada         | able bit | W = Writable bit                                                                                   | U = Unimplemented bit, read as '0'                                 |                                                   |  |  |  |  |  |

| -n = Value at POR |          | '1' = Bit is set                                                                                   | '0' = Bit is cleared                                               | x = Bit is unknown                                |  |  |  |  |  |

| bit 7             | Unimple  | mented: Read as '0'                                                                                |                                                                    |                                                   |  |  |  |  |  |

| bit 6             | -        | Start-Of-Frame Token Interru                                                                       | nt hit                                                             |                                                   |  |  |  |  |  |

| bit o             | 1 = A St | art-Of-Frame token received                                                                        | l by the SIE                                                       |                                                   |  |  |  |  |  |

| bit 5             | STALLIF  | : A STALL Handshake Inter                                                                          | rupt bit                                                           |                                                   |  |  |  |  |  |

|                   |          | TALL handshake was sent by<br>TALL handshake has not bee                                           |                                                                    |                                                   |  |  |  |  |  |

| bit 4             | 1 = Idle | Idle Detect Interrupt bit <sup>(1)</sup><br>condition detected (constant<br>dle condition detected | t Idle state of 3 ms or more)                                      |                                                   |  |  |  |  |  |

| bit 3             | TRNIF: 7 | Fransaction Complete Interru                                                                       | ıpt bit <sup>(2)</sup>                                             |                                                   |  |  |  |  |  |

|                   |          |                                                                                                    | on is complete; read USTAT re<br>on is not complete or no transa   | gister for endpoint information action is pending |  |  |  |  |  |

| bit 2             | ACTVIF:  | Bus Activity Detect Interrup                                                                       | t bit <sup>(3)</sup>                                               |                                                   |  |  |  |  |  |

|                   |          | vity on the D+/D- lines was d<br>activity detected on the D+/D                                     |                                                                    |                                                   |  |  |  |  |  |

| bit 1             | UERRIF   | : USB Error Condition Interru                                                                      | upt bit <sup>(4)</sup>                                             |                                                   |  |  |  |  |  |

|                   |          | Inmasked error condition has<br>Inmasked error condition ha                                        |                                                                    |                                                   |  |  |  |  |  |

| bit 0             | URSTIF:  | USB Reset Interrupt bit                                                                            |                                                                    |                                                   |  |  |  |  |  |

|                   |          | d USB Reset occurred; 00h i<br>JSB Reset has occurred                                              | s loaded into UADDR register                                       |                                                   |  |  |  |  |  |

| Note 1:           |          |                                                                                                    | ay want to place the USB mod                                       | •                                                 |  |  |  |  |  |

| 2:<br>3:          | •        |                                                                                                    | O to advance (valid only for IN<br>ng the detection of a UIDLE int |                                                   |  |  |  |  |  |

| 4:                | 21       | , ,                                                                                                | 0                                                                  | This bit is a status bit only and                 |  |  |  |  |  |

4: Only error conditions enabled through the UEIE register will set this bit. This bit is a status bit only and cannot be set or cleared by the user.

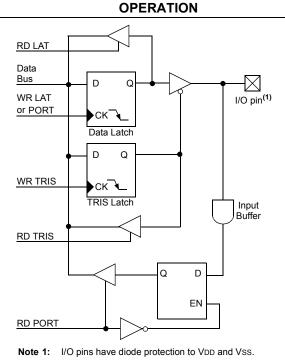

# 19.4 I<sup>2</sup>C Mode

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RB1/AN10/INT1/SCK/SCL

- Serial data (SDA) RB0/AN12/INT0/FLT0/SDI/SDA

The user must configure these pins as inputs by setting the associated TRIS bits.

#### FIGURE 19-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

# 19.4.1 REGISTERS

The MSSP module has six registers for  $I^2C$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON1, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON1 and SSPCON2 registers are readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the MSSP is configured in  $I^2C$  Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPADD act as the Baud Rate Generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### 19.4.4 CLOCK STRETCHING

Both 7-Bit and 10-Bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 19.4.4.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP bit being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 19-15).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 19.4.4.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 19.4.4.3 Clock Stretching for 7-Bit Slave Transmit Mode

7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 19-10).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit.

#### 19.4.4.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence which contains the highorder bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 19-13).

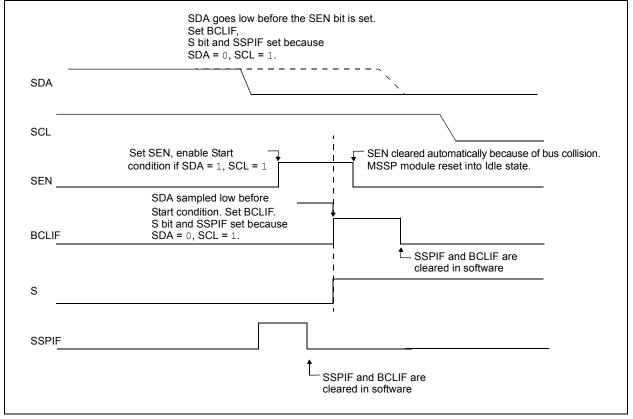

#### 19.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 19-28).

- b) SCL is sampled low before SDA is asserted low (Figure 19-29).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its inactive state (Figure 19-28).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to '0'. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 19-30). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0. If the SCL pin is sampled as '0', during this time a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

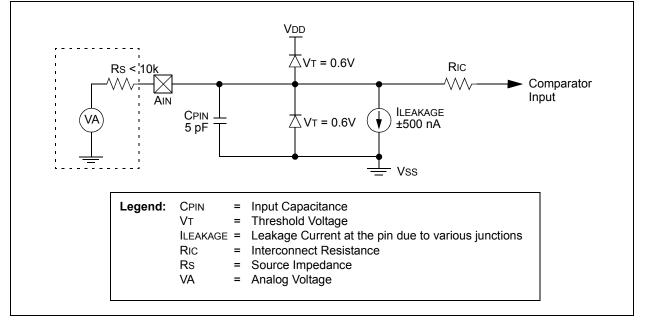

### 22.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 22-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| Name   | Bit 7    | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|----------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------------|

| CMCON  | C2OUT    | C10UT                 | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 55                         |

| CVRCON | CVREN    | CVROE                 | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 55                         |

| INTCON | GIE/GIEH | PEIE/GIEL             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR2   | OSCFIF   | CMIF                  | USBIF  | EEIF   | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 56                         |

| PIE2   | OSCFIE   | CMIE                  | USBIE  | EEIE   | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 56                         |

| IPR2   | OSCFIP   | CMIP                  | USBIP  | EEIP   | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 56                         |

| PORTA  | _        | RA6 <sup>(1)</sup>    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | 56                         |

| LATA   | _        | LATA6 <sup>(1)</sup>  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 56                         |

| TRISA  | _        | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 56                         |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

**Note 1:** PORTA<6> and its direction and latch bits are individually configured as port pins based on various oscillator modes. When disabled, these bits read as '0'.

#### 25.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

#### 25.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP operation or an external programmer.

# 25.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

# 25.7 In-Circuit Serial Programming

PIC18F2455/2550/4455/4550 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 25.8 In-Circuit Debugger

When the DEBUG Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 25-4 shows which resources are required by the background debugger.

| <b>TABLE 25-4</b> : | DEBUGGER RESOURCES |

|---------------------|--------------------|

| IADEE 20-4.         |                    |

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to  $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ , VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

# 25.9 Special ICPORT Features (44-Pin TQFP Package Only)

Under specific circumstances, the No Connect (NC) pins of devices in 44-pin TQFP packages can provide additional functionality. These features are controlled by device Configuration bits and are available only in this package type and pin count.

### 25.9.1 DEDICATED ICD/ICSP PORT

The 44-pin TQFP devices can use NC pins to provide an alternate port for In-Circuit Debugging (ICD) and In-Circuit Serial Programming (ICSP). These pins are collectively known as the dedicated ICSP/ICD port, since they are not shared with any other function of the device.

When implemented, the dedicated port activates three NC pins to provide an alternate device Reset, data and clock ports. None of these ports overlap with standard I/O pins, making the I/O pins available to the user's application.

The dedicated ICSP/ICD port is enabled by setting the ICPRT Configuration bit. The port functions the same way as the legacy ICSP/ICD port on RB6/RB7. Table 25-5 identifies the functionally equivalent pins for ICSP and ICD purposes.

#### TABLE 25-5: EQUIVALENT PINS FOR LEGACY AND DEDICATED ICD/ICSP™ PORTS

| Pin I            | Name               | Pin |                                           |

|------------------|--------------------|-----|-------------------------------------------|

| Legacy<br>Port   |                    |     | Pin Function                              |

| MCLR/VPP/<br>RE3 | NC/ICRST/<br>ICVPP | Р   | Device Reset and<br>Programming<br>Enable |

| RB6/KBI2/<br>PGC | NC/ICCK/<br>ICPGC  | I   | Serial Clock                              |

| RB7/KBI3/<br>PGD | NC/ICDT/<br>ICPGD  | I/O | Serial Data                               |

Legend: I = Input, O = Output, P = Power

# PIC18F2455/2550/4455/4550

| MULLW                   | Multiply Litera                                                                                                                                                                                                                                                                                                                                 | l with W                          |                                  | MULWF            |             | Multiply V                                                                                                                                                                                                                                                                                                                                                             | V with f                                                                                                          |                                                             |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| Syntax:                 | MULLW k                                                                                                                                                                                                                                                                                                                                         |                                   |                                  | Syntax:          |             | MULWF                                                                                                                                                                                                                                                                                                                                                                  | f {,a}                                                                                                            |                                                             |  |

| Operands:               | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                               |                                   |                                  | Operands         | s:          | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                   |                                                             |  |

| Operation:              | (W) x k $\rightarrow$ PRO                                                                                                                                                                                                                                                                                                                       | (W) x k $\rightarrow$ PRODH:PRODL |                                  |                  | a ∈ [0,1]   |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |                                                             |  |

| Status Affected:        | None                                                                                                                                                                                                                                                                                                                                            |                                   |                                  | Operation        | n:          | (W) x (f) –                                                                                                                                                                                                                                                                                                                                                            | → PRODH:PF                                                                                                        | RODL                                                        |  |

| Encoding:               | 0000 110                                                                                                                                                                                                                                                                                                                                        | )1 kkkk                           | kkkk                             | Status Af        | fected:     | None                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                   |                                                             |  |

| Description:            | An unsigned mu                                                                                                                                                                                                                                                                                                                                  | ultiplication is ca               | arried                           | Encoding         | J:          | 0000                                                                                                                                                                                                                                                                                                                                                                   | 001a f                                                                                                            | fff fff                                                     |  |

| Morder                  | out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in PRODH:PRODL register pair.<br>PRODH contains the high byte.<br>W is unchanged.<br>None of the Status flags are affected.<br>Note that neither Overflow nor Carry is<br>possible in this operation. A zero result<br>is possible but not detected. |                                   |                                  | Descriptio       | on:         | An unsigned multiplication is carried<br>out between the contents of W and t<br>register file location 'f'. The 16-bit<br>result is stored in the PRODH:PROI<br>register pair. PRODH contains the<br>high byte. Both W and 'f' are<br>unchanged.<br>None of the Status flags are affecte<br>Note that neither Overflow nor Carry<br>possible in this operation. A Zero |                                                                                                                   |                                                             |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                                                                               |                                   |                                  |                  |             | •                                                                                                                                                                                                                                                                                                                                                                      | ossible but no                                                                                                    |                                                             |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                                                                               |                                   |                                  |                  |             |                                                                                                                                                                                                                                                                                                                                                                        | the Access I                                                                                                      |                                                             |  |