Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4455-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                    | Pi          | n Num    | ber     | Pin     | Buffer   | Description                                   |  |  |  |  |

|-----------------------------|-------------|----------|---------|---------|----------|-----------------------------------------------|--|--|--|--|

| Pin Name                    | PDIP        | QFN      | TQFP    | Туре    | Туре     | Description                                   |  |  |  |  |

|                             |             |          |         |         |          | PORTC is a bidirectional I/O port.            |  |  |  |  |

| RC0/T10SO/T13CKI            | 15          | 34       | 32      |         |          |                                               |  |  |  |  |

| RC0                         |             |          |         | I/O     | ST       | Digital I/O.                                  |  |  |  |  |

| T1OSO                       |             |          |         | 0       | —        | Timer1 oscillator output.                     |  |  |  |  |

| T13CKI                      |             |          |         | Ι       | ST       | Timer1/Timer3 external clock input.           |  |  |  |  |

| RC1/T1OSI/CCP2/<br>UOE      | 16          | 35       | 35      |         |          |                                               |  |  |  |  |

| RC1                         |             |          |         | I/O     | ST       | Digital I/O.                                  |  |  |  |  |

| T1OSI                       |             |          |         | Ι       | CMOS     | Timer1 oscillator input.                      |  |  |  |  |

| <u>CCP</u> 2 <sup>(2)</sup> |             |          |         | I/O     | ST       | Capture 2 input/Compare 2 output/PWM2 output. |  |  |  |  |

| UOE                         |             |          |         | 0       | —        | External USB transceiver OE output.           |  |  |  |  |

| RC2/CCP1/P1A                | 17          | 36       | 36      |         |          |                                               |  |  |  |  |

| RC2                         |             |          |         | I/O     | ST       | Digital I/O.                                  |  |  |  |  |

| CCP1                        |             |          |         | I/O     | ST       | Capture 1 input/Compare 1 output/PWM1 output. |  |  |  |  |

| P1A                         |             |          |         | 0       | TTL      | Enhanced CCP1 PWM output, channel A.          |  |  |  |  |

| RC4/D-/VM                   | 23          | 42       | 42      |         |          |                                               |  |  |  |  |

| RC4                         |             |          |         | I       | TTL      | Digital input.                                |  |  |  |  |

| D-                          |             |          |         | I/O     |          | USB differential minus line (input/output).   |  |  |  |  |

| VM                          |             |          |         | I       | TTL      | External USB transceiver VM input.            |  |  |  |  |

| RC5/D+/VP                   | 24          | 43       | 43      |         |          |                                               |  |  |  |  |

| RC5                         |             |          |         | I       | TTL      | Digital input.                                |  |  |  |  |

| D+                          |             |          |         | I/O     |          | USB differential plus line (input/output).    |  |  |  |  |

| VP                          |             |          |         | I       | TTL      | External USB transceiver VP input.            |  |  |  |  |

| RC6/TX/CK                   | 25          | 44       | 44      |         |          |                                               |  |  |  |  |

| RC6                         |             |          |         | I/O     | ST       | Digital I/O.                                  |  |  |  |  |

| TX                          |             |          |         | 0       |          | EUSART asynchronous transmit.                 |  |  |  |  |

| СК                          |             |          |         | I/O     | ST       | EUSART synchronous clock (see RX/DT).         |  |  |  |  |

| RC7/RX/DT/SDO               | 26          | 1        | 1       |         |          |                                               |  |  |  |  |

| RC7                         |             |          |         | I/O     | ST       | Digital I/O.                                  |  |  |  |  |

| RX                          |             |          |         |         | ST       | EUSART asynchronous receive.                  |  |  |  |  |

| DT                          |             |          |         | I/O     | ST       | EUSART synchronous data (see TX/CK).          |  |  |  |  |

| SDO                         |             |          |         | 0       | <u> </u> | SPI data out.                                 |  |  |  |  |

| Legend: TTL = TTL c         |             |          |         | 100 ·   |          | MOS = CMOS compatible input or output         |  |  |  |  |

| ST = Schm                   | nitt Trigge | er input | with CN | /IOS le | vels l   | = Input                                       |  |  |  |  |

#### **TABLE 1-3**: PIC18F4455/4550 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output

Ρ = Power

Note 1: Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared.

2: Default assignment for CCP2 when CCP2MX Configuration bit is set.

3: These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

# 4.2 Master Clear Reset (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18F2455/2550/4455/4550 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See **Section 10.5 "PORTE, TRISE and LATE Registers"** for more information.

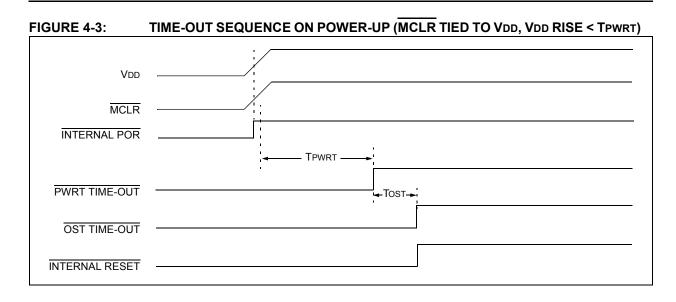

# 4.3 **Power-on Reset (POR)**

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004, **Section 28.1 "DC Characteristics"**). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

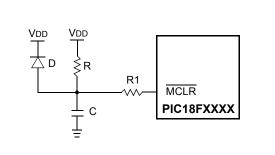

### FIGURE 4-2:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

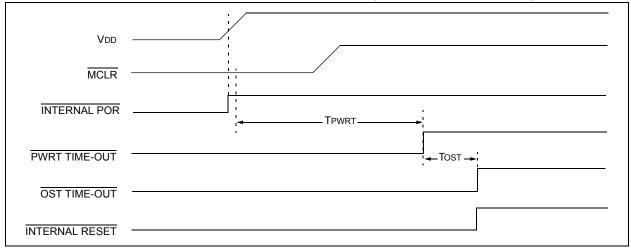

# FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

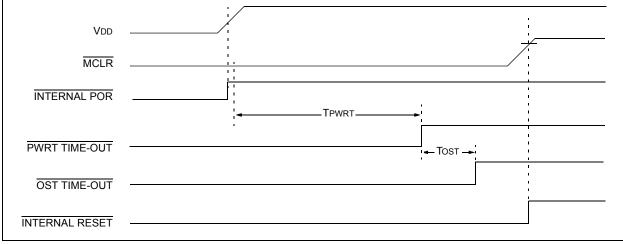

# FIGURE 4-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by user software or a Power-on Reset.

# 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. Each stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

# EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

|      |              | -                                                       |

|------|--------------|---------------------------------------------------------|

| CALL | SUB1, FAST   | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|      | •            |                                                         |

| SUB1 | •            |                                                         |

|      | RETURN, FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

# 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

## 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET, W<br>TABLE |

|-------|--------------|--------------------|

|       |              | IADDE              |

| ORG   | nn00h        |                    |

| TABLE | ADDWF        | PCL                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | •            |                    |

|       | •            |                    |

|       | •            |                    |

# 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

# 5.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds eight additional two-word commands to the existing PIC18 instruction set: ADDFSR, ADDULNK, CALLW, MOVSF, MOVSS, PUSHL, SUBFSR and SUBULNK. These instructions are executed as described in Section 5.2.4 "Two-Word Instructions".

# 5.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

# 5.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode. When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

# 5.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1') or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 5-8.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 26.2.1** "Extended Instruction Syntax".

| Pin                   | Function                               | TRIS<br>Setting | I/O                         | I/О Туре             | Description                                                                                                                        |  |  |  |

|-----------------------|----------------------------------------|-----------------|-----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RB0/AN12/             | RB0                                    | 0               | OUT                         | DIG                  | LATB<0> data output; not affected by analog input.                                                                                 |  |  |  |

| INT0/FLT0/<br>SDI/SDA |                                        | 1               | IN                          | TTL                  | PORTB<0> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input enabled. <sup>(1)</sup>                  |  |  |  |

|                       | AN12                                   | 1               | IN                          | ANA                  | A/D Input Channel 12. <sup>(1)</sup>                                                                                               |  |  |  |

|                       | INT0                                   | 1               | IN                          | ST                   | External Interrupt 0 input.                                                                                                        |  |  |  |

|                       | FLT0                                   | 1               | IN                          | ST                   | Enhanced PWM Fault input (ECCP1 module); enabled in software.                                                                      |  |  |  |

|                       | SDI                                    | 1               | IN                          | ST                   | SPI data input (MSSP module).                                                                                                      |  |  |  |

|                       | SDA                                    | 1               | OUT                         | DIG                  | I <sup>2</sup> C <sup>™</sup> data output (MSSP module); takes priority over port data.                                            |  |  |  |

|                       |                                        | 1               | IN                          | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP module); input type depends on module setting                                                    |  |  |  |

| RB1/AN10/             | RB1                                    | 0               | OUT                         | DIG                  | LATB<1> data output; not affected by analog input.                                                                                 |  |  |  |

| NT1/SCK/<br>SCL       |                                        | 1               | IN                          | TTL                  | PORTB<1> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input enabled. <sup>(1)</sup>                  |  |  |  |

|                       | AN10                                   | 1               | IN                          | ANA                  | A/D Input Channel 10. <sup>(1)</sup>                                                                                               |  |  |  |

|                       | INT1 1 IN ST External Interrupt 1 inpu |                 | External Interrupt 1 input. |                      |                                                                                                                                    |  |  |  |

|                       | SCK                                    | 0               | OUT                         | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                                     |  |  |  |

|                       |                                        | 1               | IN                          | ST                   | SPI clock input (MSSP module).                                                                                                     |  |  |  |

|                       | SCL                                    | 0               | OUT                         | DIG                  | I <sup>2</sup> C clock output (MSSP module); takes priority over port data.                                                        |  |  |  |

|                       |                                        | 1               | IN                          | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP module); input type depends on module settin                                                    |  |  |  |

| RB2/AN8/              | RB2                                    | 0               | OUT                         | DIG                  | LATB<2> data output; not affected by analog input.                                                                                 |  |  |  |

| NT2/VMO               |                                        | 1               | IN                          | TTL                  | PORTB<2> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input enabled. <sup>(1)</sup> |  |  |  |

|                       | AN8                                    | 1               | IN                          | ANA                  | A/D input channel 8. <sup>(1)</sup>                                                                                                |  |  |  |

|                       | INT2                                   | 1               | IN                          | ST                   | External Interrupt 2 input.                                                                                                        |  |  |  |

|                       | VMO                                    | 0               | OUT                         | DIG                  | External USB transceiver VMO data output.                                                                                          |  |  |  |

| RB3/AN9/              | RB3                                    | 0               | OUT                         | DIG                  | LATB<3> data output; not affected by analog input.                                                                                 |  |  |  |

| CCP2/VPO              |                                        | 1               | IN                          | TTL                  | PORTB<3> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input enabled. <sup>(1)</sup>                  |  |  |  |

|                       | AN9                                    | 1               | IN                          | ANA                  | A/D Input Channel 9. <sup>(1)</sup>                                                                                                |  |  |  |

|                       | CCP2 <sup>(2)</sup>                    | 0               | OUT                         | DIG                  | CCP2 compare and PWM output.                                                                                                       |  |  |  |

|                       |                                        | 1               | IN                          | ST                   | CCP2 capture input.                                                                                                                |  |  |  |

|                       | VPO                                    | 0               | OUT                         | DIG                  | External USB transceiver VPO data output.                                                                                          |  |  |  |

| RB4/AN11/             | RB4                                    | 0               | OUT                         | DIG                  | LATB<4> data output; not affected by analog input.                                                                                 |  |  |  |

| KBI0/CSSPP            |                                        | 1               | IN                          | TTL                  | PORTB<4> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input enabled. <sup>(1)</sup>                  |  |  |  |

|                       | AN11                                   | 1               | IN                          | ANA                  | A/D Input Channel 11. <sup>(1)</sup>                                                                                               |  |  |  |

|                       | KBI0                                   | 1               | IN                          | TTL                  | Interrupt-on-pin change.                                                                                                           |  |  |  |

|                       | CSSPP <sup>(4)</sup>                   | 0               | OUT                         | DIG                  | SPP chip select control output.                                                                                                    |  |  |  |

| RB5/KBI1/             | RB5                                    | 0               | OUT                         | DIG                  | LATB<5> data output.                                                                                                               |  |  |  |

| PGM                   |                                        | 1               | IN                          | TTL                  | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                                        |  |  |  |

|                       | KBI1                                   | 1               | IN                          | TTL                  | Interrupt-on-pin change.                                                                                                           |  |  |  |

|                       | PGM                                    | х               | IN                          | ST                   | Single-Supply Programming mode entry (ICSP™). Enabled by LVP Configuration bit; all other pin functions disabled.                  |  |  |  |

TABLE 10-3: PORTB I/O SUMMARY

Legend. OUT - Output, IN - Input, ANA - Analog Signal, DIG - Digital Output, ST - Scinnit Buller Input, I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

**Note 1:** Configuration on POR is determined by PBADEN Configuration bit. Pins are configured as analog inputs when PBADEN is set and digital inputs when PBADEN is cleared.

2: Alternate pin assignment for CCP2 when CCP2MX = 0. Default assignment is RC1.

**3:** All other pin functions are disabled when ICSP<sup>™</sup> or ICD operation is enabled.

4: 40/44-pin devices only.

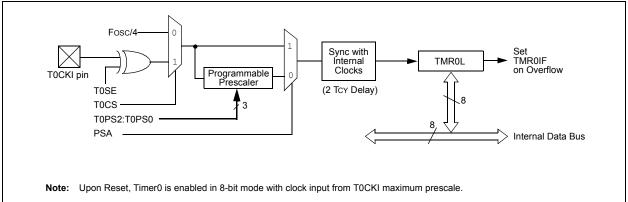

# 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected by clearing the T0CS bit (T0CON<5>). In Timer mode, the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In Counter mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI/C1OUT/ RCV. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

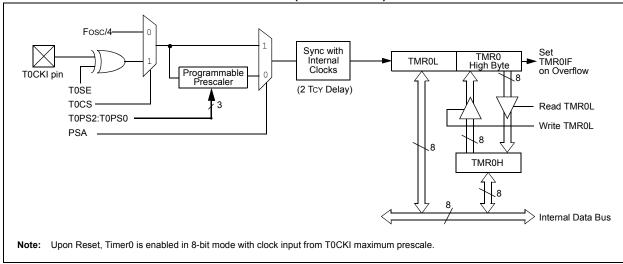

# 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

# FIGURE 11-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

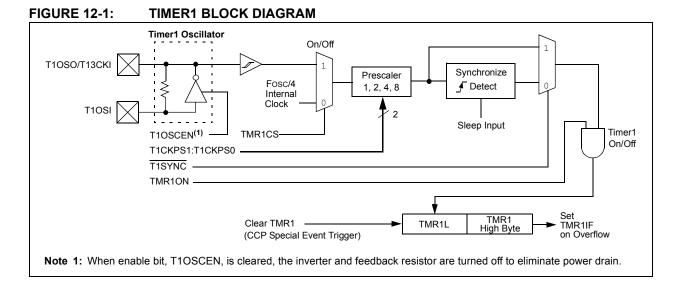

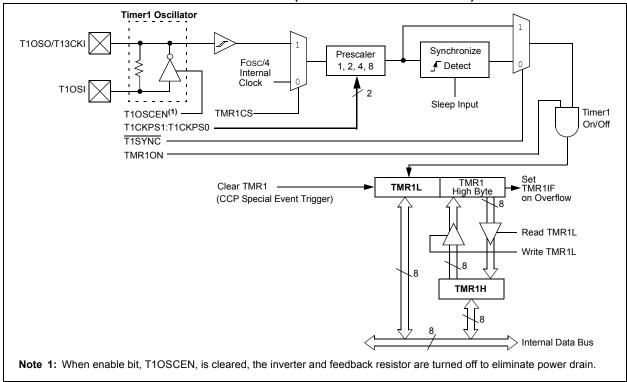

# 12.1 Timer1 Operation

Timer1 can operate in one of these modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>). When TMR1CS is cleared (= 0), Timer1 increments on every internal instruction

cycle (Fosc/4). When the bit is set, Timer1 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When Timer1 is enabled, the RC1/T1OSI/ $\overline{\text{UOE}}$  and RC0/T1OSO/T13CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

### FIGURE 12-2: TIMER1 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

### 19.3.8 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

In most Idle modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator) or the INTOSC source. See **Section 2.4** "**Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode or one of the Idle modes when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

# 19.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

# 19.3.10 BUS MODE COMPATIBILITY

Table 19-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

TABLE 19-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6                 | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-----------------------|------------|--------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL             | TMR0IE     | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR1    | SPPIF <sup>(1)</sup> | ADIF                  | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 56                         |

| PIE1    | SPPIE <sup>(1)</sup> | ADIE                  | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 56                         |

| IPR1    | SPPIP <sup>(1)</sup> | ADIP                  | RCIP       | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 56                         |

| TRISA   | _                    | TRISA6 <sup>(2)</sup> | TRISA5     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 56                         |

| TRISB   | TRISB7               | TRISB6                | TRISB5     | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 56                         |

| TRISC   | TRISC7               | TRISC6                | _          | _      |        | TRISC2 | TRISC1 | TRISC0 | 56                         |

| SSPBUF  | MSSP Rec             | eive Buffer/1         | ransmit Re | gister |        |        |        |        | 54                         |

| SSPCON1 | WCOL                 | SSPOV                 | SSPEN      | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 54                         |

| SSPSTAT | SMP                  | CKE                   | D/Ā        | Р      | S      | R/W    | UA     | BF     | 54                         |

TABLE 19-2:

REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: These bits are unimplemented in 28-pin devices; always maintain these bits clear.

**2:** RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

| R/W-0        | R/W-0                                                                                                                                                               | R-0                  | R-0               | R-0              | R-0                  | R-0                 | R-0      |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|------------------|----------------------|---------------------|----------|--|--|--|--|--|--|--|

| SMP          | CKE                                                                                                                                                                 | D/Ā                  | P <sup>(1)</sup>  | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                  | BF       |  |  |  |  |  |  |  |

| bit 7        |                                                                                                                                                                     |                      |                   |                  |                      |                     | bit      |  |  |  |  |  |  |  |

|              |                                                                                                                                                                     |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| Legend:      | la hit                                                                                                                                                              | \\/\\/::tabl         | - h:t             |                  |                      |                     |          |  |  |  |  |  |  |  |

| R = Readab   |                                                                                                                                                                     | W = Writabl          |                   | •                | lemented bit, read   |                     |          |  |  |  |  |  |  |  |

| -n = Value a | IPOR                                                                                                                                                                | '1' = Bit is s       | el                | '0' = Bit is o   | cleared              | x = Bit is unkr     | IOWN     |  |  |  |  |  |  |  |

| bit 7        | SMP: Slew Rate Control bit                                                                                                                                          |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Master or Slave mode:                                                                                                                                            |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz)</li> <li>0 = Slew rate control enabled for High-Speed mode (400 kHz)</li> </ul> |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 6        | CKE: SMBus Select bit                                                                                                                                               |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Master or Slave mode:                                                                                                                                            |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | 1 = Enable SMBus specific inputs<br>0 = Disable SMBus specific inputs                                                                                               |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 5        | D/A: Data/Address bit                                                                                                                                               |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Master mode:                                                                                                                                                     |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | Reserved.                                                                                                                                                           |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Slave mode:<br>1 = Indicates that the last byte received or transmitted was data                                                                                 |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | 0 = Indicates that the last byte received or transmitted was address                                                                                                |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 4        | P: Stop bit <sup>(1)</sup>                                                                                                                                          |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul>                                                |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 3        | S: Start bit <sup>(1)</sup>                                                                                                                                         |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Indicates that a Start bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                              |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 2        |                                                                                                                                                                     | Nrite Informati      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Slave mod                                                                                                                                                        |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | 1 = Read                                                                                                                                                            |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | 0 = Write                                                                                                                                                           |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Master mode:<br>1 = Transmit is in progress                                                                                                                      |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              |                                                                                                                                                                     | t is not in progress |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 1        | UA: Update                                                                                                                                                          | Address bit (1       | 0-Bit Slave mod   | de only)         |                      |                     |          |  |  |  |  |  |  |  |

|              | 1 = Indicates that the user needs to update the address in the SSPADD register                                                                                      |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | 0 = Address does not need to be updated                                                                                                                             |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

| bit 0        | BF: Buffer F                                                                                                                                                        |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Transmit mode:                                                                                                                                                   |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | 1 = SSPBUF is full<br>0 = SSPBUF is empty                                                                                                                           |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              | In Receive m                                                                                                                                                        |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

|              |                                                                                                                                                                     |                      | not include the A |                  |                      |                     |          |  |  |  |  |  |  |  |

| Note 1: ⊤    | his bit is cleared                                                                                                                                                  | l on Reset and       | when SSPEN        | is cleared.      |                      |                     |          |  |  |  |  |  |  |  |

|              |                                                                                                                                                                     |                      |                   |                  | ress match. This     | bit is only valid t | from the |  |  |  |  |  |  |  |

|              | ddress match to                                                                                                                                                     |                      |                   |                  |                      |                     |          |  |  |  |  |  |  |  |

# REGISTER 19-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Active mode.

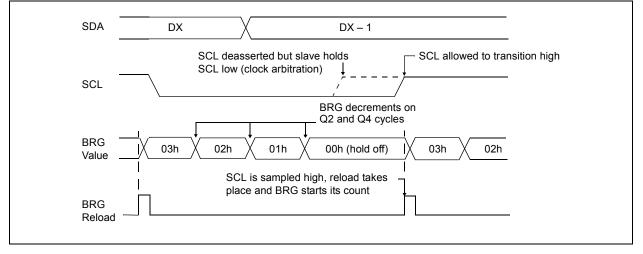

### 19.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 19-20).

| R/W-0         | R/W-0                                                                             | R/W-0                              | R/W-0          | R/W-0            | R/W-0            | R-1             | R/W-0 |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------|------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|--|--|

| CSRC          | TX9                                                                               | TXEN <sup>(1)</sup>                | SYNC           | SENDB            | BRGH             | TRMT            | TX9D  |  |  |  |  |  |  |

| bit 7         |                                                                                   |                                    |                |                  |                  |                 | bit ( |  |  |  |  |  |  |

|               |                                                                                   |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

| Legend:       |                                                                                   |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

| R = Readable  | e bit                                                                             | W = Writable                       | bit            | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |  |  |  |  |

| -n = Value at | POR                                                                               | '1' = Bit is set                   |                | '0' = Bit is cle | ared             | x = Bit is unki | nown  |  |  |  |  |  |  |

|               |                                                                                   |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 7         |                                                                                   | k Source Select                    | bit            |                  |                  |                 |       |  |  |  |  |  |  |

|               | <u>Asynchronous mode:</u><br>Don't care.                                          |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | <u>Synchronous mode:</u><br>1 = Master mode (clock generated internally from BRG) |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                   | node (clock gen<br>ode (clock from |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 6         |                                                                                   | ransmit Enable                     |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit o         |                                                                                   | 9-bit transmissio                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Selects                                                                       | 8-bit transmissio                  | on             |                  |                  |                 |       |  |  |  |  |  |  |

| bit 5         | <b>TXEN:</b> Transmit Enable bit <sup>(1)</sup>                                   |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Transmit enabled                                                              |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Transmit disabled                                                             |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 4         | SYNC: EUSART Mode Select bit<br>1 = Synchronous mode                              |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                   | onous mode                         |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 3         | •                                                                                 | nd Break Chara                     | cter bit       |                  |                  |                 |       |  |  |  |  |  |  |

|               | Asynchronous mode:                                                                |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Send Sync Break on next transmission (cleared by hardware upon completion)    |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Sync Break transmission completed<br>Synchronous mode:                        |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Don't care.                                                                       | s mode.                            |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 2         |                                                                                   | n Baud Rate Sel                    | ect bit        |                  |                  |                 |       |  |  |  |  |  |  |

|               | Asynchrono                                                                        |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = High spe                                                                      |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Low spe                                                                       |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Synchronou<br>Unused in th                                                        |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 1         |                                                                                   | smit Shift Regist                  | ter Status bit |                  |                  |                 |       |  |  |  |  |  |  |

| -             | 1 = TSR em                                                                        | -                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 0 = TSR full                                                                      |                                    |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 0         | <b>TX9D:</b> 9th b                                                                | it of Transmit Da                  | ata            |                  |                  |                 |       |  |  |  |  |  |  |

|               | Can be add                                                                        | naaa/data hit an a                 | a manifu / hit |                  |                  |                 |       |  |  |  |  |  |  |

# REGISTER 20-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

**Note 1:** SREN/CREN overrides TXEN in Sync mode with the exception that SREN has no effect in Synchronous Slave mode.

| R/W-0                         | R/W-0                                                                                                                                              | R/W-0                            | R/W-0                              | R/W-0             | R-0              | R-0                              | R-x     |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------|-------------------|------------------|----------------------------------|---------|--|--|--|--|--|

| SPEN                          | RX9                                                                                                                                                | SREN                             | CREN                               | ADDEN             | FERR             | OERR                             | RX9D    |  |  |  |  |  |

| bit 7                         |                                                                                                                                                    |                                  |                                    |                   |                  |                                  | bit     |  |  |  |  |  |

| Legend:                       |                                                                                                                                                    |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

| <b>∟egenu.</b><br>R = Readabl | e hit                                                                                                                                              | W = Writable                     | hit                                | II = I Inimplen   | nented bit, read | 1 as 'O'                         |         |  |  |  |  |  |

| -n = Value at                 |                                                                                                                                                    | '1' = Bit is set                 |                                    | '0' = Bit is clea |                  | x = Bit is unkr                  |         |  |  |  |  |  |

|                               |                                                                                                                                                    | 1 - Dit 13 3C                    |                                    |                   | arcu             |                                  |         |  |  |  |  |  |

| bit 7                         | SPEN: Serial Port Enable bit                                                                                                                       |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | 1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)                                                                      |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | 0 = Serial port disabled (held in Reset)                                                                                                           |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

| bit 6                         |                                                                                                                                                    | eceive Enable                    | oit                                |                   |                  |                                  |         |  |  |  |  |  |

|                               |                                                                                                                                                    | -bit reception<br>-bit reception |                                    |                   |                  |                                  |         |  |  |  |  |  |

| bit 5                         | SREN: Single                                                                                                                                       | e Receive Enal                   | ole bit                            |                   |                  |                                  |         |  |  |  |  |  |

|                               | Asynchronous mode:<br>Don't care.                                                                                                                  |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | <u>Synchronous mode – Master:</u><br>1 = Enables single receive<br>0 = Disables single receive<br>This bit is cleared after reception is complete. |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | Synchronous mode – Slave:<br>Don't care.                                                                                                           |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

| bit 4                         | CREN: Conti                                                                                                                                        | nuous Receive                    | Enable bit                         |                   |                  |                                  |         |  |  |  |  |  |

|                               | Asynchronous mode:<br>1 = Enables receiver<br>0 = Disables receiver                                                                                |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | Synchronous mode:                                                                                                                                  |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                  |                                    |                   |                  |                                  |         |  |  |  |  |  |

| bit 3                         | ADDEN: Add                                                                                                                                         | Iress Detect Er                  | able bit                           |                   |                  |                                  |         |  |  |  |  |  |

|                               | 1 = Enables<br>0 = Disables                                                                                                                        |                                  | tion, enables i<br>tion, all bytes | •                 |                  | buffer when RS<br>be used as pai |         |  |  |  |  |  |

| bit 2                         | FERR: Fram                                                                                                                                         | ing Error bit                    |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               |                                                                                                                                                    | error (can be u                  | pdated by rea                      | ding RCREG re     | egister and rec  | eiving next valic                | l byte) |  |  |  |  |  |

| bit 1                         | OERR: Over                                                                                                                                         | run Error bit                    |                                    |                   |                  |                                  |         |  |  |  |  |  |

|                               | 1 = Overrun<br>0 = No overru                                                                                                                       | •                                | eared by clea                      | ring bit CREN)    |                  |                                  |         |  |  |  |  |  |

| bit 0                         | RX9D: 9th bi                                                                                                                                       | t of Received D                  | Data                               |                   |                  |                                  |         |  |  |  |  |  |

|                               |                                                                                                                                                    |                                  |                                    |                   | alculated by us  |                                  |         |  |  |  |  |  |

# REGISTER 20-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

# EXAMPLE 20-1: CALCULATING BAUD RATE ERROR

| For a device with FOSC | of   | 6 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|------------------------|------|-----------------------------------------------------------------|

| Desired Baud Rate      | =    | Fosc/(64 ([SPBRGH:SPBRG] + 1))                                  |

| Solving for SPBRGH:S   | SPBI | RG:                                                             |

| Х                      | =    | ((FOSC/Desired Baud Rate)/64) – 1                               |

|                        | =    | ((16000000/9600)/64) - 1                                        |

|                        | =    | [25.042] = 25                                                   |

| Calculated Baud Rate   | =    | 1600000/(64 (25 + 1))                                           |

|                        | =    | 9615                                                            |

| Error                  | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate    |

|                        | =    | (9615 - 9600)/9600 = 0.16%                                      |

|                        |      |                                                                 |

# TABLE 20-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7                                               | Bit 6                                   | Bit 5       | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on page |  |

|---------|-----------------------------------------------------|-----------------------------------------|-------------|-------------|-------|-------|-------|-------|-------------------------|--|

| TXSTA   | CSRC                                                | CSRC TX9 TXEN SYNC SENDB BRGH TRMT TX9D |             |             |       |       |       |       |                         |  |

| RCSTA   | SPEN                                                | RX9                                     | SREN        | CREN        | ADDEN | FERR  | OERR  | RX9D  | 55                      |  |

| BAUDCON | ABDOVF                                              | RCIDL                                   | RXDTP       | TXCKP       | BRG16 | —     | WUE   | ABDEN | 55                      |  |

| SPBRGH  | PBRGH EUSART Baud Rate Generator Register High Byte |                                         |             |             |       |       |       |       |                         |  |

| SPBRG   | EUSART B                                            | aud Rate C                              | Generator R | egister Low | Byte  |       |       |       | 55                      |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

Even when the dedicated port is enabled, the ICSP functions remain available through the legacy port. When VIHH is seen on the MCLR/VPP/RE3 pin, the state of the ICRST/ICVPP pin is ignored.

- Note 1: The ICPRT Configuration bit can only be programmed through the default ICSP port (MCLR/RB6/RB7).

- The ICPRT Configuration bit must be maintained clear for all 28-pin and 40-pin devices; otherwise, unexpected operation may occur.

# 25.9.2 28-PIN EMULATION

Devices in 44-pin TQFP packages also have the ability to change their configuration under external control for debugging purposes. This allows the device to behave as if it were a 28-pin device.

This 28-pin Configuration mode is controlled through a single pin, NC/ICPORTS. Connecting this pin to VSS forces the device to function as a 28-pin device. Features normally associated with the 40/44-pin devices are disabled along with their corresponding control registers and bits. This includes PORTD and PORTE, the SPP and the Enhanced PWM functionality of CCP1. On the other hand, connecting the pin to VDD forces the device to function in its default configuration.

The configuration option is only available when background debugging and the dedicated ICD/ICSP port are both enabled (DEBUG Configuration bit is clear and ICPRT Configuration bit is set). When disabled, NC/ICPORTS is a No Connect pin.

# 25.10 Single-Supply ICSP Programming

The LVP Configuration bit enables Single-Supply ICSP Programming (formerly known as *Low-Voltage ICSP Programming* or *LVP*). When Single-Supply Programming is enabled, the microcontroller can be programmed without requiring high voltage being applied to the MCLR/VPP/RE3 pin, but the RB5/KBI1/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

While programming using <u>Single-Supply</u> Programming, VDD is applied to the MCLR/VPP/RE3 pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-Voltage Programming is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP Programming mode, the RB5 pin can no longer be used as a general purpose I/O pin and should be held low during normal operation.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 5 in the TRISB register must be cleared to disable the pull-up on RB5 and ensure the proper operation of the device.

- 4: If the device Master Clear is disabled, verify that either of the following is done to ensure proper entry into ICSP mode:

- a) disable Low-Voltage Programming (CONFIG4L<2> = 0); or

- b) make certain that RB5/KBI1/PGM is held low during entry into ICSP.

If Single-Supply ICSP Programming mode will not be used, the LVP bit can be cleared. RB5/KB11/PGM then becomes available as the digital I/O pin, RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/VPP/RE3 pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using either a Block Erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a Block Erase is required. If a Block Erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

# TABLE 26-2: PIC18FXXXX INSTRUCTION SET

| Mnemo    | onic,                           | Description                              | Quality    | 16-Bit Instruction Word |      |      |      | Status          | Nata       |  |

|----------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|------|-----------------|------------|--|

| Opera    | nds                             | Description                              | Cycles     | MSb                     | LSb  |      | LSb  | Affected        | Notes      |  |

| BYTE-ORI | ENTED O                         | OPERATIONS                               |            |                         |      |      |      |                 |            |  |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |  |

| ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |  |