Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 24KB (12K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4455-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 3.0 POWER-MANAGED MODES

PIC18F2455/2550/4455/4550 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- · Sleep mode

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 3.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS1:SCS0 bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

# 3.1.1 CLOCK SOURCES

The SCS1:SCS0 bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock, as defined by the FOSC3:FOSC0 Configuration bits

- The secondary clock (the Timer1 oscillator)

- The internal oscillator block (for RC modes)

#### 3.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 3.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| TADLE 3-1. | FUVER                |           | DES     |             |                                                                                  |

|------------|----------------------|-----------|---------|-------------|----------------------------------------------------------------------------------|

| Mada       | OSCCON<7,1:0>        |           | Modul   | e Clocking  | Augilable Cleak and Casillater Source                                            |

| Mode       | IDLEN <sup>(1)</sup> | SCS1:SCS0 | CPU     | Peripherals | Available Clock and Oscillator Source                                            |

| Sleep      | 0                    | N/A       | Off     | Off         | None – all clocks are disabled                                                   |

| PRI_RUN    | N/A                  | 00        | Clocked | Clocked     | Primary – all oscillator modes.<br>This is the normal full-power execution mode. |

| SEC_RUN    | N/A                  | 01        | Clocked | Clocked     | Secondary – Timer1 oscillator                                                    |

| RC_RUN     | N/A                  | lx        | Clocked | Clocked     | Internal oscillator block <sup>(2)</sup>                                         |

| PRI_IDLE   | 1                    | 00        | Off     | Clocked     | Primary – all oscillator modes                                                   |

| SEC_IDLE   | 1                    | 01        | Off     | Clocked     | Secondary – Timer1 oscillator                                                    |

| RC_IDLE    | 1                    | 1x        | Off     | Clocked     | Internal oscillator block <sup>(2)</sup>                                         |

TABLE 3-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

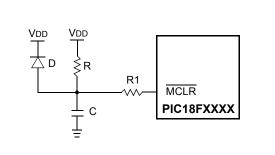

# 4.2 Master Clear Reset (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18F2455/2550/4455/4550 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See **Section 10.5 "PORTE, TRISE and LATE Registers"** for more information.

## 4.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004, **Section 28.1 "DC Characteristics"**). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

#### FIGURE 4-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

# 4.5 Device Reset Timers

PIC18F2455/2550/4455/4550 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of the PIC18F2455/2550/ 4455/4550 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 (Table 28-12) for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33, Table 28-12). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, HS and HSPLL modes and only on Power-on Reset or on exit from most power-managed modes.

### 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR condition has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT mode. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, all time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator    | Power-up <sup>(2)</sup> and                            | Power-up <sup>(2)</sup> and Brown-out |                                 |  |  |  |

|---------------|--------------------------------------------------------|---------------------------------------|---------------------------------|--|--|--|

| Configuration | PWRTEN = 0                                             | PWRTEN = 1                            | Power-Managed Mode              |  |  |  |

| HS, XT        | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                             | 1024 Tosc                       |  |  |  |

| HSPLL, XTPLL  | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup>       | 1024 Tosc + 2 ms <sup>(2)</sup> |  |  |  |

| EC, ECIO      | 66 ms <sup>(1)</sup>                                   | —                                     | —                               |  |  |  |

| ECPLL, ECPIO  | 66 ms <sup>(1)</sup> + 2 ms <sup>(2)</sup>             | 2 ms <sup>(2)</sup>                   | 2 ms <sup>(2)</sup>             |  |  |  |

| INTIO, INTCKO | 66 ms <sup>(1)</sup>                                   | _                                     | —                               |  |  |  |

| INTHS, INTXT  | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                             | 1024 Tosc                       |  |  |  |

#### TABLE 4-2: TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

**2**: 2 ms is the nominal time required for the PLL to lock.

| Register Applicable Device |      | ces  | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |           |

|----------------------------|------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|-----------|-----------|

| CCPR1H                     | 2455 | 2550 | 4455                               | 4550                                                             | XXXX XXXX                       | սսսս սսսս | սսսս սսսս |

| CCPR1L                     | 2455 | 2550 | 4455                               | 4550                                                             | XXXX XXXX                       | սսսս սսսս | սսսս սսսս |

| CCP1CON                    | 2455 | 2550 | 4455                               | 4550                                                             | 00 0000                         | 00 0000   | uu uuuu   |

|                            | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | սսսս սսսս |

| CCPR2H                     | 2455 | 2550 | 4455                               | 4550                                                             | XXXX XXXX                       | սսսս սսսս | սսսս սսսս |

| CCPR2L                     | 2455 | 2550 | 4455                               | 4550                                                             | XXXX XXXX                       | սսսս սսսս | սսսս սսսս |

| CCP2CON                    | 2455 | 2550 | 4455                               | 4550                                                             | 00 0000                         | 00 0000   | uu uuuu   |

| BAUDCON                    | 2455 | 2550 | 4455                               | 4550                                                             | 0100 0-00                       | 0100 0-00 | uuuu u-uu |

| ECCP1DEL                   | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | սսսս սսսս |

| ECCP1AS                    | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | սսսս սսսս |

| CVRCON                     | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| CMCON                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0111                       | 0000 0111 | uuuu uuuu |

| TMR3H                      | 2455 | 2550 | 4455                               | 4550                                                             | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |

| TMR3L                      | 2455 | 2550 | 4455                               | 4550                                                             | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |

| T3CON                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | սսսս սսսս | uuuu uuuu |

| SPBRGH                     | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| SPBRG                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | սսսս սսսս |

| RCREG                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| TXREG                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| TXSTA                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0010                       | 0000 0010 | uuuu uuuu |

| RCSTA                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 000x                       | 0000 000x | uuuu uuuu |

| EEADR                      | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| EEDATA                     | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | սսսս սսսս |

| EECON2                     | 2455 | 2550 | 4455                               | 4550                                                             | 0000 0000                       | 0000 0000 | 0000 0000 |

| EECON1                     | 2455 | 2550 | 4455                               | 4550                                                             | xx-0 x000                       | uu-0 u000 | uu-0 u000 |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 4: See Table 4-3 for Reset value for specific condition.

- **5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

| File Name            | Bit 7                | Bit 6                 | Bit 5              | Bit 4              | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Value on<br>POR, BOR | Details<br>on page |

|----------------------|----------------------|-----------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------|--------------------|

| EEADR                | EEPROM Ad            | dress Register        |                    |                    |                    |                    |                    |                    | 0000 0000            | 55, 91             |

| EEDATA               | EEPROM Da            | ita Register          |                    |                    |                    |                    |                    |                    | 0000 0000            | 55, 91             |

| EECON2               | EEPROM Co            | ntrol Register        | 2 (not a physic    | cal register)      |                    |                    |                    |                    | 0000 0000            | 55, 82             |

| EECON1               | EEPGD                | CFGS                  | _                  | FREE               | WRERR              | WREN               | WR                 | RD                 | xx-0 x000            | 55, 83             |

| IPR2                 | OSCFIP               | CMIP                  | USBIP              | EEIP               | BCLIP              | HLVDIP             | TMR3IP             | CCP2IP             | 1111 1111            | 56, 109            |

| PIR2                 | OSCFIF               | CMIF                  | USBIF              | EEIF               | BCLIF              | HLVDIF             | TMR3IF             | CCP2IF             | 0000 0000            | 56, 105            |

| PIE2                 | OSCFIE               | CMIE                  | USBIE              | EEIE               | BCLIE              | HLVDIE             | TMR3IE             | CCP2IE             | 0000 0000            | 56, 107            |

| IPR1                 | SPPIP <sup>(3)</sup> | ADIP                  | RCIP               | TXIP               | SSPIP              | CCP1IP             | TMR2IP             | TMR1IP             | 1111 1111            | 56, 108            |

| PIR1                 | SPPIF <sup>(3)</sup> | ADIF                  | RCIF               | TXIF               | SSPIF              | CCP1IF             | TMR2IF             | TMR1IF             | 0000 0000            | 56, 104            |

| PIE1                 | SPPIE <sup>(3)</sup> | ADIE                  | RCIE               | TXIE               | SSPIE              | CCP1IE             | TMR2IE             | TMR1IE             | 0000 0000            | 56, 106            |

| OSCTUNE              | INTSRC               | _                     | _                  | TUN4               | TUN3               | TUN2               | TUN1               | TUN0               | 00 0000              | 56, 28             |

| TRISE <sup>(3)</sup> | _                    | _                     | _                  | _                  | _                  | TRISE2             | TRISE1             | TRISE0             | 111                  | 56, 126            |

| TRISD <sup>(3)</sup> | TRISD7               | TRISD6                | TRISD5             | TRISD4             | TRISD3             | TRISD2             | TRISD1             | TRISD0             | 1111 1111            | 56, 124            |

| TRISC                | TRISC7               | TRISC6                | _                  | _                  | _                  | TRISC2             | TRISC1             | TRISC0             | 11111                | 56, 121            |

| TRISB                | TRISB7               | TRISB6                | TRISB5             | TRISB4             | TRISB3             | TRISB2             | TRISB1             | TRISB0             | 1111 1111            | 56, 118            |

| TRISA                | _                    | TRISA6 <sup>(4)</sup> | TRISA5             | TRISA4             | TRISA3             | TRISA2             | TRISA1             | TRISA0             | -111 1111            | 56, 115            |

| LATE <sup>(3)</sup>  | _                    | _                     | _                  | _                  | _                  | LATE2              | LATE1              | LATE0              | xxx                  | 56, 126            |

| LATD <sup>(3)</sup>  | LATD7                | LATD6                 | LATD5              | LATD4              | LATD3              | LATD2              | LATD1              | LATD0              | XXXX XXXX            | 56, 124            |

| LATC                 | LATC7                | LATC6                 | _                  | _                  | _                  | LATC2              | LATC1              | LATC0              | xxxxx                | 56, 121            |

| LATB                 | LATB7                | LATB6                 | LATB5              | LATB4              | LATB3              | LATB2              | LATB1              | LATB0              | XXXX XXXX            | 56, 118            |

| LATA                 | _                    | LATA6 <sup>(4)</sup>  | LATA5              | LATA4              | LATA3              | LATA2              | LATA1              | LATA0              | -xxx xxxx            | 56, 115            |

| PORTE                | RDPU <sup>(3)</sup>  | _                     | _                  | _                  | RE3 <sup>(5)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | 0 x000               | 56, 125            |

| PORTD <sup>(3)</sup> | RD7                  | RD6                   | RD5                | RD4                | RD3                | RD2                | RD1                | RD0                | XXXX XXXX            | 56, 124            |

| PORTC                | RC7                  | RC6                   | RC5 <sup>(6)</sup> | RC4 <sup>(6)</sup> | _                  | RC2                | RC1                | RC0                | xxxx -xxx            | 56, 121            |

| PORTB                | RB7                  | RB6                   | RB5                | RB4                | RB3                | RB2                | RB1                | RB0                | XXXX XXXX            | 56, 118            |

| PORTA                | _                    | RA6 <sup>(4)</sup>    | RA5                | RA4                | RA3                | RA2                | RA1                | RA0                | -x0x 0000            | 56, 115            |

| UEP15                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP14                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP13                | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP12                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP11                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP10                |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP9                 |                      | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP8                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP7                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP6                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP5                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP4                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP3                 | _                    | _                     | _                  | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP2                 | _                    |                       |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP1                 | _                    | _                     |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

| UEP0                 |                      |                       |                    | EPHSHK             | EPCONDIS           | EPOUTEN            | EPINEN             | EPSTALL            | 0 0000               | 57, 172            |

|                      |                      |                       |                    |                    |                    |                    |                    |                    |                      |                    |

| TABLE 5-2: | REGISTER | FILE SUMMARY | (CONTINUED) |

|------------|----------|--------------|-------------|

|            |          |              |             |

Legend:

x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

Bit 21 of the TBLPTRU allows access to the device Configuration bits.

Note 1:

2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

7:  $I^2C^{TM}$  Slave mode only.

The PPBRST bit (UCON<6>) controls the Reset status when Double-Buffering mode (ping-pong buffering) is used. When the PPBRST bit is set, all Ping-Pong Buffer Pointers are set to the Even buffers. PPBRST has to be cleared by firmware. This bit is ignored in buffering modes not using ping-pong buffering.

The PKTDIS bit (UCON<4>) is a flag indicating that the SIE has disabled packet transmission and reception. This bit is set by the SIE when a SETUP token is received to allow setup processing. This bit cannot be set by the microcontroller, only cleared; clearing it allows the SIE to continue transmission and/or reception. Any pending events within the Buffer Descriptor Table will still be available, indicated within the USTAT register's FIFO buffer.

The RESUME bit (UCON<2>) allows the peripheral to perform a remote wake-up by executing Resume signaling. To generate a valid remote wake-up, firmware must set RESUME for 10 ms and then clear the bit. For more information on Resume signaling, see Sections 7.1.7.5, 11.4.4 and 11.9 in the USB 2.0 specification.

The SUSPND bit (UCON<1>) places the module and supporting circuitry (i.e., voltage regulator) in a low-power mode. The input clock to the SIE is also disabled. This bit should be set by the software in response to an IDLEIF interrupt. It should be reset by the microcontroller firmware after an ACTVIF interrupt is observed. When this bit is active, the device remains attached to the bus but the transceiver outputs remain Idle. The voltage on the VUSB pin may vary depending on the value of this bit. Setting this bit before a IDLEIF request will result in unpredictable bus behavior.

**Note:** While in Suspend mode, a typical bus powered USB device is limited to 2.5 mA of current. Care should be taken to assure minimum current draw when the device enters Suspend mode.

### 17.2.2 USB CONFIGURATION REGISTER (UCFG)

Prior to communicating over USB, the module's associated internal and/or external hardware must be configured. Most of the configuration is performed with the UCFG register (Register 17-2). The separate USB voltage regulator (see **Section 17.2.2.8** "Internal **Regulator**") is controlled through the Configuration registers.

The UFCG register contains most of the bits that control the system level behavior of the USB module. These include:

- Bus Speed (full speed versus low speed)

- On-Chip Pull-up Resistor Enable

- On-Chip Transceiver Enable

- Ping-Pong Buffer Usage

The UCFG register also contains two bits which aid in module testing, debugging and USB certifications. These bits control output enable state monitoring and eye pattern generation.

**Note:** The USB speed, transceiver and pull-up should only be configured during the module setup phase. It is not recommended to switch these settings while the module is enabled.

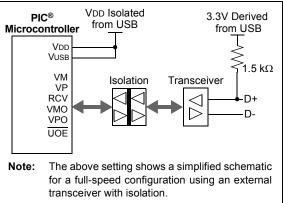

#### 17.2.2.1 Internal Transceiver

The USB peripheral has a built-in, USB 2.0, full-speed and low-speed compliant transceiver, internally connected to the SIE. This feature is useful for low-cost single chip applications. The UTRDIS bit (UCFG<3>) controls the transceiver; it is enabled by default (UTRDIS = 0). The FSEN bit (UCFG<2>) controls the transceiver speed; setting the bit enables full-speed operation.

The on-chip USB pull-up resistors are controlled by the UPUEN bit (UCFG<4>). They can only be selected when the on-chip transceiver is enabled.

The USB specification requires 3.3V operation for communications; however, the rest of the chip may be running at a higher voltage. Thus, the transceiver is supplied power from a separate source, VUSB.

#### 17.2.2.2 External Transceiver

This module provides support for use with an off-chip transceiver. The off-chip transceiver is intended for applications where physical conditions dictate the location of the transceiver to be away from the SIE. External transceiver operation is enabled by setting the UTRDIS bit.

### 19.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

## REGISTER 19-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| SMP<br>bit 7<br>Legend:<br>R = Reada<br>-n = Value<br>bit 7 | at POR<br>SMP: Samp<br><u>SPI Master I</u><br>1 = Input da | <u>mode:</u>                           | P              | S<br>U = Unimpler<br>'0' = Bit is cle | R/W<br>mented bit, rea | UA<br>ad as '0'<br>x = Bit is unkr | BF<br>bit 0 |

|-------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|----------------|---------------------------------------|------------------------|------------------------------------|-------------|

| Legend:<br>R = Reada<br>-n = Value                          | at POR<br>SMP: Samp<br><u>SPI Master I</u><br>1 = Input da | '1' = Bit is set<br>le bit<br>mode:    | bit            | •                                     |                        |                                    |             |

| R = Reada<br>-n = Value                                     | at POR<br>SMP: Samp<br><u>SPI Master I</u><br>1 = Input da | '1' = Bit is set<br>le bit<br>mode:    | bit            | •                                     |                        |                                    | nown        |

| R = Reada<br>-n = Value                                     | at POR<br>SMP: Samp<br><u>SPI Master I</u><br>1 = Input da | '1' = Bit is set<br>le bit<br>mode:    | bit            | •                                     |                        |                                    | nown        |

| -n = Value                                                  | at POR<br>SMP: Samp<br><u>SPI Master I</u><br>1 = Input da | '1' = Bit is set<br>le bit<br>mode:    | bit            | •                                     |                        |                                    | nown        |

|                                                             | <b>SMP</b> : Samp<br><u>SPI Master</u><br>1 = Input da     | le bit<br>node:                        |                | '0' = Bit is cle                      | ared                   | x = Bit is unkr                    | nown        |

| bit 7                                                       | <u>SPI Master</u><br>1 = Input da                          | <u>mode:</u>                           |                |                                       |                        |                                    |             |

| DIT /                                                       | <u>SPI Master</u><br>1 = Input da                          | <u>mode:</u>                           |                |                                       |                        |                                    |             |

|                                                             | 1 = Input da                                               |                                        |                |                                       |                        |                                    |             |

|                                                             |                                                            |                                        | d of data out  | tout time                             |                        |                                    |             |

|                                                             |                                                            | ta sampled at mi                       |                |                                       |                        |                                    |             |

|                                                             | SPI Slave m                                                | -                                      |                |                                       |                        |                                    |             |

|                                                             |                                                            | e cleared when                         | SPI is used i  | n Slave mode.                         |                        |                                    |             |

| bit 6                                                       | CKE: SPI C                                                 | lock Select bit <sup>(1)</sup>         |                |                                       |                        |                                    |             |

|                                                             |                                                            | t occurs on trans<br>t occurs on trans |                |                                       |                        |                                    |             |

| bit 5                                                       | D/A: Data/A                                                | ddress bit                             |                |                                       |                        |                                    |             |

|                                                             | Used in I <sup>2</sup> C                                   | mode only.                             |                |                                       |                        |                                    |             |

| bit 4                                                       | P: Stop bit                                                |                                        |                |                                       |                        |                                    |             |

|                                                             | Used in I <sup>2</sup> C                                   | mode only. This                        | bit is cleared | I when the MSS                        | P module is d          | isabled, SSPEN                     | is cleared. |

| bit 3                                                       | S: Start bit                                               |                                        |                |                                       |                        |                                    |             |

|                                                             | Used in I <sup>2</sup> C                                   | •                                      |                |                                       |                        |                                    |             |

| bit 2                                                       |                                                            | Write Information                      | ı bit          |                                       |                        |                                    |             |

|                                                             | Used in I <sup>2</sup> C                                   | •                                      |                |                                       |                        |                                    |             |

| bit 1                                                       | UA: Update                                                 |                                        |                |                                       |                        |                                    |             |

|                                                             | Used in I <sup>2</sup> C                                   | 5                                      |                |                                       |                        |                                    |             |

| bit 0                                                       |                                                            | ull Status bit (Re                     |                | only)                                 |                        |                                    |             |

|                                                             |                                                            | complete, SSPE                         |                | 4                                     |                        |                                    |             |

|                                                             | 0 = Receive                                                | not complete, S                        | SPBUF IS er    | npty                                  |                        |                                    |             |

| Note 1:                                                     | Polarity of clock s                                        | tate is set by the                     | e CKP bit (SS  | SPCON1<4>).                           |                        |                                    |             |

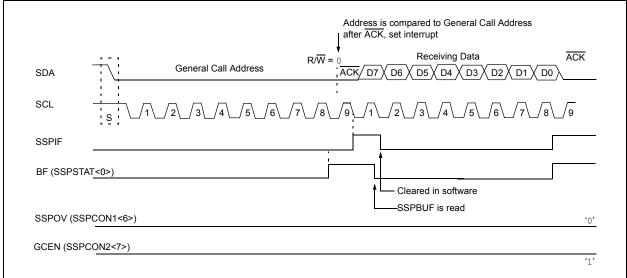

#### 19.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable (GCEN) bit is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware. If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 19-17).

# PIC18F2455/2550/4455/4550

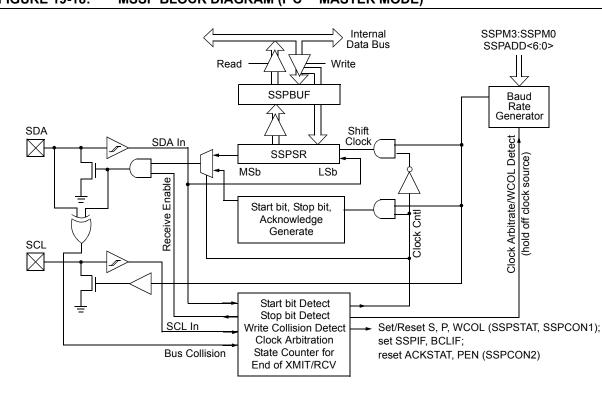

### 19.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\sf I}^2{\sf C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options:

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (and MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

# FIGURE 19-18: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

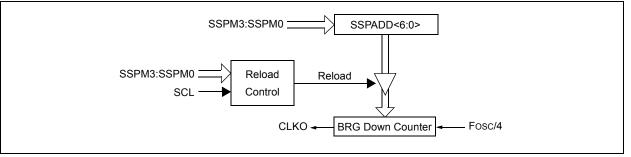

### 19.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower seven bits of the SSPADD register (Figure 19-19). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to '0' and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state. Table 19-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD. SSPADD values of less than 2 are not supported. Due to the need to support I<sup>2</sup>C clock stretching capability, I<sup>2</sup>C baud rates are partially dependent upon system parameters, such as line capacitance and pull-up strength. The parameters provided in Table 19-3 are guidelines, and the actual baud rate may be slightly slower than that predicted in the table. The baud rate formula shown in the bit description of Register 19-4 sets the maximum baud rate that can occur for a given SSPADD value.

## FIGURE 19-19: BAUD RATE GENERATOR BLOCK DIAGRAM

### TABLE 19-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE W/BRG

| Fcy    | Fcy * 2 | BRG Value | Fsc∟<br>(2 Rollovers of BRG) |

|--------|---------|-----------|------------------------------|

| 10 MHz | 20 MHz  | 18h       | 400 kHz <sup>(1)</sup>       |

| 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 4 MHz  | 8 MHz   | 09h       | 400 kHz <sup>(1)</sup>       |

| 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 1 MHz  | 2 MHz   | 02h       | 333 kHz <sup>(1)</sup>       |

| 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

**Note 1:** The I<sup>2</sup>C<sup>™</sup> interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

# PIC18F2455/2550/4455/4550

| R/W-0         | R-1                                         | R/W-0                                                       | R/W-0            | R/W-0           | U-0            | R/W-0             | R/W-0           |  |  |

|---------------|---------------------------------------------|-------------------------------------------------------------|------------------|-----------------|----------------|-------------------|-----------------|--|--|

| ABDOVF        | RCIDL                                       | RXDTP                                                       | TXCKP            | BRG16           | _              | WUE               | ABDEN           |  |  |

| bit 7         |                                             |                                                             |                  | 1               |                |                   | bit (           |  |  |

| Legend:       |                                             |                                                             |                  |                 |                |                   |                 |  |  |

| R = Readable  | e bit                                       | W = Writable                                                | bit              | U = Unimple     | mented bit, re | ad as '0'         |                 |  |  |

| -n = Value at | POR                                         | '1' = Bit is se                                             | t                | ʻ0' = Bit is cl | eared          | x = Bit is unk    | nown            |  |  |

| bit 7         |                                             | Auto-Baud Acqu                                              |                  |                 | te Detect mode | e (must be cleare | ed in software  |  |  |

|               |                                             | G rollover has o                                            | Ų                |                 |                |                   |                 |  |  |

| bit 6         | RCIDL: Red                                  | eive Operation                                              | Idle Status bit  |                 |                |                   |                 |  |  |

|               |                                             | e operation is Idl<br>e operation is ac                     |                  |                 |                |                   |                 |  |  |

| bit 5         | RXDTP: Re                                   | ceived Data Pol                                             | larity Select bi | t               |                |                   |                 |  |  |

|               | Asynchrono<br>1 = RX data<br>0 = RX data    |                                                             | inverted         |                 |                |                   |                 |  |  |

|               |                                             | <u>is modes:</u><br>ed Data (DT) is i<br>rsion of Data (D   |                  |                 | evel.          |                   |                 |  |  |

| bit 4         |                                             | ock and Data Po                                             |                  | -               |                |                   |                 |  |  |

|               | Asynchrono                                  | ous mode:                                                   |                  |                 |                |                   |                 |  |  |

|               | •                                           | <u>is modes:</u><br>CK) is inverted. I<br>rsion of Clock (0 |                  | •               |                |                   |                 |  |  |

| bit 3         | BRG16: 16-Bit Baud Rate Register Enable bit |                                                             |                  |                 |                |                   |                 |  |  |

|               |                                             | aud Rate Generaud Rate Genera                               |                  |                 |                | BRGH value ign    | ored            |  |  |

| bit 2         | Unimpleme                                   | ented: Read as                                              | '0'              |                 |                |                   |                 |  |  |

| bit 1         | WUE: Wake                                   | e-up Enable bit                                             |                  |                 |                |                   |                 |  |  |

|               | hardwa                                      |                                                             | rising edge      | -               | rrupt generate | d on falling edge | ; bit cleared i |  |  |

|               | <u>Synchronou</u><br>Unused in t            |                                                             |                  |                 |                |                   |                 |  |  |

| bit 0         | ABDEN: Au                                   | ito-Baud Detect                                             | Enable bit       |                 |                |                   |                 |  |  |

|               | cleared                                     |                                                             | on completion    | ı.              | cter. Requires | reception of a Sy | nc field (55h   |  |  |

|               | Synchronou<br>Unused in t                   | <u>is mode:</u>                                             |                  |                 |                |                   |                 |  |  |

# REGISTER 20-3: BAUDCON: BAUD RATE CONTROL REGISTER

#### 20.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 20-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value, 55h (ASCII "U", which is also the LIN bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up, using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin, or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH:SPBRG register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 20-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH register. Refer to Table 20-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. The contents of RCREG should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

#### TABLE 20-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |  |  |  |  |  |  |

|-------|------|-------------------|--|--|--|--|--|--|

| 0     | 0    | Fosc/512          |  |  |  |  |  |  |

| 0     | 1    | Fosc/128          |  |  |  |  |  |  |

| 1     | 0    | Fosc/128          |  |  |  |  |  |  |

| 1     | 1    | Fosc/32           |  |  |  |  |  |  |

|       |      |                   |  |  |  |  |  |  |

**Note:** During the ABD sequence, SPBRG and SPBRGH are both used as a 16-bit counter, independent of the BRG16 setting.

#### 20.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

# 22.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RA0 through RA5, as well as the on-chip voltage reference (see **Section 23.0 "Comparator Voltage Reference Module**"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register. The CMCON register (Register 22-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 22-1.

### REGISTER 22-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0           | R-0                                | R/W-0            | R/W-0          | R/W-0            | R/W-1           | R/W-1           | R/W-1 |

|---------------|------------------------------------|------------------|----------------|------------------|-----------------|-----------------|-------|

| C2OUT         | C1OUT                              | C2INV            | C1INV          | CIS              | CM2             | CM1             | CM0   |

| bit 7         |                                    |                  |                |                  |                 |                 | bit 0 |

|               |                                    |                  |                |                  |                 |                 |       |

| Legend:       |                                    |                  |                |                  |                 |                 |       |

| R = Readabl   | e bit                              | W = Writable     | bit            | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at | POR                                | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| h it <b>7</b> | 000117                             |                  |                |                  |                 |                 |       |

| bit 7         |                                    | parator 2 Outp   | ut dit         |                  |                 |                 |       |

|               | <u>When C2INV</u><br>1 = C2 VIN+ > |                  |                |                  |                 |                 |       |

|               | 0 = C2 VIN + 4                     |                  |                |                  |                 |                 |       |

|               | When C2INV                         |                  |                |                  |                 |                 |       |

|               | 1 = C2 VIN+ <                      |                  |                |                  |                 |                 |       |

|               | 0 = C2 VIN+ 2                      | > C2 VIN-        |                |                  |                 |                 |       |

| bit 6         | C1OUT: Com                         | parator 1 Outp   | ut bit         |                  |                 |                 |       |

|               | When C1INV                         | <u>= 0:</u>      |                |                  |                 |                 |       |

|               | 1 = C1 VIN+ >                      |                  |                |                  |                 |                 |       |

|               | 0 = C1 VIN+ <                      |                  |                |                  |                 |                 |       |

|               | When C1INV                         |                  |                |                  |                 |                 |       |

|               | 1 = C1 VIN+ <<br>0 = C1 VIN+ >     | -                |                |                  |                 |                 |       |

| bit 5         |                                    | parator 2 Outpu  | t Inversion hi | t                |                 |                 |       |

| bit 0         | 1 = C2 outpu                       |                  |                | ·                |                 |                 |       |

|               | 0 = C2 outpu                       |                  |                |                  |                 |                 |       |

| bit 4         | •                                  | parator 1 Outpu  | t Inversion bi | t                |                 |                 |       |

|               | 1 = C1 outpu                       | t inverted       |                |                  |                 |                 |       |

|               | 0 = C1 outpu                       | t not inverted   |                |                  |                 |                 |       |

| bit 3         | CIS: Compar                        | ator Input Swite | h bit          |                  |                 |                 |       |

|               | When CM2:C                         | CMO = 110:       |                |                  |                 |                 |       |

|               |                                    | connects to RA   |                |                  |                 |                 |       |

|               |                                    | connects to RA   |                | CVREF            |                 |                 |       |

|               |                                    | connects to RA   |                |                  |                 |                 |       |

| bit 2-0       |                                    | omparator Mod    |                |                  |                 |                 |       |

|               |                                    | hows the Com     |                | s and the CM2    | CM0 hit settin  | as              |       |

|               |                                    |                  |                |                  |                 | 93.             |       |

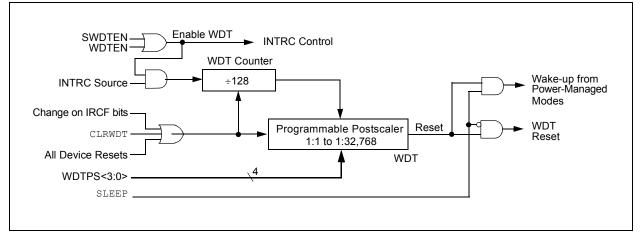

# 25.2 Watchdog Timer (WDT)

For PIC18F2455/2550/4455/4550 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### 25.2.1 CONTROL REGISTER

Register 25-15 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

#### FIGURE 25-1: WDT BLOCK DIAGRAM

# PIC18F2455/2550/4455/4550

| BNC          |                                                                              | Branch if N                                                                | lot Carry                                             |                                                      | BNN          |                                                                                 | Branch if I                                                            | Not Negative                                                                        |                                         |

|--------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|--------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------|

| Synta        | ax:                                                                          | BNC n                                                                      |                                                       |                                                      | Synta        | ax:                                                                             | BNN n                                                                  |                                                                                     |                                         |

| Oper         | ands:                                                                        | -128 ≤ n ≤ 1                                                               | 127                                                   |                                                      | Oper         | ands:                                                                           | -128 ≤ n ≤                                                             | 127                                                                                 |                                         |

| Oper         | ation:                                                                       | if Carry bit i<br>(PC) + 2 + 2                                             |                                                       |                                                      | Oper         | ation:                                                                          | if Negative<br>(PC) + 2 +                                              |                                                                                     |                                         |

| Statu        | s Affected:                                                                  | None                                                                       |                                                       |                                                      | Statu        | s Affected:                                                                     | None                                                                   |                                                                                     |                                         |

| Enco         | ding:                                                                        | 1110                                                                       | 0011 nni                                              | nn nnnn                                              | Enco         | ding:                                                                           | 1110                                                                   | 0111 ni                                                                             | nnn nnnn                                |