Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

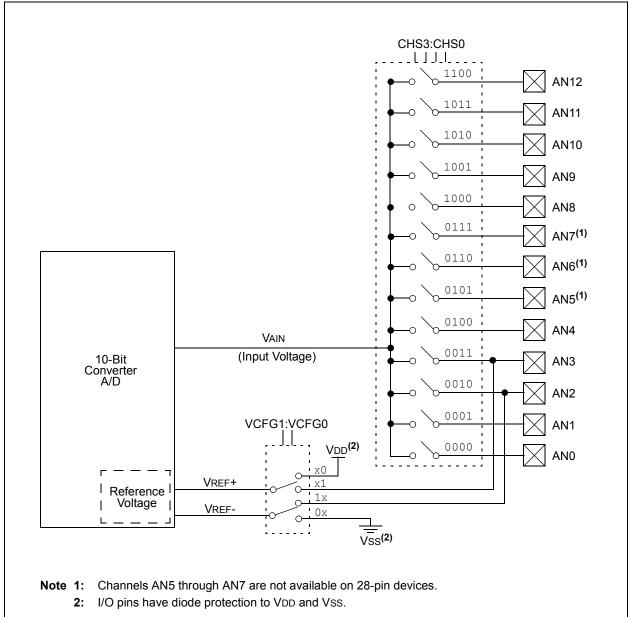

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4550-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F2455 PIC18LF2455

- PIC18F2550

PIC18LF2550

- PIC18F4455 PIC18LF4455

- PIC18F4550 PIC18LF4550

This family of devices offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Enhanced Flash program memory. In addition to these features, the PIC18F2455/2550/4455/4550 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

## 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2455/2550/4455/4550 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4%, of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 28.0 "Electrical Characteristics" for values.

#### 1.1.2 UNIVERSAL SERIAL BUS (USB)

Devices in the PIC18F2455/2550/4455/4550 family incorporate a fully featured Universal Serial Bus communications module that is compliant with the USB Specification Revision 2.0. The module supports both low-speed and full-speed communication for all supported data transfer types. It also incorporates its own on-chip transceiver and 3.3V regulator and supports the use of external transceivers and voltage regulators.

### 1.1.3 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2455/2550/4455/4550 family offer twelve different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes using crystals or ceramic resonators.

- Four External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- An internal oscillator block which provides an 8 MHz clock (±2% accuracy) and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of 6 user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. This option frees an oscillator pin for use as an additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and External Oscillator modes, which allows a wide range of clock speeds from 4 MHz to 48 MHz.

- Asynchronous dual clock operation, allowing the USB module to run from a high-frequency oscillator while the rest of the microcontroller is clocked from an internal low-power oscillator.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

# 2.0 OSCILLATOR CONFIGURATIONS

## 2.1 Overview

Devices in the PIC18F2455/2550/4455/4550 family incorporate a different oscillator and microcontroller clock system than previous PIC18F devices. The addition of the USB module, with its unique requirements for a stable clock source, make it necessary to provide a separate clock source that is compliant with both USB low-speed and full-speed specifications.

To accommodate these requirements, PIC18F2455/ 2550/4455/4550 devices include a new clock branch to provide a 48 MHz clock for full-speed USB operation. Since it is driven from the primary clock source, an additional system of prescalers and postscalers has been added to accommodate a wide range of oscillator frequencies. An overview of the oscillator structure is shown in Figure 2-1.

Other oscillator features used in PIC18 enhanced microcontrollers, such as the internal oscillator block and clock switching, remain the same. They are discussed later in this chapter.

#### 2.1.1 OSCILLATOR CONTROL

The operation of the oscillator in PIC18F2455/2550/ 4455/4550 devices is controlled through two Configuration registers and two control registers. Configuration registers, CONFIG1L and CONFIG1H, select the oscillator mode and USB prescaler/postscaler options. As Configuration bits, these are set when the device is programmed and left in that configuration until the device is reprogrammed.

The OSCCON register (Register 2-2) selects the Active Clock mode; it is primarily used in controlling clock switching in power-managed modes. Its use is discussed in **Section 2.4.1** "Oscillator Control **Register**".

The OSCTUNE register (Register 2-1) is used to trim the INTRC frequency source, as well as select the low-frequency clock source that drives several special features. Its use is described in **Section 2.2.5.2 "OSCTUNE Register"**.

# 2.2 Oscillator Types

PIC18F2455/2550/4455/4550 devices can be operated in twelve distinct oscillator modes. In contrast with previous PIC18 enhanced microcontrollers, four of these modes involve the use of two oscillator types at once. Users can program the FOSC3:FOSC0 Configuration bits to select one of these modes:

- 1. XT Crystal/Resonator

- 2. HS High-Speed Crystal/Resonator

- 3. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 4. EC External Clock with Fosc/4 Output

- 5. ECIO External Clock with I/O on RA6

- 6. ECPLL External Clock with PLL Enabled and Fosc/4 Output on RA6

- 7. ECPIO External Clock with PLL Enabled, I/O on RA6

- 8. INTHS Internal Oscillator used as Microcontroller Clock Source, HS Oscillator used as USB Clock Source

- 9. INTIO Internal Oscillator used as Microcontroller Clock Source, EC Oscillator used as USB Clock Source, Digital I/O on RA6

- 10. INTCKO Internal Oscillator used as Microcontroller Clock Source, EC Oscillator used as USB Clock Source, Fosc/4 Output on RA6

# 2.2.1 OSCILLATOR MODES AND USB OPERATION

Because of the unique requirements of the USB module, a different approach to clock operation is necessary. In previous PIC<sup>®</sup> devices, all core and peripheral clocks were driven by a single oscillator source; the usual sources were primary, secondary or the internal oscillator. With PIC18F2455/2550/4455/4550 devices, the primary oscillator becomes part of the USB module and cannot be associated to any other clock source. Thus, the USB module must be clocked from the primary clock source; however, the microcontroller core and other peripherals can be separately clocked from the secondary or internal oscillators as before.

Because of the timing requirements imposed by USB, an internal clock of either 6 MHz or 48 MHz is required while the USB module is enabled. Fortunately, the microcontroller and other peripherals are not required to run at this clock speed when using the primary oscillator. There are numerous options to achieve the USB module clock requirement and still provide flexibility for clocking the rest of the device from the primary oscillator source. These are detailed in **Section 2.3 "Oscillator Settings for USB"**.

# 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 28-12). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

# 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

# 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 25.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

### 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 25.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 25.4 "Fail-Safe Clock Monitor"**) is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

# PIC18F2455/2550/4455/4550

| Register | Applicable Devices |      | er Applicable Devices |      | Register Applicable Devices |           | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|----------|--------------------|------|-----------------------|------|-----------------------------|-----------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| TOSU     | 2455               | 2550 | 4455                  | 4550 | 0 0000                      | 0 0000    | 0 uuuu <b>(1)</b>                  |                                                                  |                                 |  |

| TOSH     | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | uuuu uuuu <b>(1)</b>               |                                                                  |                                 |  |

| TOSL     | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | uuuu uuuu <b>(1)</b>               |                                                                  |                                 |  |

| STKPTR   | 2455               | 2550 | 4455                  | 4550 | 00-0 0000                   | uu-0 0000 | uu-u uuuu <b>(1)</b>               |                                                                  |                                 |  |

| PCLATU   | 2455               | 2550 | 4455                  | 4550 | 0 0000                      | 0 0000    | u uuuu                             |                                                                  |                                 |  |

| PCLATH   | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | uuuu uuuu                          |                                                                  |                                 |  |

| PCL      | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | PC + 2 <sup>(3)</sup>              |                                                                  |                                 |  |

| TBLPTRU  | 2455               | 2550 | 4455                  | 4550 | 00 0000                     | 00 0000   | uu uuuu                            |                                                                  |                                 |  |

| TBLPTRH  | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | սսսս սսսս                          |                                                                  |                                 |  |

| TBLPTRL  | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | սսսս սսսս                          |                                                                  |                                 |  |

| TABLAT   | 2455               | 2550 | 4455                  | 4550 | 0000 0000                   | 0000 0000 | นนนน นนนน                          |                                                                  |                                 |  |

| PRODH    | 2455               | 2550 | 4455                  | 4550 | XXXX XXXX                   | uuuu uuuu | uuuu uuuu                          |                                                                  |                                 |  |

| PRODL    | 2455               | 2550 | 4455                  | 4550 | XXXX XXXX                   | uuuu uuuu | นนนน นนนน                          |                                                                  |                                 |  |

| INTCON   | 2455               | 2550 | 4455                  | 4550 | 0000 000x                   | 0000 000u | uuuu uuuu <b>(2)</b>               |                                                                  |                                 |  |

| INTCON2  | 2455               | 2550 | 4455                  | 4550 | 1111 -1-1                   | 1111 -1-1 | uuuu -u-u <b>(2)</b>               |                                                                  |                                 |  |

| INTCON3  | 2455               | 2550 | 4455                  | 4550 | 11-0 0-00                   | 11-0 0-00 | uu-u u-uu <b>(2)</b>               |                                                                  |                                 |  |

| INDF0    | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| POSTINC0 | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| POSTDEC0 | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| PREINC0  | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| PLUSW0   | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| FSR0H    | 2455               | 2550 | 4455                  | 4550 | 0000                        | 0000      | uuuu                               |                                                                  |                                 |  |

| FSR0L    | 2455               | 2550 | 4455                  | 4550 | XXXX XXXX                   | սսսս սսսս | սսսս սսսս                          |                                                                  |                                 |  |

| WREG     | 2455               | 2550 | 4455                  | 4550 | XXXX XXXX                   | uuuu uuuu | սսսս սսսս                          |                                                                  |                                 |  |

| INDF1    | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| POSTINC1 | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| POSTDEC1 | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| PREINC1  | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| PLUSW1   | 2455               | 2550 | 4455                  | 4550 | N/A                         | N/A       | N/A                                |                                                                  |                                 |  |

| FSR1H    | 2455               | 2550 | 4455                  | 4550 | 0000                        | 0000      | uuuu                               |                                                                  |                                 |  |

| FSR1L    | 2455               | 2550 | 4455                  | 4550 | XXXX XXXX                   | uuuu uuuu | นนนน นนนน                          |                                                                  |                                 |  |

| BSR      | 2455               | 2550 | 4455                  | 4550 | 0000                        | 0000      | uuuu                               |                                                                  |                                 |  |

| TABLE 4-4: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 4: See Table 4-3 for Reset value for specific condition.

- **5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

## 5.3.5 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM in the data memory space. SFRs start at the top of data memory and extend downward to occupy the top segment of Bank 15, from F60h to FFFh. A list of these registers is given in Table 5-1 and Table 5-2.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the

peripheral functions. The Reset and interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

| TABLE 5-1: SPECIAL FUNCTION REGISTER | ۲ MAP |

|--------------------------------------|-------|

|--------------------------------------|-------|

| Address | Name                    | Address | Name                    | Address | Name                  | Address | Name                 | Address | Name                   |

|---------|-------------------------|---------|-------------------------|---------|-----------------------|---------|----------------------|---------|------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                | F9Fh    | IPR1                 | F7Fh    | UEP15                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                | F9Eh    | PIR1                 | F7Eh    | UEP14                  |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | CCP1CON               | F9Dh    | PIE1                 | F7Dh    | UEP13                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H                | F9Ch    | (2)                  | F7Ch    | UEP12                  |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L                | F9Bh    | OSCTUNE              | F7Bh    | UEP11                  |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON               | F9Ah    | (2)                  | F7Ah    | UEP10                  |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                   | F99h    | (2)                  | F79h    | UEP9                   |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON               | F98h    | (2)                  | F78h    | UEP8                   |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP1DEL              | F97h    | (2)                  | F77h    | UEP7                   |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCP1AS               | F96h    | TRISE <sup>(3)</sup> | F76h    | UEP6                   |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CVRCON                | F95h    | TRISD <sup>(3)</sup> | F75h    | UEP5                   |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                 | F94h    | TRISC                | F74h    | UEP4                   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | TMR3H                 | F93h    | TRISB                | F73h    | UEP3                   |

| FF2h    | INTCON                  | FD2h    | HLVDCON                 | FB2h    | TMR3L                 | F92h    | TRISA                | F72h    | UEP2                   |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | T3CON                 | F91h    | (2)                  | F71h    | UEP1                   |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                | F90h    | (2)                  | F70h    | UEP0                   |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                 | F8Fh    | (2)                  | F6Fh    | UCFG                   |

|         |                         | FCEh    | TMR1L                   | FAEh    | RCREG                 | F8Eh    | (2)                  | F6Eh    | UADDR                  |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                 | F8Dh    | LATE <sup>(3)</sup>  | F6Dh    | UCON                   |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                 | F8Ch    | LATD <sup>(3)</sup>  | F6Ch    | USTAT                  |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA                 | F8Bh    | LATC                 | F6Bh    | UEIE                   |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                   | F8Ah    | LATB                 | F6Ah    | UEIR                   |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR                 | F89h    | LATA                 | F69h    | UIE                    |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA                | F88h    | (2)                  | F68h    | UIR                    |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2 <sup>(1)</sup> | F87h    | (2)                  | F67h    | UFRMH                  |

|         |                         | FC6h    | SSPCON1                 | FA6h    | EECON1                | F86h    | (2)                  | F66h    | UFRML                  |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSPCON2                 | FA5h    | (2)                   | F85h    | (2)                  | F65h    | SPPCON <sup>(3)</sup>  |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | (2)                   | F84h    | PORTE                | F64h    | SPPEPS <sup>(3)</sup>  |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | (2)                   | F83h    | PORTD <sup>(3)</sup> | F63h    | SPPCFG <sup>(3)</sup>  |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                  | F82h    | PORTC                | F62h    | SPPDATA <sup>(3)</sup> |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                  | F81h    | PORTB                | F61h    | (2)                    |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                  | F80h    | PORTA                | F60h    | (2)                    |

Note 1: Not a physical register.

2: Unimplemented registers are read as '0'.

3: These registers are implemented only on 40/44-pin devices.

## 9.3 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Request (Flag) registers (PIR1 and PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

## REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0                            | R-0                                                | R-0             | R/W-0            | R/W-0                | R/W-0           | R/W-0  |

|----------------------|----------------------------------|----------------------------------------------------|-----------------|------------------|----------------------|-----------------|--------|

| SPPIF <sup>(1)</sup> | ADIF                             | RCIF                                               | TXIF            | SSPIF            | CCP1IF               | TMR2IF          | TMR1IF |

| bit 7                |                                  |                                                    |                 |                  |                      |                 | bit 0  |

|                      |                                  |                                                    |                 |                  |                      |                 |        |

| Legend:              | . L.'A                           |                                                    | L 14            |                  |                      | L (0)           |        |

| R = Readable         |                                  | W = Writable                                       |                 | •                | mented bit, read     |                 |        |

| -n = Value at        | PUR                              | '1' = Bit is set                                   |                 | '0' = Bit is cle | ared                 | x = Bit is unkr | IOWI   |

| bit 7                | SPPIF: Strea                     | ming Parallel P                                    | ort Read/Writ   | te Interrupt Fla | g bit <sup>(1)</sup> |                 |        |

|                      |                                  | or a write operat<br>or write has oc               |                 | place (must b    | e cleared in sof     | tware)          |        |

| bit 6                | ADIF: A/D C                      | onverter Interru                                   | pt Flag bit     |                  |                      |                 |        |

|                      |                                  | conversion com<br>conversion is r                  |                 | be cleared in s  | oftware)             |                 |        |

| bit 5                | RCIF: EUSA                       | RT Receive Inte                                    | errupt Flag bit | t                |                      |                 |        |

|                      |                                  | SART receive b<br>SART receive b                   |                 | •                | d when RCREG         | is read)        |        |

| bit 4                | TXIF: EUSA                       | RT Transmit Inte                                   | errupt Flag bi  | t                |                      |                 |        |

|                      |                                  | SART transmit b<br>SART transmit b                 |                 | G, is empty (cle | ared when TXR        | EG is written)  |        |

| bit 3                | SSPIF: Mast                      | er Synchronous                                     | Serial Port I   | nterrupt Flag b  | it                   |                 |        |

|                      |                                  | smission/recept<br>o transmit/recei                |                 | te (must be cle  | ared in software     | e)              |        |

| bit 2                | CCP1IF: CC                       | P1 Interrupt Fla                                   | g bit           |                  |                      |                 |        |

|                      |                                  | <u>le:</u><br>register capture<br>1 register captu |                 | ust be cleared   | in software)         |                 |        |

|                      |                                  |                                                    |                 |                  | cleared in softw     | vare)           |        |

|                      | <u>PWM mode:</u><br>Unused in th |                                                    |                 |                  |                      |                 |        |

| bit 1                | TMR2IF: TM                       | R2 to PR2 Mate                                     | ch Interrupt Fl | lag bit          |                      |                 |        |

|                      |                                  | PR2 match oc<br>2 to PR2 match                     |                 | be cleared in s  | oftware)             |                 |        |

| bit 0                | TMR1IF: TM                       | R1 Overflow Int                                    | errupt Flag b   | it               |                      |                 |        |

|                      |                                  | egister overflowe<br>gister did not o              |                 | leared in softw  | vare)                |                 |        |

|                      |                                  |                                                    |                 |                  |                      |                 |        |

Note 1: This bit is reserved on 28-pin devices; always maintain this bit clear.

## 10.5 PORTE, TRISE and LATE Registers

Depending on the particular PIC18F2455/2550/4455/ 4550 device selected, PORTE is implemented in two different ways.

For 40/44-pin devices, PORTE is a 4-bit wide port. Three pins (RE0/AN5/CK1SPP, RE1/AN6/CK2SPP and RE2/AN7/OESPP) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

In addition to port data, the PORTE register (Register 10-1) also contains the RDPU control bit (PORTE<7>); this enables or disables the weak pull-ups on PORTD.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On a Power-on Reset, RE2:RE0 a | re |

|-------|--------------------------------|----|

|       | configured as analog inputs.   |    |

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

# REGISTER 10-1: PORTE REGISTER

The fourth pin of PORTE ( $\overline{\text{MCLR}/\text{VPP}/\text{RE3}}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |

|-------|----------------------------------------|

|       | a digital input only if Master Clear   |

|       | functionality is disabled.             |

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by |

|-------|--------|-----------------------|

|       |        | ; clearing output     |

|       |        | ; data latches        |

| CLRF  | LATE   | ; Alternate method    |

|       |        | ; to clear output     |

|       |        | ; data latches        |

| MOVLW | 0Ah    | ; Configure A/D       |

| MOVWF | ADCON1 | ; for digital inputs  |

| MOVLW | 03h    | ; Value used to       |

|       |        | ; initialize data     |

|       |        | ; direction           |

| MOVLW | 07h    | ; Turn off            |

| MOVWF | CMCON  | ; comparators         |

| MOVWF | TRISC  | ; Set RE<0> as inputs |

|       |        | ; RE<1> as outputs    |

|       |        | ; RE<2> as inputs     |

#### 10.5.1 PORTE IN 28-PIN DEVICES

For 28-pin devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

| R/W-0               | U-0 | U-0 | U-0 | R/W-x                | R/W-0              | R/W-0              | R/W-0              |

|---------------------|-----|-----|-----|----------------------|--------------------|--------------------|--------------------|

| RDPU <sup>(3)</sup> | —   | —   | —   | RE3 <sup>(1,2)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> |

| bit 7               |     |     |     |                      |                    |                    | bit 0              |

|                     |     |     |     |                      |                    |                    |                    |

|                     |     |     |     |                      |                    |                    |                    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | RDPU: PORTD Pull-up Enable bit                                 |

|---------|----------------------------------------------------------------|

|         | 1 = PORTD pull-ups are enabled by individual port latch values |

|         | 0 = All PORTD pull-ups are disabled                            |

| bit 6-4 | Unimplemented: Read as '0'                                     |

| bit 3-0 | RE3:RE0: PORTE Data Input bits <sup>(1,2,3)</sup>              |

- **Note 1:** implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0); otherwise, read as '0'.

- 2: RE3 is the only PORTE bit implemented on both 28-pin and 40/44-pin devices. All other bits are implemented only when PORTE is implemented (i.e., 40/44-pin devices).

- 3: Unimplemented in 28-pin devices; read as '0'.

# 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Module Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:          |                 |                                           |                                   |                  |

|------------------|-----------------|-------------------------------------------|-----------------------------------|------------------|

| R = Readable bit |                 | W = Writable bit                          | U = Unimplemented bit             | , read as '0'    |

| -n = Value a     | at POR          | '1' = Bit is set                          | x = Bit is unknown                |                  |

| bit 7            | <b>RD16:</b> 10 | 6-Bit Read/Write Mode Enal                | ble bit                           |                  |

|                  | 1 = Ena         | oles register read/write of Ti            | mer1 in one 16-bit operation      |                  |

|                  |                 | •                                         | mer1 in two 8-bit operations      |                  |

| bit 6            | T1RUN:          | Timer1 System Clock Status                | s bit                             |                  |

|                  | 1 = Dev         | ce clock is derived from Tim              | ner1 oscillator                   |                  |

|                  | 0 = Dev         | ce clock is derived from and              | other source                      |                  |

| bit 5-4          | T1CKPS          | 1:T1CKPS0: Timer1 Input (                 | Clock Prescale Select bits        |                  |

|                  | 11 <b>= 1:8</b> | Prescale value                            |                                   |                  |

|                  |                 | Prescale value                            |                                   |                  |

|                  |                 | Prescale value                            |                                   |                  |

|                  |                 | Prescale value                            |                                   |                  |

| bit 3            |                 | N: Timer1 Oscillator Enable               | bit                               |                  |

|                  |                 | r1 oscillator is enabled                  |                                   |                  |

|                  |                 | er1 oscillator is shut off                | resistor are turned off to elimir | nate nower drain |

| bit 2            |                 |                                           |                                   |                  |

|                  |                 | . Time T External Clock inp<br>/R1CS = 1: | ut Synchronization Select bit     |                  |

|                  |                 | ot synchronize external cloc              | k input                           |                  |

|                  |                 | hronize external clock input              |                                   |                  |

|                  | -               | /IR1CS = 0:                               |                                   |                  |

|                  | This bit is     | s ignored. Timer1 uses the i              | nternal clock when TMR1CS =       | • 0.             |

| bit 1            | TMR1CS          | : Timer1 Clock Source Sele                | ect bit                           |                  |

|                  | 1 = Exte        | rnal clock from RC0/T1OSC                 | D/T13CKI pin (on the rising edg   | ge)              |

|                  |                 | nal clock (Fosc/4)                        |                                   |                  |

| bit 0            | TMR10           | I: Timer1 On bit                          |                                   |                  |

|                  | 1 = Ena         | bles Timer1                               |                                   |                  |

|                  | 0 = Stop        | s Timer1                                  |                                   |                  |

## 17.2.4 USB ENDPOINT CONTROL

Each of the 16 possible bidirectional endpoints has its own independent control register, UEPn (where 'n' represents the endpoint number). Each register has an identical complement of control bits. The prototype is shown in Register 17-4.

The EPHSHK bit (UEPn<4>) controls handshaking for the endpoint; setting this bit enables USB handshaking. Typically, this bit is always set except when using isochronous endpoints.

The EPCONDIS bit (UEPn<3>) is used to enable or disable USB control operations (SETUP) through the endpoint. Clearing this bit enables SETUP transactions. Note that the corresponding EPINEN and EPOUTEN bits must be set to enable IN and OUT transactions. For Endpoint 0, this bit should always be cleared since the USB specifications identify Endpoint 0 as the default control endpoint.

The EPOUTEN bit (UEPn<2>) is used to enable or disable USB OUT transactions from the host. Setting this bit enables OUT transactions. Similarly, the EPINEN bit (UEPn<1>) enables or disables USB IN transactions from the host.

The EPSTALL bit (UEPn<0>) is used to indicate a STALL condition for the endpoint. If a STALL is issued on a particular endpoint, the EPSTALL bit for that endpoint pair will be set by the SIE. This bit remains set until it is cleared through firmware, or until the SIE is reset.

| J-0<br>—    | U-0<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0<br>EPHSHK                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FPHSHK                                                                                                                                                                                                                                                                                                                                                                                                                                 | FRONDIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FROUTEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                        | EPCONDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EPOUTEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EPINEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EPSTALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |