Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4550t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

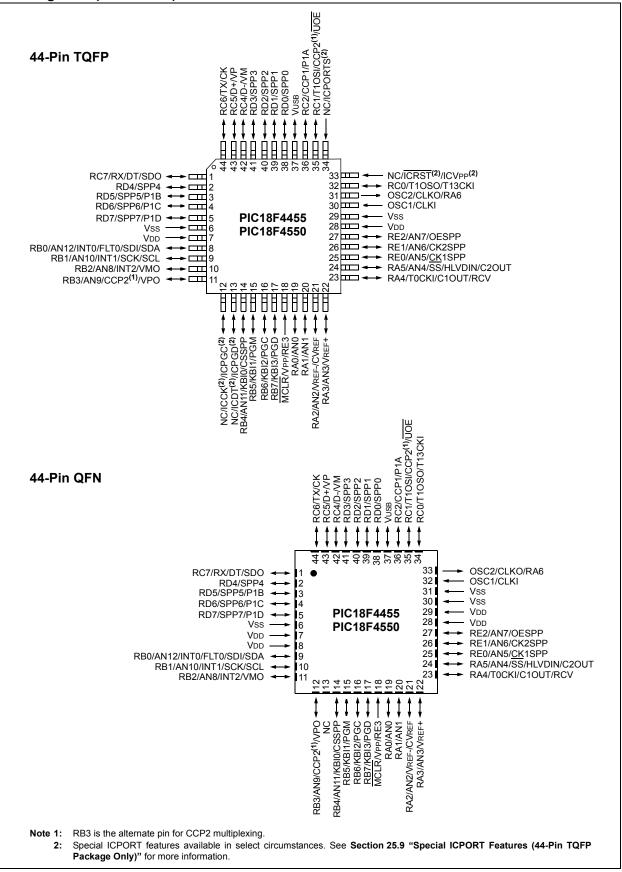

#### **Pin Diagrams (Continued)**

### 2.2.5.4 Compensating for INTOSC Drift

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made and in some cases, how large a change is needed. When using the EUSART, for example, an adjustment may be required when it begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

It is also possible to verify device clock speed against a reference clock. Two timers may be used: one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator. Both timers are cleared but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register. Finally, a CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

## 4.5 Device Reset Timers

PIC18F2455/2550/4455/4550 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of the PIC18F2455/2550/ 4455/4550 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 (Table 28-12) for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33, Table 28-12). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, HS and HSPLL modes and only on Power-on Reset or on exit from most power-managed modes.

#### 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR condition has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT mode. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, all time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator    | Power-up <sup>(2)</sup> and                            | Exit from                       |                                 |  |

|---------------|--------------------------------------------------------|---------------------------------|---------------------------------|--|

| Configuration | PWRTEN = 0                                             | PWRTEN = 1                      | Power-Managed Mode              |  |

| HS, XT        | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

| HSPLL, XTPLL  | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |  |

| EC, ECIO      | 66 ms <sup>(1)</sup>                                   | —                               | —                               |  |

| ECPLL, ECPIO  | 66 ms <sup>(1)</sup> + 2 ms <sup>(2)</sup>             | 2 ms <sup>(2)</sup>             | 2 ms <sup>(2)</sup>             |  |

| INTIO, INTCKO | 66 ms <sup>(1)</sup>                                   | _                               | —                               |  |

| INTHS, INTXT  | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

#### TABLE 4-2: TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

**2**: 2 ms is the nominal time required for the PLL to lock.

#### 5.4 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.6 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.6.1 "Indexed Addressing with Literal Offset**".

## 5.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.4.2 DIRECT ADDRESSING

Direct Addressing mode specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 5.3.4 "General **Purpose Register File**") or a location in the Access Bank (Section 5.3.3 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.3.2 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 5.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

#### EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINCO   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

|         |       |            |   |                |

#### 12.7 Considerations in Asynchronous Counter Mode

Following a Timer1 interrupt and an update to the TMR1 registers, the Timer1 module uses a falling edge on its clock source to trigger the next register update on the rising edge. If the update is completed after the clock input has fallen, the next rising edge will not be counted.

If the application can reliably update TMR1 before the timer input goes low, no additional action is needed. Otherwise, an adjusted update can be performed

following a later Timer1 increment. This can be done by monitoring TMR1L within the interrupt routine until it increments, and then updating the TMR1H:TMR1L register pair while the clock is low, or one-half of the period of the clock source. Assuming that Timer1 is being used as a Real-Time Clock, the clock source is a 32.768 kHz crystal oscillator; in this case, one-half period of the clock is 15.25  $\mu$ s.

The Real-Time Clock application code in Example 12-1 shows a typical ISR for Timer1, as well as the optional code required if the update cannot be done reliably within the required interval.

#### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                                               |

|---------|--------|--------------|---------------------------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                                       |

|         | CLRF   | TMR1L        |                                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator                 |

|         | CLRF   | secs         | ; Initialize timekeeping registers                            |

|         | CLRF   | mins         | ;                                                             |

|         | MOVLW  | .12          |                                                               |

|         | MOVWF  | hours        |                                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timerl interrupt                                     |

|         | RETURN |              |                                                               |

| RTCisr  |        |              |                                                               |

|         |        |              | ; Insert the next 4 lines of code when TMR1                   |

|         |        |              | ; can not be reliably updated before clock pulse goes low     |

|         | BTFSC  | TMR1L,0      | ; wait for TMR1L to become clear                              |

|         | BRA    | \$-2         | ; (may already be clear)                                      |

|         | BTFSS  | TMR1L,0      | ; wait for TMR1L to become set                                |

|         | BRA    | \$-2         | ; TMR1 has just incremented                                   |

|         |        |              | ; If TMR1 update can be completed before clock pulse goes low |

|         |        |              | ; Start ISR here                                              |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                                        |

|         | INCF   | secs, F      | ; Increment seconds                                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                         |

|         | CPFSGT | secs         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | secs         | ; Clear seconds                                               |

|         | INCF   | mins, F      | ; Increment minutes                                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                         |

|         | CPFSGT | mins         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | mins         | ; clear minutes                                               |

|         | INCF   | hours, F     | ; Increment hours                                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                           |

|         | CPFSGT | hours        |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | hours        | ; Reset hours                                                 |

|         | RETURN |              | ; Done                                                        |

|         |        |              |                                                               |

NOTES:

## 15.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 15.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

## TABLE 15-1:CCP MODE – TIMER<br/>RESOURCE

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 14-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 15-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

#### 15.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (capture input, compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                                  |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

### TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

**Note 1:** Includes standard and Enhanced PWM operation.

## 17.0 UNIVERSAL SERIAL BUS (USB)

This section describes the details of the USB peripheral. Because of the very specific nature of the module, knowledge of USB is expected. Some high-level USB information is provided in **Section 17.10 "Overview of USB"** only for application design reference. Designers are encouraged to refer to the official specification published by the USB Implementers Forum (USB-IF) for the latest information. USB specification Revision 2.0 is the most current specification at the time of publication of this document.

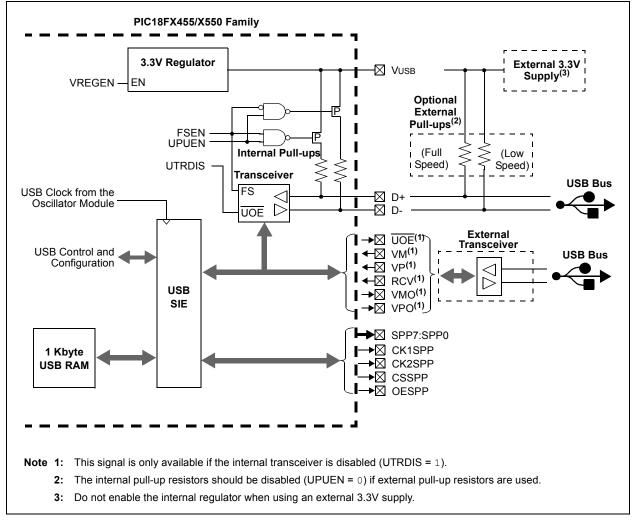

## 17.1 Overview of the USB Peripheral

The PIC18FX455/X550 device family contains a full-speed and low-speed compatible USB Serial Interface Engine (SIE) that allows fast communication between any USB host and the PIC<sup>®</sup> microcontroller. The SIE can be interfaced directly to the USB, utilizing the internal transceiver, or it can be connected through an external transceiver. An internal 3.3V regulator is also available to power the internal transceiver in 5V applications.

Some special hardware features have been included to improve performance. Dual port memory in the device's data memory space (USB RAM) has been supplied to share direct memory access between the microcontroller core and the SIE. Buffer descriptors are also provided, allowing users to freely program endpoint memory usage within the USB RAM space. A Streaming Parallel Port has been provided to support the uninterrupted transfer of large volumes of data, such as isochronous data, to external memory buffers.

Figure 17-1 presents a general overview of the USB peripheral and its features.

FIGURE 17-1: USB PERIPHERAL AND OPTIONS

#### 17.2.5 USB ADDRESS REGISTER (UADDR)

The USB Address register contains the unique USB address that the peripheral will decode when active. UADDR is reset to 00h when a USB Reset is received, indicated by URSTIF, or when a Reset is received from the microcontroller. The USB address must be written by the microcontroller during the USB setup phase (enumeration) as part of the Microchip USB firmware support.

#### 17.2.6 USB FRAME NUMBER REGISTERS (UFRMH:UFRML)

The Frame Number registers contain the 11-bit frame number. The low-order byte is contained in UFRML, while the three high-order bits are contained in UFRMH. The register pair is updated with the current frame number whenever a SOF token is received. For the microcontroller, these registers are read-only. The Frame Number register is primarily used for isochronous transfers.

## 17.3 USB RAM

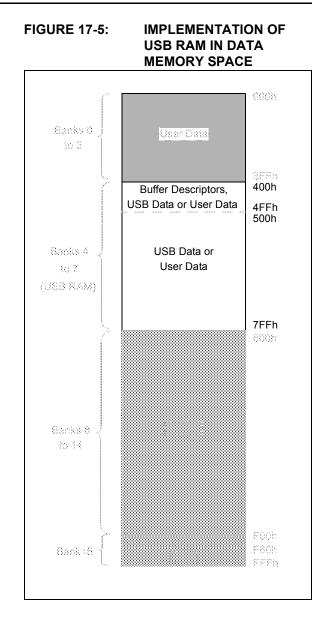

USB data moves between the microcontroller core and the SIE through a memory space known as the USB RAM. This is a special dual port memory that is mapped into the normal data memory space in Banks 4 through 7 (400h to 7FFh) for a total of 1 Kbyte (Figure 17-5).

Bank 4 (400h through 4FFh) is used specifically for endpoint buffer control, while Banks 5 through 7 are available for USB data. Depending on the type of buffering being used, all but 8 bytes of Bank 4 may also be available for use as USB buffer space.

Although USB RAM is available to the microcontroller as data memory, the sections that are being accessed by the SIE should not be accessed by the microcontroller. A semaphore mechanism is used to determine the access to a particular buffer at any given time. This is discussed in **Section 17.4.1.1 "Buffer Ownership**".

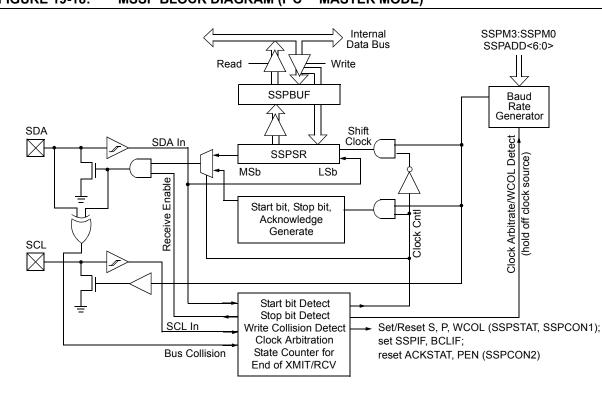

#### 19.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\sf I}^2{\sf C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options:

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (and MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

## FIGURE 19-18: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

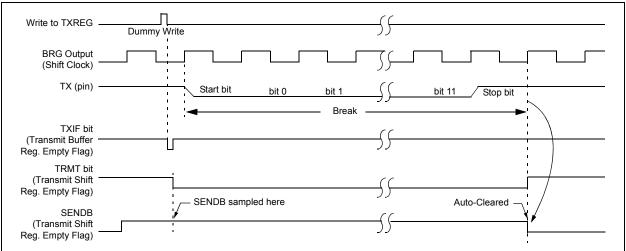

### 20.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift Register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 20-10 for the timing of the Break character sequence.

#### 20.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 20.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 20.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### FIGURE 20-10: SEND BREAK CHARACTER SEQUENCE

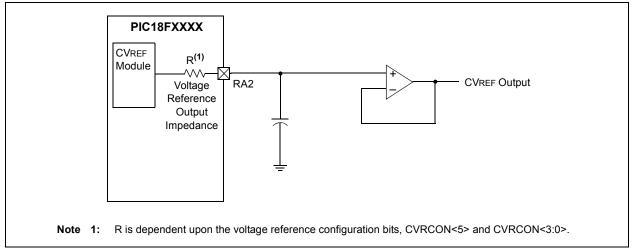

#### FIGURE 23-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 23-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-----------------------|--------|--------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN | CVROE                 | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 55                         |

| CMCON  | C2OUT | C10UT                 | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 55                         |

| TRISA  |       | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 56                         |

Legend: Shaded cells are not used with the comparator voltage reference.

**Note 1:** PORTA<6> and its direction and latch bits are individually configured as port pins based on various oscillator modes. When disabled, these bits read as '0'.

#### REGISTER 25-9: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0                                                 | U-0                                                 | U-0                          | U-0             | R/C-1               | R/C-1             | R/C-1      | R/C-1 |

|-----------------------------------------------------|-----------------------------------------------------|------------------------------|-----------------|---------------------|-------------------|------------|-------|

| —                                                   | —                                                   | —                            | —               | WRT3 <sup>(1)</sup> | WRT2              | WRT1       | WRT0  |

| bit 7                                               |                                                     |                              |                 |                     |                   |            | bit 0 |

|                                                     |                                                     |                              |                 |                     |                   |            |       |

| Legend:                                             |                                                     |                              |                 |                     |                   |            |       |

| R = Readab                                          | ole bit                                             | C = Clearable                | bit             | U = Unimpler        | mented bit, read  | as '0'     |       |

| -n = Value v                                        | vhen device is unp                                  | programmed                   |                 | u = Unchang         | ed from progran   | nmed state |       |

|                                                     |                                                     |                              |                 |                     |                   |            |       |

| bit 7-4                                             | Unimplemen                                          | ted: Read as '               | )'              |                     |                   |            |       |

| bit 3                                               | WRT3: Write                                         | Protection bit <sup>(1</sup> | )               |                     |                   |            |       |

|                                                     | 1 = Block 3 (006000-007FFFh) is not write-protected |                              |                 |                     |                   |            |       |

|                                                     | 0 = Block 3 (0                                      | 06000-007FFF                 | h) is write-pro | otected             |                   |            |       |

| bit 2                                               | WRT2: Write                                         | Protection bit               |                 |                     |                   |            |       |

|                                                     | 1 = Block 2 (004000-005FFFh) is not write-protected |                              |                 |                     |                   |            |       |

|                                                     | 0 = Block 2 (004000-005FFFh) is write-protected     |                              |                 |                     |                   |            |       |

| bit 1 WRT1: Write Protection bit                    |                                                     |                              |                 |                     |                   |            |       |

| 1 = Block 1 (002000-003FFFh) is not write-protected |                                                     |                              |                 |                     |                   |            |       |

| 0 = Block 1 (002000-003FFFh) is write-protected     |                                                     |                              |                 |                     |                   |            |       |

| bit 0                                               | WRT0: Write                                         | Protection bit               |                 |                     |                   |            |       |

|                                                     |                                                     |                              |                 |                     | not write-protect | ed         |       |

|                                                     | 0 = Block  0 (0                                     | 00800-001FFF                 | h) or (001000   | 0-001FFFh) is       | write-protected   |            |       |

|                                                     |                                                     |                              |                 |                     |                   |            |       |

**Note 1:** Unimplemented in PIC18FX455 devices; maintain this bit set.

#### REGISTER 25-10: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/C-1 | R/C-1 | R-1                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> |     | —   | —   | —   | —     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

| Legend:                      |                   |                                     |

|------------------------------|-------------------|-------------------------------------|

| R = Readable bit             | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is ur | nprogrammed       | u = Unchanged from programmed state |

| bit 7   | WRTD: Data EEPROM Write Protection bit                               |

|---------|----------------------------------------------------------------------|

|         | 1 = Data EEPROM is not write-protected                               |

|         | 0 = Data EEPROM is write-protected                                   |

| bit 6   | WRTB: Boot Block Write Protection bit                                |

|         | 1 = Boot block (000000-0007FFh) is not write-protected               |

|         | 0 = Boot block (000000-0007FFh) is write-protected                   |

| bit 5   | WRTC: Configuration Register Write Protection bit <sup>(1)</sup>     |

|         | 1 = Configuration registers (300000-3000FFh) are not write-protected |

|         | 0 = Configuration registers (300000-3000FFh) are write-protected     |

| bit 4-0 | Unimplemented: Read as '0'                                           |

|         |                                                                      |

**Note 1:** This bit is read-only in normal execution mode; it can be written only in Program mode.

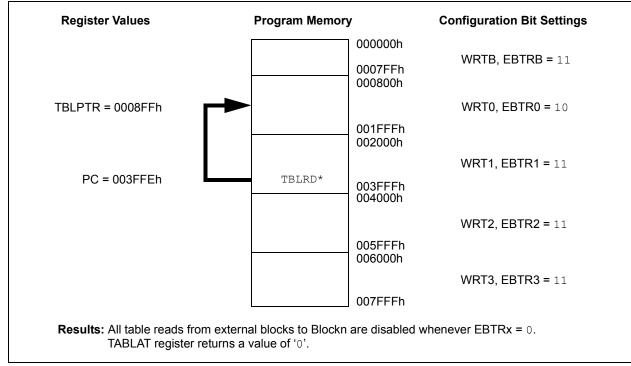

#### FIGURE 25-7: EXTERNAL BLOCK TABLE READ (EBTRx) DISALLOWED

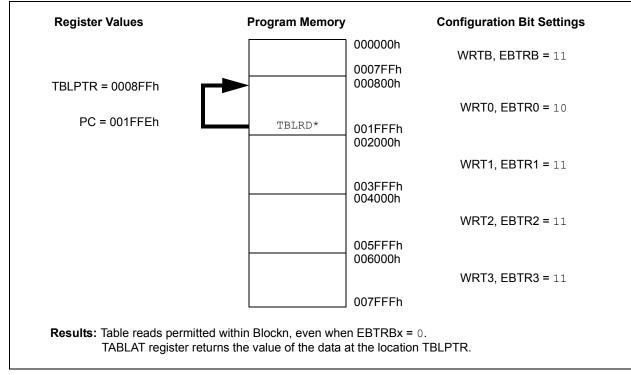

#### FIGURE 25-8: EXTERNAL BLOCK TABLE READ (EBTRx) ALLOWED

## TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                     |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| a               | RAM access bit                                                                                                                                                  |  |  |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                     |  |  |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                    |  |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |  |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |  |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |  |  |  |  |  |

| d               | Destination select bit                                                                                                                                          |  |  |  |  |  |

|                 | d = 0: store result in WREG                                                                                                                                     |  |  |  |  |  |

|                 | d = 1: store result in file register f                                                                                                                          |  |  |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |  |  |  |  |  |

| f               | 8-bit register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                                    |  |  |  |  |  |

| f <sub>s</sub>  | 12-bit register file address (000h to FFFh). This is the source address.                                                                                        |  |  |  |  |  |

| f <sub>d</sub>  | 12-bit register file address (000h to FFFh). This is the destination address.                                                                                   |  |  |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |  |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |  |  |  |  |  |

| label           | Label name.                                                                                                                                                     |  |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.                                                                                |  |  |  |  |  |

|                 | Only used with table read and table write instructions:                                                                                                         |  |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |  |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |  |

| *-              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |  |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                                         |  |  |  |  |  |

|                 | Call/Branch and Return instructions.                                                                                                                            |  |  |  |  |  |

| PC              | Program Counter.                                                                                                                                                |  |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                                       |  |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                                      |  |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |  |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |  |  |  |  |  |

| PD              | Power-Down bit.                                                                                                                                                 |  |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |  |  |  |  |  |

| S               | Fast Call/Return mode select bit                                                                                                                                |  |  |  |  |  |

|                 | s = 0: do not update into/from shadow registers                                                                                                                 |  |  |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                                          |  |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                                     |  |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                                              |  |  |  |  |  |

| TO              | Time-out bit.                                                                                                                                                   |  |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                                                   |  |  |  |  |  |

| u               | Unused or unchanged.                                                                                                                                            |  |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                                                 |  |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                                                 |  |  |  |  |  |

| х               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |

| Zs              | 7-bit offset value for indirect addressing of register files (source).                                                                                          |  |  |  |  |  |

| zd              | 7-bit offset value for indirect addressing of register files (destination).                                                                                     |  |  |  |  |  |

| { }             | Optional argument.                                                                                                                                              |  |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                                                   |  |  |  |  |  |

| (text)          | The contents of text.                                                                                                                                           |  |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                                  |  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                                    |  |  |  |  |  |

| < >             | Register bit field.                                                                                                                                             |  |  |  |  |  |

| E               | In the set of.                                                                                                                                                  |  |  |  |  |  |

|                 | User-defined term (font is Courier New).                                                                                                                        |  |  |  |  |  |

| GOT         | 0                                         | Unconditio                                                            | onal Brai                            | nch                            |                                        |  |

|-------------|-------------------------------------------|-----------------------------------------------------------------------|--------------------------------------|--------------------------------|----------------------------------------|--|

| Synta       | ax:                                       | GOTO k                                                                |                                      |                                |                                        |  |

| Oper        | ands:                                     | $0 \le k \le 104$                                                     | 8575                                 |                                |                                        |  |

| Oper        | ation:                                    | $k \rightarrow PC<20$                                                 | 0:1>                                 |                                |                                        |  |

| Statu       | is Affected:                              | None                                                                  |                                      |                                |                                        |  |

| 1st w       | oding:<br>/ord (k<7:0>)<br>word(k<19:8>)  | 1110<br>1111                                                          | 1111<br>k <sub>19</sub> kkk          | k <sub>7</sub> kkk<br>kkkk     | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |  |

| Desc        | ription:                                  | GOTO allow<br>anywhere v<br>2-Mbyte mo<br>value 'k' is<br>is always a | within the<br>emory rai<br>loaded in | entire<br>nge. The<br>to PC<20 | 20-bit<br>):1>. GOTO                   |  |

| Word        | ls:                                       | 2                                                                     | 2                                    |                                |                                        |  |

| Cycle       | es:                                       | 2                                                                     |                                      |                                |                                        |  |

| QC          | ycle Activity:                            |                                                                       |                                      |                                |                                        |  |

|             | Q1                                        | Q2                                                                    | Q3                                   |                                | Q4                                     |  |

|             | Decode                                    | Read literal<br>'k'<7:0>,                                             | No<br>operat                         | ion 'k                         | ead literal<br>3'<19:8>,<br>rite to PC |  |

|             | No<br>operation                           | No<br>operation                                                       | No<br>operat                         | ion o                          | No<br>peration                         |  |

| <u>Exan</u> | n <u>ple:</u><br>After Instructio<br>PC = |                                                                       | RE<br>HERE)                          |                                |                                        |  |

| INCF                                                                         | Increment                                                                                                                                                               | f                                                                                                                                                 |                                                                                           |                                                               |                                                                                                  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Syntax:                                                                      | INCF f{,                                                                                                                                                                | d {,a}}                                                                                                                                           |                                                                                           |                                                               |                                                                                                  |

| Operands:                                                                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                     |                                                                                                                                                   |                                                                                           |                                                               |                                                                                                  |

| Operation:                                                                   | (f) + 1 $\rightarrow$ d                                                                                                                                                 | est                                                                                                                                               |                                                                                           |                                                               |                                                                                                  |

| Status Affected:                                                             | C, DC, N,                                                                                                                                                               | OV, Z                                                                                                                                             |                                                                                           |                                                               |                                                                                                  |

| Encoding:                                                                    | 0010                                                                                                                                                                    | 10da                                                                                                                                              | fff                                                                                       | f                                                             | ffff                                                                                             |

|                                                                              | placed in V<br>placed bac<br>If 'a' is '0', 1<br>If 'a' is '1', 1<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 20<br>Bit-Orientt | k in regis<br>the Access<br>the BSR i<br>(default).<br>and the ex-<br>led, this i<br>Literal Of<br>never $f \leq 1$<br>5.2.3 "Byther<br>ad Instru | ter 'f' (<br>ss Ban<br>s used<br>(tende<br>nstruc<br>fset A<br>95 (5F<br>te-Ori<br>ctions | (defa<br>ik is<br>d to<br>d in<br>ddre<br>h).<br>ente<br>s in | ault).<br>selected.<br>select the<br>struction<br>operates<br>essing<br>See<br>ed and<br>Indexed |

| Words:                                                                       | Literal Off                                                                                                                                                             | set Mode                                                                                                                                          | e" tor (                                                                                  | deta                                                          | IIS.                                                                                             |

| Cycles:                                                                      | 1                                                                                                                                                                       |                                                                                                                                                   |                                                                                           |                                                               |                                                                                                  |

| Q Cycle Activity:                                                            |                                                                                                                                                                         |                                                                                                                                                   |                                                                                           |                                                               |                                                                                                  |

| Q1                                                                           | Q2                                                                                                                                                                      | Q3                                                                                                                                                |                                                                                           |                                                               | Q4                                                                                               |

| Decode                                                                       | Read<br>register 'f'                                                                                                                                                    | Proce<br>Data                                                                                                                                     |                                                                                           | -                                                             | /rite to<br>stination                                                                            |

| Example:<br>Before Instruc<br>CNT<br>Z<br>C<br>DC<br>After Instructio<br>CNT | = FFh<br>= 0<br>= ?<br>= ?                                                                                                                                              | CNT,                                                                                                                                              | 1, 0                                                                                      |                                                               |                                                                                                  |

| Z<br>C                                                                       | = 000                                                                                                                                                                   |                                                                                                                                                   |                                                                                           |                                                               |                                                                                                  |

| MOVFF                                                | Move f to                                                                                                                                                                                                                 | f                                                                                                                                                                                  |                                                                                                                                                              |                                                                                                                                             |   |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|

| Syntax:                                              | MOVFF f                                                                                                                                                                                                                   | s,f <sub>d</sub>                                                                                                                                                                   |                                                                                                                                                              |                                                                                                                                             |   |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 40 \\ 0 \leq f_d \leq 40 \end{array}$                                                                                                                                                   |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |

| Operation:                                           | $(f_{\text{s}}) \to f_{\text{d}}$                                                                                                                                                                                         |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |

| Status Affected:                                     | None                                                                                                                                                                                                                      |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                              | ffff<br>ffff                                                                                                                                                                       | ffff<br>ffff                                                                                                                                                 | ffff <sub>s</sub><br>ffff <sub>d</sub>                                                                                                      |   |

| Description:                                         | The conter<br>moved to a<br>Location o<br>in the 4096<br>FFFh) and<br>can also b<br>FFFh.<br>Either sou<br>(a useful s<br>MOVFF is p<br>transferring<br>peripheral<br>buffer or a<br>The MOVFT<br>PCL, TOS<br>destination | destinatio<br>f source "<br>6-byte dat<br>l location<br>e anywhe<br>rce or des<br>pecial situ<br>particularly<br>g a data n<br>register (s<br>n I/O port<br>F instructi<br>U, TOSH | n register<br>$f_s$ ' can be<br>a space (<br>of destina<br>re from 0<br>stination c<br>uation).<br>y useful for<br>hemory lo<br>such as th<br>).<br>on canno | 'f <sub>d</sub> '.<br>anywhere<br>000h to<br>tition 'f <sub>d</sub> '<br>00h to<br>an be W<br>or<br>cation to a<br>he transmit<br>t use the |   |

| Words:                                               | 2                                                                                                                                                                                                                         |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |

| Cycles:                                              | 2                                                                                                                                                                                                                         |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                           |                                                                                                                                                                                    |                                                                                                                                                              |                                                                                                                                             |   |

| Q1                                                   | Q2                                                                                                                                                                                                                        | Q3                                                                                                                                                                                 | 8                                                                                                                                                            | Q4                                                                                                                                          | 7 |

| Decode                                               | Read                                                                                                                                                                                                                      | Droce                                                                                                                                                                              |                                                                                                                                                              | No                                                                                                                                          |   |

| MOVLB                                 | Move Liter                                            | al to Lo               | w Nibb            | ole iı          | n BSR                 |

|---------------------------------------|-------------------------------------------------------|------------------------|-------------------|-----------------|-----------------------|

| Syntax:                               | MOVLW k                                               | Ι.                     |                   |                 |                       |

| Operands:                             | $0 \le k \le 255$                                     |                        |                   |                 |                       |

| Operation:                            | $k \to BSR$                                           |                        |                   |                 |                       |

| Status Affected:                      | None                                                  |                        |                   |                 |                       |

| Encoding:                             | 0000                                                  | 0001                   | kkk               | k               | kkkk                  |

| Description:                          | The eight-b<br>Bank Selec<br>of BSR<7:4<br>regardless | t Registe<br>I> always | er (BSF<br>s rema | R). T<br>iins ' | <b>he value</b><br>0' |

| Words:                                | 1                                                     |                        |                   |                 |                       |

| Cycles:                               | 1                                                     |                        |                   |                 |                       |

| Q Cycle Activity:                     |                                                       |                        |                   |                 |                       |

| Q1                                    | Q2                                                    | Q3                     |                   |                 | Q4                    |