Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                                 |

| Core Size                  | 16/32-Bit                                                                             |

| Speed                      | 72MHz                                                                                 |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 160                                                                                   |

| Program Memory Size        | -                                                                                     |

| Program Memory Type        | ROMIess                                                                               |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 82K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                             |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                  |

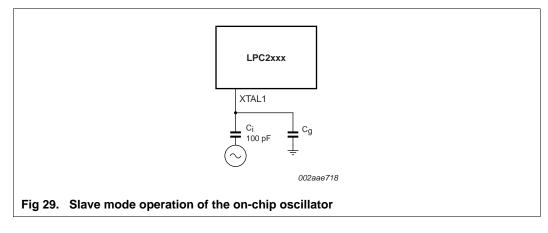

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 208-TFBGA                                                                             |

| Supplier Device Package    | 208-TFBGA (15x15)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2420fet208-551             |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Flashless 16-bit/32-bit microcontroller

| Pin | Symbol                                          | Pin | Symbol                                 | Pin | Symbol                                       | Pin | Symbol                                 |

|-----|-------------------------------------------------|-----|----------------------------------------|-----|----------------------------------------------|-----|----------------------------------------|

| 13  | P2[17]/RAS                                      | 14  | P0[11]/RXD2/SCL2/<br>MAT3[1]           | 15  | P4[4]/A4                                     | 16  | P4[5]/A5                               |

| 17  | P4[20]/A20/<br>SDA2/SCK1                        |     | -                                      |     | -                                            |     | -                                      |

| Row | ι T                                             |     |                                        |     |                                              |     |                                        |

| 1   | P0[27]/SDA0                                     | 2   | P0[31]/USB_D+2                         | 3   | P3[26]/D26/<br>MAT0[1]/PWM1[3]               | 4   | P2[26]/CKEOUT2/<br>MAT3[0]/MISO0       |

| 5   | V <sub>SSIO</sub>                               | 6   | P3[23]/D23/<br>CAP0[0]/PCAP1[0]        | 7   | P0[14]/USB_HSTEN2/<br>USB_CONNECT2/<br>SSEL1 | 8   | P2[20]/DYCS0                           |

| 9   | P1[24]/USB_RX_DM1/<br>PWM1[5]/MOSI0             | 10  | P1[25]/USB_LS1/<br>USB_HSTEN1/MAT1[1]  | 11  | P4[2]/A2                                     | 12  | P1[27]/USB_INT1/<br>USB_OVRCR1/CAP0[1] |

| 13  | P1[28]/USB_SCL1/<br>PCAP1[0]/MAT0[0]            | 14  | P0[1]/TD1/RXD3/SCL1                    | 15  | P0[10]/TXD2/SDA2/<br>MAT3[0]                 | 16  | P2[13]/EINT3/<br>MCIDAT3/I2STX_SDA     |

| 17  | P2[11]/ <del>EINT1</del> /<br>MCIDAT1/I2STX_CLK |     | -                                      |     | -                                            |     | -                                      |

| Row | ı U                                             |     |                                        |     |                                              |     |                                        |

| 1   | USB_D-2                                         | 2   | P3[25]/D25/<br>MAT0[0]/PWM1[2]         | 3   | P2[18]/CLKOUT0                               | 4   | P0[29]/USB_D+1                         |

| 5   | P2[23]/DYCS3/<br>CAP3[1]/SSEL0                  | 6   | P1[19]/USB_TX_E1/<br>USB_PPWR1/CAP1[1] | 7   | P1[20]/USB_TX_DP1/<br>PWM1[2]/SCK0           | 8   | P1[22]/USB_RCV1/<br>USB_PWRD1/MAT1[0]  |

| 9   | P4[0]/A0                                        | 10  | P4[1]/A1                               | 11  | P2[21]/DYCS1                                 | 12  | P2[22]/DYCS2/<br>CAP3[0]/SCK0          |

| 13  | V <sub>DD(3V3)</sub>                            | 14  | P1[29]/USB_SDA1/<br>PCAP1[1]/MAT0[1]   | 15  | P0[0]/RD1/TXD3/SDA1                          | 16  | P4[3]/A3                               |

| 17  | P4[16]/A16                                      |     | -                                      |     | -                                            |     | -                                      |

#### Table 3. Pin allocation table ...continued

## 6.2 Pin description

#### Table 4. **Pin description** Ball Symbol Pin Туре Description P0[0] to P0[31] I/O Port 0: Port 0 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 0 pins depends upon the pin function selected via the Pin Connect block. P0[0]/RD1/ 94[1] U15<sup>[1]</sup> I/O P0[0] — General purpose digital input/output pin. TXD3/SDA1 L RD1 — CAN1 receiver input (LPC2460 only). 0 TXD3 — Transmitter output for UART3. I/O **SDA1** — I<sup>2</sup>C1 data input/output (this is not an open-drain pin). 96<sup>[1]</sup> T14<sup>[1]</sup> P0[1]/TD1/RXD3/ I/O P0[1] — General purpose digital input/output pin. SCL1 0 TD1 — CAN1 transmitter output (LPC2460 only). RXD3 — Receiver input for UART3. Т SCL1 — I<sup>2</sup>C1 clock input/output (this is not an open-drain pin). I/O P0[2]/TXD0 202[1] C4<sup>[1]</sup> I/O P0[2] — General purpose digital input/output pin. 0 **TXD0** — Transmitter output for UART0.

Product data sheet

### Flashless 16-bit/32-bit microcontroller

| Table 4.                                                                                                                                                                                                                                                                                      | Pin desc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | riptionco                                   | ontinued                                       |                                                                      |                                                                                                                                                                                            |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin                                         | Ball                                           | Туре                                                                 | Description                                                                                                                                                                                |  |  |

| P1[26]/                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82 <u>[1]</u>                               | R10 <sup>[1]</sup>                             | I/O                                                                  | P1[26] — General purpose digital input/output pin.                                                                                                                                         |  |  |

| P1[26]/<br>USB_SSPND1/<br>PWM1[6]/<br>CAP0[0]<br>P1[27]/<br>USB_INT1/<br>USB_OVRCR1/<br>CAP0[1]<br>P1[28]/<br>USB_SCL1/<br>PCAP1[0]/<br>MAT0[0]<br>P1[29]/<br>USB_SDA1/<br>PCAP1[1]/<br>MAT0[1]                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             | 0                                              | <b>USB_SSPND1</b> — USB port 1 Bus Suspend status (OTG transceiver). |                                                                                                                                                                                            |  |  |

| P1[26]/<br>USB_SSPND1/<br>PWM1[6]/<br>CAP0[0]<br>P1[27]/<br>USB_INT1/<br>USB_OVRCR1/<br>CAP0[1]<br>P1[28]/<br>USB_SCL1/<br>PCAP1[0]/<br>MAT0[0]<br>P1[29]/<br>USB_SDA1/<br>PCAP1[1]/<br>MAT0[1]<br>P1[30]/<br>USB_PWRD2/<br>V <sub>BUS</sub> /AD0[4]<br>P1[31]/<br>USB_OVRCR2/<br>SCK1/AD0[5] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | 0                                                                    | <b>PWM1[6]</b> — Pulse Width Modulator 1, channel 6 output.                                                                                                                                |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                |                                                                      | CAP0[0] — Capture input for Timer 0, channel 0.                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                               | <del>.</del> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88 <u>[1]</u>                               | T12 <sup>[1]</sup>                             | I/O                                                                  | P1[27] — General purpose digital input/output pin.                                                                                                                                         |  |  |

| USB_OVF                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I                                                                    | <b>USB_INT1</b> — USB port 1 OTG transceiver interrupt (OTG transceiver).                                                                                                                  |  |  |

| 0/ 1 0[1]                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I                                                                    | USB_OVRCR1 — USB port 1 Over-Current status.                                                                                                                                               |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | Ι                                                                    | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90 <u>[1]</u>                               | T13 <u><sup>[1]</sup></u>                      | I/O                                                                  | P1[28] — General purpose digital input/output pin.                                                                                                                                         |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I/O                                                                  | USB_SCL1 — USB port 1 I <sup>2</sup> C-bus serial clock (OTG transceiver).                                                                                                                 |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I                                                                    | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | 0                                                                    | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                                                             |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92 <u>[1]</u>                               | U14 <u><sup>[1]</sup></u>                      | I/O                                                                  | P1[29] — General purpose digital input/output pin.                                                                                                                                         |  |  |

| —                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I/O                                                                  | USB_SDA1 — USB port 1 I <sup>2</sup> C-bus serial data (OTG transceiver).                                                                                                                  |  |  |

| MATO[1]                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I                                                                    | PCAP1[1] — Capture input for PWM1, channel 1.                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                                                               | O       MAT0[1] — Match output for Timer 0, channel         1[30]/       42 <sup>[2]</sup> P2 <sup>[2]</sup> I/O       P1[30] — General purpose digital input/output         SB_PWRD2/       I       USB_PWRD2 — Power Status for USB port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             | MAT0[1] — Match output for Timer 0, channel 0. |                                                                      |                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42 <sup>[2]</sup>                           | P2 <sup>[2]</sup>                              | I/O                                                                  | P1[30] — General purpose digital input/output pin.                                                                                                                                         |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             | I                                              | USB_PWRD2 — Power Status for USB port 2.                             |                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             | I                                              | V <sub>BUS</sub> — Monitors the presence of USB bus power.           |                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                |                                                                      | Note: This signal must be HIGH for USB reset to occur.                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | Ι                                                                    | AD0[4] — A/D converter 0, input 4.                                                                                                                                                         |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40 <u>[2]</u>                               | P1 <sup>[2]</sup>                              | I/O                                                                  | P1[31] — General purpose digital input/output pin.                                                                                                                                         |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | Ι                                                                    | <b>USB_OVRCR2</b> — Over-Current status for USB port 2.                                                                                                                                    |  |  |

| CONTINUES                                                                                                                                                                                                                                                                                     | 5[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                                                | I/O                                                                  | SCK1 — Serial Clock for SSP1.                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | Ι                                                                    | AD0[5] — A/D converter 0, input 5.                                                                                                                                                         |  |  |

| P2[0] to P                                                                                                                                                                                                                                                                                    | 2[31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |                                                | I/O                                                                  | <b>Port 2:</b> Port 2 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 2 pins depends upon the pin function selected via the Pin Connect block. |  |  |

|                                                                                                                                                                                                                                                                                               | M1[1]/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 154 <u>[1]</u>                              | B17 <u><sup>[1]</sup></u>                      | I/O                                                                  | P2[0] — General purpose digital input/output pin.                                                                                                                                          |  |  |

| TXD1/                                                                                                                                                                                                                                                                                         | к                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |                                                | 0                                                                    | <b>PWM1[1]</b> — Pulse Width Modulator 1, channel 1 output.                                                                                                                                |  |  |

| INAOLOL                                                                                                                                                                                                                                                                                       | OMAT0[0] — Match output for Ti29/<br>B_SDA1/<br>AP1[1]/<br>T0[1]92[1]U14[1]I/OP1[29] — General purpose digI/OUSB_SDA1 — USB port 1 I2C.<br>I<br>PCAP1[1] — Capture input for<br>OI<br>MAT0[1] — Capture input for<br>TO30]/<br>B_PWRD2/<br>Is/AD0[4]42[2]P2[2]I/OP1[30] — General purpose digI<br>USB_PWRD2 /<br>Is/AD0[4]42[2]P2[2]I/OP1[30] — General purpose digI<br>USB_PWRD2 /<br>Is/AD0[4]40[2]P1[2]I/OP1[31] — General purpose digI<br>B_OVRCR2/<br>K1/AD0[5]40[2]P1[2]I/OP1[31] — General purpose digI<br>USB_OVRCR2<br>K1/AD0[5]40[2]P1[2]I/OP1[31] — General purpose digI<br>O<br>D/VMN1[1]/40[2]P1[2]I/OP1[31] — General purpose digI<br>D/<br>ACECLK154[1]B17[1]I/OPort 2: Port 2 is a 32-bit I/O po<br>each bit. The operation of port<br>selected via the Pin Connect bi<br>O0/PWM1[1]/<br>D1/<br>ACECLK154[1]B17[1]I/OP2[0] — General purpose digit<br>O0/PWM1[2]/<br>D1/<br>TSTATO152[1]E14[1]I/OP2[1] — General purpose digit<br>O0/PWM1[2]/<br>D1/<br>TSTATO152[1]E14[1]I/OP2[1] — General purpose digit<br>O0PWM1[2] — Nese Width Modu<br>I<br>RXD1 — Receiver input for UA<br>OPWM1[2] — Pulse Width Modu<br>I<br>I<br>RXD1 — Receiver input for UA<br>O | <b>TXD1</b> — Transmitter output for UART1. |                                                |                                                                      |                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | 0                                                                    | TRACECLK — Trace Clock.                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                               | M1[2]/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 152 <u>[1]</u>                              | E14 <sup>[1]</sup>                             | I/O                                                                  | P2[1] — General purpose digital input/output pin.                                                                                                                                          |  |  |

| RXD1/                                                                                                                                                                                                                                                                                         | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |                                                | 0                                                                    | <b>PWM1[2]</b> — Pulse Width Modulator 1, channel 2 output.                                                                                                                                |  |  |

| PIPESTAT0                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | I                                                                    | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |                                                | 0                                                                    | PIPESTAT0 — Pipeline Status, bit 0.                                                                                                                                                        |  |  |

| P2[2]/PW                                                                                                                                                                                                                                                                                      | V1[3]/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 150 <u>[1]</u>                              | D15 <sup>[1]</sup>                             | I/O                                                                  | P2[2] — General purpose digital input/output pin.                                                                                                                                          |  |  |

| CTS1/<br>PIPESTAT                                                                                                                                                                                                                                                                             | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |                                                | 0                                                                    | <b>PWM1[3]</b> — Pulse Width Modulator 1, channel 3 output.                                                                                                                                |  |  |

| TILESTAI                                                                                                                                                                                                                                                                                      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |                                                | I                                                                    | CTS1 — Clear to Send input for UART1.                                                                                                                                                      |  |  |