Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1902-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| AddNameBit 6Bit 6Bit 4Bit 3Bit 2Bit 1Bit 0PQR, BORPIDChLATAPORTA DataLatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 10Ch       LATA       PORTA Data Latch       XXXX XXXX       uu       uu         10Dh       LATB       PORTB Data Latch       XXXX XXXX       uu         10Eh       LATC       PORTC Data Latch       XXXX XXXX       uu         10Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Value on all<br>other<br>Resets |

| 10Db       LATB       PORTB Data Latch       xxxx xxxx       uu       uu       uu       uu         10Fh       -       QRTC Data Latch       xxxx xxxx       uu       uu <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |

| 10En       LATC       PORTC Data Latch       xxxx xxxx       uu       uu         10Fn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | uuuu uuuu                       |

| 10Fh       -       Unimplemented       -       -       -       BORRD       10        10         116h       BORCON       SBOREN       BORFS       -       -       -       ADFVR1       ADFVR0       0q00000       0q         117h       FVRCON       FVREN       FVREN       TSEN       TSENG       -       -       ADFVR1       ADFVR0       0q00000       0q         118h       -       Unimplemente       FVREN       FVREN       TSEN       TSENG       -       -       ADFVR1       ADFVR0       0q00000       0q         118h       -       Unimplemente/       -       ANSA5       -       ANSA3       ANSA2       ANSA1       ANSA0       -1-1       111       -         18Dh       ANSELB       -       -       ANSB5       ANSB4       ANSB3       ANSB2       ANSB1       ANSB0      11       111        100       1011       111        -       1111         1000       000       101       1111        1111         1000       000       101       1111        11111        11111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | uuuu uuuu                       |

| tot       nom       n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | uuuu uuuu                       |

| 117h       FVRCON       FVREN       FVRENP       TSEN       TSENG       -       -       ADFVR1       ADFVR0       0q00       0q0       0q00       -       0q00       0q000       0q00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                               |

| 18h to to to the tot to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | auu                             |

| to<br>11Fh       -       Unimplemented       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       ANSA3       ANSA2       ANSA1       ANSA0       -       -       1       -       -       -       1       1       -       -       1       1       -       -       1       1       -       -       1       1       -       1       1       -       1       1       -       1       1       -       1       1       1       -       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <th1< th="">       1       1</th1<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0q0000                          |

| 18ch       ANSELA       —       —       ANSA3       ANSA2       ANSA1       ANSA0      1-1111          18bh       ANSELB       —       —       ANSB5       ANSB4       ANSB3       ANSB2       ANSB1       ANS00      1-1111          18bh       —       Unimplemented       —       —       ANSB5       ANSB1       ANSB2       ANSB1       ANS00      1-1111          18bh       —       Unimplemented       —       Unimplemented       —       —       —       —       —       —       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                               |

| 18Dh       ANSELB       —       ANSB5       ANSB5       ANSB2       ANSB1       ANSB0      11       111          18Eh       —       Unimplem=t       Unimplemet       Implemet       Implem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 18Eh        Unimplement           1         18Fh        Unimplement          1         190h        Unimplement         1       0       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00 <td>11 1111</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 1111                         |

| 18Fh        Unimplement       Image: Imag | 11 1111                         |

| 190h        Unimplement       Implement       Implement <thi< td=""><td>_</td></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                               |

| 191h       PMADRL       Program Memory Address Register Low Byte       0000000       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                               |

| 192h       PMADRH       -(2)       Program Memory Red Data Register Low Byte       1000 000       101         193h       PMDATL       Program Memory Read Data Register Low Byte       xxxx xxxx       uu         194h       PMDATH       -       -       Program Memory Read Data Register Low Byte       xxxx xxxx       uu         194h       PMDATH       -       -       Program Memory Read Data Register High Byte      xx xxxx          195h       PMCON1       -       -       Program Memory Read Data Register High Byte      xx xxxx          195h       PMCON2       Program Memory Control register 2       WRERR       WREN       WR       RD       1000 000       10         196h       PMCON2       Program Memory Control register 2        0000 000       00       10         197h       -       -       0       Unimplemented        -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                               |

| 1011       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000 0000                       |

| 194h       PMDATH       —       —       Program Memory Read Data Register High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1000 0000                       |

| 195h         PMCON1        (2)         CFGS         LWLO         FREE         WRERR         WREN         WR         RD         1000 x000         10           196h         PMCON2         Program Memory Control Register 2         0000 0000         00           197h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | uuuu uuuu                       |

| NNCONT         NNCONT<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | uu uuuu                         |

| 197h<br>to<br>19Fh       -       Unimplemented       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - </td <td>1000 q000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1000 q000                       |

| to<br>19Fh-UnimplementedBancton20Ch-UnimplementedVPUB3VPUB3VPUB1VPUB011111120Ch-OUnimplementedVPUB3VPUB2VPUB1VPUB011111120Ch-OUnimplemented1020Fh-OUnimplemented1020Fh-O-O-O <t< td=""><td>0000 0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000 0000                       |

| 20Ch        Unimplemeter            11       111       11         20Dh       WPUB       WPUB7       WPUB6       WPUB5       WPUB3       WPUB2       WPUB1       WPUB0       1111       11         20Eh        Miniplemeter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                               |

| 20Dh         WPUB         WPUB7         WPUB6         WPUB5         WPUB3         WPUB2         WPUB1         WPUB0         111         11           20Dh         —         Unimplemented         —         —         —         —         —         —         —         —         —         —         —         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

| 20Eh        Unimplemented </td <td>—</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                               |

| 20Fh        Unimplementation                                                                                                                   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1111 1111                       |

| 210h       WPUE       -       -       WPUE3       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                               |

| 211h     -     Unimplemented     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                               |

| to 21Fh Unimplemented —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                               |

| Bank E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| Bank 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 28Ch — Unimplemented —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                               |

| 29Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

| Bank 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 30Ch — Unimplemented —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                               |

| 31Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

TABLE 3-5: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Shaded locations are unimplemented, read as '0'. Note 1: These registers can be addressed from any bank.

**2:** Unimplemented, read as '1'.

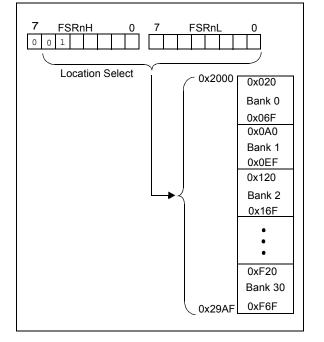

### 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

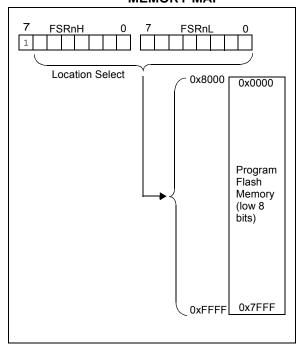

### 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

### 5.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          |     |            |            |            |            | bit 0      |

| Legend:          |                                                                  |                                                |                                                                                                       |  |  |  |  |

|------------------|------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| HC = Bit is cl   | eared by hard                                                    | ware                                           | HS = Bit is set by hardware                                                                           |  |  |  |  |

| R = Readable     | e bit                                                            | W = Writable bit                               | U = Unimplemented bit, read as '0'                                                                    |  |  |  |  |

| u = Bit is unc   | hanged                                                           | x = Bit is unknown                             | -m/n = Value at POR and BOR/Value at all other Resets                                                 |  |  |  |  |

| '1' = Bit is set | t                                                                | '0' = Bit is cleared                           | q = Value depends on condition                                                                        |  |  |  |  |

| bit 7            | STKOVE                                                           | Staak Ovorflow Elag bit                        |                                                                                                       |  |  |  |  |

|                  |                                                                  | Stack Overflow Flag bit<br>k Overflow occurred |                                                                                                       |  |  |  |  |

|                  | d or set to '0' by firmware                                      |                                                |                                                                                                       |  |  |  |  |

| bit 6            |                                                                  |                                                |                                                                                                       |  |  |  |  |

|                  |                                                                  | k Underflow occurred                           |                                                                                                       |  |  |  |  |

|                  | 0 = A Stack Underflow has not occurred or set to '0' by firmware |                                                |                                                                                                       |  |  |  |  |

| bit 5            | Unimplem                                                         | Unimplemented: Read as '0'                     |                                                                                                       |  |  |  |  |

| bit 4            | RWDT: Watchdog Timer Reset Flag bit                              |                                                |                                                                                                       |  |  |  |  |

|                  |                                                                  |                                                | occurred or set to '1' by firmware                                                                    |  |  |  |  |

|                  |                                                                  | -                                              | rred (set to '0' in hardware when a Watchdog Timer Reset)                                             |  |  |  |  |

| bit 3            |                                                                  | ICLR Reset Flag bit                            |                                                                                                       |  |  |  |  |

|                  |                                                                  | R Reset has not occurred or                    |                                                                                                       |  |  |  |  |

| 1.11.0           |                                                                  |                                                | o '0' in hardware when a MCLR Reset occurs)                                                           |  |  |  |  |

| bit 2            |                                                                  | Instruction Flag bit                           | average of a set to (1) by firming                                                                    |  |  |  |  |

|                  |                                                                  |                                                | executed or set to '1' by firmware<br>uted (set to '0' in hardware upon executing a RESET instruction |  |  |  |  |

| bit 1            |                                                                  | er-on Reset Status bit                         |                                                                                                       |  |  |  |  |