Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1902-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device      | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash Memory<br>Address Range <sup>(1)</sup> |

|-------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC16LF1902 | 2,048                           | 07FFh                          | 0780h-07FFh                                                 |

| PIC16LF1903 | 4,096                           | 0FFFh                          | 0F80h-0FFFh                                                 |

**Note 1:** High-endurance Flash applies to low byte of each address in the range.

#### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16LF1902/3 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1, and 3-2).

| TABL | E 3-3: Pl                     | C16L | F1902/3 ME                    | MORY | ( MAP (CON                    | TINU | ED)                           |      |                               |      |                               |      |                               |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

|      | BANK 8                        |      | BANK 9                        |      | BANK 10                       |      | BANK 11                       |      | BANK 12                       |      | BANK 13                       |      | BANK 14                       |

| 400h | Core Registers<br>(Table 3-2) | 480h | Core Registers<br>(Table 3-2) | 500h | Core Registers<br>(Table 3-2) | 580h | Core Registers<br>(Table 3-2) | 600h | Core Registers<br>(Table 3-2) | 680h | Core Registers<br>(Table 3-2) | 700h | Core Registers<br>(Table 3-2) |

| 40Bh |                               | 48Bh |                               | 50Bh |                               | 58Bh |                               | 60Bh |                               | 68Bh |                               | 70Bh |                               |

| 40Ch | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  | 68Ch | Unimplemented<br>Read as '0'  | 70Ch | Unimplemented<br>Read as '0'  |

| 46Fh |                               | 4EFh |                               | 56Fh |                               | 5EFh |                               | 66Fh |                               | 6EFh |                               | 76Fh |                               |

| 470h | Common RAM                    | 4F0h | Common RAM                    | 570h | Common RAM                    | 5F0h | Common RAM                    | 670h | Common RAM                    | 6F0h | Common RAM                    | 770h | Common RAM                    |

5FFh

(Accesses 70h – 7Fh)

(Accesses 70h – 7Fh)

(Accesses 70h – 7Fh)

57Fh

|              | BANK 16                                   |              | BANK 17                               |              | BANK 18                               |              | BANK 19                               |              | BANK 20                               |              | BANK 21                               |              | BANK 22                               |              | BANK 23                               |

|--------------|-------------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| 800h         | Core Registers<br>(Table 3-2)Table<br>3-2 | 880h         | Core Registers<br>(Table 3-2)         | 900h         | Core Registers<br>(Table 3-2)         | 980h         | Core Registers<br>(Table 3-2)         | A00h         | Core Registers<br>(Table 3-2)         | A80h         | Core Registers<br>(Table 3-2)         | B00h         | Core Registers<br>(Table 3-2)         | B80h         | Core Registers<br>(Table 3-2)         |

| 80Bh         | 02                                        | 88Bh         |                                       | 90Bh         |                                       | 98Bh         |                                       | A0Bh         |                                       | A8Bh         |                                       | B0Bh         |                                       | B8Bh         |                                       |

| 80Ch         |                                           | 88Ch         |                                       | 90Ch         |                                       | 98Ch         |                                       | A0Ch         |                                       | A8Ch         |                                       | B0Ch         |                                       | B8Ch         |                                       |

|              | Unimplemented<br>Read as '0'              |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |

| 86Fh         |                                           | 8EFh         |                                       | 96Fh         |                                       | 9EFh         |                                       | A6Fh         |                                       | AEFh         |                                       | B6Fh         |                                       | BEFh         |                                       |

| 870h<br>87Fh | Common RAM<br>(Accesses<br>70h – 7Fh)     | 8F0h<br>8FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 970h<br>97Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 9F0h<br>9FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | A70h<br>A7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | AF0h<br>AFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | B70h<br>B7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | BF0h<br>BFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

67Fh

(Accesses 70h – 7Fh)

6FFh

(Accesses 70h – 7Fh)

77Fh

(Accesses 70h – 7Fh)

PIC16LF1902/3

|      | BANK 24                               |      | BANK 25                               |      | BANK 26                               |      | BANK 27                               |      | BANK 28                               |      | BANK 29                               |      | BANK 30                               |

|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|

| C00h | Core Registers<br>(Table 3-2)         | C80h | Core Registers<br>(Table 3-2)         | D00h | Core Registers<br>(Table 3-2)         | D80h | Core Registers<br>(Table 3-2)         | E00h | Core Registers<br>(Table 3-2)         | E80h | Core Registers<br>(Table 3-2)         | F00h | Core Registers<br>(Table 3-2)         |

| C0Bh |                                       | C8Bh |                                       | D0Bh |                                       | D8Bh |                                       | E0Bh |                                       | E8Bh |                                       | F0Bh |                                       |

| C0Ch |                                       | C8Ch |                                       | D0Ch |                                       | D8Ch |                                       | E0Ch |                                       | E8Ch |                                       | F0Ch |                                       |

|      | Unimplemented<br>Read as '0'          |

| C6Fh |                                       | CEFh |                                       | D6Fh |                                       | DEFh |                                       | E6Fh |                                       | EEFh |                                       | F6Fh |                                       |

| C70h | Common RAM<br>(Accesses<br>70h – 7Fh) | CF0h | Common RAM<br>(Accesses<br>70h – 7Fh) | D70h | Common RAM<br>(Accesses<br>70h – 7Fh) | DF0h | Common RAM<br>(Accesses<br>70h – 7Fh) | E70h | Common RAM<br>(Accesses<br>70h – 7Fh) | EF0h | Common RAM<br>(Accesses<br>70h – 7Fh) | F70h | Common RAM<br>(Accesses<br>70h – 7Fh) |

| C7Fh |                                       | CFFh |                                       | D7Fh |                                       | DFFh |                                       | E7Fh |                                       | EFFh |                                       | F7Fh |                                       |

= Unimplemented data memory locations, read as '0' Legend:

(Accesses 70h – 7Fh)

47Fh

4FFh

| ТАВ                                            |                |                                                                     |                                                                    |             |               |              |                |                |               |                      |                                 |

|------------------------------------------------|----------------|---------------------------------------------------------------------|--------------------------------------------------------------------|-------------|---------------|--------------|----------------|----------------|---------------|----------------------|---------------------------------|

| Addr                                           | Name           | Bit 7                                                               | Bit 6                                                              | Bit 5       | Bit 4         | Bit 3        | Bit 2          | Bit 1          | Bit 0         | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank                                           | 15 (Continued) |                                                                     |                                                                    |             |               |              |                |                |               |                      |                                 |

| 7ABh                                           | _              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | —                               |

| 7ACh                                           | LCDDATA12      | —                                                                   | —                                                                  | _           | -             | —            | SEG26<br>COM0  | SEG25<br>COM0  | SEG24<br>COM0 | xxx                  | uuu                             |

| 7ADh                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | —                               |

| 7AEh                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | —                               |

| 7AFh                                           | LCDDATA15      | —                                                                   |                                                                    |             | —             | _            | SEG26<br>COM1  | SEG25<br>COM1  | SEG24<br>COM1 | xxx                  | uuu                             |

| 7B0h                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | —                               |

| 7B1h                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | _                    | _                               |

| 7B2h                                           | LCDDATA18      | _                                                                   | _                                                                  |             | —             | _            | SEG26<br>COM2  | SEG25<br>COM2  | SEG24<br>COM2 | xxx                  | uuu                             |

| 7B3h                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | _                               |

| 7B4h                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | _                               |

| 7B5h                                           | LCDDATA21      | _                                                                   | _                                                                  |             | —             | _            | SEG26<br>COM3  | SEG25<br>COM3  | SEG24<br>COM3 | xxx                  | uuu                             |

| 7B6h                                           | —              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | —                               |

| 7EFh                                           |                |                                                                     |                                                                    |             |               |              |                |                |               |                      |                                 |

| Ban                                            | k 16-30        |                                                                     |                                                                    |             |               |              |                |                |               |                      |                                 |

| x0Ch<br>or<br>x8Ch<br>to<br>x1Fh<br>or<br>x9Fh | _              | Unimpleme                                                           | Jnimplemented                                                      |             |               |              |                |                |               |                      | _                               |

|                                                | k 31           |                                                                     |                                                                    |             |               |              |                |                |               |                      |                                 |

| F8Ch                                           | _              | Unimpleme                                                           | nted                                                               |             |               |              |                |                |               | —                    | —                               |

| FE3h                                           |                |                                                                     |                                                                    |             |               |              |                | 1              | -             |                      |                                 |

| FE4h                                           | STATUS_SHAD    | —                                                                   | —                                                                  | —           | -             | —            | Z_SHAD         | DC_SHAD        | C_SHAD        | xxx                  | uuu                             |

| FE5h                                           | WREG_SHAD      | Working Re                                                          | gister Norma                                                       | I (Non-ICD) | 1             |              |                |                |               | XXXX XXXX            | uuuu uuuu                       |

| FE6h                                           | BSR_SHAD       | _                                                                   |                                                                    | _           | Bank Select I |              | · · ·          |                |               | x xxxx               | u uuuu                          |

| FE7h                                           | PCLATH_SHAD    | —                                                                   | Program Counter Latch High Register Normal (Non-ICD) Shadow        |             |               |              |                |                |               | -xxx xxxx            | uuuu uuuu                       |

| FE8h                                           | FSR0L_SHAD     |                                                                     | Indirect Data Memory Address 0 Low Pointer Normal (Non-ICD) Shadow |             |               |              |                |                |               | XXXX XXXX            | uuuu uuuu                       |

| FE9h                                           | FSR0H_SHAD     |                                                                     | ndirect Data Memory Address 0 High Pointer Normal (Non-ICD) Shadow |             |               |              |                |                |               |                      | uuuu uuuu                       |

| FEAh                                           | FSR1L_SHAD     |                                                                     | Indirect Data Memory Address 1 Low Pointer Normal (Non-ICD) Shadow |             |               |              |                |                |               |                      | uuuu uuuu                       |

| FEBh                                           | FSR1H_SHAD     | Indirect Data Memory Address 1 High Pointer Normal (Non-ICD) Shadow |                                                                    |             |               |              |                |                |               | XXXX XXXX            | uuuu uuuu                       |

| FECh                                           | -              | Unimpleme                                                           | Unimplemented —                                                    |             |               |              |                |                |               | —                    | —                               |

| FEDh                                           | 0              | _                                                                   | Current Stack Pointer 1 1111                                       |             |               |              |                |                |               |                      | 1 1111                          |

| FEEh                                           | TOSL           | Top of Stack                                                        | Top of Stack Low byte xxxx xxxx u                                  |             |               |              |                |                |               |                      |                                 |

| FEFh                                           | TOSH           | —                                                                   | Top of Stack                                                       |             |               |              |                |                |               | -xxx xxxx            | -uuu uuuu                       |

| Legen                                          | d: x = unknov  | vn, u = uncha                                                       | anged, q = va                                                      | lue depends | on condition, | - = unimplem | nented, read a | as '0', r = re | served.       |                      |                                 |

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-5:**

Legend: Note

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

These registers can be addressed from any bank.

1: 2: Unimplemented, read as '1'.

| GURE 6-4:                | INTERNAL OSCILLATOR SWITCH TIMING             |

|--------------------------|-----------------------------------------------|

|                          |                                               |

| HENGORC                  | LFINTOSC (WOT disabled)                       |

| HFINTOSC                 | Ovjetsky Colleg <sup>10</sup> - 2 cprile Sync |

| LFINTOSC                 |                                               |

| IRCF <3:0>               | $\neq 0$ $= 0$                                |

| System Clock             |                                               |

|                          | LENETOSO (WOY enabled)                        |

| HFINTOSC                 |                                               |

|                          |                                               |

| LFINTOSC                 |                                               |

| IRCF <3:0>               | $\neq 0$ $X = 0$                              |

| System Clock             |                                               |

| (39870SQ)                |                                               |

|                          | LFUECCE and an analysis                       |

| 65969030                 |                                               |

| MERICISC.                |                                               |

| \$\$C\$ <\$C\$           |                                               |

| System Circle            |                                               |

| <b>Nexte 1</b> 2 - See 3 | anaamaanaamaanaamaanaamaanaanaanaanaanaa      |

#### TABLE 6-1: OSCILLATOR SWITCHING DELAYS

| Switch From      | Switch To            | Oscillator Delay                 |

|------------------|----------------------|----------------------------------|

|                  | LFINTOSC             | 1 cycle of each clock source     |

|                  | HFINTOSC             | 2 μs (approx.)                   |

| Any clock source | ECH, ECM, ECL        | 2 cycles                         |

|                  | Secondary Oscillator | 1024 Secondary Oscillator Cycles |

### 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Word 1

- · Secondary oscillator 32 kHz crystal

- Internal Oscillator Block (INTOSC)

#### 6.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<1:0> bits in the Configuration Word 1.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-2.

#### 6.3.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<1:0> bits in the Configuration Word 1, or from the internal clock source.

#### 6.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSI and T1CKI/T1OSO device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 17.0 "Timer1 Module with Gate Control**" for more information about the Timer1 peripheral.

#### 6.3.4 SECONDARY OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

### 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 and PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See Section 7.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

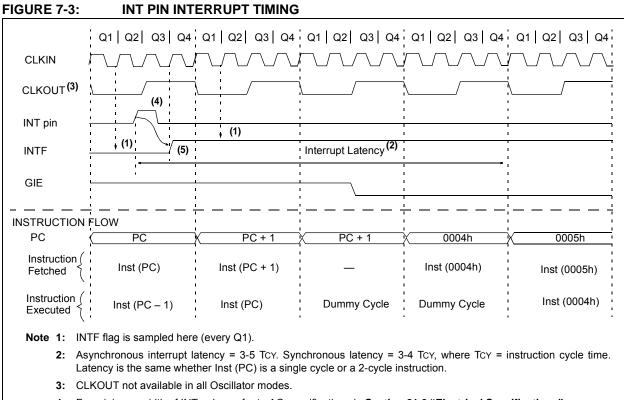

#### 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7.3 for more details.

4: For minimum width of INT pulse, refer to AC specifications in Section 21.0 "Electrical Specifications".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

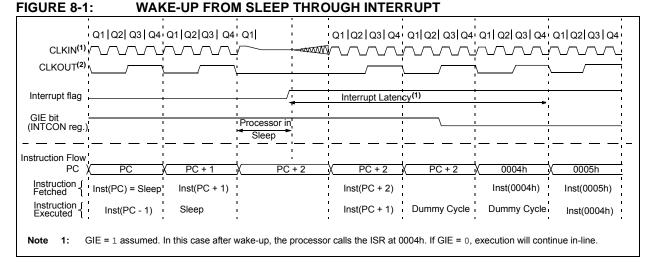

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

## TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|--------|------------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE   | IOCIE      | TMR0IF | INTF   | IOCIF  | 60                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1 | IOCBF0 | 101                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1 | IOCBN0 | 101                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1 | IOCBP0 | 101                 |

| PIE1   | TMR1GIE | ADIE   | _      | —      | _          | —      | _      | TMR1IE | 61                  |

| PIE2   | —       | _      | _      | —      | _          | LCDIE  | _      | —      | 62                  |

| PIR1   | TMR1GIF | ADIF   | _      | —      | _          | —      | _      | TMR1IF | 63                  |

| PIR2   | —       | _      | _      | —      | _          | LCDIF  | _      | —      | 64                  |

| STATUS | _       | _      | _      | TO     | PD         | Z      | DC     | С      | 16                  |

| WDTCON | _       |        |        | ١      | NDTPS<4:0> | >      |        | SWDTEN | 70                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

#### REGISTER 11-1: PORTA: PORTA REGISTER

| R/W-x/x          | R/W-x/x | R/W-x/x          | R/W-x/x | R-x/x          | R/W-x/x            | R/W-x/x           | R/W-x/x   |

|------------------|---------|------------------|---------|----------------|--------------------|-------------------|-----------|

| RA7              | RA6     | RA5              | RA4     | RA3            | RA2                | RA1               | RA0       |

| bit 7            |         |                  |         |                |                    |                   | bit C     |

|                  |         |                  |         |                |                    |                   |           |

| Legend:          |         |                  |         |                |                    |                   |           |

| R = Readable I   | bit     | W = Writable b   | oit     | U = Unimplem   | nented bit, read a | is '0'            |           |

|                  |         | x = Bit is unkno |         | -n/n = Value a | t POR and BOR      | Value at all oth  | _ /       |

| u = Bit is uncha | anged   | X - DILIS UNKIN  | JWII    |                |                    | value at all othe | er Resets |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|---------|--------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3 | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |        |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | <b>TRISA&lt;7:4&gt;:</b> PORTA Tri-State Control bits<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>TRISA3:</b> RA3 Port Tri-State Control bit<br>This bit is always '1' as RA3 is an input only                                                     |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bits<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

### REGISTER 11-3: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

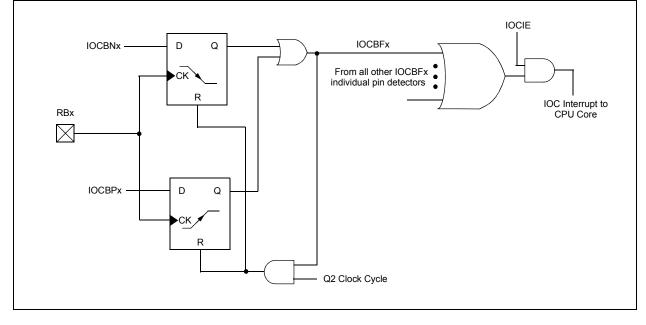

### 12.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-on-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin, or combination of PORTB pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 12-1 is a block diagram of the IOC module.

#### 12.1 Enabling the Module

To allow individual PORTB pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 12.2 Individual Pin Configuration

For each PORTB pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

#### 12.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the interrupt-on-change pins of PORTB. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

#### 12.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 12-1:

```

MOVLW 0xff

XORWF IOCBF, W

ANDWF IOCBF, F

```

#### 12.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

| R/W-0/0         | R/W-0/0                                                                                                                                                                                            | R/W-0/0                                                       | R/W-0/0        | U-0             | U-0             | R/W-0/0         | R/W-0/0          |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------|-----------------|-----------------|------------------|--|

| ADFM            |                                                                                                                                                                                                    | ADCS<2:0>                                                     |                |                 | _               | ADPRE           | ADPREF<1:0>      |  |

| bit 7           |                                                                                                                                                                                                    |                                                               |                |                 |                 |                 | bit 0            |  |

| Legend:         |                                                                                                                                                                                                    |                                                               |                |                 |                 |                 |                  |  |

| R = Readable    | e bit                                                                                                                                                                                              | W = Writable                                                  | bit            | U = Unimple     | mented bit, rea | id as '0'       |                  |  |

| u = Bit is unc  | hanged                                                                                                                                                                                             | x = Bit is unkı                                               | nown           | -               |                 | OR/Value at all | other Resets     |  |

| '1' = Bit is se | t                                                                                                                                                                                                  | '0' = Bit is cle                                              | ared           |                 |                 |                 |                  |  |

| bit 6-4         | loaded.<br>ADCS<2:0><br>000 = Fosc.<br>001 = Fosc.<br>010 = Fosc.                                                                                                                                  | : A/D Conversic<br>/2<br>/8<br>/32<br>clock supplied fi<br>/4 | n Clock Selec  | t bits          |                 | when the conve  | ersion result is |  |

|                 | 110 = Fosc<br>111 = Frc (                                                                                                                                                                          |                                                               | rom a dedicate | ed RC oscillato | r)              |                 |                  |  |

| bit 3-2         | <ul><li>111 = FRC (clock supplied from a dedicated RC oscillator)</li><li>Unimplemented: Read as '0'</li></ul>                                                                                     |                                                               |                |                 |                 |                 |                  |  |

| bit 1-0         | ADPREF<1:0>: A/D Positive Voltage Reference Configuration bits<br>00 = VREF+ is connected to VDD<br>01 = Reserved<br>10 = VREF+ is connected to external VREF+ pin <sup>(1)</sup><br>11 = Reserved |                                                               |                |                 |                 |                 |                  |  |

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 21.0 "Electrical Specifications"** for details.

### 17.10 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), shown in Register 17-2, is used to control Timer1 gate.

| R/W-0/u                                                                                                                                                                                                                                         | R/W-0/u                                                                                                                                                                                                               | R/W-0/u                            | R/W-0/u        | R/W/HC-0/u      | R-x/x            | R/W-0/u | R/W-0/u      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----------------|------------------|---------|--------------|

| TMR1GE                                                                                                                                                                                                                                          | T1GPOL                                                                                                                                                                                                                | T1GTM                              | T1GSPM         | T1GGO/<br>DONE  | T1GVAL           | T1GS    | S<1:0>       |

| bit 7                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                    |                | ·               |                  |         | bit C        |

|                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       |                                    |                |                 |                  |         |              |

| Legend:                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       |                                    |                |                 |                  |         |              |

| R = Readable                                                                                                                                                                                                                                    |                                                                                                                                                                                                                       | W = Writable                       |                |                 | nented bit, read |         |              |

| u = Bit is unch                                                                                                                                                                                                                                 | anged                                                                                                                                                                                                                 | x = Bit is unkr                    |                |                 | at POR and BC    |         | other Resets |

| '1' = Bit is set                                                                                                                                                                                                                                |                                                                                                                                                                                                                       | '0' = Bit is clea                  | ared           | HC = Bit is cle | eared by hardw   | are     |              |

| bit 7 <b>TMR1GE:</b> Timer1 Gate Enable bit<br><u>If TMR1ON = 0</u> :<br>This bit is ignored<br><u>If TMR1ON = 1</u> :<br>1 = Timer1 counting is controlled by the Timer1 gate function<br>0 = Timer1 counts regardless of Timer1 gate function |                                                                                                                                                                                                                       |                                    |                |                 |                  |         |              |

| bit 6                                                                                                                                                                                                                                           | <b>T1GPOL:</b> Timer1 Gate Polarity bit<br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                         |                                    |                |                 |                  |         |              |

| bit 5                                                                                                                                                                                                                                           | <b>T1GTM:</b> Timer1 Gate Toggle Mode bit<br>1 = Timer1 Gate Toggle mode is enabled<br>0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared<br>Timer1 gate flip-flop toggles on every rising edge. |                                    |                |                 |                  |         |              |

| bit 4                                                                                                                                                                                                                                           | T1GSPM: Tin                                                                                                                                                                                                           | ner1 Gate Sing                     | le-Pulse Mode  | bit             |                  |         |              |

|                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       | ate Single-Puls<br>ate Single-Puls |                |                 | ntrolling Timer1 | gate    |              |

| bit 3                                                                                                                                                                                                                                           | T1GGO/DON                                                                                                                                                                                                             | E: Timer1 Gate                     | e Single-Pulse | Acquisition Sta | atus bit         |         |              |

|                                                                                                                                                                                                                                                 | <ul> <li>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> </ul>                                    |                                    |                |                 |                  |         |              |

| bit 2                                                                                                                                                                                                                                           | T1GVAL: Timer1 Gate Current State bit                                                                                                                                                                                 |                                    |                |                 |                  |         |              |

|                                                                                                                                                                                                                                                 | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.<br>Unaffected by Timer1 Gate Enable (TMR1GE).                                                                                   |                                    |                |                 |                  |         |              |

| bit 1-0                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | : Timer1 Gate                      | Source Select  | bits            |                  |         |              |

|                                                                                                                                                                                                                                                 | 00 = Timer1 gate pin<br>01 = Timer0 overflow output<br>10 = Reserved<br>11 = Reserved                                                                                                                                 |                                    |                |                 |                  |         |              |

#### REGISTER 17-2: T1GCON: TIMER1 GATE CONTROL REGISTER

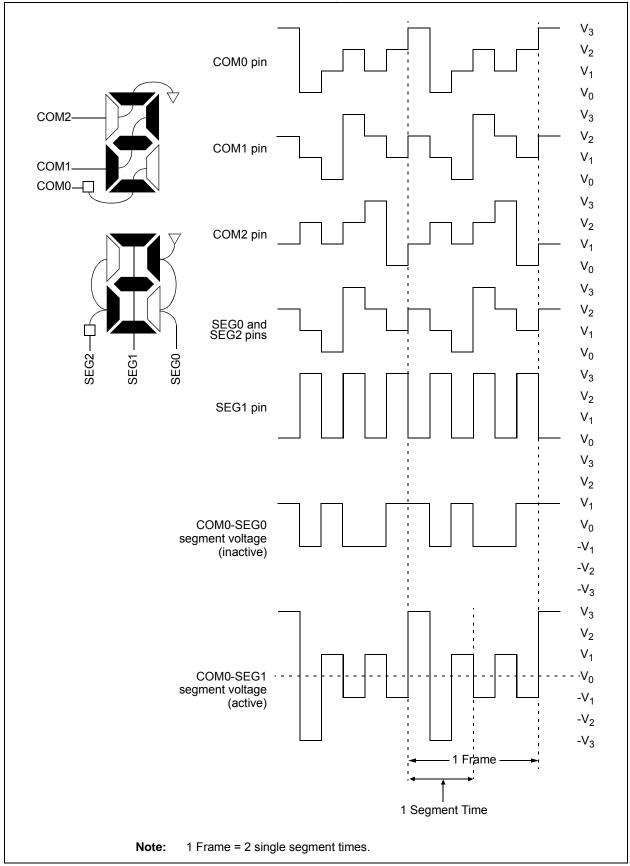

#### TABLE 18-1: LCD SEGMENT AND DATA REGISTERS

|               | # of LCD          | Registers |

|---------------|-------------------|-----------|

| Device        | Segment<br>Enable | Data      |

| PIC16LF1902/3 | 3                 | 12        |

The LCDCON register (Register 18-1) controls the operation of the LCD Driver module. The LCDPS register (Register 18-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSEn registers (Register 18-5) configure the functions of the port pins.

The following LCDSEn registers are available:

- LCDSE0 SE<7:0>

- LCDSE1 SE<15:8>

- LCDSE3 SE<26:24>

Once the module is initialized for the LCD panel, the individual bits of the LCDDATAn registers are cleared/set to represent a clear/dark pixel, respectively:

- LCDDATA0 SEG<7:0>COM0

- LCDDATA1 SEG<15:8>COM0

- LCDDATA3 SEG<7:0>COM1

- LCDDATA4 SEG<15:8>COM1

- LCDDATA6 SEG<7:0>COM2

- LCDDATA7 SEG<15:8>COM2

- LCDDATA9 SEG<7:0>COM3

- LCDDATA10 SEG<15:8>COM3

- LCDDATA12 SEG<26:24>COM0

- LCDDATA15 SEG<26:24>COM1

- LCDDATA18 SEG<26:24>COM2

- LCDDATA21 SEG<26:24>COM3

As an example, LCDDATAn is detailed in Register 18-6.

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

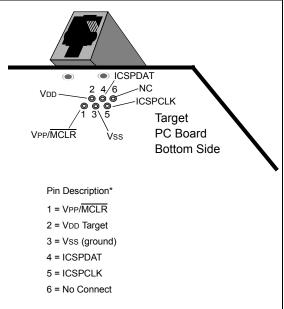

### 19.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more ICSP™ information on refer to the "PIC16F193X/LF193X/PIC16F194X/LF194X/PIC16LF 190X Memory Programming Specification" (DS41397).

#### 19.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 19.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the MCLR Reset function is automatically enabled and cannot be disabled. See **Section 5.3 "Low-Power Brown-out Reset (LPBOR)"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 19.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 19-1.

| Mnemo      | onic, | Description                   | Cvcles        |        | 14-Bit | Opcode | •    | Status   | Notes |

|------------|-------|-------------------------------|---------------|--------|--------|--------|------|----------|-------|

| Opera      | nds   | Description                   |               | MSb    |        |        | LSb  | Affected | Note  |

|            |       | BYTE-ORIENTED FILE            | REGISTER OPE  | RATIC  | NS     |        |      |          |       |

|            | f, d  | Add W and f                   | 1             | 00     | 0111   | dfff   | ffff | C, DC, Z | 2     |

| ADDWFC f   | f, d  | Add with Carry W and f        | 1             | 11     | 1101   | dfff   | ffff | C, DC, Z | 2     |

| ANDWF f    | f, d  | AND W with f                  | 1             | 00     | 0101   | dfff   | ffff | Z        | 2     |

| ASRF f     | f, d  | Arithmetic Right Shift        | 1             | 11     | 0111   | dfff   | ffff | C, Z     | 2     |

| LSLF f     | f, d  | Logical Left Shift            | 1             | 11     | 0101   | dfff   | ffff | C, Z     | 2     |

| LSRF f     | f, d  | Logical Right Shift           | 1             | 11     | 0110   | dfff   | ffff | C, Z     | 2     |

| CLRF f     | F     | Clear f                       | 1             | 00     | 0001   | lfff   | ffff | Z        | 2     |

| CLRW -     | -     | Clear W                       | 1             | 00     | 0001   | 0000   | 00xx | Z        |       |

| COMF f     | f, d  | Complement f                  | 1             | 00     | 1001   | dfff   | ffff | Z        | 2     |

| DECF f     | f, d  | Decrement f                   | 1             | 00     | 0011   | dfff   | ffff | Z        | 2     |

|            | f, d  | Increment f                   | 1             | 00     | 1010   | dfff   | ffff | Z        | 2     |

| IORWF f    | f, d  | Inclusive OR W with f         | 1             | 00     | 0100   | dfff   | ffff | Z        | 2     |

| MOVF f     | f, d  | Move f                        | 1             | 00     | 1000   | dfff   | ffff | Z        | 2     |

| MOVWF f    | F     | Move W to f                   | 1             | 00     | 0000   | lfff   | ffff |          | 2     |

| RLF f      | f, d  | Rotate Left f through Carry   | 1             | 00     | 1101   | dfff   | ffff | С        | 2     |

| RRF f      | f, d  | Rotate Right f through Carry  | 1             | 00     | 1100   | dfff   | ffff | С        | 2     |

| SUBWF f    | f, d  | Subtract W from f             | 1             | 00     | 0010   | dfff   | ffff | C, DC, Z | 2     |

| SUBWFB f   | f, d  | Subtract with Borrow W from f | 1             | 11     | 1011   | dfff   | ffff | C, DC, Z | 2     |

| SWAPF f    | f, d  | Swap nibbles in f             | 1             | 00     | 1110   | dfff   | ffff |          | 2     |

| XORWF f    | f, d  | Exclusive OR W with f         | 1             | 00     | 0110   | dfff   | ffff | Z        | 2     |

|            |       | BYTE ORIENTED                 | SKIP OPERATIO | ONS    |        |        |      |          |       |

| DECFSZ f   | f, d  | Decrement f, Skip if 0        | 1(2)          | 00     | 1011   | dfff   | ffff |          | 1, 2  |

| INCFSZ f   | f, d  | Increment f, Skip if 0        | 1(2)          | 00     | 1111   | dfff   | ffff |          | 1, 2  |

|            |       | BIT-ORIENTED FILE R           | EGISTER OPER  | RATION | IS     |        |      | •        |       |

| BCF f      | f, b  | Bit Clear f                   | 1             | 01     | 00bb   | bfff   | ffff |          | 2     |

| BSF f      | f, b  | Bit Set f                     | 1             | 01     | 01bb   | bfff   | ffff |          | 2     |

|            |       | BIT-ORIENTED S                | SKIP OPERATIO | NS     |        |        |      | •        |       |

| BTFSC f    | f, b  | Bit Test f, Skip if Clear     | 1 (2)         | 01     | 10bb   | bfff   | ffff |          | 1, 2  |

| BTFSS f    | f, b  | Bit Test f, Skip if Set       | 1 (2)         | 01     | 11bb   | bfff   | ffff |          | 1, 2  |

| LITERAL OF | PERA  |                               |               |        |        |        |      | 1        |       |

|            | ĸ     | Add literal and W             | 1             | 11     | 1110   | kkkk   |      | C, DC, Z |       |

|            | ĸ     | AND literal with W            | 1             | 11     | 1001   | kkkk   |      | Z        |       |

|            | ĸ     | Inclusive OR literal with W   | 1             | 11     | 1000   | kkkk   |      | Z        |       |

|            | ĸ     | Move literal to BSR           | 1             | 00     | 0000   | 001k   |      |          |       |

|            | ĸ     | Move literal to PCLATH        | 1             | 11     | 0001   | 1kkk   | kkkk |          |       |

|            | ĸ     | Move literal to W             | 1             | 11     | 0000   | kkkk   | kkkk |          |       |

| SUBLW I    | ĸ     | Subtract W from literal       | 1             | 11     | 1100   | kkkk   | kkkk | C, DC, Z |       |

| XORLW I    | ĸ     | Exclusive OR literal with W   | 1             | 11     | 1010   | kkkk   | kkkk | Z        |       |

#### TABLE 20-3: PIC16LF1902/3 ENHANCED INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01,10,11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                            |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR + 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR + 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP     |  |

|---------|--|

| Syntax: |  |

#### No Operation

| Syntax:          | [label] NOP   |

|------------------|---------------|

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                   |  |  |  |

|------------------|----------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RESET                                                                    |  |  |  |

| Operands:        | None                                                                             |  |  |  |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.             |  |  |  |

| Status Affected: | None                                                                             |  |  |  |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |  |  |  |

#### TABLE 21-4: I/O PORTS

| DC CHARACTERISTICS |      |                                      | Standard Operating Conditions (unless otherwise stated) |      |          |       |                                                          |  |

|--------------------|------|--------------------------------------|---------------------------------------------------------|------|----------|-------|----------------------------------------------------------|--|

| Param<br>No.       | Sym. | Characteristic                       | Min.                                                    | Тур† | Max.     | Units | Conditions                                               |  |

|                    | VIL  | Input Low Voltage                    |                                                         |      |          |       |                                                          |  |

|                    |      | I/O PORT:                            |                                                         |      |          |       |                                                          |  |

| D032               |      | with TTL buffer                      | —                                                       | _    | 0.15 VDD | V     | $1.8V \le VDD \le 3.6V$                                  |  |

| D033               |      | with Schmitt Trigger buffer          | —                                                       | _    | 0.2 Vdd  | V     | $1.8V \leq V\text{DD} \leq 3.6V$                         |  |

| D034               |      | MCLR, OSC1                           |                                                         | _    | 0.2 VDD  | V     |                                                          |  |

|                    | VIH  | Input High Voltage                   |                                                         |      |          |       |                                                          |  |

|                    |      | I/O ports:                           |                                                         |      |          |       |                                                          |  |

| D040               |      | with TTL buffer                      | 0.25 VDD +<br>0.8                                       | _    | —        | V     | $1.8V \leq V\text{DD} \leq 3.6V$                         |  |

| D041               |      | with Schmitt Trigger buffer          | 0.8 VDD                                                 | _    | —        | V     | $1.8V \leq V\text{DD} \leq 3.6V$                         |  |

| D042               |      | MCLR                                 | 0.8 VDD                                                 | _    | —        | V     |                                                          |  |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup> |                                                         |      |          |       |                                                          |  |

| D060               |      | I/O ports                            | —                                                       | ± 5  | ± 125    | nA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance @ 85°C |  |

|                    |      |                                      |                                                         | ± 5  | ± 1000   | nA    | 125°C                                                    |  |

| D061               |      | MCLR <sup>(3)</sup>                  | —                                                       | ± 50 | ± 200    | nA    | $Vss \le VPIN \le VDD @ 85^{\circ}C$                     |  |

|                    | IPUR | Weak Pull-up Current                 |                                                         |      |          |       |                                                          |  |