Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

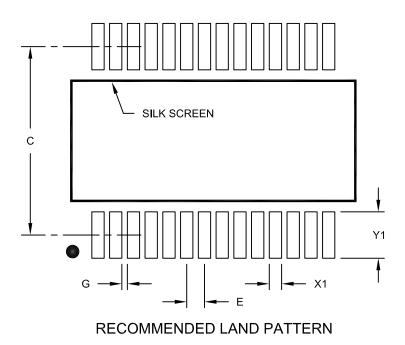

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1903-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-2: **PIC16LF1902/3 PINOUT DESCRIPTION**

| Name                                 | Function | Input<br>Type | Output<br>Type | Description                     |  |

|--------------------------------------|----------|---------------|----------------|---------------------------------|--|

| RA0/AN0/SEG12                        | RA0      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN0      | AN            |                | A/D Channel 0 input.            |  |

|                                      | SEG12    | _             | AN             | LCD Analog output.              |  |

| RA1/AN1/SEG7                         | RA1      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN1      | AN            | _              | A/D Channel 1 input.            |  |

|                                      | SEG7     | _             | AN             | LCD Analog output.              |  |

| RA2/AN2/COM2                         | RA2      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN2      | AN            | —              | A/D Channel 2 input.            |  |

|                                      | COM2     | _             | AN             | LCD Analog output.              |  |

| RA3/AN3/VREF+/COM3/SEG15             | RA3      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN3      | AN            |                | A/D Channel 3 input.            |  |

|                                      | VREF+    | AN            |                | A/D Voltage Reference input.    |  |

|                                      | COM3     | _             | AN             | LCD Analog output.              |  |

|                                      | SEG15    | _             | AN             | LCD Analog output.              |  |

| RA4/T0CKI/SEG4                       | RA4      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | TOCKI    | ST            | _              | Timer0 clock input.             |  |

|                                      | SEG4     | _             | AN             | LCD Analog output.              |  |

| RA5/AN4/SEG5                         | RA5      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN4      | AN            | _              | A/D Channel 4 input.            |  |

|                                      | SEG5     |               | AN             | LCD Analog output.              |  |

| RA6/CLKOUT/SEG1                      | RA6      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | CLKOUT   | _             | CMOS           | Fosc/4 output.                  |  |

|                                      | SEG1     | _             | AN             | LCD Analog output.              |  |

| RA7/CLKIN/SEG2                       | RA7      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | CLKIN    | CMOS          | _              | External clock input (EC mode). |  |

|                                      | SEG2     | _             | AN             | LCD Analog output.              |  |

| RB0/AN12/INT/SEG0                    | RB0      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN12     | AN            | _              | A/D Channel 12 input.           |  |

|                                      | INT      | ST            |                | External interrupt.             |  |

|                                      | SEG0     |               | AN             | LCD Analog output.              |  |

| RB1 <sup>(1)</sup> /AN10/SEG24/VLCD1 | RB1      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN10     | AN            | _              | A/D Channel 10 input.           |  |

|                                      | SEG24    | —             | AN             | LCD Analog output.              |  |

|                                      | VLCD1    | AN            | —              | LCD analog input.               |  |

| RB2 <sup>(1)</sup> /AN8/SEG25/VLCD2  | RB2      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN8      | AN            | _              | A/D Channel 8 input.            |  |

|                                      | SEG25    | —             | AN             | LCD Analog output.              |  |

|                                      | VLCD2    | AN            |                | LCD analog input.               |  |

| RB3 <sup>(1)</sup> /AN9/SEG26/VLCD3  | RB3      | TTL           | CMOS           | General purpose I/O.            |  |

|                                      | AN9      | AN            |                | A/D Channel 9 input.            |  |

|                                      | SEG26    | _             | AN             | LCD Analog output.              |  |

|                                      | VLCD3    | AN            |                | LCD analog input.               |  |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

levels

Note 1: These pins have interrupt-on-change functionality.

| AddNameBit 6Bit 6Bit 4Bit 3Bit 2Bit 1Bit 0PQR, BORPIDChLATAPORTA DataLatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 10Ch       LATA       PORTA Data Latch       XXXX XXXX       uu       uu         10Dh       LATB       PORTB Data Latch       XXXX XXXX       uu         10Eh       LATC       PORTC Data Latch       XXXX XXXX       uu         10Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Value on all<br>other<br>Resets |

| 10Db       LATB       PORTB Data Latch       xxxx xxxx       uu       uu       uu       uu         10Fh       -       QRTC Data Latch       xxxx xxxx       uu       uu <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |

| 10En       LATC       PORTC Data Latch       xxxx xxxx       uu       uu         10Fn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | uuuu uuuu                       |

| 10Fh       -       Unimplemented       -       -       -       BORRD       10        10         116h       BORCON       SBOREN       BORFS       -       -       -       ADFVR1       ADFVR0       0q00000       0q         117h       FVRCON       FVREN       FVREN       TSEN       TSENG       -       -       ADFVR1       ADFVR0       0q00000       0q         118h       -       Unimplemente       FVREN       FVREN       TSEN       TSENG       -       -       ADFVR1       ADFVR0       0q00000       0q         118h       -       Unimplemente/       -       ANSA5       -       ANSA3       ANSA2       ANSA1       ANSA0       -1-1       111       -         18Dh       ANSELB       -       -       ANSB5       ANSB4       ANSB3       ANSB2       ANSB1       ANSB0      11       111        100       111       11        -       1111         1000       000       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | uuuu uuuu                       |

| tot       nom       n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | uuuu uuuu                       |

| 117h       FVRCON       FVREN       FVRENP       TSEN       TSENG       -       -       ADFVR1       ADFVR0       0q00       0q0       0q00       -       0q00       0q000       0q00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                               |

| 18h to to to the tot to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | auu                             |

| to<br>11Fh       -       Unimplemented       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       ANSA3       ANSA2       ANSA1       ANSA0       -       -       1       -       -       -       1       1       -       -       1       1       -       -       1       1       -       -       1       1       -       1       1       -       1       1       -       1       1       -       1       1       1       -       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <th1< th="">       1       1</th1<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0q0000                          |

| 18ch       ANSELA       —       —       ANSA3       ANSA2       ANSA1       ANSA0      1-1111          18bh       ANSELB       —       —       ANSB5       ANSB4       ANSB3       ANSB2       ANSB1       ANS00      1-1111          18bh       —       Unimplemented       —       —       ANSB5       ANSB1       ANSB2       ANSB1       ANS00      1-1111          18bh       —       Unimplemented       —       Unimplemented       —       —       —       —       —       —       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                               |

| 18Dh       ANSELB       —       ANSB5       ANSB5       ANSB2       ANSB1       ANSB0      11       111          18Eh       —       Unimplem=t       Unimplemet       Implemet       Implem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 18Eh        Unimplement           1         18Fh        Unimplement          1         190h        Unimplement         1       0       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00 <td>11 1111</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 1111                         |

| 18Fh        Unimplement       Image: Imag | 11 1111                         |

| 190h        Unimplement       Implement       Implement <thi< td=""><td>_</td></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                               |

| 191h       PMADRL       Program Memory Address Register Low Byte       0000000       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                               |

| 192h       PMADRH       -(2)       Program Memory Red Data Register Low Byte       1000 000       101         193h       PMDATL       Program Memory Read Data Register Low Byte       xxxx xxxx       uu         194h       PMDATH       -       -       Program Memory Read Data Register Low Byte       xxxx xxxx       uu         194h       PMDATH       -       -       Program Memory Read Data Register High Byte      xx xxxx          195h       PMCON1       -       -       Program Memory Read Data Register High Byte      xx xxxx          195h       PMCON2       Program Memory Control register 2       WRERR       WREN       WR       RD       1000 000       10         196h       PMCON2       Program Memory Control register 2        0000 000       00       10         197h       -       -       0       Unimplemented        -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                               |

| 1011       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000 0000                       |

| 194h       PMDATH       —       —       Program Memory Read Data Register High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1000 0000                       |

| 195h         PMCON1        (2)         CFGS         LWLO         FREE         WRERR         WREN         WR         RD         1000 x000         10           196h         PMCON2         Program Memory Control Register 2         0000 0000         00           197h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | uuuu uuuu                       |

| NNCONT         NNCONT<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | uu uuuu                         |

| 197h<br>to<br>19Fh       -       Unimplemented       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - </td <td>1000 q000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1000 q000                       |

| to<br>19Fh-UnimplementedBancton20Ch-UnimplementedVPUB3VPUB3VPUB1VPUB011111120Ch-OUnimplementedVPUB3VPUB2VPUB1VPUB011111120Ch-OUnimplemented1020Fh-OUnimplemented1020Fh-O-O-O <t< td=""><td>0000 0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000 0000                       |

| 20Ch        Unimplemeter            11       111       11         20Dh       WPUB       WPUB7       WPUB6       WPUB5       WPUB3       WPUB2       WPUB1       WPUB0       1111       11         20Eh        Miniplemeter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                               |

| 20Dh         WPUB         WPUB7         WPUB6         WPUB5         WPUB3         WPUB2         WPUB1         WPUB0         111         11           20Dh         —         Unimplemented         —         —         —         —         —         —         —         —         —         —         —         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _         _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

| 20Eh        Unimplemented </td <td>—</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                               |

| 20Fh        Unimplementation                                                                                                                   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1111 1111                       |

| 210h       WPUE       -       -       WPUE3       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                               |

| 211h     -     Unimplemented     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                               |

| to 21Fh Unimplemented —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                               |

| Bank E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| Bank 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 28Ch — Unimplemented —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                               |

| 29Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

| Bank 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 30Ch — Unimplemented —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                               |

| 31Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

TABLE 3-5: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Shaded locations are unimplemented, read as '0'. Note 1: These registers can be addressed from any bank.

**2:** Unimplemented, read as '1'.

### 4.5 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

#### REGISTER 4-3: DEVICEID: DEVICE ID REGISTER

|       |          | R      | R | R   | R        | R | R     |

|-------|----------|--------|---|-----|----------|---|-------|

|       |          |        |   | DEV | <8:3>    |   |       |

|       |          | bit 13 |   |     |          |   | bit 8 |

|       |          |        |   |     |          |   |       |

| R     | R        | R      | R | R   | R        | R | R     |

|       | DEV<2:0> |        |   |     | REV<4:0> |   |       |

| bit 7 |          |        |   |     |          |   | bit 0 |

| -     |          |        |   |     |          |   |       |

### Legend:

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '1'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | P = Programmable bit                                  |

bit 13-5 **DEV<8:0>:** Device ID bits

| Device      | DEVICEID<13:0> Values |          |  |  |

|-------------|-----------------------|----------|--|--|