Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

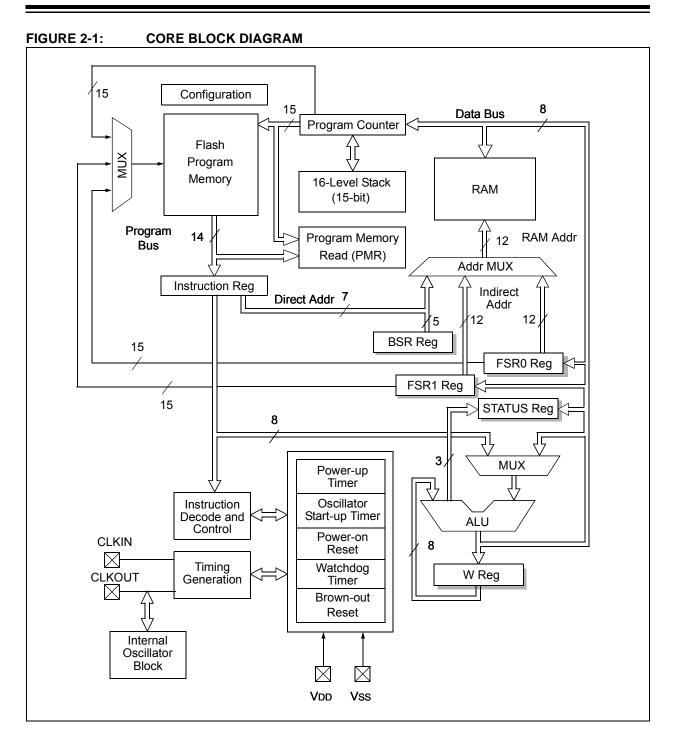

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1903t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                              | Function | Input<br>Type | Output<br>Type | Description                         |

|-----------------------------------|----------|---------------|----------------|-------------------------------------|

| RB4 <sup>(1)</sup> /AN11/COM0     | RB4      | TTL           | CMOS           | General purpose I/O.                |

|                                   | AN11     | AN            |                | A/D Channel 11 input.               |

|                                   | COM0     |               | AN             | LCD Analog output.                  |

| RB5 <sup>(1)</sup> /AN13/COM1     | RB5      | TTL           | CMOS           | General purpose I/O.                |

|                                   | AN13     | AN            |                | A/D Channel 13 input.               |

|                                   | COM1     | _             | AN             | LCD Analog output.                  |

| RB6 <sup>(1)</sup> /ICSPCLK/SEG14 | RB6      | TTL           | CMOS           | General purpose I/O.                |

|                                   | ICSPCLK  | ST            |                | Serial Programming Clock.           |

|                                   | SEG14    |               | AN             | LCD Analog output.                  |

| RB7 <sup>(1)</sup> /ICSPDAT/SEG13 | RB7      | TTL           | CMOS           | General purpose I/O.                |

|                                   | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                     |

|                                   | SEG13    |               | AN             | LCD Analog output.                  |

| RC0/T1OSO/T1CKI                   | RC0      | TTL           | CMOS           | General purpose I/O.                |

|                                   | T1OSO    | XTAL          | XTAL           | Timer1 oscillator connection.       |

|                                   | T1CKI    | ST            |                | Timer1 clock input.                 |

| RC1/T10SI                         | RC1      | TTL           | CMOS           | General purpose I/O.                |

|                                   | T1OSI    | XTAL          | XTAL           | Timer1 oscillator connection.       |

| RC2/SEG3                          | RC2      | TTL           | CMOS           | General purpose I/O.                |

|                                   | SEG3     | _             | AN             | LCD Analog output.                  |

| RC3/SEG6                          | RC3      | TTL           | CMOS           | General purpose I/O.                |

|                                   | SEG6     | _             | AN             | LCD Analog output.                  |

| RC4/T1G/SEG11                     | RC4      | TTL           | CMOS           | General purpose I/O.                |

|                                   | T1G      | XTAL          | XTAL           | Timer1 oscillator connection.       |

|                                   | SEG11    |               | AN             | LCD Analog output.                  |

| RC5/SEG10                         | RC5      | TTL           | CMOS           | General purpose I/O.                |

|                                   | SEG10    |               | AN             | LCD Analog output.                  |

| RC6/SEG9                          | RC6      | ST            | CMOS           | General purpose I/O.                |

|                                   | SEG9     |               | AN             | LCD Analog output.                  |

| RC7/SEG8                          | RC7      | ST            | CMOS           | General purpose I/O.                |

|                                   | SEG8     | _             | AN             | LCD Analog output.                  |

| RE3/MCLR/VPP                      | RE3      | TTL           | CMOS           | General purpose I/O.                |

|                                   | MCLR     | ST            | _              | Master Clear with internal pull-up. |

|                                   | VPP      | HV            | _              | Programming voltage.                |

| Vdd                               | Vdd      | Power         | _              | Positive supply.                    |

| Vss                               | Vss      | Power         |                | Ground reference.                   |

TABLE 1-2. PIC16LF1902/3 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS = CMOS compatible input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

OD = Open-Drain

levels

Note 1: These pins have interrupt-on-change functionality.

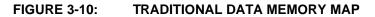

#### 3.5.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

## 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

| Note: | The DEBUG bit in Configuration Words is     |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

#### 5.3 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) is an essential part of the Reset subsystem. Refer to Figure 5-1 to see how the BOR interacts with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit ( $\overline{BOR}$ ) is changed to indicate that a BOR Reset has occurred. The same bit is set for both the BOR and the LPBOR. Refer to Register 5-2.

#### 5.3.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Word 2. When the device is erased, the LPBOR module defaults to disabled.

### 5.3.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is to be OR'd together with the Reset signal of the BOR module to provide the generic BOR signal which goes to the PCON register and to the power control block.

## 5.4 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Word 1 and the LVP bit of Configuration Word 2 (Table 5-2).

TABLE 5-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

## 5.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

```

Note: A Reset does not drive the \overline{\text{MCLR}} pin low.

```

## 5.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.4** "**PORTE Registers**" for more information.

## 5.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0** "**Watchdog Timer**" for more information.

### 5.6 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 5-4 for default conditions after a RESET instruction has occurred.

## 5.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Word 2. See **Section 5.7 "Stack Overflow/Underflow Reset"** for more information.

## 5.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

## 5.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of Configuration Word 1.

## 5.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 6.0 "Oscillator Module"** for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution immediately (see Figure 5-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| TABLE 3-3. SUMMART OF REGISTERS ASSOCIATED WITTRESETS |        |        |            |       |       |       |       |        |                     |

|-------------------------------------------------------|--------|--------|------------|-------|-------|-------|-------|--------|---------------------|

| Name                                                  | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

| BORCON                                                | SBOREN | BORFS  | _          |       |       | _     | _     | BORRDY | 40                  |

| PCON                                                  | STKOVF | STKUNF | _          | RWDT  | RMCLR | RI    | POR   | BOR    | 44                  |

| STATUS                                                | _      | _      | _          | TO    | PD    | Z     | DC    | С      | 16                  |

| WDTCON                                                |        |        | WDTPS<4:0> |       |       |       |       | SWDTEN | 70                  |

TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

#### 7.6.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 7-2.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

#### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|-----|-----|-----|-----|-----|---------|

| TMR1GIE | ADIE    | —   | —   | —   | —   | —   | TMR1IE  |

| bit 7   |         |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | TMR1GIE: Timer1 Gate Interrupt Enable bit          |

|---------|----------------------------------------------------|

|         | 1 = Enables the Timer1 Gate Acquisition interrupt  |

|         | 0 = Disables the Timer1 Gate Acquisition interrupt |

| bit 6   | ADIE: A/D Converter (ADC) Interrupt Enable bit     |

|         | 1 = Enables the ADC interrupt                      |

|         | 0 = Disables the ADC interrupt                     |

| bit 5-1 | Unimplemented: Read as '0'                         |

| bit 0   | TMR1IE: Timer1 Overflow Interrupt Enable bit       |

|         | 1 = Enables the Timer1 overflow interrupt          |

|         | 0 = Disables the Timer1 overflow interrupt         |

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Secondary oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- 9. I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- · Modules using Secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **13.0** "Fixed Voltage Reference (FVR)" for more information.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 5.11**, **Determining the Cause of a Reset**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

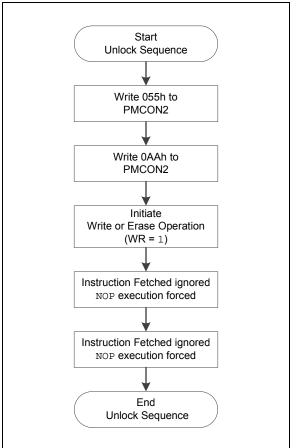

#### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash Program Memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

#### FIGURE 10-3:

#### FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

#### **REGISTER 11-5: PORTB: PORTB REGISTER**

| R/W-x/u                                 | R/W-x/u | R/W-x/u                                               | R/W-x/u      | R/W-x/u          | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------------------------------------|---------|-------------------------------------------------------|--------------|------------------|---------|---------|---------|

| RB7                                     | RB6     | RB5                                                   | RB4          | RB3              | RB2     | RB1     | RB0     |

| bit 7                                   |         |                                                       |              |                  |         |         | bit 0   |

|                                         |         |                                                       |              |                  |         |         |         |

| Legend:                                 |         |                                                       |              |                  |         |         |         |

| R = Readable bit W = Writable bit       |         |                                                       | U = Unimpler | mented bit, read | as '0'  |         |         |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |              |                  |         |         |         |

| '1' = Bit is set                        |         | '0' = Bit is clea                                     | ared         |                  |         |         |         |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 11-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 11-7: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

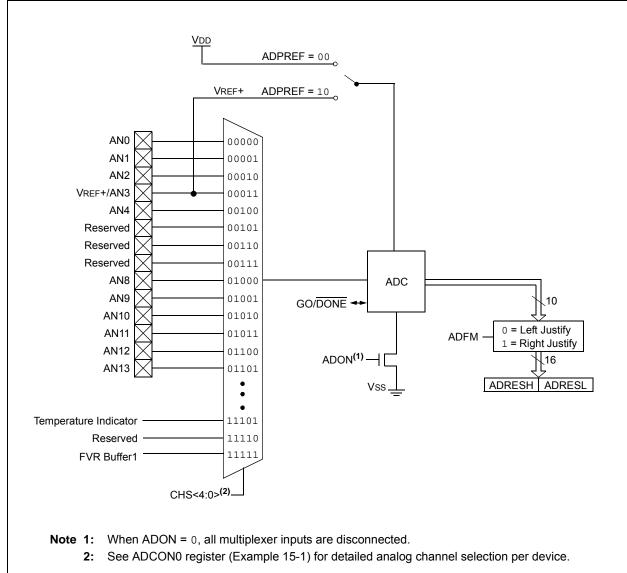

## 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 15-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

#### FIGURE 15-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

| FIGURE 17-6:           | TIMER1 GATE SINGLE                                               | -PULSE AND TOGGLE COMBINED MODE                      |

|------------------------|------------------------------------------------------------------|------------------------------------------------------|

| TMR1 <u>GE</u>         |                                                                  |                                                      |

| T1GSPM                 |                                                                  |                                                      |

| T1GTM                  |                                                                  |                                                      |

| T1GG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled or</li> </ul> | Cleared by hardware on<br>falling edge of T1GVAL     |

| T1G_IN                 | rising edge of T10                                               |                                                      |

| т1СКІ                  |                                                                  |                                                      |

| T1GV <u>AL</u>         |                                                                  |                                                      |

| Timer1                 | Ν                                                                | N + 1 N + 2 N + 3 N + 4                              |

| TMR1GIF                | <ul> <li>Cleared by software</li> </ul>                          | Set by hardware on Cleared by falling edge of T1GVAL |

## PIC16LF1902/3

#### REGISTER 18-2: LCDPS: LCD PHASE REGISTER

| R/W-0/0          | R/W-0/0                      | R-0/0                               | R-0/0              | R/W-0/0       | R/W-0/0          | R/W-1/1          | R/W-1/1      |

|------------------|------------------------------|-------------------------------------|--------------------|---------------|------------------|------------------|--------------|

| WFT              | BIASMD                       | LCDA                                | WA                 |               | LP<              | 3:0>             |              |

| bit 7            |                              |                                     |                    |               |                  |                  | bit (        |

|                  |                              |                                     |                    |               |                  |                  |              |

| Legend:          |                              |                                     |                    |               |                  | (0)              |              |

| R = Readable     |                              | W = Writable                        |                    | -             | mented bit, read |                  |              |

| u = Bit is unch  | -                            | x = Bit is unk                      |                    |               | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                              | '0' = Bit is cle                    | eared              | C = Only clea | arable bit       |                  |              |

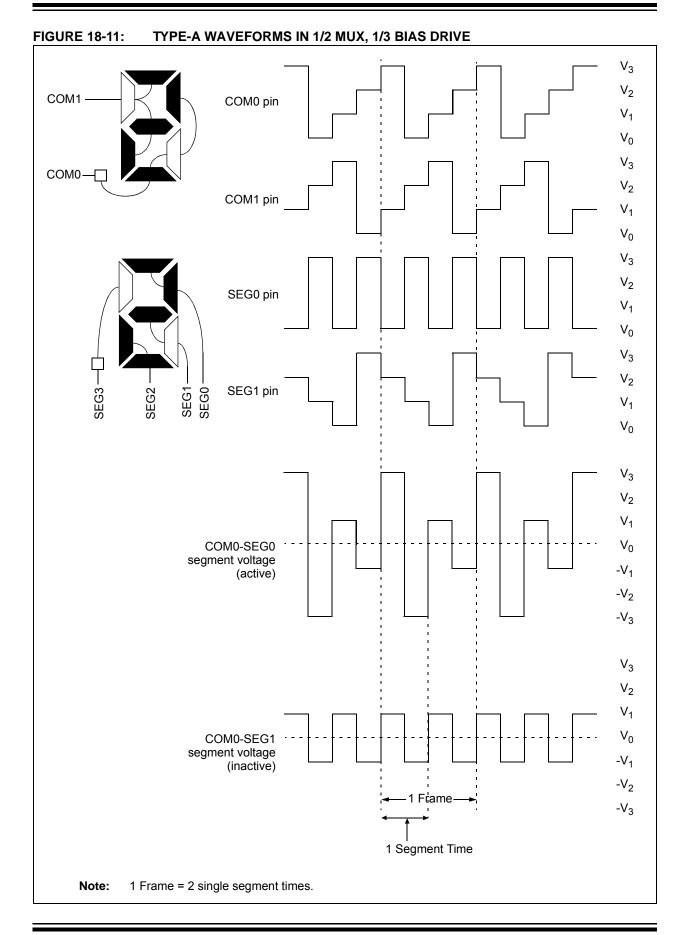

| bit 7            | WFT: Wavefo                  | orm Type hit                        |                    |               |                  |                  |              |

| bit i            |                              | phase changes                       | on each fram       | ne boundary   |                  |                  |              |

|                  |                              | phase changes                       |                    |               |                  |                  |              |

| bit 6            | BIASMD: Bia                  | as Mode Selec                       | t bit              |               |                  |                  |              |

|                  | When LMUX                    | <1:0> = <u>00:</u>                  |                    |               |                  |                  |              |

|                  |                              | as mode (do no                      | ot set this bit to | oʻ1')         |                  |                  |              |

|                  | When LMUX                    |                                     |                    |               |                  |                  |              |

|                  | 1 = 1/2 Bias<br>0 = 1/3 Bias |                                     |                    |               |                  |                  |              |

|                  | When LMUX                    |                                     |                    |               |                  |                  |              |

|                  | 1 = 1/2 Bias                 |                                     |                    |               |                  |                  |              |

|                  | 0 = 1/3 Bias                 | mode                                |                    |               |                  |                  |              |

|                  | When LMUX                    |                                     |                    |               |                  |                  |              |

|                  |                              | mode (do not s                      |                    | 1')           |                  |                  |              |

| bit 5            |                              | Active Status b                     |                    |               |                  |                  |              |

|                  |                              | ver module is a<br>ver module is ir |                    |               |                  |                  |              |

| bit 4            | WA: LCD Wr                   | ite Allow Statu                     | s bit              |               |                  |                  |              |

|                  |                              | the LCDDATA                         |                    |               |                  |                  |              |

| bit 3-0          | LP<3:0>: LC                  | D Prescaler S                       | election bits      |               |                  |                  |              |

|                  | 1111 <b>= 1</b> :16          |                                     |                    |               |                  |                  |              |

|                  | 1110 = 1:15                  |                                     |                    |               |                  |                  |              |

|                  | 1101 = 1:14<br>1100 = 1:13   |                                     |                    |               |                  |                  |              |

|                  | 1011 = 1:12                  |                                     |                    |               |                  |                  |              |

|                  | 1010 = <b>1</b> : <b>11</b>  |                                     |                    |               |                  |                  |              |

|                  | 1001 = 1:10                  |                                     |                    |               |                  |                  |              |

|                  | 1000 = 1:9<br>0111 = 1:8     |                                     |                    |               |                  |                  |              |

|                  | 0110 = 1.7                   |                                     |                    |               |                  |                  |              |

|                  | 0101 = 1:6                   |                                     |                    |               |                  |                  |              |

|                  | 0100 = 1:5                   |                                     |                    |               |                  |                  |              |

|                  | 0011 = 1:4<br>0010 = 1:3     |                                     |                    |               |                  |                  |              |

|                  | 0010 = 1.3<br>0001 = 1.2     |                                     |                    |               |                  |                  |              |

|                  | 0000 = 1:1                   |                                     |                    |               |                  |                  |              |

| R/W-0/0              | R/W-0/0                                                                                            | R/W-0/0                                                                                                                                         | R/W-0/0                                                                                                  | U-0                                                                                                | R/W-0/0                                                                                                               | R/W-0/0                                                                                                                            | R/W-0/0                                                                                          |  |  |

|----------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| LRLAP<1:0>           |                                                                                                    | LRLBF                                                                                                                                           | P<1:0>                                                                                                   | —                                                                                                  |                                                                                                                       | LRLAT<2:0>                                                                                                                         |                                                                                                  |  |  |

| bit 7                |                                                                                                    |                                                                                                                                                 |                                                                                                          |                                                                                                    |                                                                                                                       |                                                                                                                                    | bit (                                                                                            |  |  |

|                      |                                                                                                    |                                                                                                                                                 |                                                                                                          |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

| Legend:              |                                                                                                    |                                                                                                                                                 |                                                                                                          |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

| R = Readable         | e bit                                                                                              | W = Writable bit                                                                                                                                |                                                                                                          | -                                                                                                  | mented bit, read                                                                                                      |                                                                                                                                    |                                                                                                  |  |  |

| u = Bit is unchanged |                                                                                                    | x = Bit is unknown                                                                                                                              |                                                                                                          | -n/n = Value a                                                                                     | at POR and BO                                                                                                         | R/Value at all ot                                                                                                                  | her Resets                                                                                       |  |  |

| '1' = Bit is set     |                                                                                                    | '0' = Bit is clea                                                                                                                               | 0' = Bit is cleared                                                                                      |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

| bit 7-6              | During Time in<br>00 = Internal<br>01 = Internal<br>10 = Internal                                  | LCD Reference<br>nterval A (Refer<br>LCD Reference<br>LCD Reference<br>LCD Reference                                                            | toFigure 18-4<br>Ladder is pow<br>Ladder is pow<br>Ladder is pow                                         | ):<br>vered down and<br>vered in Low-P<br>vered in Mediui                                          | d unconnected<br>ower mode<br>m-Power mode                                                                            |                                                                                                                                    |                                                                                                  |  |  |

| bit 5-4              | LRLBP<1:0><br>During Time in<br>00 = Internal<br>01 = Internal<br>10 = Internal                    | LCD Reference<br>: LCD Reference<br>nterval B (Refer<br>LCD Reference<br>LCD Reference<br>LCD Reference<br>LCD Reference                        | e Ladder B Tir<br>to Figure 18-4<br>Ladder is pov<br>Ladder is pov                                       | ne Power Cont<br>):<br>vered down and<br>vered in Low-P<br>vered in Mediu                          | rol bits<br>d unconnected<br>ower mode<br>m-Power mode                                                                |                                                                                                                                    |                                                                                                  |  |  |

| bit 3                | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                 | ,                                                                                                        |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

| bit 2-0              |                                                                                                    | LRLAT<2:0>: LCD Reference Ladder A Time Interval Control bits<br>Sets the number of 32 kHz clocks that the A Time Interval Power mode is active |                                                                                                          |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

|                      | For type A wa                                                                                      | veforms (WFT =                                                                                                                                  | • 0):                                                                                                    |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

|                      | 001 = Interna<br>010 = Interna<br>011 = Interna<br>100 = Interna<br>101 = Interna<br>110 = Interna | I LCD Reference<br>I LCD Reference<br>I LCD Reference<br>I LCD Reference<br>I LCD Reference                                                     | e Ladder is in<br>e Ladder is in | A' Power mode<br>A' Power mode<br>A' Power mode<br>A' Power mode<br>A' Power mode<br>A' Power mode | e for 1 clock and<br>for 2 clocks and<br>for 3 clocks and<br>for 4 clocks and<br>for 5 clocks and<br>for 6 clocks and | d 'B' Power mod<br>d 'B' Power mod<br>nd 'B' Power mod | le for 14 clocks<br>le for 13 clocks<br>le for 12 clocks<br>le for 11 clocks<br>le for 10 clocks |  |  |

|                      | For type B wa                                                                                      | veforms (WFT =                                                                                                                                  | 1):                                                                                                      |                                                                                                    |                                                                                                                       |                                                                                                                                    |                                                                                                  |  |  |

|                      | 001 = Interna<br>010 = Interna<br>011 = Interna<br>100 = Interna<br>101 = Interna<br>110 = Interna | I LCD Reference<br>I LCD Reference<br>I LCD Reference<br>I LCD Reference<br>I LCD Reference                                                     | e Ladder is in<br>e Ladder is in | A' Power mode<br>A' Power mode<br>A' Power mode<br>A' Power mode<br>A' Power mode<br>A' Power mode | e for 1 clock and<br>for 2 clocks and<br>for 3 clocks and<br>for 4 clocks and<br>for 5 clocks and<br>for 6 clocks and | d 'B' Power mod<br>d 'B' Power mod  | le for 30 clock<br>le for 29 clock<br>le for 28 clock<br>le for 27 clock<br>le for 26 clock      |  |  |

## REGISTER 18-7: LCDRL: LCD REFERENCE LADDER CONTROL REGISTERS

## PIC16LF1902/3

# PIC16LF1902/3

| Mnemonic,<br>Operands |      | Description                                   | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|------|-----------------------------------------------|--------|---------------|------|------|------|----------|-------|

|                       |      | Description                                   | Cycles | MSb           |      |      | LSb  | Affected | NOLES |

|                       |      | CONTROL OPERA                                 | TIONS  |               |      |      |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11            | 001k | kkkk | kkkk |          |       |

| BRW                   | -    | Relative Branch with W                        | 2      | 00            | 0000 | 0000 | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2      | 00            | 0000 | 0000 | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11            | 0100 | kkkk | kkkk |          |       |

| RETURN                | -    | Return from Subroutine                        | 2      | 00            | 0000 | 0000 | 1000 |          |       |

|                       |      |                                               | TIONS  |               |      |      |      |          |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00            | 0000 | 0110 | 0100 | TO, PD   |       |

| NOP                   | _    | No Operation                                  | 1      | 00            | 0000 | 0000 | 0000 |          |       |

| OPTION                | _    | Load OPTION_REG register with W               | 1      | 00            | 0000 | 0110 | 0010 |          |       |

| RESET                 | -    | Software device Reset                         | 1      | 00            | 0000 | 0000 | 0001 |          |       |

| SLEEP                 | -    | Go into Standby mode                          | 1      | 00            | 0000 | 0110 | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00            | 0000 | 0110 | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED |               |      |      |      |          |       |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11            | 0001 | 0nkk | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00            | 0000 | 0001 | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |               |      |      |      |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11            | 1111 | 0nkk | kkkk | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00            | 0000 | 0001 | 1nmm |          | 2, 3  |

|                       |      | modifier, mm                                  |        |               |      |      |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11            | 1111 | 1nkk | kkkk |          | 2     |

## TABLE 20-3: PIC16LF1902/3 ENHANCED INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

## 21.3 AC Characteristics

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp3 |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| т       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerc  | ase letters (pp) and their meanings: |     |                |

| рр      |                                      |     |                |

| сс      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| CS      | CS                                   | rw  | RD or WR       |

| di      | SDI                                  | SC  | SCK            |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | TOCKI          |

| io      | I/O PORT                             | t1  | T1CKI          |

| mc      | MCLR                                 | wr  | WR             |

| Upperc  | ase letters and their meanings:      | •   |                |

| S       |                                      |     |                |

| F       | Fall                                 | Р   | Period         |

| н       | High                                 | R   | Rise           |

| 1       | Invalid (High-Impedance)             | V   | Valid          |

| L       | Low                                  | Z   | High-Impedance |

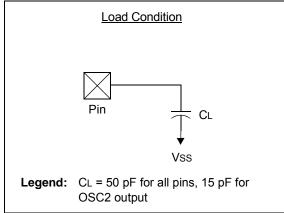

#### FIGURE 21-4: LOAD CONDITIONS

## 22.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

Graphs and charts are not available at this time.

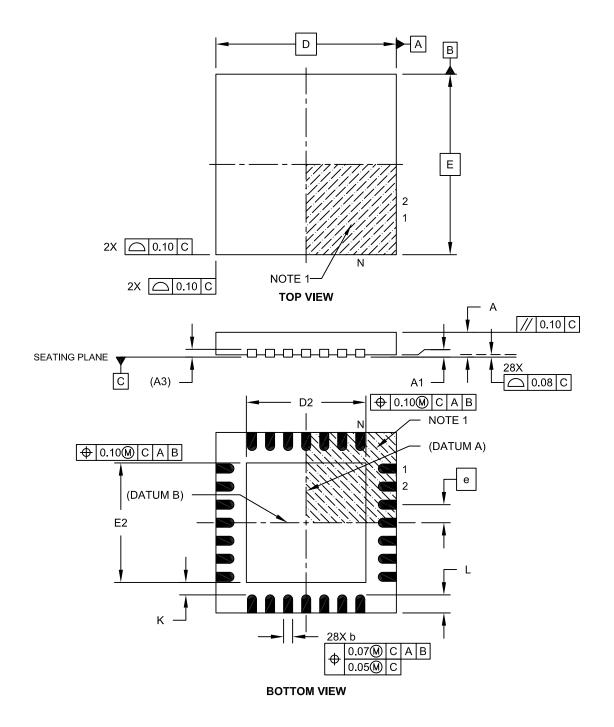

28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15