Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

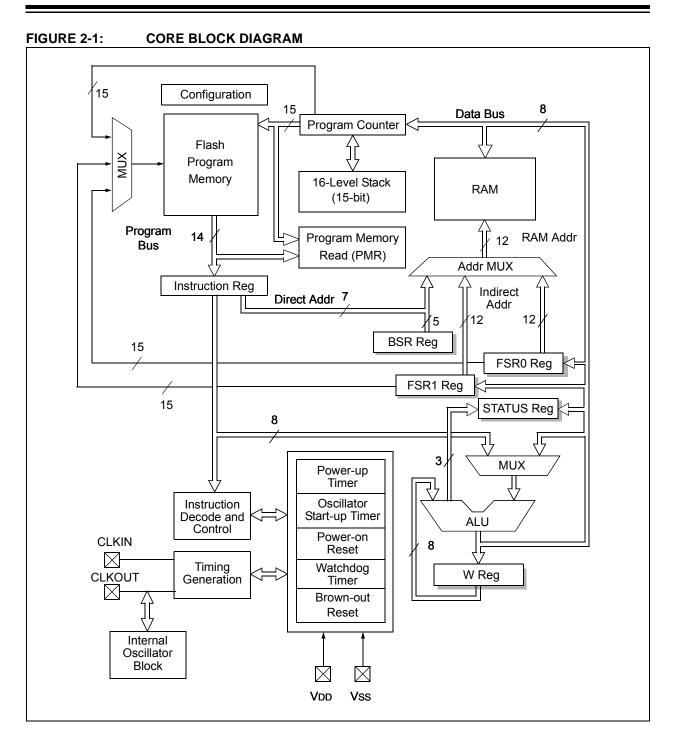

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

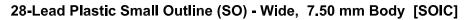

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1903t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- · Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device      | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash Memory<br>Address Range <sup>(1)</sup> |

|-------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC16LF1902 | 2,048                           | 07FFh                          | 0780h-07FFh                                                 |

| PIC16LF1903 | 4,096                           | 0FFFh                          | 0F80h-0FFFh                                                 |

**Note 1:** High-endurance Flash applies to low byte of each address in the range.

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16LF1902/3 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1, and 3-2).

|              |                                                                                    | R/P-1                                                                                                          | R/P-1                             | R/P-1              | R/P-1               | R/P-1                          | U-1           |  |

|--------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------|---------------------|--------------------------------|---------------|--|

|              |                                                                                    | LVP <sup>(1)</sup>                                                                                             | DEBUG <sup>(2)</sup>              | LPBOR              | BORV <sup>(3)</sup> | STVREN                         | _             |  |

|              |                                                                                    | bit 13                                                                                                         |                                   | ·                  |                     |                                | bit 8         |  |

| U-1          | U-1                                                                                | U-1                                                                                                            | U-1                               | U-1                | U-1                 | R/P-1                          | R/P-1         |  |

| <u> </u>     |                                                                                    |                                                                                                                |                                   | <u> </u>           |                     | WRT<                           |               |  |

| bit 7        |                                                                                    |                                                                                                                |                                   |                    |                     | , with                         | bit           |  |

|              |                                                                                    |                                                                                                                |                                   |                    |                     |                                |               |  |

| Legend:      |                                                                                    |                                                                                                                |                                   |                    |                     |                                |               |  |

| R = Reada    |                                                                                    | P = Program                                                                                                    |                                   | -                  | nented bit, read    |                                |               |  |

| '0' = Bit is | cleared                                                                            | '1' = Bit is set                                                                                               |                                   | -n = Value wh      | en blank or aft     | er Bulk Erase                  |               |  |

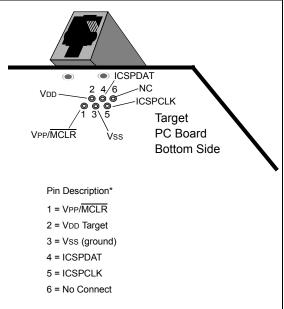

| bit 13       |                                                                                    | Itage Program                                                                                                  | ning Enable bit                   | .(1)               |                     |                                |               |  |

| bit 10       |                                                                                    | ige programmir                                                                                                 |                                   |                    |                     |                                |               |  |

|              | 0 = High-volta                                                                     | age on MCLR r                                                                                                  | nust be used fo                   | or programming     | 9                   |                                |               |  |

| bit 12       |                                                                                    | Circuit Debugge                                                                                                |                                   |                    |                     |                                |               |  |

|              | 1 = In-Circuit Debugger disabled, ICSPCLK and ICSPDAT are general purpose I/O pins |                                                                                                                |                                   |                    |                     |                                |               |  |

| bit 11       |                                                                                    | 0 = In-Circuit Debugger enabled, ICSPCLK and ICSPDAT are dedicated to the debugger<br>LPBOR: Low-Power BOR bit |                                   |                    |                     |                                |               |  |

|              |                                                                                    | er BOR is disal                                                                                                |                                   |                    |                     |                                |               |  |

|              |                                                                                    | er BOR is enat                                                                                                 |                                   |                    |                     |                                |               |  |

| bit 10       | BORV: Brown                                                                        | n-out Reset Vol                                                                                                | Itage Selection                   | bit <sup>(3)</sup> |                     |                                |               |  |

|              |                                                                                    |                                                                                                                | e (VBOR), low tr                  |                    |                     |                                |               |  |

| 1.1.0        |                                                                                    | -                                                                                                              | e (VBOR) high tr                  |                    | ed                  |                                |               |  |

| bit 9        |                                                                                    |                                                                                                                | nderflow Reset<br>flow will cause |                    |                     |                                |               |  |

|              |                                                                                    |                                                                                                                | flow will not ca                  |                    |                     |                                |               |  |

| bit 8-2      |                                                                                    | ted: Read as '                                                                                                 |                                   |                    |                     |                                |               |  |

| bit 1-0      | -                                                                                  |                                                                                                                | Self-Write Prote                  | ection bits        |                     |                                |               |  |

|              |                                                                                    | nemory (PIC16                                                                                                  |                                   |                    |                     |                                |               |  |

|              |                                                                                    | ite protection o                                                                                               |                                   |                    |                     |                                | hal           |  |

|              |                                                                                    |                                                                                                                |                                   |                    |                     | by PMCON cont<br>by PMCON cont |               |  |

|              |                                                                                    |                                                                                                                |                                   |                    |                     | by PMCON con                   |               |  |

|              | <u>4 kW Flash m</u>                                                                | nemory (PIC16                                                                                                  | LF1903 only):                     |                    |                     |                                |               |  |

|              |                                                                                    | ite protection o                                                                                               |                                   |                    |                     |                                |               |  |

|              |                                                                                    |                                                                                                                |                                   |                    |                     | by PMCON con<br>by PMCON con   |               |  |

|              |                                                                                    |                                                                                                                |                                   |                    |                     | by PMCON con                   |               |  |

| Note 1:      | The LVP bit cann                                                                   | ot be programr                                                                                                 | ned to '0' wher                   | n Programming      | mode is enter       | ed via LVP.                    |               |  |

|              | The DEBUG bit in                                                                   |                                                                                                                |                                   |                    |                     |                                | ols including |  |

|              | debuggers and p                                                                    |                                                                                                                |                                   |                    |                     |                                |               |  |

|              | 00 1                                                                               | rogrammers. r                                                                                                  |                                   |                    |                     |                                | a ⊥.          |  |

#### **REGISTER 4-2: CONFIGURATION WORD 2**

# 4.2 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 4.2.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word 1. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.3** "Write **Protection**" for more information.

#### 4.3 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word 2 define the size of the program memory block that is protected.

# 4.4 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 10.4 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16F193X/LF193X/PIC16F194X/LF194X/PIC16LF 190X Memory Programming Specification" (DS41397).

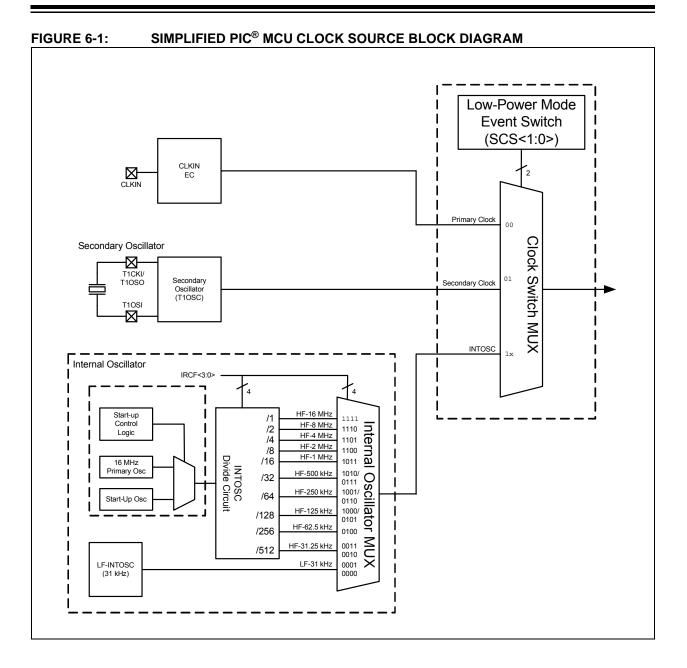

# 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. An example is: oscillator module (EC mode) circuit.

Internal clock sources are contained internally within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Word 1 to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 6.3 "Clock Switching" for more information.

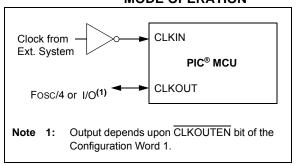

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the CLKIN input. CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Word 1:

- High power, 4-20 MHz (FOSC = 11)

- Medium power, 0.5-4 MHz (FOSC = 10)

- Low power, 0-0.5 MHz (FOSC = 01)

There is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

FIGURE 6-2: EXTERNAL CLOCK (EC) MODE OPERATION

# 6.4 Oscillator Control Registers

'1' = Bit is set

#### REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

'0' = Bit is cleared

| U-0              | R/W-0/0 | R/W-1/1         | R/W-1/1 | R/W-1/1        | U-0              | R/W-0/0          | R/W-0/0      |

|------------------|---------|-----------------|---------|----------------|------------------|------------------|--------------|

| —                |         | IRCF            | <3:0>   |                | _                | SCS              | <1:0>        |

| bit 7            |         |                 |         |                |                  |                  | bit 0        |

|                  |         |                 |         |                |                  |                  |              |

| Legend:          |         |                 |         |                |                  |                  |              |

| R = Readable b   | bit     | W = Writable    | bit     | U = Unimplen   | nented bit, read | d as '0'         |              |

| u = Bit is uncha | nged    | x = Bit is unkr | nown    | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| bit 7   | Unimplemented: Read as '0'                                  |

|---------|-------------------------------------------------------------|

| bit 6-3 | IRCF<3:0>: Internal Oscillator Frequency Select bits        |

|         | 000x = 31  kHz LF                                           |

|         | 001x = 31.25 kHz                                            |

|         | 0100 = 62.5 kHz                                             |

|         | 0101 = 125 kHz                                              |

|         | 0110 = 250 kHz                                              |

|         | 0111 = 500 kHz (default upon Reset)                         |

|         | $1000 = 125  \text{kHz}^{(1)}$                              |

|         | $1001 = 250 \text{ kHz}^{(1)}$                              |

|         | 1010 = 500 kHz <sup>(1)</sup>                               |

|         | 1011 = 1 MHz                                                |

|         | 1100 = 2 MHz                                                |

|         | 1101 = 4 MHz                                                |

|         | 1110 = 8 MHz                                                |

|         | 1111 = 16 MHz                                               |

| bit 2   | Unimplemented: Read as '0'                                  |

| bit 1-0 | SCS<1:0>: System Clock Select bits                          |

|         | 1x = Internal oscillator block                              |

|         | 01 = Secondary oscillator                                   |

|         | 00 = Clock determined by FOSC<1:0> in Configuration Word 1. |

|         | , , , , , , , , , , , , , , , , , , , ,                     |

Note 1: Duplicate frequency derived from HFINTOSC.

| R-1/q            | U-0                                                                                                                                         | R-q/q            | R-0/q              | U-0              | U-0              | R-0/0          | R-0/g        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|------------------|------------------|----------------|--------------|

| T1OSCR           | _                                                                                                                                           | OSTS             | HFIOFR             | _                | _                | LFIOFR         | HFIOFS       |

| bit 7            |                                                                                                                                             | 0010             |                    |                  |                  | Linorit        | bit C        |

|                  |                                                                                                                                             |                  |                    |                  |                  |                | bit 0        |

| Legend:          |                                                                                                                                             |                  |                    |                  |                  |                |              |

| R = Readable     | bit                                                                                                                                         | W = Writable     | bit                | U = Unimpler     | mented bit, read | 1 as '0'       |              |

| u = Bit is unch  | nanged                                                                                                                                      | x = Bit is unkr  | nown               | -n/n = Value a   | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |                                                                                                                                             | '0' = Bit is cle | ared               | q = Condition    | al               |                |              |

|                  |                                                                                                                                             |                  |                    |                  |                  |                |              |

| bit 7            | T1OSCR: Tin                                                                                                                                 | ner1 Oscillator  | Ready bit          |                  |                  |                |              |

|                  | If T1OSCEN                                                                                                                                  |                  |                    |                  |                  |                |              |

|                  | 1 = Timer1 oscillator is ready                                                                                                              |                  |                    |                  |                  |                |              |

|                  | 0 = Timer1 oscillator is not ready                                                                                                          |                  |                    |                  |                  |                |              |

|                  | If T1OSCEN = 0:<br>1 = Timer1 clock source is always ready                                                                                  |                  |                    |                  |                  |                |              |

| bit 6            |                                                                                                                                             | ted: Read as '   |                    |                  |                  |                |              |

| bit 5            | -                                                                                                                                           | ator Start-up Ti |                    | hit              |                  |                |              |

| bit 0            |                                                                                                                                             | •                |                    |                  |                  |                |              |

|                  | <ul> <li>1 = Running from the external clock source (EC)</li> <li>0 = Running from an internal oscillator (FOSC&lt;1:0&gt; = 00)</li> </ul> |                  |                    |                  |                  |                |              |

| bit 4            | HFIOFR: High                                                                                                                                | n-Frequency Ir   | ternal Oscillat    | or Ready bit     |                  |                |              |

|                  | 1 = HFINTOS                                                                                                                                 | SC is ready      |                    |                  |                  |                |              |

|                  | 0 = HFINTOSC is not ready                                                                                                                   |                  |                    |                  |                  |                |              |

| bit 3-2          | Unimplemen                                                                                                                                  | ted: Read as '   | 0'                 |                  |                  |                |              |

| bit 1            | LFIOFR: Low-Frequency Internal Oscillator Ready bit                                                                                         |                  |                    |                  |                  |                |              |

|                  | 1 = LFINTOSC is ready                                                                                                                       |                  |                    |                  |                  |                |              |

|                  |                                                                                                                                             | SC is not ready  |                    |                  |                  |                |              |

| bit 0            | •                                                                                                                                           | n-Frequency In   |                    |                  |                  |                |              |

|                  |                                                                                                                                             |                  |                    | and is driving   |                  |                |              |

|                  | 0 = HFINTOS                                                                                                                                 | SC 16 MHz os     | cillator is not st | able, the Start- | up Oscillator is | driving IN FOS | C            |

# REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

# TABLE 6-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6   | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|---------|-------|--------|---------|--------|--------|--------|---------------------|

| OSCCON  |        |         | IRCF  | <3:0>  |         | _      | SCS    | <1:0>  | 53                  |

| OSCSTAT | T1OSCR | _       | OSTS  | HFIOFR | _       | _      | LFIOFR | HFIOFS | 54                  |

| T1CON   | TMR10  | CS<1:0> | T1CKP | S<1:0> | T1OSCEN | T1SYNC |        | TMR10N | 130                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 6-3:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | _       | _       | _        | _        | CLKOUTEN | BOREI    | N<1:0>  | —       | 24                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | <1:0>    | _        | FOSC    | <1:0>   | 34                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|-------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF | INTF    | IOCIF  | 60                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   |        | PS<2:0> |        | 121                 |

| PIE1       | TMR1GIE | ADIE   | _      | _      | _     | _      | _       | TMR1IE | 61                  |

| PIE2       | _       | _      | _      | _      | _     | LCDIE  | _       | —      | 62                  |

| PIR1       | TMR1GIF | ADIF   | _      | _      | _     | _      | _       | TMR1IF | 63                  |

| PIR2       |         | _      | _      | _      |       | LCDIF  |         | _      | 64                  |

TABLE 7-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

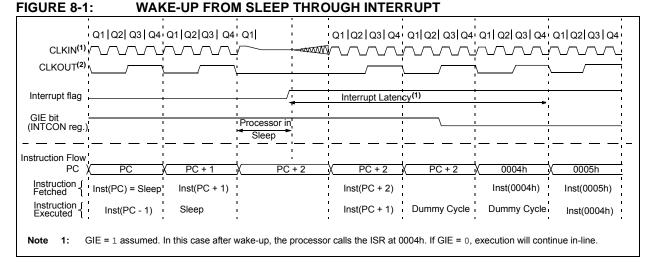

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

# TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|--------|------------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE   | IOCIE      | TMR0IF | INTF   | IOCIF  | 60                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1 | IOCBF0 | 101                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1 | IOCBN0 | 101                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1 | IOCBP0 | 101                 |

| PIE1   | TMR1GIE | ADIE   | _      | —      | _          | —      | _      | TMR1IE | 61                  |

| PIE2   | —       | _      | _      | —      | _          | LCDIE  | _      | —      | 62                  |

| PIR1   | TMR1GIF | ADIF   | _      | —      | _          | —      | _      | TMR1IF | 63                  |

| PIR2   | —       | _      | _      | —      | _          | LCDIF  | _      | —      | 64                  |

| STATUS | _       | _      | _      | TO     | PD         | Z      | DC     | С      | 16                  |

| WDTCON | _       |        |        | ١      | NDTPS<4:0> | >      |        | SWDTEN | 70                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

# 9.6 Watchdog Control Register

#### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Resets |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -m/n = Value at POR and BOR/Value at all other         1' = Bit is set       '0' = Bit is cleared       -m/n = Value at POR and BOR/Value at all other         Dit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         Dit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         Dit 5-1       WDTPS       WDTPS       -m/n = Value at POR and BOR/Value at all other         Dit 5-1       WDTPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -m/n = Value at POR and BOR/Value at all other         1' = Bit is set       '0' = Bit is cleared       -m/n = Value at POR and BOR/Value at all other         bit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         bit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         bit 5-1       WDTPS       WDTPS       Watchdog Timer Period Select bits <sup>(1)</sup> Bit Value = Prescale Rate       00000 = 1:32 (Interval 1 ms nominal)       00010 = 1:266 (Interval 2 ms nominal)         00010 = 1:28 (Interval 4 ms nominal)       00011 = 1:256 (Interval 8 ms nominal)       00101 = 1:204 (Interval 32 ms nominal)         0010 = 1:2048 (Interval 16 ms nominal)       00110 = 1:2048 (Interval 32 ms nominal)       00111 = 1:4096 (Interval 128 ms nominal)         0110 = 1:2048 (Interval 512 ms nominal)       01001 = 1:16384 (Interval 512 ms nominal)       01001 = 1:16384 (Interval 512 ms nominal)         0101 = 1:16384 (Interval 151 ms nominal)       0101 = 1:65536 (Interval 2s nominal)       0101 = 1:65536 (Interval 4s nominal)         0101 = 1:132768 (Interval 2s nominal)       0101 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)       0101 = 1:131072 (2 <sup>17</sup> ) | Resets |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -m/n = Value at POR and BOR/Value at all other         1' = Bit is set       '0' = Bit is cleared       -m/n = Value at POR and BOR/Value at all other         bit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         bit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         bit 5-1       WDTPS       WDTPS       Watchdog Timer Period Select bits <sup>(1)</sup> Bit Value = Prescale Rate       00000 = 1:32 (Interval 1 ms nominal)       00010 = 1:266 (Interval 2 ms nominal)         00010 = 1:28 (Interval 4 ms nominal)       00011 = 1:256 (Interval 8 ms nominal)       00101 = 1:204 (Interval 32 ms nominal)         0010 = 1:2048 (Interval 16 ms nominal)       00110 = 1:2048 (Interval 32 ms nominal)       00111 = 1:4096 (Interval 128 ms nominal)         0110 = 1:2048 (Interval 512 ms nominal)       01001 = 1:16384 (Interval 512 ms nominal)       01001 = 1:16384 (Interval 512 ms nominal)         0101 = 1:16384 (Interval 151 ms nominal)       0101 = 1:65536 (Interval 2s nominal)       0101 = 1:65536 (Interval 4s nominal)         0101 = 1:132768 (Interval 2s nominal)       0101 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)       0101 = 1:131072 (2 <sup>17</sup> ) | Resets |

| u = Bit is unchanged       x = Bit is unknown       -m/n = Value at POR and BOR/Value at all other         1' = Bit is set       '0' = Bit is cleared       -m/n = Value at POR and BOR/Value at all other         0't 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         obit 7-6       Unimplemented: Read as '0'       -m/n = Value at POR and BOR/Value at all other         obit 5-1       WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup> Bit Value = Prescale Rate         00000 = 1:32 (Interval 1 ms nominal)       00010 = 1:428 (Interval 2 ms nominal)       00011 = 1:256 (Interval 4 ms nominal)         00010 = 1:512 (Interval 4 ms nominal)       00101 = 1:1024 (Interval 32 ms nominal)       00101 = 1:1024 (Interval 32 ms nominal)         00110 = 1:2048 (Interval 64 ms nominal)       0011 = 1:4096 (Interval 128 ms nominal)       00101 = 1:2048 (Interval 51 ms nominal)         01010 = 1:2048 (Interval 51 ms nominal)       0101 = 1:16384 (Interval 51 ms nominal)       0101 = 1:16384 (Interval 51 ms nominal)         0101 = 1:65536 (Interval 1s nominal)       0101 = 1:65536 (Interval 2s nominal)       0101 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)         0100 = 1:131072 (2 <sup>17</sup> )       0111 = 1:4096 (Interval 4s nominal)       0100 = 1:131072 (2 <sup>17</sup> )                                                              | Resets |

| 1' = Bit is set'0' = Bit is clearedbit 7-6Unimplemented: Read as '0'bit 5-1WDTPS<4:0>: Watchdog Timer Period Select bits(1)Bit Value = Prescale Rate $00000 = 1:32$ (Interval 1 ms nominal) $0001 = 1:64$ (Interval 2 ms nominal) $00010 = 1:128$ (Interval 4 ms nominal) $00010 = 1:256$ (Interval 8 ms nominal) $00100 = 1:512$ (Interval 16 ms nominal) $00101 = 1:1024$ (Interval 32 ms nominal) $00110 = 1:2048$ (Interval 64 ms nominal) $00111 = 1:4096$ (Interval 128 ms nominal) $00101 = 1:16384$ (Interval 512 ms nominal) $01001 = 1:16384$ (Interval 512 ms nominal) $01010 = 1:32768$ (Interval 1s nominal) $01011 = 1:65536$ (Interval 2s nominal) $01011 = 1:65536$ (Interval 2s nominal) $01011 = 1:65536$ (Interval 2s nominal) $01010 = 1:327768$ (Interval 2s nominal) $01010 = 1:31072$ (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Resets |

| bit 7-6 Unimplemented: Read as '0'<br>bit 5-1 WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup><br>Bit Value = Prescale Rate<br>00000 = 1:32 (Interval 1 ms nominal)<br>0001 = 1:64 (Interval 2 ms nominal)<br>00100 = 1:128 (Interval 4 ms nominal)<br>0011 = 1:256 (Interval 8 ms nominal)<br>00100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1224 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>00111 = 1:4096 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01011 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| bit 5-1<br>WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup><br>Bit Value = Prescale Rate<br>00000 = 1:32 (Interval 1 ms nominal)<br>00011 = 1:64 (Interval 2 ms nominal)<br>00010 = 1:128 (Interval 4 ms nominal)<br>00101 = 1:256 (Interval 4 ms nominal)<br>00100 = 1:512 (Interval 6 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01010 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01011 = 1:65536 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01011 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| bit 5-1<br>WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup><br>Bit Value = Prescale Rate<br>00000 = 1:32 (Interval 1 ms nominal)<br>00011 = 1:64 (Interval 2 ms nominal)<br>00010 = 1:128 (Interval 4 ms nominal)<br>00101 = 1:256 (Interval 4 ms nominal)<br>00100 = 1:512 (Interval 6 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01010 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01011 = 1:65536 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01011 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| Bit Value = Prescale Rate<br>00000 = 1:32 (Interval 1 ms nominal)<br>00011 = 1:64 (Interval 2 ms nominal)<br>00010 = 1:128 (Interval 4 ms nominal)<br>00011 = 1:256 (Interval 8 ms nominal)<br>00100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1024 (Interval 16 ms nominal)<br>00101 = 1:2048 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01001 = 1:16384 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01010 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 00000 = 1:32 (Interval 1 ms nominal)<br>00001 = 1:64 (Interval 2 ms nominal)<br>00010 = 1:128 (Interval 4 ms nominal)<br>00011 = 1:256 (Interval 8 ms nominal)<br>00100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01100 = 1:131072 (217) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| 00001 = 1:64 (Interval 2 ms nominal)<br>00010 = 1:128 (Interval 4 ms nominal)<br>00011 = 1:256 (Interval 8 ms nominal)<br>00100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01011 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>$01100 = 1:131072 (2^{17}) (Interval 4s nominal)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 00010 = 1:128 (Interval 4 ms nominal)<br>00011 = 1:256 (Interval 8 ms nominal)<br>00100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01010 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01011 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| 00011 = 1:256 (Interval 8 ms nominal)<br>0100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01000 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 00100 = 1:512 (Interval 16 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>$01011 = 1:131072$ ( $2^{17}$ ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 00101 = 1:1024 (Interval 32 ms nominal)<br>00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal)<br>01001 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 00110 = 1:2048 (Interval 64 ms nominal)<br>00111 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| 00111 = 1:4096 (Interval 128 ms nominal)<br>01000 = 1:8192 (Interval 256 ms nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| 01001 = 1:16384 (Interval 512 ms nominal)<br>01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 01010 = 1:32768 (Interval 1s nominal)<br>01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| 01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| $01100 = 1.131072 (2 ) (Interval 48 nominal) 01101 = 1.262144 (2^{18}) (Interval 88 nominal)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 01110 = 1:524288 (2 <sup>19</sup> ) (Interval 16s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 01111 = 1:1048576 (2 <sup>20</sup> ) (Interval 32s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

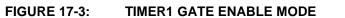

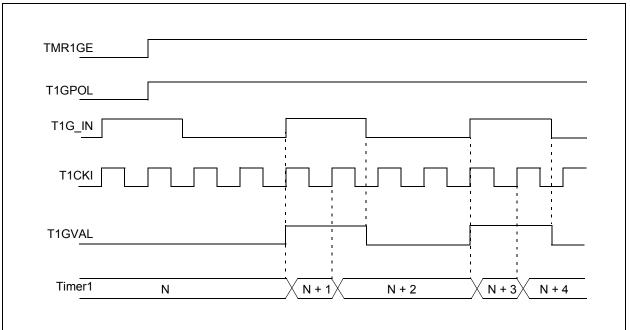

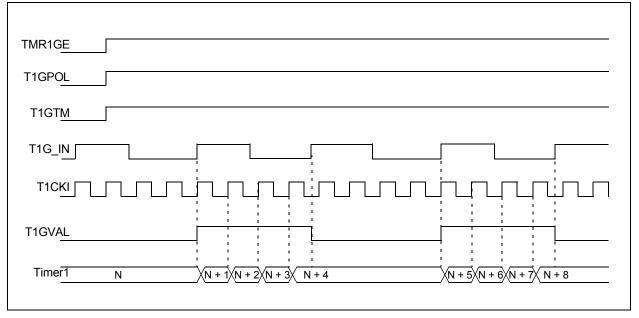

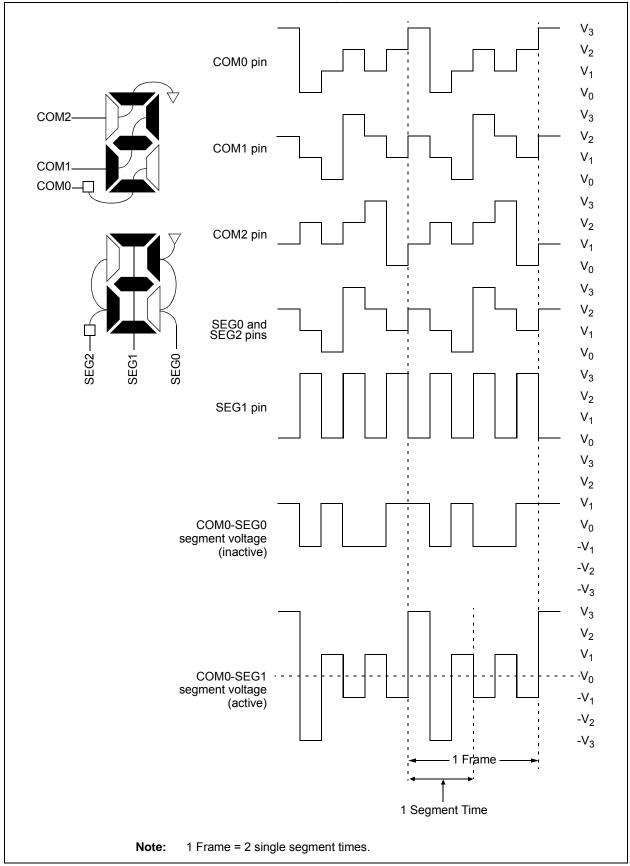

| 10000 = 1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal)<br>10001 = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |