Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | SC140 Core                                                              |

| Interface               | DSI, Ethernet, RS-232                                                   |

| Clock Rate              | 400MHz                                                                  |

| Non-Volatile Memory     | External                                                                |

| On-Chip RAM             | 1.436MB                                                                 |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.20V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 431-BFBGA, FCBGA                                                        |

| Supplier Device Package | 431-FCPBGA (20x20)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmsc8126tmp6400 |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|  | Table 4. | DMA Controller |

|--|----------|----------------|

|--|----------|----------------|

| Feature                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Multi-Channel<br>DMA Controller | <ul> <li>16 time-multiplexed unidirectional channels.</li> <li>Services up to four external peripherals.</li> <li>Supports DONE or DRACK protocol on two external peripherals.</li> <li>Each channel group services 16 internal requests generated by eight internal FIFOs. Each FIFO generates: <ul> <li>—A watermark request to indicate that the FIFO contains data for the DMA to empty and write to the destination.</li> <li>—A hungry request to indicate that the FIFO can accept more data.</li> </ul> </li> <li>Priority-based time-multiplexing between channels using 16 internal priority levels.</li> <li>A flexible channel configuration: <ul> <li>—All channels support all features.</li> <li>—All channels connect to the system bus or local bus.</li> </ul> </li> <li>Flyby transfers in which a single data access is transferred directly from the source to the destination without using a DMA FIFO.</li> </ul> |  |  |  |

| Table 5. | Serial | Interfaces |

|----------|--------|------------|

|----------|--------|------------|

| Feature                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Time-Division<br>Multiplexing<br>(TDM) | <ul> <li>Up to four independent TDM modules, each with the following features:</li> <li>Optional operating configurations: <ul> <li>—Totally independent receive and transmit channels, each having one data line, one clock line, and one frame sync line.</li> <li>—Four data lines with one clock and one frame sync shared among the transmit and receive lines.</li> <li>Connects gluelessly to most T1/E1 framers as well as to common buses such as the ST-BUS.</li> <li>Hardware A-law/µ-law conversion.</li> <li>Up to 62.5 Mbps per TDM (62.5 MHz bit clock if one data line is used, 31.25 MHz if two data lines are used, 15.63 MHz if four data lines are used).</li> <li>Up to 256 channels.</li> <li>Up to 16 MB per channel buffer (granularity 8 bytes), where A/µ law buffer size is double (granularity 16 byte).</li> <li>Receive buffers share one global write offset pointer that is written to the same offset relative to their start address.</li> <li>Transmit buffers share one global read offset pointer that is read from the same offset relative to their start address.</li> <li>All channels share the same word size.</li> <li>Two programmable receive and two programmable transmit threshold levels with interrupt generation that can be used, for example, to implement double buffering.</li> <li>Each channel can be programmed to be active or inactive.</li> <li>2., 4., 8., or 16-bit channels are stored in the internal memory as 2-, 4-, 8-, or 16-bit channels, respectively.</li> <li>The TDM transmitter sync signal (TxTSYN) can be configured as either input or output.</li> <li>Frame sync and data signals can be programmed to be sampled either on the rising edge or on the falling edge of the clock.</li> <li>Frame sync and be programmed as active low or active high.</li> <li>Selectable delay (0–3 bits) between the frame sync signal and the beginning of the frame.</li> </ul> </li> </ul> |  |  |

| Table 5. | Serial Interfaces | (Continued) |

|----------|-------------------|-------------|

|----------|-------------------|-------------|

| Feature                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ethernet<br>Controller | <ul> <li>Complies with IEEE Std 802® including Std. 802.3™, 802.3u™, 802.3x™, and 802.3ac™.</li> <li>Three Ethernet physical interfaces:         <ul> <li>10/100 Mbps MII.</li> <li>10/100 Mbps MII.</li> <li>10/100 Mbps SMII.</li> <li>Full and half-duplex support.</li> </ul> </li> <li>Full and half-duplex support.</li> <li>Full-and half-duplex support.</li> <li>Full-and half-duplex support.</li> <li>Out-of-sequence transmit queue for initiating flow-control.</li> <li>Programmable maximum frame length supports jumbo frames (up to 9.6 K) and virtual local area network (VLAN) tags and priority.</li> <li>Retransmission from transmit FIPO following a collision.</li> <li>CRC generation and verification of inbound/outbound packets.</li> <li>Address recognition:             <ul> <li>Each exact match can be programmed to be accepted or rejected.</li> <li>Broadcast address (acceptriject).</li> <li>Exact match 48-bit individual (unicast) addresse.</li> <li>Hash (256-bit hash) check of group (muticast) addresses.</li> <li>Promiscuous mode.</li> </ul> </li> <li>Pattern matching:         <ul> <li>Up to 16 unique 4-byte patterns.</li> <li>Programmable pattern size in 4-byte increments up to 64 bytes.</li> <li>Accept or reject frames if a match is detected.</li> <li>Up to 16 unique 4-byte pattern matches.</li> <li>Programmable pattern size in 4-byte increments up to 64 bytes.</li> <li>Accept or reject frames if a match is detected.</li> <li>Up to 16 unique 4-byte pattern size in 4-byte increments up to 64 bytes.</li> <li>Programmable pattern size in 4-byte increments up to 64 bytes.</li> <li>Programmable pattern size in 4-byte increments up to 64 bytes.</li> <li>Bertion with expansion or replacement for transmit frames; VLAN tag insertio</li></ul></li></ul> |  |  |

# 1.4 Direct Slave Interface, System Bus, Ethernet, and Interrupt Signals

The direct slave interface (DSI) is combined with the system bus because they share some common signal lines. Individual assignment of a signal to a specific signal line is configured through internal registers. **Table 1-5** describes the signals in this group.

**Note:** Although there are fifteen interrupt request (IRQ) connections to the core processors, there are multiple external lines that can connect to these internal signal lines. After reset, the default configuration enables only IRQ[1–7], but includes two input lines each for IRQ[1–3] and IRQ7. The designer must select one line for each required interrupt and reconfigure the other external signal line or lines for alternate functions. Additional alternate IRQ lines and IRQ[8–15] are enabled through the GPIO signal lines.

| Signal Name | Туре          | Description                                                                                                                                            |  |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HD0         | Input/ Output | Host Data Bus 0<br>Bit 0 of the DSI data bus.                                                                                                          |  |

| SWTE        | Input         | Software Watchdog Timer Disable.<br>It is sampled on the rising edge of PORESET signal.                                                                |  |

| HD1         | Input/ Output | Host Data Bus 1<br>Bit 1 of the DSI data bus.                                                                                                          |  |

| DSISYNC     | Input         | <b>DSI Synchronous</b><br>Distinguishes between synchronous and asynchronous operation of the DSI. It is sampled on the rising edge of PORESET signal. |  |

| HD2         | Input/ Output | Host Data Bus 2<br>Bit 2 of the DSI data bus.                                                                                                          |  |

| DSI64       | Input         | DSI 64<br>Defines the width of the DSI and SYSTEM Data buses. It is sampled on the rising edge of PORESET signal.                                      |  |

| HD3         | Input/ Output | Host Data Bus 3<br>Bit 3 of the DSI data bus.                                                                                                          |  |

| MODCK1      | Input         | <b>Clock Mode 1</b><br>Defines the clock frequencies. It is sampled on the rising edge of PORESET signal.                                              |  |

| HD4         | Input/ Output | Host Data Bus 4<br>Bit 4 of the DSI data bus.                                                                                                          |  |

| MODCK2      | Input         | <b>Clock Mode 2</b><br>Defines the clock frequencies. It is sampled on the rising edge of PORESET signal.                                              |  |

| HD5         | Input/ Output | Host Data Bus 5<br>Bit 5 of the DSI data bus.                                                                                                          |  |

| CNFGS       | Input         | <b>Configuration Source</b><br>One signal out of two that indicates reset configuration mode. It is sampled on the rising edge of<br>PORESET signal.   |  |

| HD[6–31]    | Input/ Output | Host Data Bus 6–31<br>Bits 6–31 of the DSI data bus.                                                                                                   |  |

| Table 1-5. | DSI, System Bus, Ethernet, and Interrupt Signals |

|------------|--------------------------------------------------|

|            | , _ <b>,</b> _ <b>,</b>                          |

### Signals/Connections

| Signal Name | Туре          | Description                                                                                                                                                       |  |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HD46        | Input/ Output | Host Data Bus 46<br>Bit 46 of the DSI data bus.                                                                                                                   |  |

| D46         | Input/ Output | System Bus Data 46<br>For write transactions, the bus master drives valid data on this line. For read transactions, the slave drives<br>valid data on this bus.   |  |

| ETHTXD0     | Output        | Ethernet Transmit Data 0<br>In MII and RMII modes, bit 0 of the Ethernet transmit data.                                                                           |  |

| HD47        | Input/ Output | Host Data Bus 47<br>Bit 47 of the DSI data bus.                                                                                                                   |  |

| D47         | Input/ Output | System Bus Data 47<br>For write transactions, the bus master drives valid data on this line. For read transactions, the slave drives<br>valid data on this bus.   |  |

| ETHTXD1     | Output        | Ethernet Transmit Data 1<br>In MII and RMII modes, bit 1 of the Ethernet transmit data.                                                                           |  |

| HD48        | Input/ Output | Host Data Bus 48<br>Bit 48 of the DSI data bus.                                                                                                                   |  |

| D48         | Input/ Output | System Bus Data 48<br>For write transactions, the bus master drives valid data on this line. For read transactions, the slave drives<br>valid data on this bus.   |  |

| ETHTXD2     | Output        | Ethernet Transmit Data 2<br>In MII mode only, bit 2 of the Ethernet transmit data.                                                                                |  |

| Reserved    | Input         | In RMII mode, this signal is reserved and can be left unconnected.                                                                                                |  |

| HD49        | Input/ Output | Host Data Bus 49<br>Bit 49 of the DSI data bus.                                                                                                                   |  |

| D49         | Input/ Output | System Bus Data 49<br>For write transactions, the bus master drives valid data on this line. For read transactions, the slave drives<br>valid data on this bus.   |  |

| ETHTXD3     | Output        | Ethernet Transmit Data 3<br>In MII mode only, bit 3 of the Ethernet transmit data.                                                                                |  |

| Reserved    | Input         | In RMII mode, this signal is reserved and can be left unconnected.                                                                                                |  |

| HD[50–53]   | Input/ Output | Host Data Bus 50–53<br>Bits 50–53 of the DSI data bus.                                                                                                            |  |

| D[50–53]    | Input/ Output | System Bus Data 50–53<br>For write transactions, the bus master drives valid data on this bus. For read transactions, the slave drives<br>valid data on this bus. |  |

| Reserved    | Input         | If the Ethernet port is enabled and multiplexed with the DSI/System bus, these signals are reserved and can be left unconnected.                                  |  |

| HD54        | Input/ Output | Host Data Bus 54<br>Bit 54 of the DSI data bus.                                                                                                                   |  |

| D54         | Input/ Output | System Bus Data 54<br>For write transactions, the bus master drives valid data on this line. For read transactions, the slave drives<br>valid data on this bus.   |  |

| ETHTX_EN    | Output        | Ethernet Transmit Data Enable<br>In MII and RMII modes, indicates that the transmit data is valid.                                                                |  |

### Table 1-5. DSI, System Bus, Ethernet, and Interrupt Signals (Continued)

### Direct Slave Interface, System Bus, Ethernet, and Interrupt Signals

| Table 1-5. | DSI, System Bus, Ethernet, and Interrupt Signals (Continent of Continent of Cont | ued) |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Signal Name | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HWBS[4–7]   | Input         | Host Write Byte Strobes (In Asynchronous dual mode)<br>One bit per byte is used as a strobe for host write accesses.                                                                                                                                                                                                                                                                                                         |  |

| HDBS[4-7]   | Input         | Host Data Byte Strobe (in Asynchronous single mode)<br>One bit per byte is used as a strobe for host read or write accesses                                                                                                                                                                                                                                                                                                  |  |

| HWBE[4-7]   | Input         | Host Write Byte Enable (In Synchronous dual mode)<br>One bit per byte is used to indicate a valid data byte for host write accesses.                                                                                                                                                                                                                                                                                         |  |

| HDBE[4-7]   | Input         | Host Data Byte Enable (in Synchronous single mode)<br>One bit per byte is used as a strobe enable for host read or write accesses                                                                                                                                                                                                                                                                                            |  |

| PWE[4-7]    | Output        | System Bus Write Enable<br>Outputs of the bus general-purpose chip-select machine (GPCM). These signals select byte lanes for<br>write operations.                                                                                                                                                                                                                                                                           |  |

| PSDDQM[4-7] | Output        | System Bus SDRAM DQM<br>From the SDRAM control machine. These signals select specific byte lanes of SDRAM devices.                                                                                                                                                                                                                                                                                                           |  |

| PBS[4-7]    | Output        | System Bus UPM Byte Select<br>From the UPM in the memory controller, these signals select specific byte lanes during memory<br>operations. The timing of these signals is programmed in the UPM. The actual driven value depends on<br>the address and size of the transaction and the port size of the accessed device.                                                                                                     |  |

| HRDS        | Input         | Host Read Data Strobe (In Asynchronous dual mode)<br>Used as a strobe for host read accesses.                                                                                                                                                                                                                                                                                                                                |  |

| HRW         | Input         | Host Read/Write Select (in Asynchronous/Synchronous single mode)<br>Host read/write select.                                                                                                                                                                                                                                                                                                                                  |  |

| HRDE        | Input         | Host Read Data Enable (In Synchronous dual mode)<br>Indicates valid data for host read accesses.                                                                                                                                                                                                                                                                                                                             |  |

| HBRST       | Input         | Host Burst<br>The host asserts this signal to indicate that the current transaction is a burst transaction in synchronous<br>mode only.                                                                                                                                                                                                                                                                                      |  |

| HDST[0-1]   | Input         | Host Data Structure 0–1<br>Defines the data structure of the host access in DSI little-endian mode.                                                                                                                                                                                                                                                                                                                          |  |

| HA[9–10]    |               | Host Bus Address 9–10<br>Used by an external host to access the internal address space.                                                                                                                                                                                                                                                                                                                                      |  |

| HCS         | Input         | Host Chip Select DSI chip select. The DSI is accessed only if $\overline{\text{HCS}}$ is asserted and HCID[0–3] matches the Chip_ID.                                                                                                                                                                                                                                                                                         |  |

| HBCS        | Input         | Host Broadcast Chip Select<br>DSI chip select for broadcast mode. Enables more than one DSI to share the same host chip-select signal<br>for broadcast write accesses.                                                                                                                                                                                                                                                       |  |

| HTA         | Output        | Host Transfer Acknowledge<br>Upon a read access, indicates to the host when the data on the data bus is valid. Upon a write access,<br>indicates to the host that the data on the data bus was written to the DSI write buffer.                                                                                                                                                                                              |  |

| HCLKIN      | Input         | Host Clock Input<br>Host clock signal for DSI synchronous mode.                                                                                                                                                                                                                                                                                                                                                              |  |

| A[0-31]     | Input/ Output | Address Bus<br>When the MSC8126 is in external master bus mode, these signals function as the system address bus.<br>The MSC8126 drives the address of its internal bus masters and responds to addresses generated by<br>external bus masters. When the MSC8126 is in internal master bus mode, these signals are used as<br>address lines connected to memory devices and are controlled by the MSC8126 memory controller. |  |

| тто         | Input/ Output | Bus Transfer Type 0<br>The bus master drives this signals during the address tenure to specify the type of the transaction.                                                                                                                                                                                                                                                                                                  |  |

| HA7         |               | Host Bus Address 7<br>Used by an external host to access the internal address space.                                                                                                                                                                                                                                                                                                                                         |  |

### Signals/Connections

| Signal Name                                                                                                               |  | Туре                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------|--|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ7                                                                                                                      |  | Input                                                                                                                          | Interrupt Request 7<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INT_OUT                                                                                                                   |  | Output                                                                                                                         | Interrupt Output<br>This output indicates whether an unmasked interrupt is pending in the MSC8126 internal interrupt<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2. When used as the<br>set of Bus Reques<br>EXT_BR3/EXT_B0<br>is not a MSC8126<br>chapter in the MS0<br>defined by EXT_xx |  | en used as the<br>of Bus Reques<br>_BR3/EXT_BC<br>ot a MSC8126<br>oter in the <i>MSC</i><br>ned by EXT_xx<br>e a dual function | controller.<br>face Unit (SIU) chapter in the <i>MSC8126 Reference Manual</i> for details on how to configure these signals<br>is control arbiter, the MSC8126 can support up to three external bus masters. Each master uses its own<br>Bus Grant, and Data Bus Grant signals (BR/BG/DBG, EXT_BR2/EXT_BG2/EXT_DBG2, and<br>/EXT_DBG3). Each of these signal sets must be configured to indicate whether the external master is or<br>aster device. See the Bus Configuration Register (BCR) description in the System Interface Unit (SIU)<br><i>126 Reference Manual</i> for details on how to configure these signals. The second and third set of signals is<br>to indicate that they can only be used with external master devices. The first set of signals (BR/BG/DBG<br>When the MSC8126 is not the bus arbiter, it uses these signals (BR/BG/DBG) to obtain master control of |

### Table 1-5. DSI, System Bus, Ethernet, and Interrupt Signals (Continued)

# 1.5 Memory Controller Signals

Refer to the Memory Controller chapter in the *MSC8126 Reference Manual* for details on configuring these signals.

| Signal Name | Туре          | Description                                                                                                                                                                                                                                                                                                               |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCTL0       | Output        | System Bus Buffer Control 0<br>Controls buffers on the data bus. Usually used with $\overline{\text{BCTL1}}$ . The exact function of this signal is defined by the value of SIUMCR[BCTLC].                                                                                                                                |

| BCTL1       | Output        | System Bus Buffer Control 1<br>Controls buffers on the data bus. Usually used with $\overline{\text{BCTL0}}$ . The exact function of this signal is defined by<br>the value of SIUMCR[BCTLC].                                                                                                                             |

| CS5         | Output        | System and Local Bus Chip Select 5<br>Enables specific memory devices or peripherals connected to MSC8126 buses.                                                                                                                                                                                                          |

| BM[0–2]     | Input         | <b>Boot Mode 0–2</b><br>Defines the boot mode of the MSC8126. This signal is sampled on PORESET deassertion.                                                                                                                                                                                                              |

| TC[0-2]     | Input/ Output | <b>Transfer Code 0–2</b><br>The bus master drives these signals during the address tenure to specify the type of the code.                                                                                                                                                                                                |

| BNKSEL[0-2] | Output        | Bank Select 0–2<br>Selects the SDRAM bank when the MSC8126 is in 60x-compatible bus mode.                                                                                                                                                                                                                                 |

| ALE         | Output        | Address Latch Enable<br>Controls the external address latch used in an external master bus.                                                                                                                                                                                                                               |

| PWE[0-3]    | Output        | System Bus Write Enable<br>Outputs of the bus general-purpose chip-select machine (GPCM). These signals select byte lanes for<br>write operations.                                                                                                                                                                        |

| PSDDQM[0-3] | Output        | System Bus SDRAM DQM<br>From the SDRAM control machine. These signals select specific byte lanes of SDRAM devices.                                                                                                                                                                                                        |

| PBS[0-3]    | Output        | <b>System Bus UPM Byte Select</b><br>From the UPM in the memory controller, these signals select specific byte lanes during memory operations. The timing of these signals is programmed in the UPM. The actual driven value depends on the address and size of the transaction and the port size of the accessed device. |

| <b>Table 1-6.</b> Memory Controller Signals |

|---------------------------------------------|

|---------------------------------------------|

| Table 1-7. GPIO, TDM, UART, Ethernet, and Timer Signals (Con |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| Signal Name | Туре          | Description                                                                                                                                                                                                                                         |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO11      | Input/ Output | <b>General-Purpose Input Output 11</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.               |

| TDM2TDAT    | Input/ Output | <b>TDM2 Serial Transmitter Data</b><br>The transmit data signal for TDM 2. As an output, this can be the DATA_D data signal for TDM 2. For<br>configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation. |

| IRQ9        | Input         | Interrupt Request 9<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                             |

| ETHRX_ER    | Input         | Ethernet Receive Data Error<br>In MII and RMII modes, indicates a receive data error.                                                                                                                                                               |

| ETHTXD      | Output        | Ethernet Transmit Data<br>In SMII, used as the Ethernet transmit data line.                                                                                                                                                                         |

| GPIO12      | Input/ Output | General-Purpose Input Output 12<br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.                      |

| TDM2RSYN    | Input/ Output | <b>TDM2 Receive Frame Sync</b><br>The receive sync signal for TDM 2. As an input, this can be the DATA_B data signal for TDM 2. For<br>configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation.        |

| IRQ10       | Input         | Interrupt Request 10<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                            |

| ETHRXD1     | Input         | Ethernet Receive Data 1<br>Bit 1 of the Ethernet receive data (MII and RMII mode).                                                                                                                                                                  |

| ETHSYNC     | Output        | Ethernet Sync Signal<br>In SMII mode, this is the Ethernet sync signal input.                                                                                                                                                                       |

| GPIO13      | Input/ Output | <b>General-Purpose Input Output 13</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.               |

| TDM2RCLK    | Input/ Output | <b>TDM2 Receive Clock</b><br>The receive clock signal for TDM 2. As an input, this can be the DATA_C data signal for TDM 2. For configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation.               |

| IRQ11       | Input         | Interrupt Request 11<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                            |

| ETHMDC      | Output        | Ethernet Management Clock<br>Used for the MDIO reference clock for MII, RMII, and SMII modes.                                                                                                                                                       |

| Table 1-7. | GPIO, TDM | , UART, Ethernet, | and Timer Signals | (Continued) |

|------------|-----------|-------------------|-------------------|-------------|

|------------|-----------|-------------------|-------------------|-------------|

| Signal Name | Туре          | Description                                                                                                                                                                                                                           |  |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPIO18      | Input/ Output | <b>General-Purpose Input Output 18</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model. |  |

| TDM1RSYN    | Input/ Output | <b>TDM1 Receive Frame Sync</b><br>The receive sync signal for TDM 1. As an input, this can be the DATA_B data signal for TDM 1. For<br>configuration details, refer to the <i>MSC8126 Reference Manual</i> .                          |  |

| DREQ2       | Input         | DMA Request 1<br>Used by an external peripheral to request DMA service.                                                                                                                                                               |  |

| GPIO19      | Input/ Output | <b>General-Purpose Input Output 19</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model. |  |

| TDM1RCLK    | Input/ Output | <b>TDM1 Receive Clock</b><br>The receive clock signal for TDM 1. As an input, this can be the DATA_C data signal for TDM 1. For configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation. |  |

| DACK2       | Output        | <b>DMA Acknowledge 2</b><br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                      |  |

| GPIO20      | Input/ Output | General-Purpose Input Output 20<br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.         |  |

| TDM1RDAT    | Input/ Output | <b>TDM1 Serial Receiver Data</b><br>The receive data signal for TDM 1. As an input, this can be the DATA_A data signal for TDM 1. For<br>configuration details, refer to the <i>MSC8126 Reference Manual</i> .                        |  |

| GPIO21      | Input/ Output | <b>General-Purpose Input Output 21</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model. |  |

| TDM0TSYN    | Input/ Output | <b>TDM0 Transmit frame Sync</b><br>Transmit Frame Sync for TDM 0.                                                                                                                                                                     |  |

| GPIO22      | Input/ Output | <b>General-Purpose Input Output 22</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.     |  |

| TDM0TCLK    | Input         | TDM 0 Transmit Clock<br>Transmit Clock for TDM 0.                                                                                                                                                                                     |  |

| DONE2       | Input/ Output | <b>DMA Done 2</b><br>Signifies that the channel must be terminated. If the DMA generates DONE, the channel handling this peripheral is inactive. As an input to the DMA, DONE closes the channel much like a normal channel closing.  |  |

|             |               | <b>Note:</b> See the <i>MSC8126 Reference Manual</i> chapters on DMA and GPIO for information on configuring the DRACK or DONE mode and signal direction.                                                                             |  |

| DRACK2      | Output        | <b>DMA Data Request Acknowledge 2</b><br>Asserted by the DMA controller to indicate that the DMA controller has sampled the peripheral request.                                                                                       |  |

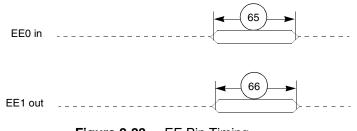

### 2.5.5.3 DMA Data Transfers

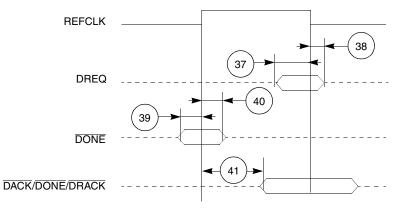

**Table 2-16** describes the DMA signal timing.

| No    | Chavastavistis                                                                 | Ref = CLKIN |     | Ref = CLKOUT |     | Linite |

|-------|--------------------------------------------------------------------------------|-------------|-----|--------------|-----|--------|

| No.   | Characteristic                                                                 |             | Мах | Min          | Max | Units  |

| 37    | DREQ set-up time before the 50% level of the falling edge of REFCLK            | 5.0         | _   | 5.0          | —   | ns     |

| 38    | DREQ hold time after the 50% level of the falling edge of REFCLK               | 0.5         |     | 0.5          | —   | ns     |

| 39    | DONE set-up time before the 50% level of the rising edge of REFCLK             | 5.0         |     | 5.0          | _   | ns     |

| 40    | DONE hold time after the 50% level of the rising edge of REFCLK                | 0.5         | _   | 0.5          | _   | ns     |

| 41    | DACK/DRACK/DONE delay after the 50% level of the REFCLK rising edge            | 0.5         | 7.5 | 0.5          | 8.4 | ns     |

| Note: | CLKOUT synchronization mode is not supported in cores operating above 400 MHz. |             |     |              |     |        |

Table 2-16. DMA Signals

The DREQ signal is synchronized with REFCLK. To achieve fast response, a synchronized peripheral should assert DREQ according to the timings in **Table 2-16**. Figure 2-8 shows synchronous peripheral interaction.

Figure 2-8. DMA Signals

## 2.5.6 DSI Timing

The timings in the following sections are based on a 20 pF capacitive load.

### 2.5.6.1 DSI Asynchronous Mode

| Table 2-17. | DSI Asynchronous Mode Timin | a |

|-------------|-----------------------------|---|

|             |                             | 9 |

| No.    | Characteristics                                                                                                                                                                                                                                                 | Min                                                                                             | Мах                                                                                             | Unit                 |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|

| 100    | Attributes <sup>1</sup> set-up time before strobe (HWBS[n]) assertion                                                                                                                                                                                           | 1.5                                                                                             | —                                                                                               | ns                   |

| 101    | Attributes <sup>1</sup> hold time after data strobe deassertion                                                                                                                                                                                                 | 1.3                                                                                             | —                                                                                               | ns                   |

| 102    | Read/Write data strobe deassertion width:         • DCR[HTAAD] = 1         - Consecutive access to the same DSI         - Different device with DCR[HTADT] = 01         - Different device with DCR[HTADT] = 10         - Different device with DCR[HTADT] = 11 | $1.8 + T_{REFCLK}$ $5 + T_{REFCLK}$ $5 + (1.5 \times T_{REFCLK})$ $5 + (2.5 \times T_{REFCLK})$ | _                                                                                               | ns<br>ns<br>ns<br>ns |

|        | • DCR[HTAAD] = 0                                                                                                                                                                                                                                                | 1.8 + T <sub>REFCLK</sub>                                                                       |                                                                                                 | ns                   |

| 103    | Read data strobe deassertion to output data high impedance                                                                                                                                                                                                      | _                                                                                               | 8.5                                                                                             | ns                   |

| 104    | Read data strobe assertion to output data active from high impedance                                                                                                                                                                                            | 2.0                                                                                             | —                                                                                               | ns                   |

| 105    | Output data hold time after read data strobe deassertion                                                                                                                                                                                                        | 2.2                                                                                             | —                                                                                               | ns                   |

| 106    | Read/Write data strobe assertion to HTA active from high impedance                                                                                                                                                                                              | 2.2                                                                                             | —                                                                                               | ns                   |

| 107    | Output data valid to HTA assertion                                                                                                                                                                                                                              | 3.2 —                                                                                           |                                                                                                 | ns                   |

| 108    | Read/Write data strobe assertion to HTA valid <sup>2</sup>                                                                                                                                                                                                      | _                                                                                               | 6.7                                                                                             | ns                   |

| 109    | Read/Write data strobe deassertion to output $\overline{\text{HTA}}$ high impedance.<br>(DCR[HTAAD] = 0, $\overline{\text{HTA}}$ at end of access released at logic 0)                                                                                          | _                                                                                               | 6.5                                                                                             | ns                   |

| 110    | Read/Write data strobe deassertion to output $\overline{\text{HTA}}$ deassertion.<br>(DCR[HTAAD] = 1, $\overline{\text{HTA}}$ at end of access released at logic 1)                                                                                             | _                                                                                               | 6.5                                                                                             | ns                   |

| 111    | Read/Write data strobe deassertion to output HTA high impedance.<br>(DCR[HTAAD] = 1, HTA at end of access released at logic 1<br>• DCR[HTADT] = 01<br>• DCR[HTADT] = 10<br>• DCR[HTADT] = 11                                                                    | _                                                                                               | 5 + T <sub>REFCLK</sub><br>5 + (1.5 × T <sub>REFCLK</sub> )<br>5 + (2.5 × T <sub>REFCLK</sub> ) | ns<br>ns<br>ns       |

| 112    | Read/Write data strobe assertion width                                                                                                                                                                                                                          | 1.8 + T <sub>REFCLK</sub>                                                                       | _                                                                                               | ns                   |

| 201    | Host data input set-up time before write data strobe deassertion                                                                                                                                                                                                |                                                                                                 | —                                                                                               | ns                   |

| 202    | Host data input hold time after write data strobe deassertion 1.5 —                                                                                                                                                                                             |                                                                                                 |                                                                                                 | ns                   |

| Notes: | <ol> <li>Attributes refers to the following signals: HCS, HA[11–29], HCID[0–4</li> <li>This specification is tested in dual strobe mode. Timing in single stro</li> <li>All values listed in this table are tested or guaranteed by design.</li> </ol>          | ••• · · · · · · · · · · · · · · · · · ·                                                         |                                                                                                 |                      |

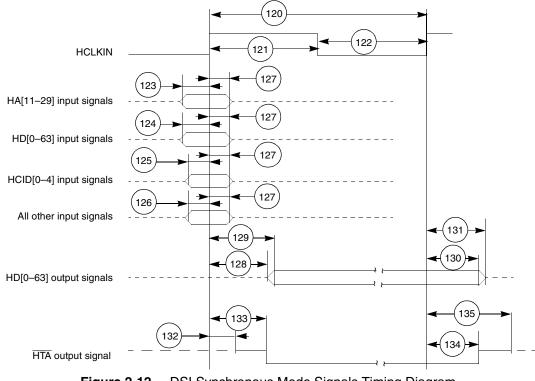

# 2.5.6.2 DSI Synchronous Mode

| No.    | Characteristic                                                                                                                  | Expression             | Min  | Max  | Units |

|--------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|-------|

| 120    | HCLKIN Cycle Time <sup>1, 2</sup>                                                                                               | HTC                    | 10.0 | 55.6 | ns    |

| 121    | HCLKIN high Pulse Width                                                                                                         | $(0.5\pm0.1)	imes$ HTC | 4.0  | 33.3 | ns    |

| 122    | HCLKIN low Pulse Width                                                                                                          | $(0.5\pm0.1)	imes$ HTC | 4.0  | 33.3 | ns    |

| 123    | HA[11–29] inputs set-up time                                                                                                    | _                      | 1.2  | _    | ns    |

| 124    | HD[0-63] inputs set-up time                                                                                                     |                        | 0.4  |      | ns    |

| 125    | HCID[0-4] inputs set-up time                                                                                                    |                        | 1.3  |      | ns    |

| 126    | All other inputs set-up time                                                                                                    | _                      | 1.2  | -    | ns    |

| 127    | All inputs hold time                                                                                                            |                        | 1.5  |      | ns    |

| Notes: | <ol> <li>Values are based on a frequency range of 18–100 MH</li> <li>Refer to Table 2-6 for HCLKIN frequency limits.</li> </ol> | Ζ.                     |      |      |       |

| Table 2-18. | DSI Inputs—Synchronous Mode |

|-------------|-----------------------------|

|-------------|-----------------------------|

| No. | Characteristic                                | Min | Max | Units |

|-----|-----------------------------------------------|-----|-----|-------|

| 128 | HCLKIN high to HD[0-63] output active         | 2.0 | —   | ns    |

| 129 | HCLKIN high to HD[0–63] output valid          |     | 6.3 | ns    |

| 130 | HD[0–63] output hold time                     | 1.7 | _   | ns    |

| 131 | HCLKIN high to HD[0–63] output high impedance |     | 7.6 | ns    |

| 132 | HCLKIN high to HTA output active              | 2.0 |     | ns    |

| 133 | HCLKIN high to HTA output valid               | -   | 5.9 | ns    |

| 134 | HTA output hold time                          | 1.7 | _   | ns    |

| 135 | HCLKIN high to HTA high impedance             | _   | 6.3 | ns    |

Figure 2-12. DSI Synchronous Mode Signals Timing Diagram

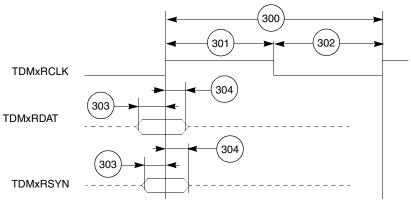

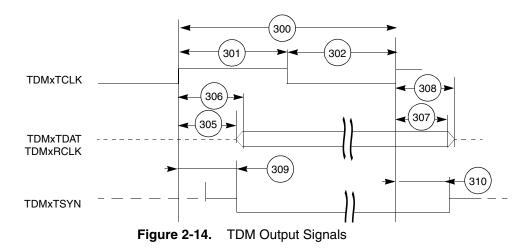

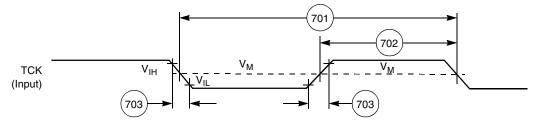

# 2.5.7 TDM Timing

| Ne     | Chavastavistis                                                                                                                                                                                                                                                                                           | Everencion            | Ref = CLKIN |      | Unite |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|------|-------|

| No.    | Characteristic                                                                                                                                                                                                                                                                                           | Expression            | Min         | Max  | Units |

| 300    | TDMxRCLK/TDMxTCLK                                                                                                                                                                                                                                                                                        | TC1                   | 16          | _    | ns    |

| 301    | TDMxRCLK/TDMxTCLK high pulse width                                                                                                                                                                                                                                                                       | $(0.5\pm0.1)	imes$ TC | 7           | _    | ns    |

| 302    | TDMxRCLK/TDMxTCLK low pulse width                                                                                                                                                                                                                                                                        | $(0.5\pm0.1)	imes$ TC | 7           | —    | ns    |

| 303    | TDM receive all input set-up time                                                                                                                                                                                                                                                                        |                       | 1.3         | —    | ns    |

| 304    | TDM receive all input hold time                                                                                                                                                                                                                                                                          |                       | 1.0         | _    | ns    |

| 305    | TDMxTCLK high to TDMxTDAT/TDMxRCLK output active <sup>2,3</sup>                                                                                                                                                                                                                                          |                       | 2.8         | _    | ns    |

| 306    | TDMxTCLK high to TDMxTDAT/TDMxRCLK output valid <sup>2,3</sup>                                                                                                                                                                                                                                           |                       |             | 8.8  | ns    |

| 307    | All output hold time <sup>5</sup>                                                                                                                                                                                                                                                                        |                       | 2.5         | _    | ns    |

| 308    | TDMxTCLK high to TDmXTDAT/TDMxRCLK output high impedance <sup>2,3</sup>                                                                                                                                                                                                                                  |                       |             | 10.5 | ns    |

| 309    | TDMxTCLK high to TDMXTSYN output valid <sup>2</sup>                                                                                                                                                                                                                                                      |                       |             | 8.5  | ns    |

| 310    | TDMxTSYN output hold time <sup>5</sup>                                                                                                                                                                                                                                                                   |                       | 2.5         | _    | ns    |