# E·XFL

### NXP USA Inc. - KMSC8126VT8000 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Details                 |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Obsolete                                                               |

| Туре                    | SC140 Core                                                             |

| Interface               | DSI, Ethernet, RS-232                                                  |

| Clock Rate              | 500MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 1.436MB                                                                |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | 0°C ~ 90°C (TJ)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 431-BFBGA, FCBGA                                                       |

| Supplier Device Package | 431-FCPBGA (20x20)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmsc8126vt8000 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 3. | Buses and | Memory | Controller |

|----------|-----------|--------|------------|

|----------|-----------|--------|------------|

| Feature                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 60x-Compatible<br>System Bus    | <ul> <li>64/32-bit data and 32-bit address 60x bus.</li> <li>Support for multiple-master designs.</li> <li>Four-beat burst transfers (eight-beat in 32-bit wide mode).</li> <li>Port size of 64, 32, 16, and 8 controlled by the internal memory controller.</li> <li>Bus can access external memory expansion or off-device peripherals, or it can enable an external host device to access internal resources.</li> <li>Slave support, direct access by an external host to internal resources including the M1 and M2 memories.</li> <li>On-device arbitration between up to four master devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Direct Slave<br>Interface (DSI) | <ul> <li>A 32/64-bit wide slave host interface that operates only as a slave device under the control of an external host processor.</li> <li>21–25 bit address, 32/64-bit data.</li> <li>Direct access by an external host to internal and external resources, including the M1 and the M2 memories as well as external devices on the system bus.</li> <li>Synchronous and asynchronous accesses, with burst capability in the synchronous mode.</li> <li>Dual or single-strobe modes.</li> <li>Write and read buffers improve host bandwidth.</li> <li>Byte enable signals enables 1, 2, 4, and 8 byte write access granularity.</li> <li>Sliding window mode enables access with reduced number of address pins.</li> <li>Chip ID decoding enables using one CS signal for multiple DSPs.</li> <li>Broadcast CS signal enables parallel write to multiple DSPs.</li> <li>Big-endian, little-endian, and munged little-endian support.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 3-Mode Signal<br>Multiplexing   | <ul> <li>64-bit DSI, 32-bit system bus.</li> <li>32-bit DSI, 64-bit system bus.</li> <li>32-bit DSI, 32-bit system bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Memory Controller               | <ul> <li>Flexible eight-bank memory controller:</li> <li>Three user-programmable machines (UPMs), general-purpose chip-select machine (GPCM), and a page-mode SDRAM machine.</li> <li>Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash memory, and other user-definable peripherals.</li> <li>Byte enables for either 64-bit or 32-bit bus width mode.</li> <li>Eight external memory banks (banks 0–7). Two additional memory banks (banks 9, 11) control IPBus peripherals and internal memories. Each bank has the following features: <ul> <li>—32-bit address decoding with programmable mask.</li> <li>—Variable block sizes (32 KB to 4 GB).</li> <li>—Selectable memory controller machine.</li> <li>—Two types of data errors check/correction: normal odd/even parity and read-modify-write (RMW) odd/even parity for single accesses.</li> <li>—Write-protection capability.</li> <li>—Control signal generation machine selection on a per-bank basis.</li> <li>—Support for internal or external masters on the system bus.</li> <li>—Data buffer controls activated on a per-bank basis.</li> <li>—RMW data parity check (on system bus only).</li> <li>—Extensive external memory-controller/bus-slave support.</li> <li>—Parity byte select pin, which enables a fast, glueless connection to RMW-parity devices (on the system bus only).</li> <li>—Data pipeline to reduce data set-up time for synchronous devices.</li> </ul></li></ul> |  |  |

Table 7.

Coprocessors

| Feature | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VCOP    | <ul> <li>Fully programmable feed-forward channel decoding, feed-forward channel equalization and traceback sessions.</li> <li>Up to 400 3GPP 12.2kbps AMR channels (channel decoding, number of channels linear to frequency).</li> <li>Up to 200 blind transport format detect (BTFD) channels according to the 3GPP standard. Number of channels linear to frequency.</li> <li>For channel decoding: <ul> <li>Constraint length between K = 5 and K = 9.</li> <li>Puncture Codes.</li> <li>Rate 1/2, 1/3, 1/4 and 1/6.</li> <li>Four fully programmable polynomials (rate 1/6 is implemented by three polynomials only).</li> <li>History buffer with up to 768 stages for 3G standards.</li> <li>Input symbols are 8-bit (256 levels) signed soft symbols.</li> <li>Output is hard decision (1-bit).</li> </ul> </li> <li>For GSM channel equalization: <ul> <li>Fully programmable 4 to 6 estimated channel autocorrelation coefficients (S-Parameters).</li> <li>History buffer with up to 4090 stages for GSM.</li> <li>Matched filter input is 8-bit (256 levels).</li> <li>SOVA assist algorithm.</li> <li>Output 8-bit coded detta values for SOVA assist algorithm, 1-bit hard decision traceback and history buffer or recursive traceback.</li> </ul> </li> <li>Fully programmable block length for all sessions.</li> <li>Programmable learning period length for the traceback session.</li> <li>Supports the start of feed-forward according to a presaved PM memory content. However the history buffer is not saved. Therefore the traceback is according to the current block only.</li> <li>Each SC140 can program the VCOP parameters while the VCOP is in IDLE mode and then the VCOP can run independently on the whole block of data.</li> <li>Dumping path metrics to the internal memory on up to 12 predefined stages; this is needed for BTFD applications.</li> <li>Interrupt lines and status bits notify the cores on session completion.</li> </ul> |  |  |

| ТСОР    | <ul> <li>Full support of 3GPP and CDMA2000 standards in Turbo decode.</li> <li>Up to 20 turbo-coding 384 kbps channels.</li> <li>8 state PCCC with polynomial as supported by the 3G standards.</li> <li>Iterative decoding structure based on Maximum A-Posteriori probability (MAP), with calculations performed in the LOG domain.</li> <li>Encoding rate of 1/2, 1/3, 1/4, 1/5 with programmable puncturing for the parity symbols.</li> <li>Full flexibility interleave function via a look-up table.</li> <li>Flexible block size (1–32767 bits).</li> <li>MAX log MAP and log MAP (MAX*) approximation.</li> <li>Programmable number of iterations, with resolution of half iteration (one MAP).</li> <li>Fully automatic execution when the GO command executes.</li> <li>High data rates (for multi-channel systems or multiple channel accumulating to high data rates).</li> <li>Can stop processing after every MAP when soft lambda all reach a programmable quality threshold.</li> <li>Minimum and maximum number of iterations to execute in conjunction with the stop criteria.</li> <li>The SC140 core or host can stop the processing after every MAP during run time.</li> <li>Automatic, internal normalization for α, β overflow handling, with zero overhead.</li> <li>Automatic, internal Λ clipping for Λ overflow handling, with zero overhead.</li> <li>Additional least significant bit in α, β, γ arithmetic guarding against precision loss during the gamma calculation due to the division by 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Table 8. | Power and Packaging |

|----------|---------------------|

|----------|---------------------|

| Feature                      | Description                                                                                                                                                                                                                                                                                     |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reduced Power<br>Dissipation | <ul> <li>Low-power CMOS design.</li> <li>Separate power supply for internal logic (1.2 V for 400 MHz or 500 MHz) and I/O (3.3 V).</li> <li>Low-power standby modes.</li> <li>Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-dependent).</li> </ul> |  |  |

| Packaging                    | <ul> <li>0.8 mm pitch Flip-Chip Plastic Ball-Grid Array (FC-PBGA).</li> <li>431-connection (ball).</li> <li>20 mm × 20 mm.</li> </ul>                                                                                                                                                           |  |  |

### Table 9. Software Support

| Feature                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Real-Time<br>Operating System<br>(RTOS) | <ul> <li>The real-time operating system (RTOS) fully supports device architecture (multi-core, memory hierarchy, ICache, timers, DMA controller, interrupts, peripherals), as follows:</li> <li>High-performance and deterministic, delivering predictive response time.</li> <li>Optimized to provide low interrupt latency with high data throughput.</li> <li>Preemptive and priority-based multitasking.</li> <li>Fully interrupt/event driven.</li> <li>Small memory footprint.</li> <li>Comprehensive set of APIs.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Multi-Core<br>Support                   | <ul> <li>One instance of kernel code in all four SC140 cores.</li> <li>Dynamic and static memory allocation from local memory (M1) and shared memory (M2).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Distributed<br>System Support           | <ul> <li>Transparent inter-task communications between tasks running inside the SC140 cores and the other tasks running in on-board devices or remote network devices:</li> <li>Messaging mechanism between tasks using mailboxes and semaphores.</li> <li>Networking support; data transfer between tasks running inside and outside the device using networking protocols.</li> <li>Includes integrated device drivers for such peripherals as TDM, UART, and external buses.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Software Support                        | <ul> <li>Task debugging utilities integrated with compilers and vendors.</li> <li>Board support package (BSP) for the application development system (ADS).</li> <li>Integrated development environment (IDE):         <ul> <li>-C/C++ compiler with in-line assembly so developers can generate highly optimized DSP code. Translates C/C++ code into parallel fetch sets and maintains high code density.</li> <li>-Librarian. User can create libraries for modularity.</li> <li>-A collection of C/C++ functions for developer use.</li> <li>-Highly efficient linker to produce executables from object code.</li> <li>-Seamlessly integrated real-time, non-intrusive multi-mode debugger for debugging highly optimized DSP algorithms. The developer can choose to debug in source code, assembly code, or mixed mode.</li> <li>-Device simulation models enable design and simulation before hardware availability.</li> <li>-Profiler using a patented binary code instrumentation (BCI) technique helps developers identify program design inefficiencies.</li> <li>-Version control. Metrowerks® CodeWarrior® includes plug-ins for ClearCase, Visual SourceSafe, and CVS.</li> </ul> </li> </ul> |  |  |

| Boot Options                            | <ul> <li>External memory.</li> <li>External host.</li> <li>UART.</li> <li>TDM.</li> <li>I<sup>2</sup>C</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

### Signals/Connections

| Signal Name | Туре          | Description                                                                                                                                                                                                                                                           |  |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IRQ1        | Input         | Interrupt Request 1<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                                               |  |

| DP1         | Input/ Output | System Bus Data Parity 1<br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity<br>1 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 1<br>and D[8–15].   |  |

| DACK1       | Output        | <b>DMA Acknowledge 1</b><br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                      |  |

| EXT_BG2     | Output        | <b>External Bus Grant 2<sup>2</sup></b><br>The MSC8126 asserts this signal to grant bus ownership to an external bus master.                                                                                                                                          |  |

| IRQ2        | Input         | Interrupt Request 2<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                                               |  |

| DP2         | Input/ Output | <b>System Bus Data Parity 2</b><br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity 2 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 2 and D[16–23]. |  |

| DACK2       | Output        | DMA Acknowledge 2<br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                             |  |

| EXT_DBG2    | Output        | <b>External Data Bus Grant 2</b> <sup>2</sup><br>The MSC8126 asserts this signal to grant data bus ownership to an external bus master.                                                                                                                               |  |

| IRQ3        | Input         | Interrupt Request 3<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                                               |  |

| DP3         | Input/ Output | System Bus Data Parity 3<br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity<br>3 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 3<br>and D[24–31].  |  |

| DREQ2       | Input         | DMA Request 2<br>Used by an external peripheral to request DMA service.                                                                                                                                                                                               |  |

| EXT_BR3     | Input         | <b>External Bus Request 3</b> <sup>2</sup><br>An external master should assert this signal to request bus ownership from the internal arbiter.                                                                                                                        |  |

| IRQ4        | Input         | Interrupt Request 4<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                                               |  |

| DP4         | Input/ Output | System Bus Data Parity 4<br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity<br>4 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 4<br>and D[32–39].  |  |

| DACK3       | Output        | <b>DMA Acknowledge 3</b><br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                      |  |

| EXT_DBG3    | Output        | <b>External Data Bus Grant 3<sup>2</sup></b><br>The MSC8126 asserts this signal to grant data bus ownership to an external bus master.                                                                                                                                |  |

### Table 1-5. DSI, System Bus, Ethernet, and Interrupt Signals (Continued)

| Table 1-5. | DSI, System Bus, | Ethernet, and | I Interrupt Signals | (Continued) |

|------------|------------------|---------------|---------------------|-------------|

|------------|------------------|---------------|---------------------|-------------|

| Signal Name | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IRQ5        | Input         | Interrupt Request 5<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from th<br>SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DP5         | Input/ Output | System Bus Data Parity 5<br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity<br>5 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 5<br>and D[40–47].                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| DACK4       | Output        | <b>DMA Acknowledge 4</b><br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| EXT_BG3     | Output        | <b>External Bus Grant 3<sup>2</sup></b><br>The MSC8126 asserts this signal to grant bus ownership to an external bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ÎRQ6        | Input         | Interrupt Request 6<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| DP6         | Input/ Output | <b>System Bus Data Parity 6</b><br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity 6 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 6 and D[48–55].                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| DREQ3       | Input         | DMA Request 3<br>Used by an external peripheral to request DMA service.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| IRQ7        | Input         | Interrupt Request 7<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| DP7         | Input/ Output | System Bus Data Parity 7<br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity<br>7 signal should give odd parity (odd number of ones) on the group of signals that includes data parity 7<br>and D[56–63].                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| DREQ4       | Input         | <b>DMA Request 4</b><br>Used by an external peripheral to request DMA service.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| TA          | Input/ Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| TEA         | Input/ Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NMI         | Input         | Non-Maskable Interrupt<br>When an external device asserts this line, it generates an non-maskable interrupt in the MSC8126, which<br>is processed internally (default) or is directed to an external host for processing (see NMI_OUT).                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| NMI_OUT     | Output        | Non-Maskable Interrupt Output<br>An open-drain signal driven from the MSC8126 internal interrupt controller. This output indicates whether<br>a non-maskable interrupt is pending in the MSC8126 internal interrupt controller, waiting to be handled by<br>an external host.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PSDVAL      | Input/ Output | <b>Port Size Data Valid</b><br>Indicates that a data beat is valid on the data bus. The difference between the TA signal and the PSDVAL signal is that the TA signal is asserted to indicate data transfer terminations, while the PSDVAL signal is asserted with each data beat movement. When TA is asserted, PSDVAL is always asserted. However, when PSDVAL is asserted, TA is not necessarily asserted. For example, if the DMA controller initiates a double word ( $2 \times 64$ bits) transaction to a memory device with a 32-bit port size, PSDVAL is asserted three times without TA and, finally, both signals are asserted to terminate the transfer. |  |  |

### Signals/Connections

| Signal Name | Туре          | Description                                                                                                                                                                                                                                         |  |  |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIO23      | Input/ Output | <b>General-Purpose Input Output 23</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.               |  |  |

| TDM0TDAT    | Input/ Output | <b>TDM0 Serial Transmitter Data</b><br>The transmit data signal for TDM 0. As an output, this can be the DATA_D data signal for TDM 0. For<br>configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation. |  |  |

| IRQ13       | Input         | Interrupt Request 13<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                            |  |  |

| GPIO24      | Input/ Output | <b>General-Purpose Input Output 24</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.               |  |  |

| TDMORSYN    | Input/ Output | <b>TDM0 Receive Frame Sync</b><br>The receive sync signal for TDM 0. As an input, this can be the DATA_B data signal for TDM 0. For<br>configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation.        |  |  |

| IRQ14       | Input         | Interrupt Request 14<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                            |  |  |

| GPIO25      | Input/ Output | <b>General-Purpose Input Output 25</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.               |  |  |

| TDM0RCLK    | Input/ Output | <b>TDM0 Receive Clock</b><br>The receive clock signal for TDM 0. As an input, this can be the DATA_C data signal for TDM 0. For configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation.               |  |  |

| IRQ15       | Input         | Interrupt Request 15<br>One of fifteen external lines that can request a service routine, via the internal interrupt controller, from the<br>SC140 core.                                                                                            |  |  |

| GPIO26      | Input/ Output | General-Purpose Input Output 26<br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.                      |  |  |

| TDM0RDAT    | Input/ Output | <b>TDM0 Serial Receiver Data</b><br>The receive data signal for TDM 0. As an input, this can be the DATA_A data signal for TDM 0. For configuration details, refer to the <i>MSC8126 Reference Manual</i> chapter describing TDM operation.         |  |  |

| GPIO27      | Input/ Output | General-Purpose Input Output 27<br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.                      |  |  |

| DREQ1       | Input         | DMA Request 1<br>Used by an external peripheral to request DMA service.                                                                                                                                                                             |  |  |

| URXD        | Input         | UART Receive Data                                                                                                                                                                                                                                   |  |  |

| GPIO28      | Input/ Output | <b>General-Purpose Input Output 28</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8126 Reference Manual</i> GPIO programming model.               |  |  |

| DREQ2       | Input         | DMA Request 2<br>Used by an external peripheral to request DMA service.                                                                                                                                                                             |  |  |

| UTXD        | Output        | UART Transmit Data                                                                                                                                                                                                                                  |  |  |

### Table 1-7. GPIO, TDM, UART, Ethernet, and Timer Signals (Continued)

| Signal Name | Туре  | Signal Description                                                                              |

|-------------|-------|-------------------------------------------------------------------------------------------------|

| ETHCRS      | Input | Carrier Sense<br>In MII mode, indicates that either the transmit or receive medium is non-idle. |

| ETHRXD      | Input | Ethernet Receive Data<br>In SMII mode, used for the Ethernet receive data.                      |

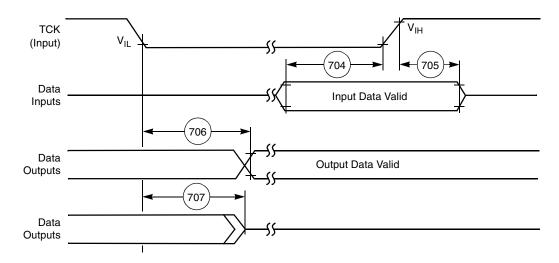

# **1.8 EOnCE Event and JTAG Test Access Port Signals**

The MSC8126 uses two sets of debugging signals for the two types of internal debugging modules: EOnCE and the JTAG TAP controller. Each internal SC140 core has an EOnce module, but they are all accessed externally by the same two signals EE0 and EE1. The MSC8126 supports the standard set of test access port (TAP) signals defined by IEEE Std 1149.1 Standard Test Access Port and Boundary-Scan Architecture specification and described in Table 1-9.

| Signal Name | Туре   | Signal Description                                                                                                                                                                                                               |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EE0         | Input  | EOnCE Event Bit 0<br>Puts the internal SC140 cores into Debug mode.                                                                                                                                                              |

| EE1         | Output | EOnCE Event Bit 1<br>Indicates that at least one on-device SC140 core is in Debug mode.                                                                                                                                          |

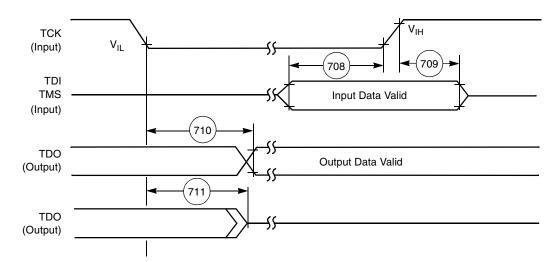

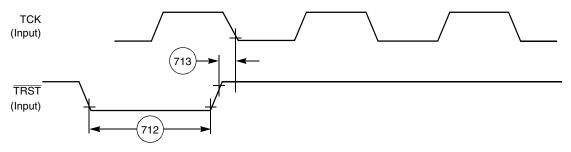

| ТСК         | Input  | Test Clock<br>Synchronizes the JTAG test logic.                                                                                                                                                                                  |

| TDI         | Input  | Test Data Input<br>A test data serial signal for test instructions and data. TDI is sampled on the rising edge of TCK and has<br>an internal pull-up resistor.                                                                   |

| TDO         | Output | <b>Test Data Output</b><br>A test data serial signal for test instructions and data. TDO can be tri-stated. The signal is actively driven in the shift-IR and shift-DR controller states and changes on the falling edge of TCK. |

| TMS         | Input  | Test Mode Select<br>Sequences the test controller state machine, is sampled on the rising edge of TCK, and has an internal<br>pull-up resistor.                                                                                  |

| TRST        | Input  | Test Reset<br>Asynchronously initializes the test controller; must be asserted during power up.                                                                                                                                  |

| Table 1-9. | JTAG TAP Signals |

|------------|------------------|

|------------|------------------|

# 1.9 Reserved Signals

| Table 1-10. | Reserved Signals |

|-------------|------------------|

|-------------|------------------|

| Signal Name | Туре  | Signal Description                                                             |

|-------------|-------|--------------------------------------------------------------------------------|

| TEST        | Input | Test<br>For manufacturing testing. You <i>must</i> connect this signal to GND. |

| Characteristic                                                            | Symbol                               | Min  | Typical                              | Max   | Unit     |

|---------------------------------------------------------------------------|--------------------------------------|------|--------------------------------------|-------|----------|

| Input high voltage <sup>1</sup> , all inputs except CLKIN                 | V <sub>IH</sub>                      | 2.0  | _                                    | 3.465 | V        |

| Input low voltage <sup>1</sup>                                            | V <sub>IL</sub>                      | GND  | 0                                    | 0.4   | V        |

| CLKIN input high voltage                                                  | V <sub>IHC</sub>                     | 2.4  | 3.0                                  | 3.465 | V        |

| CLKIN input low voltage                                                   | V <sub>ILC</sub>                     | GND  | 0                                    | 0.4   | V        |

| Input leakage current, V <sub>IN</sub> = V <sub>DDH</sub>                 | I <sub>IN</sub>                      | -1.0 | 0.09                                 | 1     | μA       |

| Tri-state (high impedance off state) leakage current, $V_{IN} = V_{DDH}$  | I <sub>OZ</sub>                      | -1.0 | 0.09                                 | 1     | μA       |

| Signal low input current, $V_{IL} = 0.4 V^2$                              | ١ <sub>L</sub>                       | -1.0 | 0.09                                 | 1     | μA       |

| Signal high input current, $V_{IH} = 2.0 V^2$                             | Ι <sub>Η</sub>                       | -1.0 | 0.09                                 | 1     | μA       |

| Output high voltage, I <sub>OH</sub> = -2 mA,<br>except open drain pins   | V <sub>OH</sub>                      | 2.0  | 3.0                                  | —     | V        |

| Output low voltage, I <sub>OL</sub> = 3.2 mA                              | V <sub>OL</sub>                      |      | 0                                    | 0.4   | V        |

| Internal supply current: <ul> <li>Wait mode</li> <li>Stop mode</li> </ul> | I <sub>DDW</sub><br>I <sub>DDS</sub> |      | 375 <sup>3</sup><br>290 <sup>3</sup> |       | mA<br>mA |

| Typical power at 400 MHz <sup>4</sup>                                     | Р                                    |      | 1.15                                 | _     | W        |

Table 2-4. **DC Electrical Characteristics**

2. Not tested. Guaranteed by design.

Measured for 1.2 V core at 25°C junction temperature. 3.

The typical power values were measured using an EFR code with the device running at a junction temperature of 25°C. No 4. peripherals were enabled and the ICache was not enabled. The source code was optimized to use all the ALUs and AGUs and all four cores. It was created using CodeWarrior<sup>®</sup> 2.5. These values are provided as examples only. Power consumption is application dependent and varies widely. To assure proper board design with regard to thermal dissipation and maintaining proper operating temperatures, evaluate power consumption for your application and use the design guidelines in Chapter 4 of this document and in MSC8102, MSC8122, and MSC8126 Thermal Management Design Guidelines (AN2601).

## 2.5 AC Timings

The following sections include illustrations and tables of clock diagrams, signals, and parallel I/O outputs and inputs. When systems such as DSP farms are developed using the DSI, use a device loading of 4 pF per pin. AC timings are based on a 20 pF load, except where noted otherwise, and a 50  $\Omega$  transmission line. For loads smaller than 20 pF, subtract 0.06 ns per pF down to 10 pF load. For loads larger than 20 pF, add 0.06 ns for SIU/Ethernet/DSI delay and 0.07 ns for GPIO/TDM/timer delay. When calculating overall loading, also consider additional RC delay.

### 2.5.1 Output Buffer Impedances

| Table 2-5. | Output Buffer Impedances |

|------------|--------------------------|

|------------|--------------------------|

| Output Buffers                                                                                                                | Typical Impedance (Ω) |  |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| System bus                                                                                                                    | 50                    |  |

| Memory controller                                                                                                             | 50                    |  |

| Parallel I/O                                                                                                                  | 50                    |  |

| Note: These are typical values at 65°C. The impedance may vary by ±25% depending on device process and operating temperature. |                       |  |

### 2.5.2 Start-Up Timing

Starting the device requires coordination among several input sequences including clocking, reset, and power. **Section 2.5.3** describes the clocking characteristics. **Section 2.5.4** describes the reset and power-up characteristics. You must use the following guidelines when starting up an MSC8126 device:

- **PORESET** and **TRST** must be asserted externally for the duration of the power-up sequence. See **Table 2-10** for timing.

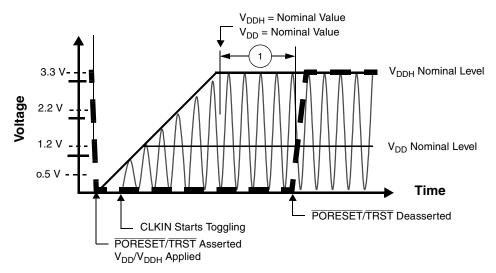

- If possible, bring up the  $V_{DD}$  and  $V_{DDH}$  levels together. For designs with separate power supplies, bring up the  $V_{DD}$  levels and then the  $V_{DDH}$  levels (see **Figure 2-3**).

- CLKIN should start toggling at least 16 cycles (starting after V<sub>DDH</sub> reaches its nominal level) before PORESET deassertion to guarantee correct device operation (see Figure 2-2 and Figure 2-3).

- CLKIN must not be pulled high during V<sub>DDH</sub> power-up. CLKIN can toggle during this period.

The following figures show acceptable start-up sequence examples. Figure 2-2 shows a sequence in which  $V_{DD}$  and  $V_{DDH}$  are raised together. Figure 2-3 shows a sequence in which  $V_{DDH}$  is raised after  $V_{DD}$  and CLKIN begins to toggle as  $V_{DDH}$  rises.

Figure 2-2. Start-Up Sequence with  $V_{DD}$  and  $V_{DDH}$  Raised Together

### 2.5.4.3 Reset Timing Tables

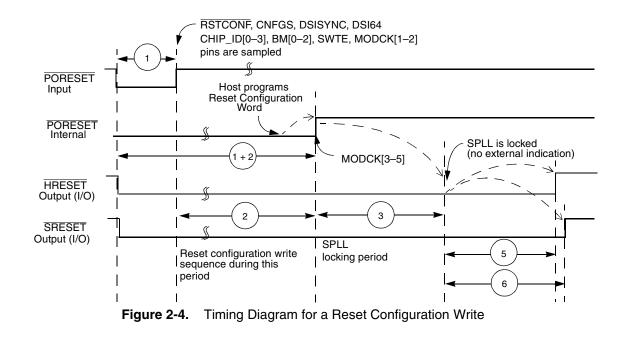

**Table 2-11** and **Figure 2-4** describe the reset timing for a reset configuration write through the direct slave interface (DSI) or through the system bus.

| No.   | Characteristics                                                                                                                                                                                           | Expression                                                    | Min              | Max             | Unit           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|-----------------|----------------|

| 1     | <ul> <li>Required external PORESET duration minimum</li> <li>CLKIN = 20 MHz</li> <li>CLKIN = 133 MHz (400 MHz core)</li> <li>CLKIN = 166 MHz (500 MHz core)</li> </ul>                                    | 16/CLKIN                                                      | 800<br>120<br>96 | 800<br>—        | ns<br>ns<br>ns |

| 2     | Delay from deassertion of external PORESET to deassertion of internal<br>PORESET<br>• CLKIN = 20 MHz to 166 MHz                                                                                           | 1024/CLKIN                                                    | 6.17             | 51.2            | μs             |

| 3     | Delay from de-assertion of internal PORESET to SPLL lock <ul> <li>CLKIN = 20 MHz (RDF = 1)</li> <li>CLKIN = 133 MHz (RDF = 2) (400 MHz core)</li> <li>CLKIN = 166 MHz (RDF = 2) (500 MHz core)</li> </ul> | 6400/(CLKIN/RDF)<br>(PLL reference clock-<br>division factor) | 320<br>96<br>77  | 320<br>96<br>77 | μs<br>μs<br>μs |

| 5     | Delay from SPLL to HRESET deassertion<br>• REFCLK = 40 MHz to 166 MHz                                                                                                                                     | 512/REFCLK                                                    | 3.08             | 12.8            | μs             |

| 6     | Delay from SPLL lock to SRESET deassertion <ul> <li>REFCLK = 40 MHz to 166 MHz</li> </ul>                                                                                                                 | 515/REFCLK                                                    | 3.10             | 12.88           | μs             |

| 7     | Setup time from assertion of RSTCONF, CNFGS, DSISYNC, DSI64,<br>CHIP_ID[0–3], BM[0–2], SWTE, and MODCK[1–2] before deassertion of<br>PORESET                                                              |                                                               | 3                | _               | ns             |

| 8     | Hold time from deassertion of PORESET to deassertion of RSTCONF,<br>CNFGS, DSISYNC, DSI64, CHIP_ID[0–3], BM[0–2], SWTE, and<br>MODCK[1–2]                                                                 |                                                               | 5                | _               | ns             |

| Note: | Timings are not tested, but are guaranteed by design.                                                                                                                                                     | ·                                                             |                  |                 |                |

Table 2-11.

Timing for a Reset Configuration Write through the DSI or System Bus

The UPM machine and GPCM machine outputs change on the internal tick determined by the memory controller configuration. The AC specifications are relative to the internal tick. SDRAM machine outputs change only on the REFCLK rising edge.

|                 |                                                                                                                                                                                                | Value for Bus Speed in MHz |            |              |          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|--------------|----------|

| No.             | Characteristic                                                                                                                                                                                 | Ref = CI                   | KIN        | Ref = CLKOUT | Units    |

|                 |                                                                                                                                                                                                | 133                        | 166        | 133          |          |

| 10              | Hold time for all signals after the 50% level of the REFCLK rising edge                                                                                                                        | 0.5                        | 0.5        | 0.5          | ns       |

| 11a             | ARTRY/ABB set-up time before the 50% level of the REFCLK rising edge                                                                                                                           | 3.0                        | 3.0        | 3.0          | ns       |

| 11b             | DBG/DBB/BG/BR/TC set-up time before the 50% level of the REFCLK rising edge                                                                                                                    | 3.3                        | 3.3        | 3.3          | ns       |

| 11c             | AACK set-up time before the 50% level of the REFCLK rising edge                                                                                                                                | 2.9                        | 2.9        | 2.9          | ns       |

| 11d             | <ul> <li>TA/TEA/PSDVAL set-up time before the 50% level of the REFCLK rising edge</li> <li>Data-pipeline mode</li> <li>Non-pipeline mode</li> </ul>                                            | 3.4<br>4.0                 | 3.4<br>4.0 | 3.4<br>4.0   | ns<br>ns |

| 12              | Data bus set-up time before REFCLK rising edge in Normal mode <ul> <li>Data-pipeline mode</li> <li>Non-pipeline mode</li> </ul>                                                                | 1.8<br>4.0                 | 1.7<br>4.0 | 1.8<br>4.0   | ns<br>ns |

| 13              | Data bus set-up time before the 50% level of the REFCLK rising edge<br>in ECC and PARITY modes<br>• Data-pipeline mode<br>• Non-pipeline mode                                                  | 2.0<br>7.3                 | 2.0<br>7.3 | 2.0<br>7.3   | ns<br>ns |

| 14              | DP set-up time before the 50% level of the REFCLK rising edge <ul> <li>Data-pipeline mode</li> <li>Non-pipeline mode</li> </ul>                                                                | 2.0<br>6.1                 | 2.0<br>6.1 | 2.0<br>6.1   | ns<br>ns |

| 15a             | <ul> <li>TS and Address bus set-up time before the 50% level of the REFCLK rising edge</li> <li>Extra cycle mode (SIUBCR[EXDD] = 0)</li> <li>No extra cycle mode (SIUBCR[EXDD] = 1)</li> </ul> | 3.6<br>5.0                 | 3.6<br>5.0 | 3.8<br>5.0   | ns<br>ns |

| 15b             | Address attributes: TT/TBST/TSZ/GBL set-up time before the 50%<br>level of the REFCLK rising edge<br>• Extra cycle mode (SIUBCR[EXDD] = 0)<br>• No extra cycle mode (SIUBCR[EXDD] = 1)         | 3.5<br>4.4                 | 3.5<br>4.4 | 3.5<br>4.4   | ns<br>ns |

| 16 <sup>1</sup> | PUPMWAIT signal set-up time before the 50% level of the REFCLK rising edge                                                                                                                     | 3.7                        | 3.7        | 3.7          | ns       |

Table 2-13. AC Timing for SIU Inputs

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Value for Bus Speed in MHz |            |              |           |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|--------------|-----------|

| No.             | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ref = CLKIN                |            | Ref = CLKOUT | Units     |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 133                        | 166        | 133          |           |