Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | ARM® Cortex®-M0                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 50MHz                                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                                      |

| Number of I/O              | 30                                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 4K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 48-LQFP                                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/mini58lde |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Two I<sup>2</sup>C devices

- Supports Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allowing devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allow for versatile rate control

- Supports multiple address recognition (four slave addresses with mask option)

- ADC (Analog-to-Digital Converter)

- 10-bit SAR ADC with 250 kSPS

- Up to 8-ch single-end input and one internal input from band-gap

- Conversion started either by software trigger or external pin trigger

- Analog Comparator

- Two analog comparators with programmable 16-level internal voltage reference

- Built-in CRV (comparator reference voltage)

- ISP (In-System Programming), ICP (In-Circuit Programming), and IAP (In-Application-Programming) update

- BOD (Brown-out Detector)

- With 4 programmable threshold levels: 4.4V/3.7V/2.7V/2.2V

- Supports Brown-out interrupt and reset option

- 96-bit unique ID

- LVR (Low Voltage Reset)

- Threshold voltage level: 2.0V

- Operating Temperature: -40°C ~105°C

- Reliability: EFT >  $\pm$  4KV, ESD HBM pass 4KV

- Packages:

- Green package (RoHS)

- 48-pin LQFP (7x7), 33-pin QFN (5x5) , 33-pin QFN (4x4), 20-pin TSSOP

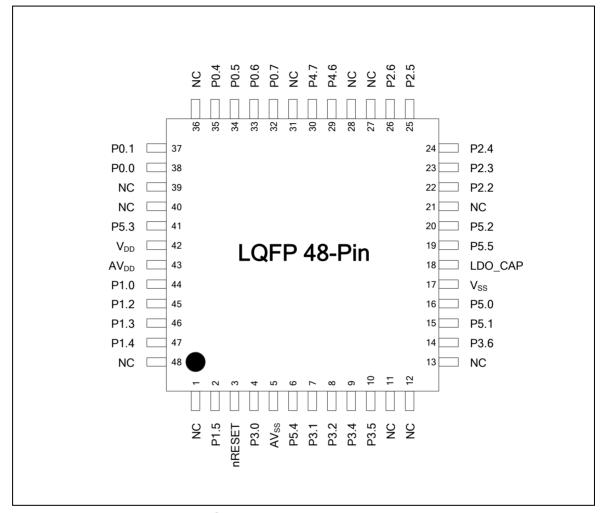

### 4.3 PIN CONFIGURATION

### 4.3.1 LQFP 48-pin

Figure 4.3-1 NuMicro<sup>®</sup> Mini58 Series LQFP 48-pin Diagram

# 4.4 Pin Description

| Pin Number     |               |                 |                  |          |                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------|---------------|-----------------|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LQFP<br>48-pin | QFN<br>33-pin | TSSOP<br>20-pin | Pin Name         | Pin Type | Description                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1              |               |                 | NC               |          | Not connected                                                                                                                                                                                                                                                                                                          |  |  |  |

|                |               |                 | P1.5             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

|                |               | 4               | ADC_CH5          | AI       | ADC analog input pin                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2              | 1             | 4               | UART1_TXD        | 0        | UART1 transmitter output pin                                                                                                                                                                                                                                                                                           |  |  |  |

|                |               |                 | ACMP0_P0         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                   |  |  |  |

| 3              | 2             | 5               | nRESET           | I(ST)    | The Schmitt trigger input pin for hardware device reset. A " <b>Low</b> " on this pin for 768 clock counter of Internal RC 22.1184 MHz while the system clock is running will reset the device. nRESET pin has an internal pull-up resistor allowing power-on reset by simply connecting an external capacitor to GND. |  |  |  |

|                |               |                 | P3.0             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

| 4              | 3             |                 | ADC_CH6          | AI       | ADC analog input pin                                                                                                                                                                                                                                                                                                   |  |  |  |

|                |               |                 | ACMP1_N          | AI       | Analog comparator negative input pin                                                                                                                                                                                                                                                                                   |  |  |  |

| 5              |               |                 | AV <sub>SS</sub> | AP       | Ground pin for analog circuit                                                                                                                                                                                                                                                                                          |  |  |  |

| 6              | 4             |                 | P5.4             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

|                |               |                 | P3.1             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

| 7              | 5             |                 | ADC_CH7          | AI       | ADC analog input pin                                                                                                                                                                                                                                                                                                   |  |  |  |

|                |               |                 | ACMP1_P0         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                   |  |  |  |

|                |               |                 | P3.2             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

|                |               |                 | INT0             | I        | External interrupt 0 input pin                                                                                                                                                                                                                                                                                         |  |  |  |

| 8              | 6             | 6               | STADC            | I        | ADC external trigger input pin                                                                                                                                                                                                                                                                                         |  |  |  |

|                |               |                 | TM0_EXT          | I/O      | Timer 0 external capture / reset trigger input pin / toggle output pin                                                                                                                                                                                                                                                 |  |  |  |

|                |               |                 | ACMP1_P1         | AI       | Analog comparator positive input pin (not support in TSSOP20 package)                                                                                                                                                                                                                                                  |  |  |  |

|                |               |                 | P3.4             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

| 9              | 7             | 7               | TM0_CNT_OU<br>T  | I/O      | Timer 0 external event counter input pin / toggle output pin                                                                                                                                                                                                                                                           |  |  |  |

|                |               |                 | I2C0_SDA         | I/O      | I <sup>2</sup> C0 data I/O pin                                                                                                                                                                                                                                                                                         |  |  |  |

|                |               |                 | ACMP1_P2         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                   |  |  |  |

|                |               | 8               | P3.5             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

| 10             | 8             |                 | TM1_CNT_OU<br>T  | I/O      | Timer 1 external event counter input pin / toggle output pin                                                                                                                                                                                                                                                           |  |  |  |

|                |               |                 | I2C0_SCL         | I/O      | l <sup>2</sup> C0 clock I/O pin                                                                                                                                                                                                                                                                                        |  |  |  |

|                |               |                 | ACMP1_P3         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                   |  |  |  |

| 11             |               |                 | NC               |          | Not connected                                                                                                                                                                                                                                                                                                          |  |  |  |

Г

| Pin Number     |               |                 |            |          |                                    |  |  |  |

|----------------|---------------|-----------------|------------|----------|------------------------------------|--|--|--|

| LQFP<br>48-pin | QFN<br>33-pin | TSSOP<br>20-pin | Pin Name   | Pin Type | Description                        |  |  |  |

|                |               |                 | P2.5       | I/O      | General purpose digital I/O pin    |  |  |  |

| 25 17          |               | 13              | UART1_TXD  | 0        | UART1 transmitter output pin       |  |  |  |

|                |               |                 | PWM0_CH3   | 0        | PWM3 output of PWM unit            |  |  |  |

|                |               |                 | P2.6       | I/O      | General purpose digital I/O pin    |  |  |  |

| 26             | 18            |                 | PWM0_CH4   | 0        | PWM4 output of PWM unit            |  |  |  |

|                |               |                 | ACMP1_O    | 0        | Analog comparator output pin       |  |  |  |

| 27             |               |                 | NC         |          | Not connected                      |  |  |  |

| 28             |               |                 | NC         |          | Not connected                      |  |  |  |

|                |               |                 | P4.6       | I/O      | General purpose digital I/O pin    |  |  |  |

| 29             | 19            | 14              | ICE_CLK    | I        | Serial wired debugger clock pin    |  |  |  |

|                |               |                 | UART1_RXD  | I        | UART1 data receiver input pin      |  |  |  |

|                |               |                 | P4.7       | I/O      | General purpose digital I/O pin    |  |  |  |

| 30             | 20            | 15              | ICE_DAT    | I/O      | Serial wired debugger data pin     |  |  |  |

|                |               |                 | UART1_TXD  | 0        | UART1 transmitter output pin       |  |  |  |

| 31             |               |                 | NC         |          | Not connected                      |  |  |  |

|                |               |                 | P0.7       | I/O      | General purpose digital I/O pin    |  |  |  |

| 32 21          |               | 16              | SPI0_CLK   | I/O      | SPI serial clock pin               |  |  |  |

|                |               |                 | PWM0_CH0   | 0        | PWM0 output of PWM unit            |  |  |  |

|                |               |                 | P0.6       | I/O      | General purpose digital I/O pin    |  |  |  |

| 33 22          |               | 17              | SPI0_MISO  | I/O      | SPI MISO (master in/slave out) pin |  |  |  |

|                |               |                 | PWM0_CH1   | 0        | PWM1 output of PWM unit            |  |  |  |

|                |               |                 | P0.5       | I/O      | General purpose digital I/O pin    |  |  |  |

| 34             | 23            | 18              | SPI0_MOSI  | 0        | SPI MOSI (master out/slave in) pin |  |  |  |

|                |               |                 | PWM0_CH4   | 0        | PWM4 output of PWM unit            |  |  |  |

|                |               | 19              | P0.4       | I/O      | General purpose digital I/O pin    |  |  |  |

| 35             | 24            |                 | SPI0_SS    | I/O      | SPI slave select pin               |  |  |  |

|                |               |                 | PWM0_CH5   | 0        | PWM5 output of PWM unit            |  |  |  |

| 36             |               |                 | NC         |          | Not connected                      |  |  |  |

|                |               |                 | P0.1       | I/O      | General purpose digital I/O pin    |  |  |  |

| 07             | 05            |                 | UART0_nRTS | 0        | UART0 RTS pin                      |  |  |  |

| 37             | 25            |                 | UART0_RXD  | I        | UART0 data receiver input pin      |  |  |  |

|                |               |                 | SPI0_SS    | I/O      | SPI slave select pin               |  |  |  |

| 38             | 26            |                 | P0.0       | I/O      | General purpose digital I/O pin    |  |  |  |

|                |               |                 |            |          |                                    |  |  |  |

Ē

# **6** FUNCTIONAL DESCRIPTION

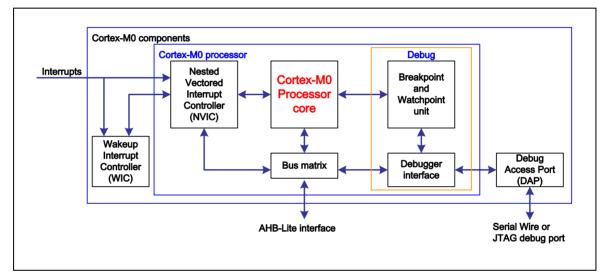

# 6.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 Core

### 6.1.1 Overview

The Cortex<sup>®</sup>-M0 processor, a configurable, multistage, 32-bit RISC processor, has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex<sup>®</sup>-M profile processors. The profile supports two modes - Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset and can be entered as a result of an exception return. Figure 6.1-1 shows the functional controller of the processor.

Figure 6.1-1 Functional Block Diagram

### 6.1.2 Features

- A low gate count processor

- ARMv6-M Thumb<sup>®</sup> instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- System interface supported with little-endian data accesses

- Ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model:

This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

Low power Idle mode entry using the Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or return from interrupt sleep-on-exit feature

# 6.2 System Manager

### 6.2.1 Overview

System management includes the following sections:

- System Reset

- System Power Architecture

- System Memory Map

- System management registers for Part Number ID, chip reset and on-chip controllers reset, and multi-functional pin control

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control registers

## 6.2.2 System Reset

The system reset can be issued by one of the events listed below. These reset event flags can be read from SYS\_RSTSTS register to determine the reset source. Hardware reset can reset chip through peripheral reset signals. Software reset can trigger reset through control registers.

- Hardware Reset Sources

- Power-on Reset (POR)

- Low level on the nRESET pin

- Watchdog Time-out Reset and Window Watchdog Reset (WDT/WWDT Reset)

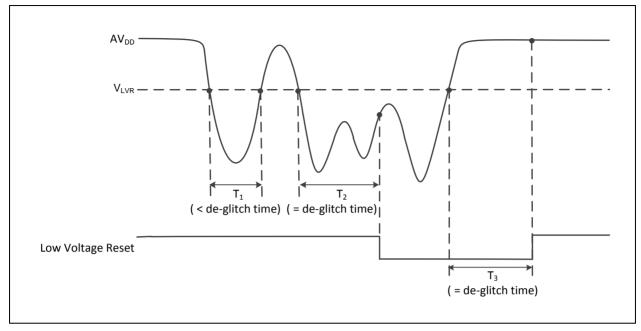

- Low Voltage Reset (LVR)

- Brown-out Detector Reset (BOD Reset)

- CPU Lockup Reset

- Software Reset Sources

- CHIP Reset will reset whole chip by writing 1 to CHIPRST (SYS\_IPRST0[0])

- MCU Reset to reboot but keeping the booting setting from APROM or LDROM by writing 1 to SYSRESETREQ (SCS\_AIRCR[2])

- CPU Reset for Cortex<sup>®</sup>-M0 core Only by writing 1 to CPURST (SYS\_IPRST0[1])

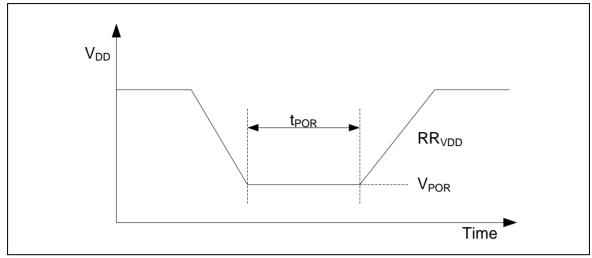

Figure 6.2-4 Low Voltage Reset (LVR) Waveform

### 6.2.2.4 Brown-out Detector Reset (BOD Reset)

If the Brown-out Detector (BOD) function is enabled by setting the Brown-out Detector Enable Bit BODEN (SYS\_BODCTL[0]), Brown-Out Detector function will detect  $AV_{DD}$  during system operation. When the  $AV_{DD}$  voltage is lower than  $V_{BOD}$  which is decided by BODEN (SYS\_BODCTL[0]) and BODVL (SYS\_BODCTL[2:1]) and the state keeps longer than De-glitch time (Max(20\*HCLK cycles, 1\*LIRC cycle)), chip will be reset. The BOD reset will control the chip in reset state until the  $AV_{DD}$  voltage rises above  $V_{BOD}$  and the state keeps longer than De-glitch time. The default value of BODEN, BODVL and BODRSTEN is set by flash controller user configuration register CBOVEXT (CONFIG0[23]), CBOV (CONFIG0[22:21]) and CBORST (CONFIG0[20]) respectively. User can determine the initial BOD setting by setting the CONFIG0 register. Figure 6.2-5 shows the Brown-Out Detector waveform.

(FMC\_ISPCTL[1]) bit is automatically reloaded from CONFIG setting. User can set the CHIPRST (SYS\_IPRST0[0]) to 1 to assert the CHIP Reset signal.

The MCU Reset is similar with CHIP Reset. The difference is that BS (FMC\_ISPCTL[1]) will not be reloaded from CONFIG setting and keep its original software setting for booting from APROM or LDROM. User can set the SYSRESETREQ (SCS\_AIRCR[2]) to 1 to assert the MCU Reset.

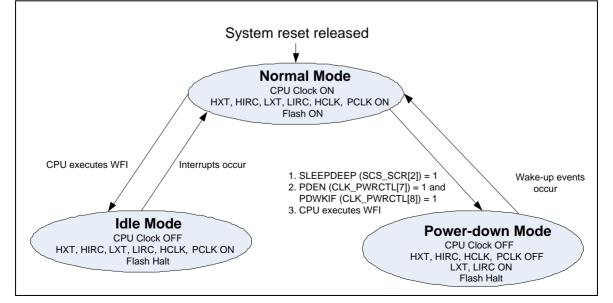

### 6.2.3 Power Modes and Wake-up Sources

There are several wake-up sources in Idle mode and Power-down mode. Table 6.2-2 lists the available clocks for each power mode.

| Power Mode       | Normal Mode                                              | Idle Mode                     | Power-down Mode                                                                                   |

|------------------|----------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------|

| Definition       | CPU is in active state                                   | CPU is in sleep state         | CPU is in sleep state<br>and all clocks stop<br>except LXT and LIRC.<br>SRAM content<br>retended. |

| Entry Condition  | Chip is in normal<br>mode after system<br>reset released | CPU executes WFI instruction. | CPU sets sleep mode<br>enable and power<br>down enable and<br>executes WFI<br>instruction.        |

| Wake-up Sources  | N/A                                                      | All interrupts                | WDT, I <sup>2</sup> C, Timer,<br>UART, BOD and<br>GPIO                                            |

| Available Clocks | All                                                      | All except CPU clock          | LXT and LIRC                                                                                      |

| After Wake-up    | N/A                                                      | CPU back to normal mode       | CPU back to normal mode                                                                           |

Table 6.2-2 Power Mode Difference Table

### Figure 6.2-6 Power Mode State Machine

| BOD              | Brown-Out Detector<br>Interrupt After software writes 1 to clear SYS_BODCTL[BODIF]. |                                                                                      |  |  |

|------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| GPIO             | GPIO Interrupt                                                                      | After software write 1 to clear the Px_INTSRC[n] bit.                                |  |  |

| TIMER            | Timer Interrupt                                                                     | After software writes 1 to clear TWKF (TIMERx_INTSTS[1]) and TIF (TIMERx_INTSTS[0]). |  |  |

| WDT              | WDT Interrupt                                                                       | After software writes 1 to clear WKF (WDT_CTL[5]) (Write Protect).                   |  |  |

| UART             | nCTS wake-up                                                                        | After software writes 1 to clear CTSWKIF (UARTx_INTSTS[16]).                         |  |  |

| l <sup>2</sup> C | Falling edge in the I2C_SDA or I2C_CLK                                              | After software writes 1 to clear WKIF ( I2C_STATUS1[0]).                             |  |  |

Table 6.2-4 Condition of Entering Power-down Mode Again

### 6.2.4 System Power Architecture

In this chip, the power distribution is divided into three segments.

- Analog power from AV<sub>DD</sub> and AV<sub>SS</sub> provides the power for analog components operation. AV<sub>DD</sub> must be equal to V<sub>DD</sub> to avoid leakage current.

- Digital power from V<sub>DD</sub> and V<sub>SS</sub> supplies power to the I/O pins and internal regulator which provides a fixed 1.8V power for digital operation.

- Built-in a capacitor for internal voltage regulator

The output of internal voltage regulator, LDO\_CAP, requires an external capacitor which should be located close to the corresponding pin. Analog power ( $AV_{DD}$ ) should be the same voltage level as the digital power ( $V_{DD}$ ). Figure 6.2-7 shows the power distribution of the Mini58 series.

### 6.2.6.2 System Memory Map

The memory locations assigned to each on-chip controllers are shown in the following table.

| Addressing Space                                 | Token            | Modules                                          |  |  |  |  |

|--------------------------------------------------|------------------|--------------------------------------------------|--|--|--|--|

| Flash and SRAM Memory Space                      |                  |                                                  |  |  |  |  |

| 0x0000_0000 – 0x0000_7FFF                        | FLASH_BA         | Flash Memory Space (32 KB)                       |  |  |  |  |

| 0x2000_0000 – 0x2000_0FFF                        | SRAM_BA          | SRAM Memory Space (4 KB)                         |  |  |  |  |

| AHB Modules Space (0x5000_000                    | ) – 0x501F_FFFF) | ·                                                |  |  |  |  |

| 0x5000_0000 – 0x5000_01FF                        | SYS_BA           | System Global Control Registers                  |  |  |  |  |

| 0x5000_0200 – 0x5000_02FF                        | CLK_BA           | Clock Control Registers                          |  |  |  |  |

| 0x5000_0300 – 0x5000_03FF                        | INT_BA           | Interrupt Multiplexer Control Registers          |  |  |  |  |

| 0x5000_4000 – 0x5000_7FFF                        | GP_BA            | GPIO (P0~P5) Control Registers                   |  |  |  |  |

| 0x5000_C000 - 0x5000_FFFF                        | FMC_BA           | Flash Memory Control Registers                   |  |  |  |  |

| APB Modules Space (0x4000_0000                   | – 0x401F_FFFF)   | ·                                                |  |  |  |  |

| 0x4000_4000 – 0x4000_00FF                        | WDT_BA           | Watchdog Timer Control Registers                 |  |  |  |  |

| 0x4000_4100 – 0x4000_47FF                        | WWDT_BA          | Window Watchdog Timer Control Registers          |  |  |  |  |

| 0x4001_0000 – 0x4001_3FFF                        | TMR_BA           | Timer0/Timer1 Control Registers                  |  |  |  |  |

| 0x4002_0000 – 0x4002_3FFF                        | I2C0_BA          | I <sup>2</sup> C0 Interface Control Registers    |  |  |  |  |

| 0x4003_0000 – 0x4003_3FFF                        | SPI_BA           | SPI with Master/slave Function Control Registers |  |  |  |  |

| 0x4004_0000 – 0x4004_3FFF                        | PWM_BA           | PWM Control Registers                            |  |  |  |  |

| 0x4005_0000 – 0x4005_3FFF                        | UART0_BA         | UART0 Control Registers                          |  |  |  |  |

| 0x400D_0000 – 0x400D_3FFF                        | ACMP_BA          | Analog Comparator Control Registers              |  |  |  |  |

| 0x400E_0000 – 0x400E_3FFF                        | ADC_BA           | Analog-Digital-Converter (ADC) Control Registers |  |  |  |  |

| 0x4012_0000 – 0x4012_3FFF                        | I2C1_BA          | I <sup>2</sup> C1 Interface Control Registers    |  |  |  |  |

| 0x4015_0000 – 0x4015_3FFF                        | UART1_BA         | UART1 Control Registers                          |  |  |  |  |

| System Control Space (0xE000_E000 – 0xE000_EFFF) |                  |                                                  |  |  |  |  |

| 0xE000_E010 – 0xE000_E0FF                        | SCS_BA           | System Timer Control Registers                   |  |  |  |  |

| 0xE000_E100 - 0xE000_ECFF                        | SCS_BA           | Nested Vectored Interrupt Control Registers      |  |  |  |  |

| 0xE000_ED00 – 0xE000_ED8F                        | SCS_BA           | System Control Block Registers                   |  |  |  |  |

Table 6.2-6 Address Space Assignments for On-Chip Modules

# MINI58DE

# nuvoTon

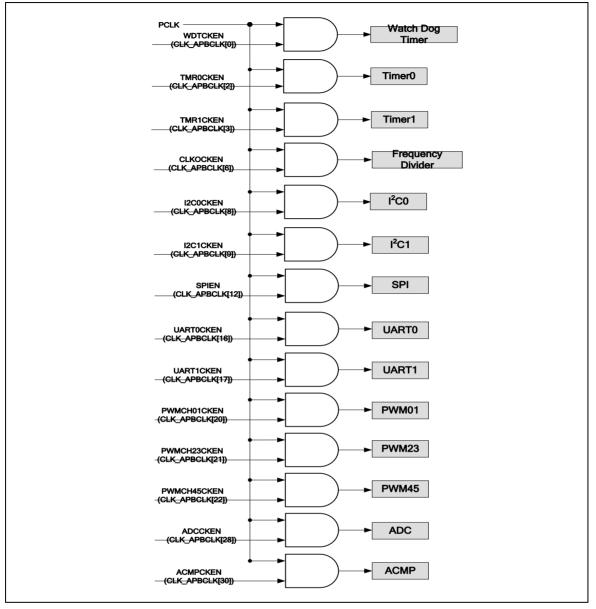

Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK

## 6.4 Flash Memory Controller (FMC)

#### 6.4.1 Overview

The NuMicro<sup>®</sup> Mini58 series is equipped with 32 Kbytes on-chip embedded flash for application and Data Flash to store some application dependent data. A User Configuration block provides for system initialization. A 2.5 Kbytes loader ROM (LDROM) is used for In-System-Programming (ISP) function. A 512 bytes security protection ROM (SPROM) can conceal user program. This chip also supports In-Application-Programming (IAP) function, user switches the code executing without the chip reset after the embedded flash updated.

### 6.4.2 Features

- Supports 32 Kbytes application ROM (APROM).

- Supports 2.5 Kbytes loader ROM (LDROM).

- Supports configurable Data Flash size to share with APROM.

- Supports 512 bytes security protection ROM (SPROM) to conceal user program.

- Supports 12 bytes User Configuration block to control system initialization.

- Supports 512 bytes page erase for all embedded flash.

- Supports CRC-32 checksum calculation function.

- Supports In-System-Programming (ISP) / In-Application-Programming (IAP) to update embedded flash memory.

- Each pin of PWM0\_CH0 to PWM0\_CH5 has independent polarity setting control

- Hardware fault brake protections

- Supports software trigger

- Two Interrupt source types:

- Synchronously requested at PWM frequency when down counter comparison matched (edge- and center-aligned type) or underflow (edgealigned type)

- Requested when external fault brake asserted

- BKP0: EINT0 or CPO1

- BKP1: EINT1 or CPO0

- The PWM signals before polarity control stage are defined in the view of positive logic. The PWM ports is active high or active low are controlled by polarity control register

- Supports mask aligned function

- Supports independently rising CMP matching, PERIOD matching, falling CMP matching (in Center-aligned type), period matching to trigger ADC conversion

- Timer comparing matching event trigger PWM to do phase change in BLDC application

- Supports ACMP output event trigger PWM to force PWM output at most one period low, this feature is usually for step motor control

- Provides interrupt accumulation function

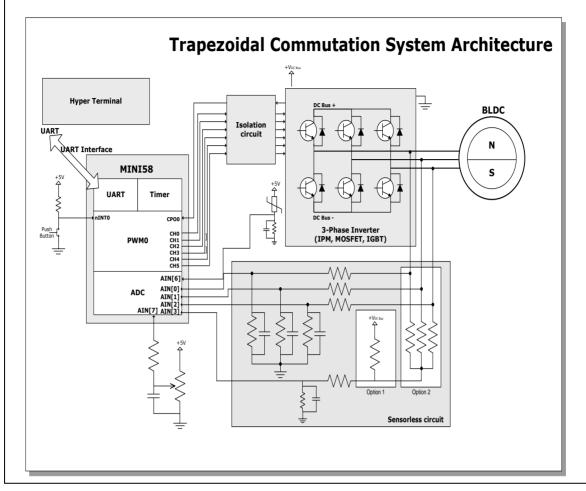

Figure 6.7-1 Application Circuit Diagram

# 6.11 I<sup>2</sup>C Serial Interface Controller (I<sup>2</sup>C)

### 6.11.1 Overview

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method for data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously. There are two sets of  $I^2C$  controller and only  $I^2C0$  supports Power-down wake-up function.

### 6.11.2 Features

The I<sup>2</sup>C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus include:

- Supports up to two I<sup>2</sup>C ports

- Master/Slave mode

- Bi-directional data transfer between masters and slaves

- Multi-master bus

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allowing devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Built-in 14-bit time-out counter that requests the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows

- Programmable clocks allowing for versatile rate control

- Supports 7-bit addressing mode

- Supports multiple address recognition (four slave address registers with mask option)

- Supports Power-down wake-up function (Only I<sup>2</sup>C0 channel support this function)

- Supports two-level buffer function

## 6.12 Serial Peripheral Interface (SPI)

### 6.12.1 Overview

The Serial Peripheral Interface (SPI) applies to synchronous serial data communication and allows full duplex transfer. Devices communicate in Master/Slave mode with 4-wire bi-direction interface. The SPI controller performing a serial-to-parallel conversion on data received from a peripheral device, and a parallel-to-serial conversion on data transmitted to a peripheral device. SPI controller can be configured as a master or a slave device.

### 6.12.2 Features

- Supports Master or Slave mode operation

- Configurable transfer bit length

- Provides four 32-bit FIFO buffers

- Supports MSB first or LSB first transfer

- Supports byte reorder function

- Supports byte or word suspend mode

- Supports Slave 3-wire mode

## 6.14 Analog Comparator (ACMP)

### 6.14.1 Overview

The NuMicro<sup>®</sup> Mini58 series contains two comparators which can be used in a number of different configurations. The comparator output is logic 1 when positive input is greater than negative input, otherwise the output is 0. Each comparator can be configured to generate interrupt when the comparator output value changes.

### 6.14.2 Features

- Analog input voltage range: 0 ~ AV<sub>DD</sub>

- Supports Hysteresis function

- Optional internal reference voltage source for each comparator negative input

- ACMP0 supports:

- Four positive sources

- P1.5, P1.0, P1.2, or P1.3

- Three negative sources

- P1.4

- Internal Comparator Reference Voltage (CRV)

- Internal band-gap voltage (V<sub>BG</sub>)

- ACMP1 supports:

- Four positive sources

- P3.1, P3.2, P3.4, or P3.5

- Three negative sources

- P3.0

- Internal Comparator Reference Voltage (CRV)

- Internal band-gap voltage (V<sub>BG</sub>)

## 8 ELECTRICAL CHARACTERISTICS

## 8.1 Absolute Maximum Ratings

| Symbol              | Parameter                                 | Min                  | Мах                  | Unit |

|---------------------|-------------------------------------------|----------------------|----------------------|------|

| $V_{DD} - V_{SS}$   | DC Power Supply                           | -0.3                 | +7.0                 | V    |

| V <sub>IN</sub>     | Input Voltage                             | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                      | 4                    | 24                   | MHz  |

| T <sub>A</sub>      | Operating Temperature                     | -40                  | +105                 | °C   |

| T <sub>s⊤</sub>     | Storage Temperature                       | -55                  | +150                 | °C   |

| I <sub>DD</sub>     | Maximum Current into V <sub>DD</sub>      | -                    | 120                  | mA   |

| I <sub>SS</sub>     | Maximum Current out of $V_{SS}$           | -                    | 120                  | mA   |

|                     | Maximum Current sunk by an I/O pin        | -                    | 35                   | mA   |

| I <sub>IO</sub>     | Maximum Current sourced by an I/O pin     | -                    | 35                   | mA   |

|                     | Maximum Current sunk by total I/O pins    | -                    | 100                  | mA   |

|                     | Maximum Current sourced by total I/O pins | -                    | 100                  | mA   |

**Note:** Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the life and reliability of the device.

### 2. XTAL1 is a CMOS input.

3. Pins of P0, P1, P2, P3, P4 and P5 can source a transition current when they are being externally driven from 1 to 0. In the condition of  $V_{DD}$ =5.5V, the transition current reaches its maximum value when  $V_{IN}$  approximates to 2V.

4. Only enable modules which support 10 kHz LIRC clock source

Figure 8.4-1 Power-up Ramp Condition

## 8.4.6 Comparator

| Symbol           | Parameter               | Min | Тур | Мах                   | Unit | Test Condition                                       |

|------------------|-------------------------|-----|-----|-----------------------|------|------------------------------------------------------|

| V <sub>CMP</sub> | Supply Voltage          | 2.5 | -   | 5.5                   | V    |                                                      |

| T <sub>A</sub>   | Temperature             | -40 | 25  | 105                   | °C   | -                                                    |

| I <sub>CMP</sub> | Operation Current       | -   | 40  | 80                    | μA   | AV <sub>DD</sub> =5V                                 |

| V <sub>OFF</sub> | Input Offset Voltage    |     | 10  | 20                    | mV   | -                                                    |

| V <sub>SW</sub>  | Output Swing            | 0.1 | -   | $AV_{DD} - 0.1$       | V    | -                                                    |

| V <sub>COM</sub> | Input Common Mode Range | 0.1 | -   | AV <sub>DD</sub> -0.1 | V    | -                                                    |

| -                | DC Gain                 | 40  | 70  | -                     | dB   | -                                                    |

| T <sub>PGD</sub> | Propagation Delay       | -   | 200 | -                     | ns   | V <sub>COM</sub> =1.2 V,<br>V <sub>DIFF</sub> =0.1 V |

| V <sub>HYS</sub> | Hysteresis              | -   | ±30 | ±60                   | mV   | V <sub>COM</sub> =1.2 V                              |

| Т <sub>STB</sub> | Stable time             | -   | -   | 1                     | μs   |                                                      |