Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | ARM® Cortex®-M0                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 50MHz                                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                                      |

| Number of I/O              | 29                                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 4K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 32-WFQFN Exposed Pad                                                                  |

| Supplier Device Package    | 33-QFN (5x5)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/mini58zde |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **3 ABBREVIATIONS**

| Acronym | Description                                      |

|---------|--------------------------------------------------|

| ACMP    | Analog Comparator Controller                     |

| ADC     | Analog-to-Digital Converter                      |

| АНВ     | Advanced High-Performance Bus                    |

| APB     | Advanced Peripheral Bus                          |

| BOD     | Brown-out Detection                              |

| DAP     | Debug Access Port                                |

| FIFO    | First In, First Out                              |

| FMC     | Flash Memory Controller                          |

| GPIO    | General-Purpose Input/Output                     |

| HCLK    | The Clock of Advanced High-Performance Bus       |

| HIRC    | 22.1184 MHz Internal High Speed RC Oscillator    |

| НХТ     | 4~24 MHz External High Speed Crystal Oscillator  |

| ICP     | In Circuit Programming                           |

| ISP     | In System Programming                            |

| ISR     | Interrupt Service Routine                        |

| LDO     | Low Dropout Regulator                            |

| LIRC    | 10 kHz internal low speed RC oscillator (LIRC)   |

| LXT     | 32.768 kHz External Low Speed Crystal Oscillator |

| NVIC    | Nested Vectored Interrupt Controller             |

| PCLK    | The Clock of Advanced Peripheral Bus             |

| PLL     | Phase-Locked Loop                                |

| PWM     | Pulse Width Modulation                           |

| SPI     | Serial Peripheral Interface                      |

| SPS     | Samples per Second                               |

| TMR     | Timer Controller                                 |

| UART    | Universal Asynchronous Receiver/Transmitter      |

| UCID    | Unique Customer ID                               |

| WDT     | Watchdog Timer                                   |

| WWDT    | Window Watchdog Timer                            |

Table 3-1 List of Abbreviations

| Part Number | APROM | DAM   | Data Flash Loader I/O Timer Connectivity | Comp   | Comp. PWM |              | PWM ADC | ISP 22 | IRC<br>22.1184   | Deskore |        |              |     |     |            |

|-------------|-------|-------|------------------------------------------|--------|-----------|--------------|---------|--------|------------------|---------|--------|--------------|-----|-----|------------|

| Fart Number | APROW | KAIVI | Data FidSh                               | ROM    | 1/0       |              | UART    | SPI    | I <sup>2</sup> C | comp.   | PVVIVI | ADC          | ICP | MHz | Package    |

| MINI58LDE   | 32 KB | 4 KB  | Configurable                             | 2.5 KB | up to 30  | 2x32-<br>bit | 2       | 1      | 2                | 2       | 6      | 8x10-<br>bit | v   | v   | LQFP48     |

| MINI58ZDE   | 32 KB | 4 KB  | Configurable                             | 2.5 KB | up to 29  | 2x32-<br>bit | 2       | 1      | 2                | 2       | 6      | 8x10-<br>bit | v   | v   | QFN33(5x5) |

| MINI58TDE   | 32 KB | 4 KB  | Configurable                             | 2.5 KB | up to 29  | 2x32-<br>bit | 2       | 1      | 2                | 2       | 6      | 8x10-<br>bit | v   | v   | QFN33(4x4) |

| MINI58FDE   | 32 KB | 4 KB  | Configurable                             | 2.5 KB | up to 17  | 2x32-<br>bit | 2       | 1      | 2                | -       | 6      | 4x10-<br>bit | v   | v   | TSSOP20    |

## 4.2 NuMicro<sup>®</sup> Mini58 Series Product Selection Guide

Table 4.2-1 NuMicro<sup>®</sup> Mini58 Series Product Selection Guide

### 4.3 PIN CONFIGURATION

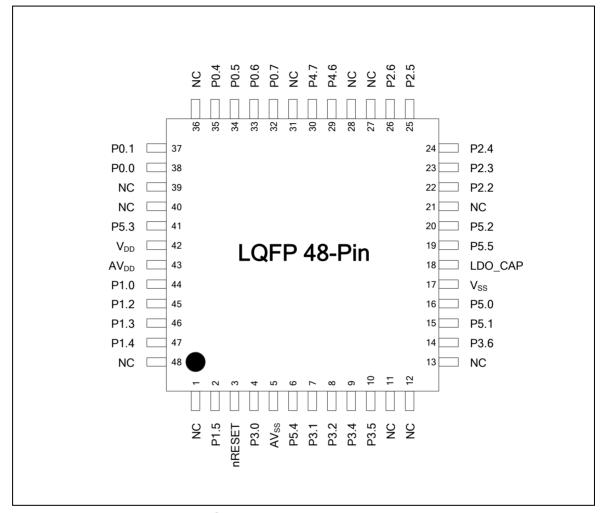

### 4.3.1 LQFP 48-pin

Figure 4.3-1 NuMicro<sup>®</sup> Mini58 Series LQFP 48-pin Diagram

## 4.4 Pin Description

| F              | in Numbe      | r               |                  |          |                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------------|---------------|-----------------|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LQFP<br>48-pin | QFN<br>33-pin | TSSOP<br>20-pin | Pin Name         | Pin Type | Description                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1              |               |                 | NC               |          | Not connected                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                |               |                 | P1.5             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

|                | 4             | 4               | ADC_CH5          | AI       | ADC analog input pin                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2              | 1             | 4               | UART1_TXD        | 0        | UART1 transmitter output pin                                                                                                                                                                                                                                                                                                       |  |  |  |

|                |               |                 | ACMP0_P0         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                               |  |  |  |

| 3              | 2             | 5               | nRESET           | I(ST)    | The Schmitt trigger input pin for hardware device reset. A " <b>Low</b> "<br>on this pin for 768 clock counter of Internal RC 22.1184 MHz while<br>the system clock is running will reset the device. nRESET pin has<br>an internal pull-up resistor allowing power-on reset by simply<br>connecting an external capacitor to GND. |  |  |  |

|                |               |                 | P3.0             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

| 4              | 3             |                 | ADC_CH6          | AI       | ADC analog input pin                                                                                                                                                                                                                                                                                                               |  |  |  |

|                |               |                 | ACMP1_N          | AI       | Analog comparator negative input pin                                                                                                                                                                                                                                                                                               |  |  |  |

| 5              |               |                 | AV <sub>SS</sub> | AP       | Ground pin for analog circuit                                                                                                                                                                                                                                                                                                      |  |  |  |

| 6              | 4             |                 | P5.4             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

|                |               |                 | P3.1             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

| 7              | 5             |                 | ADC_CH7          | AI       | ADC analog input pin                                                                                                                                                                                                                                                                                                               |  |  |  |

|                |               |                 | ACMP1_P0         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                               |  |  |  |

|                |               |                 | P3.2             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

|                |               |                 | INT0             | I        | External interrupt 0 input pin                                                                                                                                                                                                                                                                                                     |  |  |  |

| 8              | 6             | 6               | STADC            | I        | ADC external trigger input pin                                                                                                                                                                                                                                                                                                     |  |  |  |

|                |               |                 | TM0_EXT          | I/O      | Timer 0 external capture / reset trigger input pin / toggle output pin                                                                                                                                                                                                                                                             |  |  |  |

|                |               |                 | ACMP1_P1         | AI       | Analog comparator positive input pin (not support in TSSOP20 package)                                                                                                                                                                                                                                                              |  |  |  |

|                |               |                 | P3.4             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

| 9              | 7             | 7               | TM0_CNT_OU<br>T  | I/O      | Timer 0 external event counter input pin / toggle output pin                                                                                                                                                                                                                                                                       |  |  |  |

|                |               |                 | I2C0_SDA         | I/O      | I <sup>2</sup> C0 data I/O pin                                                                                                                                                                                                                                                                                                     |  |  |  |

|                |               |                 | ACMP1_P2         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                               |  |  |  |

|                |               |                 | P3.5             | I/O      | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

| 10             | 8             | 8               | TM1_CNT_OU<br>T  | I/O      | Timer 1 external event counter input pin / toggle output pin                                                                                                                                                                                                                                                                       |  |  |  |

|                |               |                 | I2C0_SCL         | I/O      | l <sup>2</sup> C0 clock I/O pin                                                                                                                                                                                                                                                                                                    |  |  |  |

|                |               |                 | ACMP1_P3         | AI       | Analog comparator positive input pin                                                                                                                                                                                                                                                                                               |  |  |  |

| 11             |               |                 | NC               |          | Not connected                                                                                                                                                                                                                                                                                                                      |  |  |  |

- NVIC

- 32 external interrupt inputs, each with four levels of priority

- Dedicated Non-maskable Interrupt (NMI) input

- Supports for both level-sensitive and pulse-sensitive interrupt lines

- Supports Wake-up Interrupt Controller (WIC) and, providing Ultra-low Power Idle mode

- Debug support

- Four hardware breakpoints

- Two watch points

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling

- Single step and vector catch capabilities

- Bus interfaces

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory

- Single 32-bit slave port that supports the DAP (Debug Access Port)

(FMC\_ISPCTL[1]) bit is automatically reloaded from CONFIG setting. User can set the CHIPRST (SYS\_IPRST0[0]) to 1 to assert the CHIP Reset signal.

The MCU Reset is similar with CHIP Reset. The difference is that BS (FMC\_ISPCTL[1]) will not be reloaded from CONFIG setting and keep its original software setting for booting from APROM or LDROM. User can set the SYSRESETREQ (SCS\_AIRCR[2]) to 1 to assert the MCU Reset.

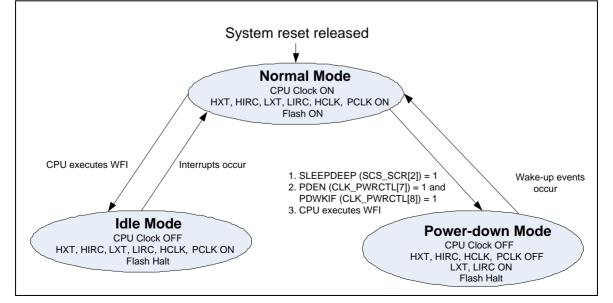

#### 6.2.3 Power Modes and Wake-up Sources

There are several wake-up sources in Idle mode and Power-down mode. Table 6.2-2 lists the available clocks for each power mode.

| Power Mode       | Normal Mode                                              | Idle Mode                     | Power-down Mode                                                                                   |

|------------------|----------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------|

| Definition       | CPU is in active state                                   | CPU is in sleep state         | CPU is in sleep state<br>and all clocks stop<br>except LXT and LIRC.<br>SRAM content<br>retended. |

| Entry Condition  | Chip is in normal<br>mode after system<br>reset released | CPU executes WFI instruction. | CPU sets sleep mode<br>enable and power<br>down enable and<br>executes WFI<br>instruction.        |

| Wake-up Sources  | N/A                                                      | All interrupts                | WDT, I <sup>2</sup> C, Timer,<br>UART, BOD and<br>GPIO                                            |

| Available Clocks | All                                                      | All except CPU clock          | LXT and LIRC                                                                                      |

| After Wake-up    | N/A                                                      | CPU back to normal mode       | CPU back to normal mode                                                                           |

Table 6.2-2 Power Mode Difference Table

#### Figure 6.2-6 Power Mode State Machine

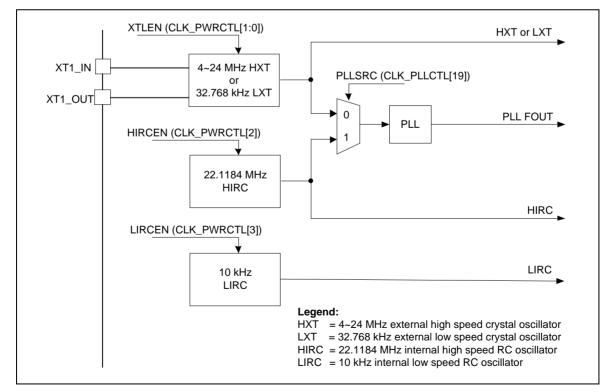

### 6.3 Clock Controller

#### 6.3.1 Overview

The clock controller generates clocks for the whole chip, including system clocks and all peripheral clocks. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and clock divider. The chip enters Power-down mode when Cortex<sup>®</sup>-M0 core executes the WFI instruction only if the PDEN (CLK\_PWRCTL[7]) bit is set to 1. After that, chip enters Power-down mode and waits for wake-up interrupt source triggered to exit Power-down mode. In Power-down mode, the clock controller turns off the 4~24 MHz external high speed crystal (HXT) and 22.1184 MHz internal high speed RC oscillator (HIRC) to reduce the overall system power consumption. The following figures show the clock generator and the overview of the clock source control.

The clock generator consists of 3 sources as listed below:

- 4~24 MHz external high speed crystal oscillator (HXT) or 32.768 kHz (LXT) external low speed crystal oscillator

- Programmable PLL output clock frequency (PLL source can be selected from external 4 ~ 24 MHz external high speed crystal (HXT) or 22.1184 MHz internal high speed oscillator (HIRC)) (PLL FOUT)

- 22.1184 MHz internal high speed RC oscillator (HIRC)

- 10 kHz internal low speed RC oscillator (LIRC)

Figure 6.3-1 Clock Generator Block Diagram

|                   | Peripheral Clok<br>Selectable | Ext. CLK (HXT Or<br>LXT) | HIRC | LIRC | HCLK | PLL |

|-------------------|-------------------------------|--------------------------|------|------|------|-----|

| WDT               | Yes                           | Yes                      | No   | Yes  | Yes  | No  |

| WWDT              | Yes                           | Yes                      | No   | Yes  | Yes  | No  |

| Timer0            | Yes                           | Yes                      | Yes  | Yes  | Yes  | No  |

| Timer1            | Yes                           | Yes                      | Yes  | Yes  | Yes  | No  |

| I <sup>2</sup> C0 | No                            | -                        | -    | -    | -    | -   |

| l <sup>2</sup> C1 | No                            | -                        | -    | -    | -    | -   |

| SPI               | Yes                           | Yes                      | No   | No   | Yes  | Yes |

| UART0             | Yes                           | Yes                      | Yes  | No   | No   | Yes |

| UART1             | Yes                           | Yes                      | Yes  | No   | No   | Yes |

| PWM               | No                            | -                        | -    | -    | -    | -   |

| ADC               | Yes                           | Yes                      | Yes  | No   | Yes  | Yes |

| ACMP              | No                            | -                        | -    | -    | -    | -   |

Table 6.3-1 Peripheral Clock Source Selection Table

**Note:** For the peripherals those peripheral clock are not selectable, its clock source is fixed to PCLK.

#### 6.3.5 Power-down Mode Clock

When chip enters Power-down mode, system clocks, some clock sources, and some peripheral clocks will be disabled. Some clock sources and peripheral clocks are still active in Power-down mode.

The clocks still kept active are listed below:

- **Clock Generator**

- 10 kHz internal low speed oscillator (LIRC) clock

- 32.768 kHz external low speed crystal oscillator (LXT) clock (If PDLXT = 1 and XTLEN[1:0] = 10)

- Peripherals Clock (When 10 kHz low speed oscillator is adopted as clock source)

- Watchdog Clock

- Timer 0/1 Clock

#### 6.3.6 Frequency Divider Output

This device is equipped with a power-of-2 frequency divider which is composed of 16 chained divide-by-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to the CLKO pin. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^1$  to  $F_{in}/2^{16}$  where  $F_{in}$  is input clock frequency to the clock divider.

- Each pin of PWM0\_CH0 to PWM0\_CH5 has independent polarity setting control

- Hardware fault brake protections

- Supports software trigger

- Two Interrupt source types:

- Synchronously requested at PWM frequency when down counter comparison matched (edge- and center-aligned type) or underflow (edgealigned type)

- Requested when external fault brake asserted

- BKP0: EINT0 or CPO1

- BKP1: EINT1 or CPO0

- The PWM signals before polarity control stage are defined in the view of positive logic. The PWM ports is active high or active low are controlled by polarity control register

- Supports mask aligned function

- Supports independently rising CMP matching, PERIOD matching, falling CMP matching (in Center-aligned type), period matching to trigger ADC conversion

- Timer comparing matching event trigger PWM to do phase change in BLDC application

- Supports ACMP output event trigger PWM to force PWM output at most one period low, this feature is usually for step motor control

- Provides interrupt accumulation function

## 6.10 UART Controller (UART)

#### 6.10.1 Overview

The NuMicro<sup>®</sup> Mini58 series provides two channels of Universal Asynchronous Receiver/Transmitters (UART). The UART0 performs supports flow control function. The UART0 performs a serial-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU. The UART0 controller also supports IrDA SIR Function, and RS-485 function mode. The UART0 channel supports six types of interrupts. The UART1 channel supports five types of interrupts. The UART1 channel supports five types of interrupts. The UART1 conversion on data received from the peripheral, and a parallel-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU. The UART1 only performs a serial-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU. The UART0 has 16 bytes Receiver/Transmitter FIFO. The UART1 only has one Receiver/Transmitter buffer.

#### 6.10.2 Features

- Full duplex, asynchronous communications

- Separates receive/transmit 16/16 bytes entry FIFO for data payloads (Only Available in UART0)

- Separates receive/transmit 1/1 byte buffer for data payloads (Only Available in UART1)

- Supports hardware auto flow control/flow control function (CTS, RTS) and programmable RTS flow control trigger level (Only Available in UART0)

- Programmable receiver buffer trigger level (Only Available in UART0)

- Supports programmable baud-rate generator for each channel individually

- Supports CTS wake-up function (Only Available in UART0)

- Supports 8-bit receiver buffer time-out detection function

- Programmable transmitting data delay time between the last stop and the next start bit by setting UART\_TOUT[15:8] register

- Supports break error, frame error, parity error and receive/transmit buffer overflow detection function

- Fully programmable serial-interface characteristics

- Programmable number of data bit, 5, 6, 7, 8 character

- Programmable parity bit, even, odd, no parity or stick parity bit generation and detection

- Programmable stop bit, 1, 1.5, or 2 stop bit generation

- Supports IrDA SIR function mode (Only Available in UART0)

- Supports 3/16-bit duration for normal mode

- Supports RS-485 function mode (Only Available in UART0)

- Supports RS-485 9-bit mode

- Supports hardware or software enable to program RTS pin to control RS-485 transmission directly

### 6.13 Analog-to-Digital Converter (ADC)

#### 6.13.1 Overview

The Mini58 series contains one 10-bit successive approximation analog-to-digital converters (SAR A/D converter) with eight input channels. The A/D converters can be started by software, external pin (STADC/P3.2) or PWM trigger.

#### 6.13.2 Features

- Analog input voltage range: 0 ~ Analog Supply Voltage from AV<sub>DD</sub>

- 10-bit resolution and 8-bit accuracy is guaranteed

- Up to eight single-end analog input channels

- Maximum ADC clock frequency is 6 MHz, and 14 ADC clocks per sample

- Two operating modes

- Single mode: A/D conversion is performed one time on a specified channel

- PWM sequence mode: When PWM trigger, two of three ADC channels from 0 to 2 will automatically convert analog data in the sequence of channel [0,1] or channel[1,2] or channel[0,2] defined by MODESEL (ADC\_SEQCTL[3:2])

- An A/D conversion can be started by:

- Software write 1 to SWTRG bit

- External pin STADC

- PWM trigger with optional start delay period

- Each Conversion result is held in data register with valid and overrun indicators

- Conversion results can be compared with specified value and user can select whether to generate an interrupt when conversion result matches the compare register setting

- Channel 7 supports 2 input sources: External analog voltage and internal fixed bandgap voltage

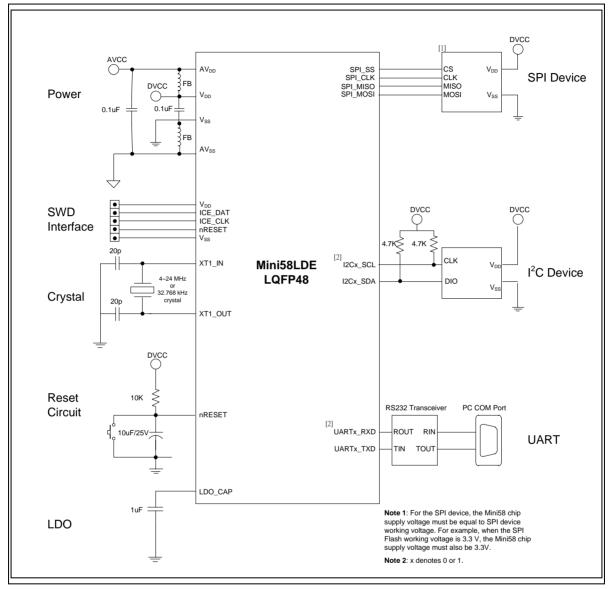

## 7 APPLICATION CIRCUIT

May. 09, 2018

| I <sub>IDLE8</sub>   |                                                                      | - | 2.265 | -   | mA | 3.3V                            | х                                                               | V               | х        | х                      |

|----------------------|----------------------------------------------------------------------|---|-------|-----|----|---------------------------------|-----------------------------------------------------------------|-----------------|----------|------------------------|

| I <sub>IDLE9</sub>   |                                                                      | _ | 4.577 |     | mA | V <sub>DD</sub>                 | нхт                                                             | HIRC            | PLL      | All Digital<br>Modules |

| IDLE9                | Operating Current                                                    |   |       |     |    | 5.5V                            | V                                                               | х               | х        | V                      |

| I <sub>IDLE10</sub>  | Idle Mode<br>HCLK =12 MHz                                            | - | 3.364 | -   | mA | 5.5V                            | V                                                               | х               | х        | Х                      |

| I <sub>IDLE11</sub>  |                                                                      | - | 3.062 | -   | mA | 3.3V                            | V                                                               | х               | х        | V                      |

| I <sub>IDLE12</sub>  |                                                                      | - | 1.871 | -   | mA | 3.3V                            | V                                                               | х               | Х        | х                      |

| I <sub>IDLE13</sub>  |                                                                      | - | 2.838 | -   | mA | V <sub>DD</sub>                 | нхт                                                             | HIRC            | PLL      | All Digital<br>Modules |

|                      | Operating Current                                                    |   |       |     |    | 5.5V                            | V                                                               | х               | х        | V                      |

| I <sub>IDLE14</sub>  | Idle Mode<br>HCLK = 4 MHz                                            | - | 2.433 | -   | mA | 5.5V                            | V                                                               | х               | х        | х                      |

| I <sub>IDLE15</sub>  |                                                                      | - | 1.446 | -   | mA | 3.3V                            | V                                                               | х               | Х        | V                      |

| I <sub>IDLE16</sub>  |                                                                      | - | 1.048 | -   | mA | 3.3V                            | V                                                               | х               | х        | х                      |

| I <sub>IDLE17</sub>  |                                                                      | - | 167   | -   | μA | V <sub>DD</sub>                 | LXT                                                             | HIRC            | PLL      | All Digital<br>Modules |

|                      | Operating Current                                                    |   |       |     |    | 5.5V                            | V                                                               | х               | х        | V                      |

| I <sub>IDLE18</sub>  | Idle Mode<br>HCLK = 32.768 kHz                                       | - | 166   | -   | μA | 5.5V                            | V                                                               | х               | х        | х                      |

| I <sub>IDLE19</sub>  |                                                                      | - | 150   | -   | μA | 3.3V                            | V                                                               | х               | х        | V                      |

| I <sub>IDLE20</sub>  |                                                                      | - | 149   | -   | μA | 3.3V                            | V                                                               | х               | х        | х                      |

| I <sub>IDLE 21</sub> |                                                                      | _ | 167   | -   | μA | V <sub>DD</sub>                 | нхт                                                             | LIRC            | PLL      | All Digital<br>Modules |

|                      | Operating Current                                                    |   |       |     |    | 5.5V                            | х                                                               | V               | х        | V <sup>[4]</sup>       |

| I <sub>IDLE 22</sub> | Idle Mode<br>HCLK = 10 kHz                                           | - | 166   | -   | μA | 5.5V                            | х                                                               | V               | х        | х                      |

| I <sub>IDLE 23</sub> |                                                                      | - | 150   | -   | μA | 3.3V                            | х                                                               | V               | х        | V <sup>[4]</sup>       |

| IIDLE 24             |                                                                      | - | 149   | -   | μA | 3.3V                            | х                                                               | V               | х        | х                      |

| I <sub>PWD1</sub>    | Standby Current                                                      | - | 6.2   | -   | μΑ | V <sub>DD</sub> = 5<br>blocks t | .5 V, All<br>turned of                                          | oscillato<br>f. | rs and a | nalog                  |

| I <sub>PWD2</sub>    | (Deep Sleep Mode)                                                    | - | 5.8   | -   | μA |                                 | $V_{DD}$ = 3.3 V, All oscillators and analog blocks turned off. |                 |          |                        |

| I <sub>IL</sub>      | Logic 0 Input Current<br>P0/1/2/3/4/5 (Quasi-<br>bidirectional Mode) | - | -70   | -75 | μΑ | V <sub>DD</sub> = 5             | .5 V, V <sub>IN</sub>                                           | = 0V            |          |                        |

#### 2. XTAL1 is a CMOS input.

3. Pins of P0, P1, P2, P3, P4 and P5 can source a transition current when they are being externally driven from 1 to 0. In the condition of  $V_{DD}$ =5.5V, the transition current reaches its maximum value when  $V_{IN}$  approximates to 2V.

4. Only enable modules which support 10 kHz LIRC clock source

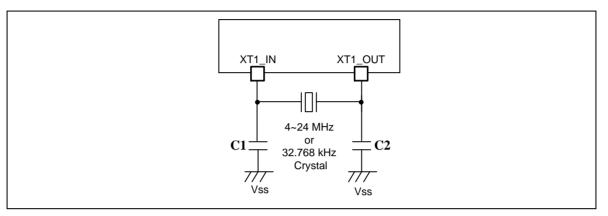

| 4 MHz ~ 24 MHz | 20 pF | 20 pF |

|----------------|-------|-------|

| 32.768 kHz     | 20 pF | 20 pF |

Figure 8.3-1 Mini58 Typical Crystal Application Circuit

## 8.3.5 22.1184 MHz Internal High Speed RC Oscillator (HIRC)

| Symbol           | Parameter            | Min  | Тур     | Max  | Unit | Test Conditions                                               |

|------------------|----------------------|------|---------|------|------|---------------------------------------------------------------|

| V <sub>HRC</sub> | Supply Voltage       | 1.62 | 1.8     | 1.98 | V    | -                                                             |

|                  | Center Frequency     | -    | 22.1184 |      | MHz  | -                                                             |

| f <sub>HRC</sub> | Calibrated Internal  | -1   | -       | +1   | %    | T <sub>A</sub> = 25 °C<br>V <sub>DD</sub> = 5 V               |

|                  | Oscillator Frequency | -2   | -       | +2   | %    | T <sub>A</sub> = -40°C ~105℃<br>V <sub>DD</sub> =2.5 V~ 5.5 V |

| I <sub>HRC</sub> | Operating Current    | -    | 700     | -    | μA   | $T_A = 25 \text{ °C}, V_{DD} = 5 \text{ V}$                   |

| I <sub>LVR</sub> | Quiescent Current | -    | 1    | 5    | μA | AV <sub>DD</sub> =5.5V |

|------------------|-------------------|------|------|------|----|------------------------|

|                  |                   | 1.90 | 2.00 | 2.10 | V  | T <sub>A</sub> =25°C   |

| V <sub>LVR</sub> |                   | 1.70 | 1.90 | 2.05 | V  | T <sub>A</sub> =-40°C  |

|                  |                   | 2.00 | 2.20 | 2.45 | V  | T <sub>A</sub> =105°C  |

### 8.4.4 Brown-out Detector

| Symbol           | Parameter          | Min | Тур  | Max  | Unit | Test Condition                |

|------------------|--------------------|-----|------|------|------|-------------------------------|

| AV <sub>DD</sub> | Supply Voltage     | 0   | -    | 5.5  | V    | -                             |

| T <sub>A</sub>   | Temperature        | -40 | 25   | 105  | °C   | -                             |

| I <sub>BOD</sub> | Quiescent Current  | -   | -    | 140  | μA   | AV <sub>DD</sub> =5.5V        |

|                  |                    | 4.2 | 4.38 | 4.55 | V    | BODEN = 1,<br>BOD_VL [1:0]=11 |

| V                | Brown-out Detector | 3.5 | 3.68 | 3.85 | V    | BODEN = 1,<br>BOD_VL [1:0]=10 |

| V <sub>bod</sub> | (Falling edge)     | 2.5 | 2.68 | 2.85 | V    | BODEN = 1,<br>BOD_VL [1:0]=01 |

|                  |                    | 2.0 | 2.18 | 2.35 | V    | BODEN = 1,<br>BOD_VL [1:0]=00 |

|                  |                    | 4.3 | 4.52 | 4.75 | V    | BODEN = 1,<br>BOD_VL [1:0]=11 |

| V                | Brown-out Detector | 3.5 | 3.8  | 4.05 | V    | BODEN = 1,<br>BOD_VL [1:0]=10 |

| V <sub>BOD</sub> | (Rising edge)      | 2.5 | 2.77 | 3.05 | V    | BODEN = 1,<br>BOD_VL [1:0]=01 |

|                  |                    | 2.0 | 2.25 | 2.55 | V    | BODEN = 1,<br>BOD_VL [1:0]=00 |

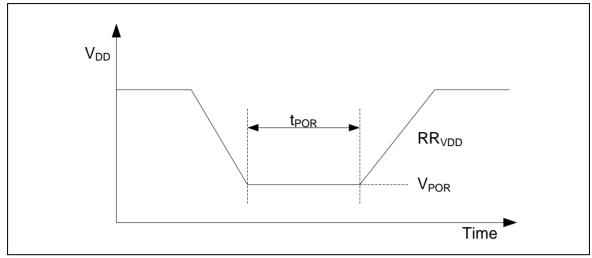

## 8.4.5 Power-on Reset

| Symbol            | Parameter                                                                           | Min   | Тур | Мах | Unit | Test Condition |

|-------------------|-------------------------------------------------------------------------------------|-------|-----|-----|------|----------------|

| T <sub>A</sub>    | Temperature                                                                         | -40   | 25  | 105 | °C   | -              |

| V <sub>POR</sub>  | Reset Voltage                                                                       | 1.6   | 2   | 2.4 | V    | -              |

| V <sub>POR</sub>  | V <sub>DD</sub> Start Voltage to Ensure<br>Power-on Reset                           | -     | -   | 100 | mV   |                |

| RR <sub>VDD</sub> | V <sub>DD</sub> Raising Rate to Ensure<br>Power-on Reset                            | 0.025 | -   | -   | V/ms |                |

| t <sub>POR</sub>  | Minimum Time for $V_{\text{DD}}$ Stays at $V_{\text{POR}}$ to Ensure Power-on Reset | 0.5   | -   | -   | ms   |                |

Figure 8.4-1 Power-up Ramp Condition

## 8.4.6 Comparator

| Symbol           | Parameter               | Min | Тур | Мах                   | Unit | Test Condition                                       |

|------------------|-------------------------|-----|-----|-----------------------|------|------------------------------------------------------|

| V <sub>CMP</sub> | Supply Voltage          | 2.5 | -   | 5.5                   | V    |                                                      |

| T <sub>A</sub>   | Temperature             | -40 | 25  | 105                   | °C   | -                                                    |

| I <sub>CMP</sub> | Operation Current       | -   | 40  | 80                    | μA   | AV <sub>DD</sub> =5V                                 |

| V <sub>OFF</sub> | Input Offset Voltage    |     | 10  | 20                    | mV   | -                                                    |

| V <sub>SW</sub>  | Output Swing            | 0.1 | -   | $AV_{DD} - 0.1$       | V    | -                                                    |

| V <sub>COM</sub> | Input Common Mode Range | 0.1 | -   | AV <sub>DD</sub> -0.1 | V    | -                                                    |

| -                | DC Gain                 | 40  | 70  | -                     | dB   | -                                                    |

| T <sub>PGD</sub> | Propagation Delay       | -   | 200 | -                     | ns   | V <sub>COM</sub> =1.2 V,<br>V <sub>DIFF</sub> =0.1 V |

| V <sub>HYS</sub> | Hysteresis              | -   | ±30 | ±60                   | mV   | V <sub>COM</sub> =1.2 V                              |

| Т <sub>STB</sub> | Stable time             | -   | -   | 1                     | μs   |                                                      |

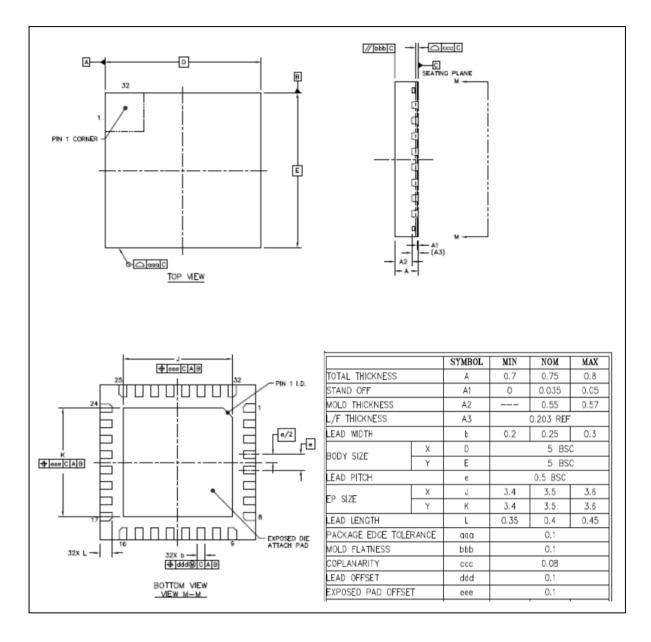

## 9.3 33-pin QFN (5 mm x 5 mm)

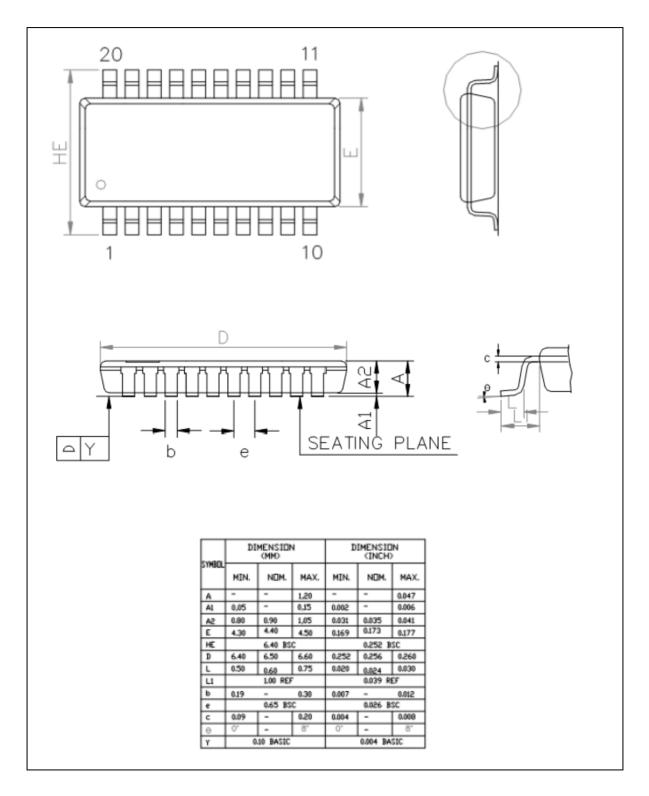

## 9.4 20-pin TSSOP