Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 4992                                                                        |

| Total RAM Bits                 | 75776                                                                       |

| Number of I/O                  | 278                                                                         |

| Number of Gates                | 397000                                                                      |

| Voltage - Supply               | 1.425V ~ 3.6V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                           |

| Package / Case                 | 680-BBGA                                                                    |

| Supplier Device Package        | 680-FPBGA (35x35)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ort8850l-1bm680i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **ORT8850 Overview**

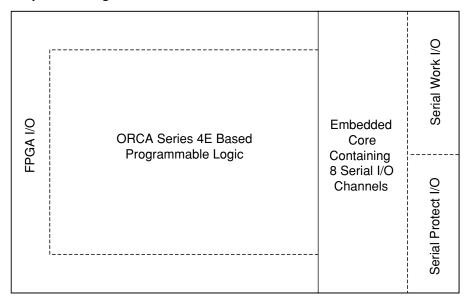

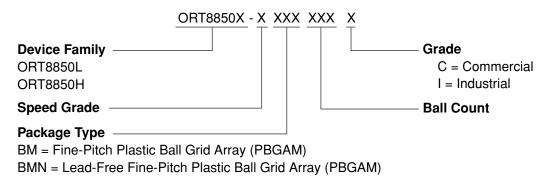

The ORT8850 FPSCs provide high-speed backplane transceivers combined with FPGA logic. There are two devices in the ORT8850 family. The ORT8850L device is based on 1.5 V OR4E02 ORCA FPGA and has a 26 x 24 array of Programmable Logic Cells (PLCs). The ORT8850H device is based on 1.5 V OR4E06 ORCA FPGA and has a 46 x 44 array. The embedded core which contains the backplane transceivers is attached to the right side of the device and is integrated directly into the FPGA array. A top level diagram of the basic chip configuration is shown in Figure 1.

Figure 1. ORT8850 Top Level Diagram

#### **Embedded Core Overview**

The ORT8850 embedded core contains a pseudo-SONET block for backplane or intra-board, chip-to-chip communication. The SONET block includes a High-Speed Interface (HSI) macrocell and a Synchronous Transport Module (STM) macrocell. It supports eight full-duplex channels and performs data transfer, scrambling/descrambling and SONET framing at the maximum rate of 850 Mbits/s. Figure 2 shows a top level diagram of the ORT8850 and the basic data flows through the device.

#### **LVDS Reference Clock**

The reference clock for the ORT8850 SERDES is an LVDS input (SYS\_CLK\_[P:N]). This reference clock can run in the range from 63.00 MHz to 106.25 MHz and is used to clock the entire Embedded Core. This clock is also available in the FPGA interface as the output signal FPGA\_SYSCLK at the Embedded Core/FPGA Logic interface.

The supported range of reference clock frequencies will drive the internal and link serial rates from 504 MHz to 850 MHz. For standard SONET applications a reference clock rate of 77.76 MHz will allow the ORT8850 to communicate with standard SONET devices. If the ORT8850 is communicating with another ORT8850, the reference clock can run anywhere in the defined range. When using a non 77.76 MHz reference clock, the frame pulse will now need to be derived from the non standard rate thus making the frame pulse rate not 8 kHz, but rather a single clock pulse every 9720 clock cycles.

### System Considerations for Reference Clock Distribution

There are two main system clocking architectures that can be used with the ORT8850 at the system level to provide the LVDS reference clocks. The recommended approach is to distribute a single reference clock to all boards. However, independent clocks can be used on each board provided that they are matched with sufficient accuracy and the alignment is not used. These two approaches are summarized in the following paragraphs

#### **Distributed Clocking**

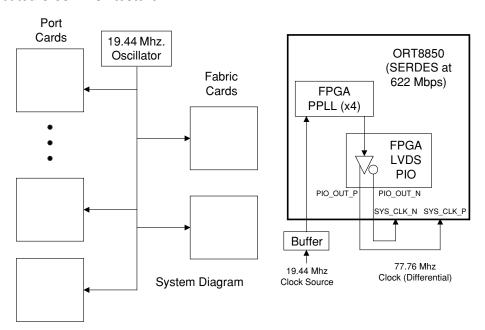

A distributed clock architecture, shown in Figure 5, uses a single source for the system reference clock. This single source drives all devices on both the line and switch sides of the backplane. Typically this is a lower speed clock such as a 19.44 MHz signal. An external PLL on each board or and internal ORT8850 FPGA PLL is then used to multiply the clock to the desired reference clock rate (i.e. by 4x to 77.76 MHz if the distributed clock is at 19.44 MHz). Using this type of clock architecture the ORT8850 data channels are fully synchronous and no domain transfer is required from the transmitter to the receiver.

Figure 5. Distributed Clock Architecture

#### Independent Clocking

An independent clock architecture uses independent clock sources on each ORT8850 board. With this architecture, for the SERDES to sample correctly the independent oscillators must be within reference clock tolerance requirements for the Clock and Data Recovery (CDR) to correctly sample the incoming data and recover data and clock. The local reference clock and the recovered clock will not be synchronous since they are created from a different source. The alignment FIFO uses the recovered clock for write and the local reference clock for read. Due to

Pointer Mover Performance Monitoring: There is Pointer Mover performance monitoring in the Receiver section. Alarm Indication Signals (AIS-P) and elastic store overflows are reported. AIS-P is implemented as a per STS-1 alarm bit. Elastic store overflow will cause an alarm bit to be set on a per STS-1 basis.

FIFO Aligner Monitoring: There is monitoring of the FIFO aligner operating point, and upon deviating from the nominal operating point of the FIFO by more than user programmable threshold values (min and max threshold values), an alarm bit is set. Threshold values are defined per device; alarm flags are per channel.

Frame Offset Monitoring: There is monitoring of the frame offset between all enabled channels (disabled channels do not interfere with the monitoring). Monitoring is performed continuously. Upon exceeding the maximum allowed frame offset (18 bytes) between all enabled channels, an alarm bit is set.

#### **Error Insertion**

A1/A2 Error Insert: There is a Frame Error inject feature in the transmitter section, allowing the user to replace framing bytes A1/A2 (only last A1 byte and first A2 byte) with a selectable A1/A2 byte value for a selectable number of consecutive frames. The number of consecutive frames to alter is specified by a 4-bit field, while A1/A2 value is specified by two 8-bit fields. The error insert feature is on a per channel basis, A1/A2 values and 4-bit frame count value are on a per device basis.

B1 Error Insert: There is a B1 error insert feature in the transmitter section, allowing the user to insert errors on user selectable bits in the B1 byte. Errors are created by simply inverting bit values. Bits to invert are specified through an 8-bit control. To insert an error, software will first set the bits in the "transmitter B1 error insert mask". Then, on a per channel basis software will write a one to the "B1 error insert command". The insertion circuitry performs a rising edge detect on the bit, and will issue a corruption signal for the next frame, for one frame only. This feature is on a per channel basis.

TOH Serial Output Port Parity Error Insert: There is a Parity error inject feature, in the receive section, allowing the user to invert the parity bit of each serial output port. This feature inserts a single error. This feature is on a per channel basis.

Parallel Output Bus Parity Error Insert: There is a Parity error inject feature, in the receive section, allowing the user to invert parity lines (DOUTxx\_PAR) associated with each output parallel busses (DOUTxx[7:0]). This feature inserts a single error. This feature is on a per channel basis. This feature supports both 'even' and 'odd' parities.

#### Loopback

There are two types of loopback that can be utilized inside the embedded ASIC core of the ORT8850, near end loopback and far end (line side) loopback. Both of these loopbacks are controlled by control registers inside the ORT8850 core, which are accessible from the system bus and the MicroProcessor Interface (MPI). In both loopback modes, all channels are placed with a single control. The data paths in the two loopback modes are shown in Figure 8.

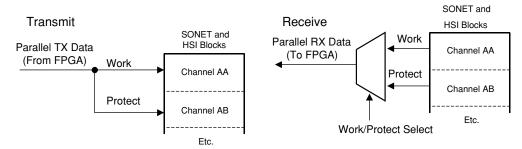

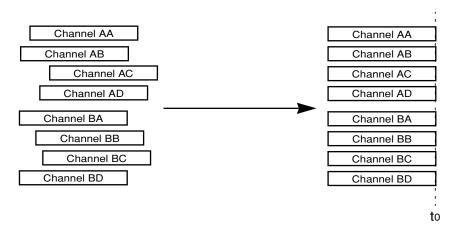

AA. This same scheme is used for channels groupings of AC/AD, BA/BB, and BC/BD. For quad protection when the alignment FIFOs are to be used, the protection switching must be done in FPGA logic.

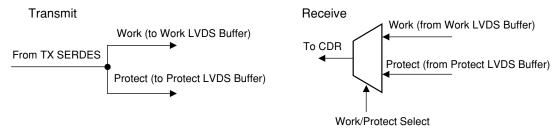

Figure 9. Parallel Protection Switching

LVDS protection switching (Figure 10) takes place at the LVDS buffer before the serial data is sent into the CDR. The selection is between the main LVDS buffer and the protect LVDS buffer. The main LVDS buffer provide the main receive data on RXDxx\_W\_[P:N] while the protect LVDS buffers provide protection receive data on RXDxx\_P\_[P:N]. When operating using the main LVDS buffers (default) no status information is available on the protect LVDS buffers since the serial stream must reach the SONET framer before status information is available on the data stream. The same is also true for the main LVDS buffers when operating with the protect buffers.

Figure 10. LVDS Protection Switching

See Table 17 and Table 18 and the accompanying text for details and register settings for the protection switching options.

### **FPSC Configuration - Overview**

Configuration of the ORT8850 occurs in two stages: FPGA bit stream configuration and embedded core setup.

#### **FPGA Configuration - Overview**

Prior to becoming operational, the FPGA goes through a sequence of states, including power-up, initialization, configuration, start-up, and operation. The FPGA logic is configured by the standard FPGA bit stream configuration means as discussed in the Series 4 FPGA data sheet. The options for the embedded core are set via registers that are accessed through the FPGA system bus. The system bus can be driven by an external PPC compliant microprocessor via the MPI block or via a user master interface in FPGA logic. A simple IP block, that drives the system by using the user interface and uses very little FPGA logic, is available in the *MPI/System Bus* technical note (TN1017). This IP block sets up the embedded core via a state machine and allows the ORT8850 to work in an independent system without an external MicroProcessor Interface.

#### **Embedded Core Setup**

All options for the operation of the core are configured according to the memory map shown in Table 19.

During the power-up sequence, the ORT8850 device (FPGA programmable circuit and the core) is held in reset. All the LVDS output buffers and other output buffers are held in 3-state. All Flip-Flops in the core area are in reset state, with the exception of the boundry-scan shift registers, which can only be reset by boundary-scan reset. After power-up reset, the FPGA can start configuration. During FPGA configuration, the ORT8850 core will be held in

reset and all the local bus interface signals forced high, but the following active-high signals, PROT\_SWITCH\_AA, PROT\_SWITCH\_BA, PROT\_SWITCH\_BC, TX\_TOH\_CK\_EN, SYS\_FP, LINE\_FP, will be forced low. The CORE\_READY signal sent from the embedded core to FPGA is held low, indicating that the core is not ready to interact with FPGA logic. At the end of the FPGA configuration sequence, the CORE\_READY signal will be held low for six SYS\_CLK cycles after DONE, TRI\_IO and RST\_N (core global reset) are high. Then it will go active-high, indicating the embedded core is ready to function and interact with FPGA programmable circuit. During FPGA reconfiguration when DONE and TRI\_IO are low, the CORE\_READY signal sent from the core to FPGA will be held low again to indicate the embedded core is not ready to interact with FPGA logic. During FPGA partial configuration, CORE\_READY stays active. The same FPGA configuration sequence described previously will repeat again.

The initialization of the embedded core consists of two steps: register configuration and synchronization of the alignment FIFO. The steps to configure the ORT8850 device for normal operation are listed in Table 4 and Table 5.

### **Generic Backplane Transceiver Application**

**Independent Channels, Transparent TOH:** Table 4 lists the register values to setup the ORT8850 as eight independent SONET channels (no alignment) using transparent TOH. The order is specific. The values are given from the PowerPC point of view. If using the MPI to write data to the ORT8850, the value given in the table is the value that should be used. If using the UMI of the system bus, the data value would need to be byte flipped.

Table 4. Independent Channels, Transparent TOH

| Register<br>Address | Value | Description                                                                                   |

|---------------------|-------|-----------------------------------------------------------------------------------------------|

| 0x30004             | 0x05  | Lock register. This value must be written to allow writing to any other ORT8850 core register |

| 0x30005             | 0x80  | Lock register. This value must be written to allow writing to any other ORT8850 core register |

| 0x30020             | 0x07  | Turn on Channel AA in functional mode                                                         |

| 0x30021             | 0xFF  | Channel AA - Transparent TOH from parallel data                                               |

| 0x30022             | 0xFF  | Channel AA - Transparent TOH from parallel data                                               |

| 0x30038             | 0x07  | Turn on Channel AB in functional mode                                                         |

| 0x30030             | 0xFF  | Channel AB - Transparent TOH from parallel data                                               |

| 0x3003A             | 0xFF  | Channel AB - Transparent TOH from parallel data                                               |

| 0x30050             | 0x07  | Turn on Channel AC function mode                                                              |

| 0x30051             | 0xFF  | Channel AC - Transparent TOH from parallel data                                               |

| 0x30052             | 0xFF  | Channel AB - Transparent TOH from parallel data                                               |

| 0x30068             | 0x07  | Turn on Channel AD in functional mode                                                         |

| 0x30069             | 0xFF  | Channel AD - Transparent TOH from parallel data                                               |

| 0x3006A             | 0xFF  | Channel AD - Transparent TOH from parallel data                                               |

| 0x30080             | 0x07  | Turn on Channel BA functional mode                                                            |

| 0x30081             | 0xFF  | Channel BA- Transparent TOH from parallel data                                                |

| 0x30082             | 0xFF  | Channel AD - Transparent TOH from parallel data                                               |

| 0x30098             | 0x07  | Turn on Channel BB in functional mode                                                         |

| 0x30099             | 0xFF  | Channel BB- Transparent TOH from parallel data                                                |

| 0x3009A             | 0xFF  | Channel BB- Transparent TOH from parallel data                                                |

| 0x300B0             | 0x07  | Turn on Channel BC in functional mode                                                         |

| 0x300B1             | 0xFF  | Channel BC- Transparent TOH from parallel data                                                |

| 0x300B2             | 0xFF  | Channel BC - Transparent TOH from parallel data                                               |

| 0x300C8             | 0x07  | Turn on Channel BD in functional mode                                                         |

| 0x300C9             | 0xFF  | Channel BD - Transparent TOH from parallel data                                               |

| 0x300CA             | 0xFF  | Channel BD - Transparent TOH from parallel data                                               |

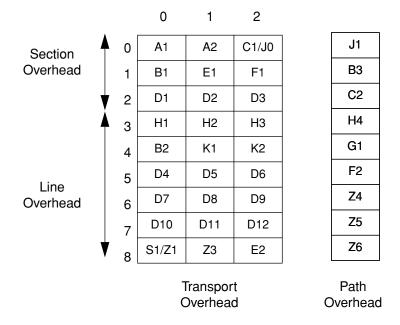

Figure 13. SONET Overhead Bytes

When used in true SONET applications, most TOH bytes would be generated in the FPGA logic or by an external device. The TOH bytes have the following functions. Table 9 and Table 10 show how the Embedded Core modifies these bytes in the transmit direction and Table 12 shows how the bytes are modified in the receive direction.

#### **Section Overhead Bytes:**

- A1, A2 These bytes are used for framing and to mark the beginning of a SONET frame. A1 has the value 0xF6 and A2 has the value 0x28.

- C1/J0 Section Trace Message This byte carries the section trace message. The message is interpreted to verify connectivity to a particular node in the network.

- B1 Section Bit Interleaved Parity (BIP-8) byte This byte carries the parity information which is used to check for transmission errors in a section. The computed parity value is transmitted in the next frame in the B1 position. It is defined only for the first STS-1 of a STS-N signal. The other bytes have a default value of 0x00 if using serial TOH insertion. In transparent TOH mode the other bytes are passed through from DINxx bus.

- E1 Section orderwire byte This byte carries local orderwire information, which provides for a 64 Kbits/s voice channel between two Section Termination Equipment (STE) devices.

- F1 Section user channel byte This byte provides a 64 Kbits/s user channel which can be used in a proprietary fashion.

- D1, D2, D3 Section Data Communications Channel (SDCC) bytes These bytes provide a 192 Kbits/s channel for transmission of information across STEs. This information could be for control and configuration, status monitoring, alarms, network administration data etc.

#### **Line Overhead Bytes:**

- H1, H2 STS Payload Pointers (H1 and H2) These bytes are used to locate the start of the SPE in a SONET frame. These two bytes contain the offset value, in bytes, between the pointer bytes and the start of the SPE. These bytes are used for all the STS-1 signals contained in an STS-N signal to indicate the individual starting positions of the SPEs. They bytes also contain justification indications, concatenation indications and path alarm indication (AIS-P).

- H3 Pointer Action Byte (H3) This byte is used during frequency justifications. When a negative justification is

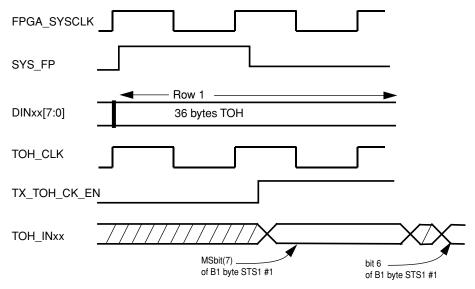

#### **Serial TOH Insertion Mode**

In the transmit direction the SPE bytes are always transferred unaltered from the input parallel bus to the serial LVDS output. On the other hand, TOH bytes are received from the serial input port and are inserted in the STS-12 frame before being sent to the LVDS output in the Serial TOH Insertion mode. The FPGA logic must provide framing information to the Core using the TX\_TOH\_CK\_EN Input signal. TOH data is input on a row by row basis, with a one clock cycle frame pulse delineating the start of a row, as shown in Figure 14. As shown in the figure, while the SPE bytes are being transmitted for one row, the FPGA logic must simultaneously supply the Core with the TOH data for the next row. Detailed timing for the TOH serial input is shown later in Figure 31.

Figure 14. TOH Serial Port Input Framing Signals (FPGA to Core)

Incoming serial TOH data is synchronized initially to the free running clock, TOH\_CLK. TOH\_CLK can operate from a minimum frequency of 25 Mhz. to a maximum frequency of 106 MHz. TOH bytes are transferred in the order shown in Figure 15. Bytes are transferred over the serial links with the MSB first. Data should be transferred over the serial link on a row-by-row basis. With three TOH bytes/per row for each STS-1 stream and a total of 12 STS-1 streams per STS-12 frame, a total of 288 TOH bits must be transferred for each row. The 288 TOH bits per row can be sent back-to-back. In this case, TX\_TO\_CLK\_EN will be high continuously for 288 TOH\_CLK cycles.

It is the responsibility of the user to synchronize transfer of the TOH bytes to a pre-determined window of time relative to the STS-12 frame position on the parallel input bus, i.e., the 36 TOH bytes to be inserted in row number n must be transferred to the Core during the time the SPE bytes of row n-1 are being transferred to the Core over the parallel input bus. Within each SPE row, a guard band of four TOH\_CLK cycles must be provided on each side of the TOH transfer window. No data may be transferred in these guard bands.

Figure 20. Alignment of all Eight SERDES Channels.

There is a provision to allow certain streams to be disabled (i.e. not producing alarms or affecting synchronization). These streams can be enabled at a later time without disrupting other streams. If the newly enabled stream needs to be a part of a bigger group the entire group must be resynchronized unless the affected stream was active when the initial synchronization was performed. As long as all streams to be aligned were active when the most recent synchronization was performed, individual streams may be enabled or disabled without affecting synchronization.

It is recommended that users select the smallest possible groups for channel alignment. If an application only requires that two channels be aligned then it is best to use by-2 grouping. All of the channels in a group will affect the group's total alignment. If a channel in a group fails or is shut down it will not affect any of the other channels in the group. This channel will simply be removed from the alignment algorithm. When the channel is re-enabled into a working group it will be out of alignment with the rest of the group. It will be necessary to perform a FIFO realignment procedure to realign the group. During a FIFO realignment data will not pass through any of the channels in the alignment group.

#### **Alignment FIFO Algorithm**

The algorithm controlling writes to the alignment FIFO and reads from it operates as follows: Prior to detecting the first frame pulse for a link being aligned, each link in the group continually writes to address 0 within its own FIFO (each link has a FIFO). When the first link in the group receives a frame pulse from Framer block the write pointer for the corresponding FIFO increments to next write address on each clock cycle. L inks that have not received a frame pulse continue to write into their respective FIFOs. When any link receives a frame pulse, the write address for that FIFO will be reset to '0'

The operation of the alignment algorithm requires a wait of several clocks from the first arriving frame pulse before reading of FIFO data begins. In this case, when all frame pulses arrive together the alignment algorithm initiates reads after 9 clocks cycles. If, however, the first to last arriving frame pulses are separated by multiple clock cycles, there will be additional clock cycles between the first frame pulse and the first read. If all links in the group have not reported a valid frame pulse signal after 18 clock cycles, an out of sync state is entered and an alarm is generated.

After all links have received frame pulses and are incrementing their write addresses while writing into their FIFOs, data is then read out of each link's FIFO one byte at a time. All aligned links are now Frame/byte/bit synchronous.

#### **FIFO Alignment Procedure**

The FIFO alignment block has the ability to be realigned by changing the value of bits in the alignment control registers. This may be done in the FPGA logic or under the control of an external device through the system bus or MPI. Alignment must take place after the stream has settled with valid data to guarantee proper channel alignment and uncorrupted data transmission.

Channel realignment must occur when a channel goes from the Out-Of-Frame (OOF) state to the In-Frame state. This happens when the channels are first powered up and given a valid frame pulse. This is the obvious known

Table 19. Memory Map Descriptions

| (0x)<br>Absolute<br>Address | Bit           | Туре | Name                             | Reset<br>Value<br>(0x) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|---------------|------|----------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30000                       | [0:7]         | R    | -                                | 05                     | Internal device revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30001                       | [0:7]         | R    | -                                | 80                     | Internal device revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30002                       | [0:7]         | R    | -                                | 80                     | Internal device revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30003                       | [0:7]         | R/W  | scratch pad                      | 00                     | The scratch pad has no function and is not used anywhere in the core. However, this register can be written to and read from for debugging purposes.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30004                       | [0:7]         | R/W  | lockreg MSB                      | 00                     | In order to write to registers in memory locations 0x30006 to 0x300FF, lockreg MSB and lockreg LSB must be respectively set to the values of 05 and 80. If the MSB and LSB lockreg values are not set to {05, 80}, then any values written to the registers in memory locations 0x30006 to 0x300FF will be ignored. After reset (both hard and soft), the core is in a write locked mode. The core needs to be unlocked before it can be written to.  Also note that the scratch pad register (0 x 30003) can always be written to as it is unaffected by write lock mode. |

| 30005                       | [0:7]         | R/W  | lockreg LSB                      | 00                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30006                       | [0]           | R/W  | global reset                     | 0                      | The global reset is a soft (software initiated) reset which will have the exact reset effect as a hard (RST_N pin) reset. This is a pulse register and does not have to be cleared.                                                                                                                                                                                                                                                                                                                                                                                        |

|                             | [1-7]         | -    | Not Used                         | 0                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30007                       | [0:7]         | -    | Not Used                         | 00                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Device Regis                | ster Block    | (S   |                                  |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             | [0]           | R/W  | LVDS loopback control            | 0                      | 0 = No Loopback<br>1 = LVDS loopback, transmit to receive. TX serial data is looped<br>back to the RX serial input. TX data is still available at the TX<br>pins                                                                                                                                                                                                                                                                                                                                                                                                           |

|                             | [1]           | -    | Not Used                         | 0                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             | [2]           | -    | Not Used                         | 0                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30008                       | 30008 [3] R/W |      | LVDS Protection<br>Switch enable | 0                      | 0 = Protection switching performed via bit settings in registers 0x30037 etc. 1 = Protection switching performed via hardware pins LVDS_PROT_SWITCH_xx                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                             | [4]           | R/W  | TOH RX serial enable             | 0                      | TOH_CK_FP_EN signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             | [5-7]         | -    | Not Used                         | 0                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             |               |      |                                  | •                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 19. Memory Map Descriptions (Continued)

| Absolute Address   Bit   Type   Name   (0x)   Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30019   [0:7] - Not Used   00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Channel Register Blocks  30020* 30038 30050 30068 30080 30098 300B0 300C8  [1] R/W AIS-L control OF O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Solution   Solution |

| 30038 30050 30068 30080 30080 30080 30080 30080 30080 30080 30008 300C8  [1] R/W AIS-L control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 30050 30068 30080 30098 30098 30000 30008  [1] R/W AIS-L control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30080 30098 300B0 300C8  [2] R/W TOH output parity error insert   0   0 = Do not insert a parity error in parity bit of receive TOH serial output for as long as this bit is set  [3] R/W RX K1/K2 source select   0   0 = Set receive direction K1 K2 bytes to 0.   1 = Pass receive direction K1 K2 through pointer mover.  [4] R/W DOUTxx bus parity error in DOUTxx_PAR for as long as this bit is set.  [5] R/W channel   0   0 = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 30088 30080 300C8  [2] R/W TOH output parity error insert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 300B0 300C8    2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 300C8  [3] R/W RX K1/K2 source put for as long as this bit is set  [4] R/W DOUTxx bus parity error in parity bit of receive 1OH serial out put for as long as this bit is set  [5] R/W channel  [6] R/W channel  [7] Insert parity error in parity bit of receive 1OH serial out put for as long as this bit is set  [8] R/W RX K1/K2 source of the put for as long as this bit is set.  [8] R/W DOUTxx bus parity error in DOUTxx_PAR for as long as this bit is set.  [8] R/W channel  [9] O = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [3] R/W RX K1/K2 source select 0 0 = Set receive direction K1 K2 bytes to 0.  1 = Pass receive direction K1 K2 through pointer mover.  4] R/W DOUTxx bus parity error in sert 0 0 = Do not insert parity error. 1 = Insert parity error in DOUTxx_PAR for as long as this bit is set.  5] R/W channel 0 0 = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| select  [4] R/W DOUTxx bus parity error insert  [5] R/W channel  1 = Pass receive direction K1 K2 through pointer mover.  0 0 = Do not insert parity error.  1 = Insert parity error in DOUTxx_PAR for as long as this bit is set.  0 0 = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [4] R/W DOUTxx bus parity error in DOUTxx_PAR for as long as this bit is set.  [5] R/W channel 0 0 = Do not insert parity error.  1 = Insert parity error in DOUTxx_PAR for as long as this bit is set.  0 0 = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ity error insert  1 = Insert parity error in DOUTxx_PAR for as long as this bit is set.  [5] R/W channel  0 0 = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit is set.  [5] R/W channel 0 0 = Power down CDR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| enable/disable   1 = Functional mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [6] R/W DOUTxx_EN 0 DOUTxx_EN signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |