Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                       |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 4K x 8                                                                |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

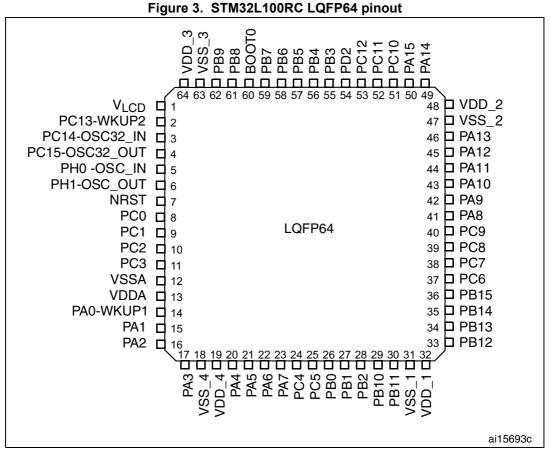

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l100rct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 3.14.3    | SysTick timer                                                     | . 27 |

|---|-------|-----------|-------------------------------------------------------------------|------|

|   |       | 3.14.4    | Independent watchdog (IWDG)                                       | . 27 |

|   |       | 3.14.5    | Window watchdog (WWDG)                                            | . 27 |

|   | 3.15  | Commu     | nication interfaces                                               | 27   |

|   |       | 3.15.1    | I <sup>2</sup> C bus                                              | . 27 |

|   |       | 3.15.2    | Universal synchronous/asynchronous receiver transmitter (USART) . | . 27 |

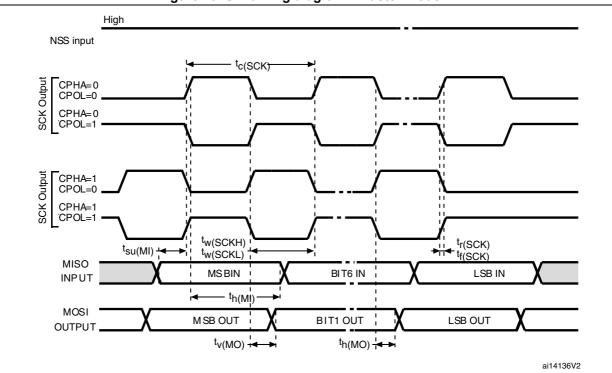

|   |       | 3.15.3    | Serial peripheral interface (SPI)                                 | . 28 |

|   |       | 3.15.4    | Universal serial bus (USB)                                        | . 28 |

|   | 3.16  | CRC (c    | yclic redundancy check) calculation unit                          | 28   |

|   | 3.17  | Develop   | oment support                                                     | 29   |

|   |       | 3.17.1    | Serial wire JTAG debug port (SWJ-DP)                              | . 29 |

|   |       | 3.17.2    | Embedded Trace Macrocell™                                         | . 29 |

|   |       |           |                                                                   |      |

| 4 | Pin d | escripti  | ons                                                               | 30   |

| 5 | Mom   | orv man   | ping                                                              | 20   |

| 5 | WEIN  | лу шар    | ping                                                              | 33   |

| 6 | Elect | rical cha | aracteristics                                                     | 40   |

|   | 6.1   | Parame    | ter conditions                                                    | 40   |

|   |       | 6.1.1     | Minimum and maximum values                                        | . 40 |

|   |       | 6.1.2     | Typical values                                                    | . 40 |

|   |       | 6.1.3     | Typical curves                                                    | . 40 |

|   |       | 6.1.4     | Loading capacitor                                                 | . 40 |

|   |       | 6.1.5     | Pin input voltage                                                 | . 40 |

|   |       | 6.1.6     | Power supply scheme                                               | . 41 |

|   |       | 6.1.7     | Optional LCD power supply scheme                                  | . 42 |

|   |       | 6.1.8     | Current consumption measurement                                   | . 42 |

|   | 6.2   | Absolut   | e maximum ratings                                                 | 43   |

|   | 6.3   | Operati   | ng conditions                                                     | 44   |

|   |       | 6.3.1     | General operating conditions                                      | . 44 |

|   |       | 6.3.2     | Embedded reset and power control block characteristics            | . 45 |

|   |       | 6.3.3     | Embedded internal reference voltage                               | . 47 |

|   |       | 6.3.4     | Supply current characteristics                                    | . 48 |

|   |       | 6.3.5     | Wakeup time from low-power mode                                   | . 59 |

|   |       | 6.3.6     | External clock source characteristics                             | . 60 |

|   |       | 6.3.7     | Internal clock source characteristics                             | . 65 |

|   |       | 6.3.8     | PLL characteristics                                               | . 68 |

|   |       |           |                                                                   |      |

## 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source**: three different clock sources can be used to drive the master clock SYSCLK:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- **Clock-out capability (MCO: microcontroller clock output):** it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

### 3.7 Memories

The STM32L100RC device has the following features:

- 16 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 128 Kbytes of embedded Flash program memory

- 4 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect or read-out protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

## 3.8 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose timers, DAC and ADC.

# 3.9 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 32 segment terminals to drive up to 320224 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

DocID024995 Rev 4

## 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L100RC device with up to 20 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs with up to 20 external channels in a group.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

#### 3.10.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode. See *Table 14: Embedded internal reference voltage calibration values*.

# 3.14 Timers and watchdogs

The ultra-low-power STM32L100RC device includes seven general-purpose timers, two basic timers, and two watchdog timers.

*Table 5* compares the features of the general-purpose and basic timers.

| Timer                  | Counter resolution Counter type |                      | Counter type Prescaler factor request |     | Capture/compare<br>channels | Complementary<br>outputs |

|------------------------|---------------------------------|----------------------|---------------------------------------|-----|-----------------------------|--------------------------|

| TIM2,<br>TIM3,<br>TIM4 | 16-bit                          | Up, down,<br>up/down | Any integer between<br>1 and 65536    | Yes | 4                           | No                       |

| TIM9                   | 16-bit                          | Up, down,<br>up/down | Any integer between<br>1 and 65536    | No  | 2                           | No                       |

| TIM10,<br>TIM11        | 16-bit                          | Up                   | Any integer between<br>1 and 65536    | No  | 1                           | No                       |

| TIM6,<br>TIM7          | 16-bit                          | Up                   | Any integer between<br>1 and 65536    | Yes | 0                           | No                       |

Table 5. Timer feature comparison

# 3.14.1 General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11)

There are seven synchronizable general-purpose timers embedded in the STM32L100RC device (see *Table 5* for differences).

#### TIM2, TIM3, TIM4

TIM2, TIM3, TIM4 are based on 16-bit auto-reload up/down counter. They include a 16-bit prescaler. They feature four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures/output compares/PWMs on the largest packages.

TIM2, TIM3, TIM4 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM10, TIM11 and TIM9

TIM10 and TIM11 are based on a 16-bit auto-reload upcounter. TIM9 is based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4 full-featured general-purpose timers.

# 4 Pin descriptions

1. This figure shows the package top view.

| Table 6. Legend/abbreviations | used in the | pinout table |

|-------------------------------|-------------|--------------|

|-------------------------------|-------------|--------------|

| Name          | Abbreviation                    | Definition                                                                                            |

|---------------|---------------------------------|-------------------------------------------------------------------------------------------------------|

| Pin name      |                                 | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |

|               | S                               | Supply pin                                                                                            |

| Pin type      | I                               | Input only pin                                                                                        |

|               | I/O                             | Input / output pin                                                                                    |

|               | FT                              | 5 V tolerant I/O                                                                                      |

| I/O structure | TC                              | Standard 3.3 V I/O                                                                                    |

| NO structure  | В                               | Dedicated BOOT0 pin                                                                                   |

|               | RST                             | Bidirectional reset pin with embedded weak pull-up resistor                                           |

| Notes         | Unless otherwis and after reset | e specified by a note, all I/Os are set as floating inputs during                                     |

| Pins   |                   |                     |                            |                                   | Pin fur                                                          | nctions                                    |

|--------|-------------------|---------------------|----------------------------|-----------------------------------|------------------------------------------------------------------|--------------------------------------------|

| LQFP64 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function<br>(after reset) | Alternate functions                                              | Additional functions                       |

| 17     | PA3               | I/O                 | -                          | PA3                               | TIM2_CH4/TIM9_CH2<br>/USART2_RX/LCD_SEG2                         | ADC_IN3/<br>COMP1_INP/OPAMP1_VOUT          |

| 18     | V <sub>SS_4</sub> | S                   | -                          | V <sub>SS_4</sub>                 | -                                                                | -                                          |

| 19     | $V_{DD_4}$        | S                   | -                          | V <sub>DD_4</sub>                 | -                                                                | -                                          |

| 20     | PA4               | I/O                 | -                          | PA4                               | SPI1_NSS/SPI3_NSS/<br>I2S3_WS/USART2_CK                          | ADC_IN4/DAC_OUT1/<br>COMP1_INP             |

| 21     | PA5               | I/O                 | -                          | PA5                               | TIM2_CH1_ETR/SPI1_SCK                                            | ADC_IN5/<br>DAC_OUT2/COMP1_INP             |

| 22     | PA6               | I/O                 | FT                         | PA6                               | TIM3_CH1/TIM10_CH1/<br>SPI1_MISO/LCD_SEG3                        | ADC_IN6/COMP1_INP/<br>OPAMP2_VINP          |

| 23     | PA7               | I/O                 | FT                         | PA7                               | TIM3_CH2/TIM11_CH1/<br>SPI1_MOSI/LCD_SEG4                        | ADC_IN7/COMP1_INP<br>/OPAMP2_VINM          |

| 24     | PC4               | I/O                 | FT                         | PC4                               | LCD_SEG22                                                        | ADC_IN14/COMP1_INP                         |

| 25     | PC5               | I/O                 | FT                         | PC5                               | LCD_SEG23                                                        | ADC_IN15/COMP1_INP                         |

| 26     | PB0               | I/O                 | -                          | PB0                               | TIM3_CH3/LCD_SEG5                                                | ADC_IN8/COMP1_INP/<br>OPAMP2_VOUT/VREF_OUT |

| 27     | PB1               | I/O                 | FT                         | PB1                               | TIM3_CH4/LCD_SEG6                                                | ADC_IN9/<br>COMP1_INP/VREF_OUT             |

| 28     | PB2               | I/O                 | FT                         | PB2/BOOT1                         | BOOT1                                                            | COMP1_INP                                  |

| 29     | PB10              | I/O                 | FT                         | PB10                              | TIM2_CH3/I2C2_SCL/<br>USART3_TX/LCD_SEG10                        | -                                          |

| 30     | PB11              | I/O                 | FT                         | PB11                              | TIM2_CH4/I2C2_SDA/<br>USART3_RX/LCD_SEG11                        | -                                          |

| 31     | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                 | -                                                                | -                                          |

| 32     | V <sub>DD_1</sub> | S                   | -                          | V <sub>DD_1</sub>                 | -                                                                | -                                          |

| 33     | PB12              | I/O                 | FT                         | PB12                              | TIM10_CH1/I2C2_SMBA/<br>SPI2_NSS/I2S2_WS/<br>USART3_CK/LCD_SEG12 | ADC_IN18/COMP1_INP                         |

| 34     | PB13              | I/O                 | FT                         | PB13                              | TIM9_CH1/SPI2_SCK/<br>I2S2_CK/ USART3_CTS/<br>LCD_SEG13          | ADC_IN19/COMP1_INP                         |

| 35     | PB14              | I/O                 | FT                         | PB14                              | TIM9_CH2/SPI2_MISO/<br>USART3_RTS/LCD_SEG14                      | ADC_IN20/COMP1_INP                         |

Table 7. STM32L100RC pin definitions (continued)

#### Alternate functions

#### Table 8. Alternate function input/output

|           |                    |              |          |                | Digital alter | nate function | number              |            |   |        |   |          |              |

|-----------|--------------------|--------------|----------|----------------|---------------|---------------|---------------------|------------|---|--------|---|----------|--------------|

|           | AFIO0              | AFIO1        | AFIO2    | AFIO3          | AFIO4         | AFIO5         | AFIO6               | AFIO7      | • | AFIO11 | • | AFIO14   | AFIO15       |

| Port name | Alternate function |              |          |                |               |               |                     |            |   |        |   |          |              |

|           | SYSTEM             | TIM2         | TIM3/4   | TIM9/<br>10/11 | I2C1/2        | SPI1/2        | SPI3                | USART1/2/3 |   | LCD    |   | CPRI     | SYSTEM       |

| BOOT0     | BOOT0              | -            | -        | -              | -             | -             | -                   | -          |   | -      |   | -        | EVENT<br>OUT |

| NRST      | NRST               | -            | -        | -              | -             | -             | -                   | -          |   | -      |   | -        | -            |

| PA0-WKUP1 | -                  | TIM2_CH1_ETR | -        | -              | -             | -             | -                   | USART2_CTS |   | -      |   | TIMx_IC1 | EVENT<br>OUT |

| PA1       | -                  | TIM2_CH2     | -        | -              | -             | -             | -                   | USART2_RTS |   | SEG0   |   | TIMx_IC2 | EVENT<br>OUT |

| PA2       | -                  | TIM2_CH3     | -        | TIM9_CH1       | -             | -             | -                   | USART2_TX  |   | SEG1   |   | TIMx_IC3 | EVENT<br>OUT |

| PA3       | -                  | TIM2_CH4     | -        | TIM9_CH2       | -             | -             | -                   | USART2_RX  |   | SEG2   |   | TIMx_IC4 | EVENT<br>OUT |

| PA4       | -                  | -            | -        | -              | -             | SPI1_NSS      | SPI3_NSS<br>I2S3_WS | USART2_CK  |   | -      |   | TIMx_IC1 | EVENT<br>OUT |

| PA5       | -                  | TIM2_CH1_ETR | -        | -              | -             | SPI1_SCK      | -                   | -          |   | -      |   | TIMx_IC2 | EVENT<br>OUT |

| PA6       | -                  | -            | TIM3_CH1 | TIM10_CH1      | -             | SPI1_MISO     | -                   | -          |   | SEG3   |   | TIMx_IC3 | EVENT<br>OUT |

| PA7       | -                  | -            | TIM3_CH2 | TIM11_CH1      | -             | SPI1_MOSI     | -                   | -          |   | SEG4   |   | TIMx_IC4 | EVENT<br>OUT |

| PA8       | мсо                | -            | -        | -              | -             | -             | -                   | USART1_CK  |   | COM0   |   | TIMx_IC1 | EVENT<br>OUT |

| PA9       | -                  | -            | -        | -              | -             | -             | -                   | USART1_TX  |   | COM1   |   | TIMx_IC2 | EVENT<br>OUT |

| PA10      | -                  | -            | -        | -              | -             | -             | -                   | USART1_RX  |   | COM2   |   | TIMx_IC3 | EVENT<br>OUT |

| PA11      | -                  | -            | -        | -              | -             | SPI1_MISO     | -                   | USART1_CTS |   | -      |   | TIMx_IC4 | EVENT<br>OUT |

35/104

36/104

DocID024995 Rev 4

5

|            |            |              |          |                | Digital alter | nate function  | number               |            |        |          |              |

|------------|------------|--------------|----------|----------------|---------------|----------------|----------------------|------------|--------|----------|--------------|

| <b>_</b> / | AFIO0      | AFIO1        | AFIO2    | AFIO3          | AFIO4         | AFIO5          | AFIO6                | AFIO7      | AFIO11 | AFIO14   | AFIO15       |

| Port name  |            | I            | L        |                | Alte          | rnate function | 1                    |            |        | 1 1      |              |

|            | SYSTEM     | TIM2         | TIM3/4   | TIM9/<br>10/11 | I2C1/2        | SPI1/2         | SPI3                 | USART1/2/3 | LCD    | CPRI     | SYSTEM       |

| PA12       | -          | -            | -        | -              | -             | SPI1_MOSI      | -                    | USART1_RTS | -      | TIMx_IC1 | EVENT<br>OUT |

| PA13       | JTMS-SWDIO | -            | -        | -              | -             | -              | -                    | -          | -      | TIMx_IC2 | EVENT<br>OUT |

| PA14       | JTCK-SWCLK | -            | -        | -              | -             | -              | -                    | -          | -      | TIMx_IC3 | EVEN<br>TOUT |

| PA15       | JTDI       | TIM2_CH1_ETR | -        | -              | -             | SPI1_NSS       | SPI3_NSS<br>I2S3_WS  | -          | SEG17  | TIMx_IC4 | EVEN<br>TOUT |

| PB0        | -          | -            | TIM3_CH3 | -              | -             | -              | -                    | -          | SEG5   | -        | EVEN<br>TOUT |

| PB1        | -          | -            | TIM3_CH4 | -              | -             | -              | -                    | -          | SEG6   | -        | EVENT<br>OUT |

| PB2        | BOOT1      | -            | -        | -              | -             | -              | -                    | -          | -      | -        | EVENT<br>OUT |

| PB3        | JTDO       | TIM2_CH2     | -        | -              | -             | SPI1_SCK       | SPI3_SCK<br>I2S3_CK  | -          | SEG7   | -        | EVENT<br>OUT |

| PB4        | NJTRST     | -            | TIM3_CH1 | -              | -             | SPI1_MISO      | SPI3_MISO            | -          | SEG8   | -        | EVENT<br>OUT |

| PB5        | -          | -            | TIM3_CH2 | -              | I2C1_<br>SMBA | SPI1_MOSI      | SPI3_MOSI<br>I2S3_SD | -          | SEG9   | -        | EVENT<br>OUT |

| PB6        | -          | -            | TIM4_CH1 | -              | I2C1_SCL      | -              | -                    | USART1_TX  | -      | -        | EVENT<br>OUT |

| PB7        | -          | -            | TIM4_CH2 | -              | I2C1_SDA      | -              | -                    | USART1_RX  | -      | -        | EVENT<br>OUT |

| PB8        | -          | -            | TIM4_CH3 | TIM10_CH1      | I2C1_SCL      | -              | -                    | -          | SEG16  | -        | EVENT<br>OUT |

| PB9        | -          | -            | TIM4_CH4 | TIM11_CH1      | I2C1_SDA      | -              | -                    | -          | COM3   | -        | EVENT<br>OUT |

| PB10       | -          | TIM2_CH3     | -        | -              | I2C2_SCL      | -              | -                    | USART3_TX  | SEG10  | -        | EVENT<br>OUT |

| Symbol                  | Parameter               | Cond                                                           | litions                                               | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit      |

|-------------------------|-------------------------|----------------------------------------------------------------|-------------------------------------------------------|-------------------|------|--------------------|-----------|

|                         |                         |                                                                | Range 3,                                              | 1 MHz             | 50   | 130                |           |

|                         |                         |                                                                | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 78.5 | 195                |           |

|                         |                         |                                                                | VOS[1:0] = 11                                         | 4 MHz             | 140  | 310                |           |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,                                              | 4 MHz             | 165  | 310                |           |

|                         |                         | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 310  | 440                |           |

|                         |                         | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 590  | 830                |           |

|                         |                         | - /                                                            | Range 1,                                              | 8 MHz             | 350  | 550                |           |

|                         | Supply current in Sleep |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 680  | 990                |           |

|                         | mode, Flash             |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2100               |           |

| L (Clean)               | OFF                     | HSI clock source<br>(16 MHz)                                   | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 640  | 890                |           |

|                         |                         |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2200               | _         |

|                         |                         | MSI clock, 65 kHz                                              | Range 3,                                              | 65 kHz            | 19   | 60                 |           |

|                         |                         | MSI clock, 524 kHz                                             | V <sub>CORE</sub> =1.2 V                              | 524 kHz           | 33   | 99                 |           |

|                         |                         | MSI clock, 4.2 MHz                                             | VOS[1:0] = 11                                         | 4.2 MHz           | 145  | 210                |           |

| I <sub>DD</sub> (Sleep) |                         |                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz             | 60.5 | 130                | - μΑ<br>- |

|                         |                         |                                                                |                                                       | 2 MHz             | 89.5 | 190                |           |

|                         |                         |                                                                |                                                       | 4 MHz             | 150  | 320                |           |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,<br>V <sub>CORE</sub> =1.5 V                  | 4 MHz             | 180  | 320                |           |

|                         |                         | $f_{HSE} = f_{HCLK}/2$                                         |                                                       | 8 MHz             | 320  | 460                |           |

|                         | Supply current          | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 605  | 840                |           |

|                         | in Sleep                |                                                                | Range 1,                                              | 8 MHz             | 380  | 540                |           |

|                         | mode, Flash<br>ON       |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 695  | 1000               |           |

|                         |                         |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2100               |           |

|                         |                         | HSI clock source                                               | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 650  | 910                |           |

|                         |                         | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2200               |           |

|                         | Supply current          | MSI clock, 65 kHz                                              | Range 3,                                              | 65 kHz            | 30   | 90                 | 1         |

|                         | in Sleep<br>mode, Flash | MSI clock, 524 kHz                                             | V <sub>CORE</sub> =1.2V                               | 524 kHz           | 44   | 96                 | 1         |

|                         | ON                      | MSI clock, 4.2 MHz                                             | VOS[1:0] = 11                                         | 4.2 MHz           | 155  | 220                | 1         |

Table 18. Current consumption in Sleep mode

1. Guaranteed by characterization results, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

- 3. In Low-power sleep and run mode, the Flash memory must always be in power-down mode.

- 4. Data based on a differential IDD measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

- Data based on a differential IDD measurement between DAC in reset configuration and continuous DAC conversion of VDD/2. DAC is in buffered mode, output is left floating.

- 6. Including supply current of internal reference voltage.

#### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under the conditions summarized in *Table 12*.

| Symbol                  | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Conditions                                                        | Тур       | Max <sup>(1)</sup>                                                                                                                                                                                                                                                                       | Unit |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| t <sub>WUSLEEP</sub>    | Wakeup from Sleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f <sub>HCLK</sub> = 32 MHz                                        | 0.4       | -                                                                                                                                                                                                                                                                                        |      |  |

| +                       | Wakeup from Low-power sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                      | <b>31</b> |                                                                                                                                                                                                                                                                                          |      |  |

| <sup>t</sup> wusleep_lp | mode, f <sub>HCLK</sub> = 262 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                 | 46        | 11       -         0.4       -         46       -         46       -         3.2       -         7.7       8.9         3.2       13.1         0.2       13.4         16       20         31       37         57       66         12       123         221       236         58       104 |      |  |

|                         | Wakeup from Stop mode,<br>regulator in Run mode<br>ULP bit = 1 and FWU bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 8.2       | -                                                                                                                                                                                                                                                                                        |      |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $f_{HCLK} = f_{MSI} = 4.2 \text{ MHz}$<br>Voltage range 1 and 2   | 7.7       | 8.9                                                                                                                                                                                                                                                                                      |      |  |

|                         | PWakeup from Low-power sleep<br>mode, $f_{HCLK} = 262 \text{ kHz}$ Flash enable<br>f_{HCLK} = 260 Flash switchWakeup from Stop mode,<br>regulator in Run mode<br>ULP bit = 1 and FWU bit = 1f_{HCLK} = f_{MS}PWakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1f_{HCLK} = f_{MS}PWakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1f_{HCLK} = f_{MS}PWakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1f_{HCLK} = f_{MS}PWakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1f_{HCLK} = f_{MS}FIACLK = f_{MS}f_{HCLK} = f_ | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 8.2       | 13.1                                                                                                                                                                                                                                                                                     | μs   |  |

| <sup>t</sup> WUSTOP     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 10.2      | 13.4                                                                                                                                                                                                                                                                                     |      |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 16        | 20                                                                                                                                                                                                                                                                                       |      |  |

|                         | OLP bit = 1 and $FVVO$ bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $           |           |                                                                                                                                                                                                                                                                                          |      |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 57        | 66                                                                                                                                                                                                                                                                                       |      |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 112       | 123                                                                                                                                                                                                                                                                                      |      |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 221       | 236                                                                                                                                                                                                                                                                                      |      |  |

| t                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 58        | 104                                                                                                                                                                                                                                                                                      |      |  |

| <sup>t</sup> wustdby    | Wakeup from Standby mode<br>FWU bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.6       | 3.25                                                                                                                                                                                                                                                                                     | ms   |  |

Table 24. Low-power mode wakeup timings

1. Guaranteed by characterization, not tested in production, unless otherwise specified

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

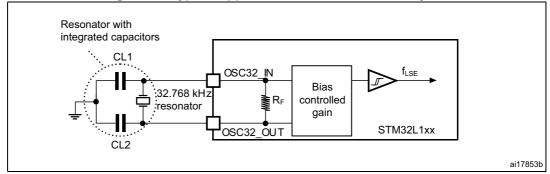

- Note: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 13).  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \leq 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L = 6 \text{ pF}$  and  $C_{\text{stray}} = 2 \text{ pF}$ , then  $C_{L1} = C_{L2} = 8 \text{ pF}$ .

#### Figure 13. Typical application with a 32.768 kHz crystal

| Symbol                                | Parameter                          | Condition                                | Тур | Мах | Unit |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|------|

|                                       |                                    | MSI range 0                              | -   | 40  |      |

|                                       |                                    | MSI range 1                              | -   | 20  |      |

|                                       |                                    | MSI range 2                              | -   | 10  |      |

|                                       |                                    | MSI range 3                              | -   | 4   |      |

| . (2)                                 | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5 | μs   |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 5                              | -   | 2   |      |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |      |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -   | 3   |      |

| f                                     | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz  |

| fover(MSI)                            |                                    | Any range to range 6                     | -   | 6   |      |

Table 31. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results, not tested in production.

## Flash memory and data EEPROM

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |

|                   | Programming/ erasing                                                           | Erasing                                         | -    | 3.28 | 3.94               |      |  |

| t <sub>prog</sub> | time for byte / word /<br>double word / half-page                              | Programming                                     | -    | 3.28 | 3.94               | ms   |  |

|                   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 600  |                    | μA   |  |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |

Table 34. Flash memory and data EEPROM characteristics

1. Guaranteed by design, not tested in production.

| Symbol                          | Parameter                                                                           | Conditions                  | \                  | Unit |     |         |  |

|---------------------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------|------|-----|---------|--|

|                                 | Falameter                                                                           | Conditions                  | Min <sup>(1)</sup> | Тур  | Max | Onit    |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory                                           | $T_A = -40^{\circ}C$ to     | 10                 | -    | -   | kavalaa |  |

| NCAC, \                         | Cycling (erase / write)<br>EEPROM data memory                                       | 105 °C                      | 300                | -    | -   | kcycles |  |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C       | -T <sub>RFT</sub> = +85 °C  | 30                 | -    | -   |         |  |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C              | 1 <sub>RET</sub> - +65 C    | 30                 | -    | -   | Vooro   |  |

| 'RET` ´                         | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C      | -T <sub>RET</sub> = +105 °C | 10                 | -    | -   | years   |  |

|                                 | Data retention (EEPROM data memory)<br>after 300 kcycles at T <sub>A</sub> = 105 °C | 1 <sub>RET</sub> = 1105 C   | 10                 | -    | -   |         |  |

1. Guaranteed by characterization results, not tested in production.

2. Characterization is done according to JEDEC JESD22-A117.

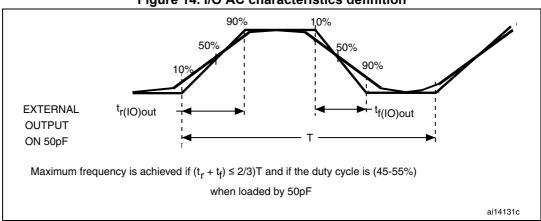

## 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 47* are derived from tests performed under the conditions summarized in *Table 12*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter Conditions Min                           |                                                                                           | Тур                                       | Max                                | Unit                                  |    |  |

|------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------|----|--|

| V <sub>IL</sub>  |                                                    | TC and FT I/O                                                                             | -                                         | -                                  | 0.3 V <sub>DD</sub> <sup>(1)(2)</sup> |    |  |

|                  | Input low level voltage                            | BOOT0                                                                                     | -                                         | -                                  | 0.14 V <sub>DD</sub> <sup>(2)</sup>   |    |  |

|                  |                                                    | TC I/O                                                                                    | 0.45 V <sub>DD</sub> +0.38 <sup>(2)</sup> | -                                  | -                                     |    |  |

| $V_{\text{IH}}$  | Input high level voltage                           | FT I/O                                                                                    | 0.39 V <sub>DD</sub> +0.59 <sup>(2)</sup> | -                                  | -                                     | V  |  |

|                  |                                                    | BOOT0                                                                                     | 0.15 V <sub>DD</sub> +0.56 <sup>(2)</sup> | -                                  | -                                     |    |  |

| V                | I/O Schmitt trigger voltage                        | TC and FT I/O                                                                             | -                                         | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                     |    |  |

| V <sub>hys</sub> | hysteresis <sup>(2)</sup>                          | BOOT0                                                                                     | -                                         | 0.01                               | -                                     |    |  |

|                  | Input leakage current <sup>(4)</sup>               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                        | -                                         | -                                  | ±50                                   |    |  |

| I <sub>lkg</sub> |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches         | -                                         | -                                  | ±50                                   |    |  |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                                         | -                                  | ±50                                   | nA |  |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                        | -                                         | -                                  | ±250                                  |    |  |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>TC and FT I/Os                       | -                                         | -                                  | ±50                                   |    |  |

|                  |                                                    | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                            | -                                         | -                                  | ±10                                   | μA |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)(1)</sup> | $V_{IN} = V_{SS}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>  | $V_{IN} = V_{DD}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ |  |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                         | -                                         | 5                                  | -                                     | pF |  |

| Table 41. | I/O sta | tic characteristics |

|-----------|---------|---------------------|

|-----------|---------|---------------------|

1. Guaranteed by test in production

2. Guaranteed by design, not tested in production.

3. With a minimum of 200 mV.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

#### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 44*)

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under the conditions summarized in *Table 12*.