Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| roduct Status             | Active                                                                           |

| Core Processor            | MIPS32® microAptiv™                                                              |

|                           | ·                                                                                |

| Core Size                 | 32-Bit Single-Core                                                               |

| peed                      | 200MHz                                                                           |

| Connectivity              | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG               |

| eripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| lumber of I/O             | 78                                                                               |

| rogram Memory Size        | 1MB (1M x 8)                                                                     |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 512K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| ata Converters            | A/D 40x10b                                                                       |

| Scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 100-TQFP                                                                         |

| upplier Device Package    | 100-TQFP (14x14)                                                                 |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecg100-i-pf |

#### TABLE 4: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

A34 **124-PIN VTLA (BOTTOM VIEW)** A17 B29 B13 PIC32MZ0512EC(E/F/K)124 B41 PIC32MZ1024EC(G/H/M)124 PIC32MZ1024EC(E/F/K)124 PIC32MZ2048EC(G/H/M)124 B56 A51

Α1

Polarity Indicator

A68

| Package<br>Pin # | Full Pin Name                        |

|------------------|--------------------------------------|

| B1               | EBIA5/AN34/PMA5/RA5                  |

| B2               | EBID6/AN16/PMD6/RE6                  |

| В3               | EBIA6/AN22/RPC1/PMA6/RC1             |

| B4               | AN36/ETXD1/RJ9                       |

| B5               | EBIWE/AN20/RPC3/PMWR/RC3             |

| В6               | AN14/C1IND/RPG6/SCK2/RG6             |

| В7               | EBIA3/AN12/C2IND/RPG8/SCL4/PMA3/RG8  |

| B8               | VDD                                  |

| В9               | EBIA2/AN11/C2INC/RPG9/PMA2/RG9       |

| B10              | AN25/RPE8/RE8                        |

| B11              | AN45/C1INA/RPB5/RB5                  |

| B12              | AN37/ERXCLK/EREFCLK/RJ11             |

| B13              | Vss                                  |

| B14              | PGEC2/AN46/RPB6/RB6                  |

| B15              | VREF-/CVREF-/AN27/RA9                |

| B16              | AVDD                                 |

| B17              | AN38/ETXD2/RH0                       |

| B18              | EBIA10/AN48/RPB8/PMA10/RB8           |

| B19              | EBIA13/CVREFOUT/AN5/RPB10/PMA13/RB10 |

| B20              | Vss                                  |

| B21              | TCK/EBIA19/AN29/RA1                  |

| B22              | TDO/EBIA17/AN31/RPF12/RF12           |

| B23              | AN8/RB13                             |

| B24              | EBIA0/AN10/RPB15/OCFB/PMA0/RB15      |

| B25              | VDD                                  |

| B26              | AN41/ERXD1/RH5                       |

| B27              | AN32/AETXD0/RPD14/RD14               |

| B28              | OSC1/CLKI/RC12                       |

| Package<br>Pin # | Full Pin Name               |  |  |  |  |  |  |  |  |

|------------------|-----------------------------|--|--|--|--|--|--|--|--|

| B29              | Vss                         |  |  |  |  |  |  |  |  |

| B30              | D+                          |  |  |  |  |  |  |  |  |

| B31              | RPF2/SDA3/RF2               |  |  |  |  |  |  |  |  |

| B32              | ERXD0/RH8                   |  |  |  |  |  |  |  |  |

| B33              | ECOL/RH10                   |  |  |  |  |  |  |  |  |

| B34              | EBIRDY1/SDA2/RA3            |  |  |  |  |  |  |  |  |

| B35              | VDD                         |  |  |  |  |  |  |  |  |

| B36              | EBIA9/RPF4/SDA5/PMA9/RF4    |  |  |  |  |  |  |  |  |

| B37              | RPA14/SCL1/RA14             |  |  |  |  |  |  |  |  |

| B38              | EBIA15/RPD9/PMCS2/PMA15/RD9 |  |  |  |  |  |  |  |  |

| B39              | EMDC/RPD11/RD11             |  |  |  |  |  |  |  |  |

| B40              | ERXDV/ECRSDV/RH13           |  |  |  |  |  |  |  |  |

| B41              | SOSCI/RPC13/RC13            |  |  |  |  |  |  |  |  |

| B42              | EBID14/RPD2/PMD14/RD2       |  |  |  |  |  |  |  |  |

| B43              | EBID12/RPD12/PMD12/RD12     |  |  |  |  |  |  |  |  |

| B44              | ETXERR/RJ0                  |  |  |  |  |  |  |  |  |

| B45              | EBIRDY3/RJ2                 |  |  |  |  |  |  |  |  |

| B46              | SQICS1/RPD5/RD5             |  |  |  |  |  |  |  |  |

| B47              | ETXCLK/RPD7/RD7             |  |  |  |  |  |  |  |  |

| B48              | Vss                         |  |  |  |  |  |  |  |  |

| B49              | EBID10/RPF1/PMD10/RF1       |  |  |  |  |  |  |  |  |

| B50              | EBID8/RPG0/PMD8/RG0         |  |  |  |  |  |  |  |  |

| B51              | TRD3/SQID3/RA7              |  |  |  |  |  |  |  |  |

| B52              | EBID0/PMD0/RE0              |  |  |  |  |  |  |  |  |

| B53              | VDD                         |  |  |  |  |  |  |  |  |

| B54              | TRD2/SQID2/RG14             |  |  |  |  |  |  |  |  |

| B55              | TRD0/SQID0/RG13             |  |  |  |  |  |  |  |  |

| B56              | EBID3/RPE3/PMD3/RE3         |  |  |  |  |  |  |  |  |

- The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Note Select (PPS)" for restrictions.

- Every I/O port pin (RAx-RJx) can be used as a change notification pin (CNAx-CNJx). See Section 12.0 "I/O Ports" for more information.

- Shaded pins are 5V tolerant. 3:

- The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

## 2.10 Considerations When Interfacing to Remotely Powered Circuits

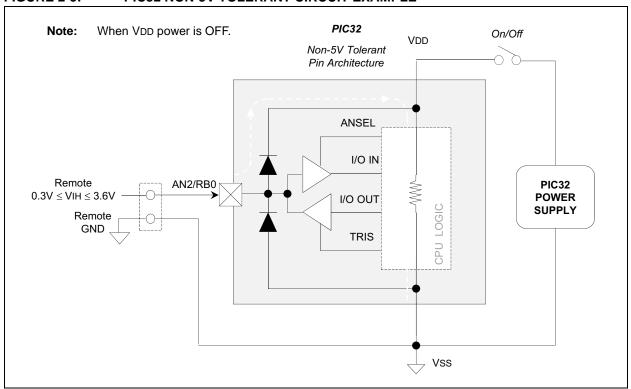

### 2.10.1 NON-5V TOLERANT INPUT PINS

A quick review of the absolute maximum rating section in **37.0** "Electrical Characteristics" will indicate that the voltage on any non-5v tolerant pin may not exceed AVDD/VDD + 0.3V. Figure 2-5 shows an example of a remote circuit using an independent power source, which is powered while connected to a PIC32 non-5V tolerant circuit that is not powered.

FIGURE 2-5: PIC32 NON-5V TOLERANT CIRCUIT EXAMPLE

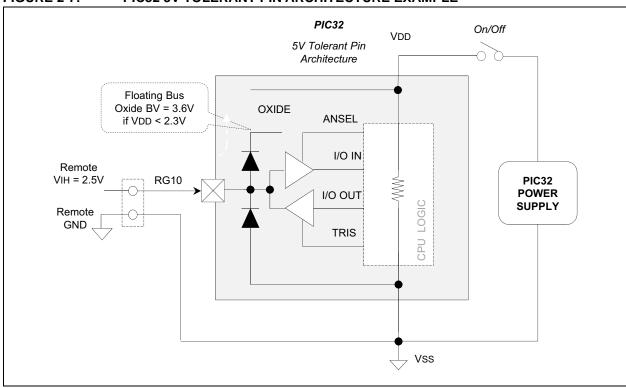

#### 2.10.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be ≤ 3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

FIGURE 2-7: PIC32 5V TOLERANT PIN ARCHITECTURE EXAMPLE

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                   | -                    |                       |                   |                   | _                | _                |

| 22.40        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                   | _                    | _                     | _                 | _                 | _                | _                |

| 45.0         | R/W-0, HC         | R/W-0               | R-0, HS, HC          | R-0, HS, HC           | U-0               | U-0               | U-0              | U-0              |

| 15:8         | WR <sup>(1)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | U-0                 | U-0                  | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | SWAP              | _                   | _                    | _                     |                   | NVMOP             | <3:0>            |                  |

| Legend: |                   | HS = Hardware Set | HC = Hardware Cleared      |                    |  |  |

|---------|-------------------|-------------------|----------------------------|--------------------|--|--|

|         | R = Readable bit  | W = Writable bit  | U = Unimplemented bit, rea | d as '0'           |  |  |

|         | -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit (1)

This bit cannot be cleared and can be set only when WREN = 1 and the unlock sequence has been performed.

1 = Initiate a Flash operation

0 = Flash operation is complete or inactive

bit 14 WREN: Write Enable bit<sup>(1)</sup>

1 = Enable writes to the WR bit and disables writes to the NVMOP<3:0> bits

0 = Disable writes to WR bit and enables writes to the NVMOP<3:0> bits

bit 13 WRERR: Write Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 = Voltage level is acceptable for programming

bit 11-8 Unimplemented: Read as '0'

bit 7 **SWAP:** Program Flash Bank Swap Control bit

This bit can be modified only when the WREN bit is '0' and the unlock sequence has been performed.

- 1 = Program Flash Bank 2 is mapped to the lower mapped region and program Flash Bank 1 is mapped to the upper mapped region

- 0 = Program Flash Bank 1 is mapped to the lower mapped region and program Flash Bank 2 is mapped to the upper mapped region

bit 6-4 Unimplemented: Read as '0'

Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

#### REGISTER 8-5: REFOXTRIM: REFERENCE OSCILLATOR TRIM REGISTER (x = 1-4)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | 31:24 ROTRIM<8:1> |                   |                   |                   |                   |                   |                  |                  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | -                 | _                | -                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:y = Value set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

111111111 = 511/512 divisor added to RODIV value 111111110 = 510/512 divisor added to RODIV value

•

•

100000000 = 256/512 divisor added to RODIV value

•

•

000000010 = 2/512 divisor added to RODIV value 000000001 = 1/512 divisor added to RODIV value

000000000 = 0 divisor added to RODIV value

bit 22-0 Unimplemented: Read as '0'

- Note 1: While the ON bit (REFOxCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

- 2: Do not write to this register when the ON bit (REFOxCON<15>) is not equal to the ACTIVE bit (REFOxCON<8>).

- 3: Specified values in this register do not take effect if RODIV<14:0> (REFOxCON<30:16>) = 0.

### 9.2 Prefetch Control Registers

### TABLE 9-1: PREFETCH REGISTER MAP

| TABLE O II. I TALI LI OTT REGIOTER III/II |                                 |          |       |       |       |       |        |          |      |      |      |      |       |        |          |      |          |      |           |

|-------------------------------------------|---------------------------------|----------|-------|-------|-------|-------|--------|----------|------|------|------|------|-------|--------|----------|------|----------|------|-----------|

| ess (                                     | _                               | o        |       |       |       |       |        | Bits     |      |      |      |      |       |        |          |      |          | s    |           |

| Virtual Address<br>(BF8E_#)               | Register<br>Name <sup>(1)</sup> | Bit Rang | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10    | 25/9 | 24/8 | 23/7 | 22/6 | 21/5  | 20/4   | 19/3     | 18/2 | 17/1     | 16/0 | All Reset |

| 0000                                      | DDECON                          | 31:16    | _     | _     | _     | _     | _      | PFMSECEN | _    | _    | _    | _    | _     | _      | _        | _    | _        | _    | 0000      |

| 0000                                      | PRECON                          | 15:0     |       | _     | _     | _     | _      | _        | _    | _    | _    | _    | PREFE | N<1:0> | _        | Р    | FMWS<2:0 | >    | 0007      |

| 0040                                      | DDECTAT                         | 31:16    | _     | _     | _     | _     | PFMDED | PFMSEC   | _    | _    | _    | _    | _     | _      | _        | _    | _        | _    | 0000      |

| 0010                                      | PRESTAT                         | 15:0     | _     | _     | _     | _     | _      | _        | _    | _    |      |      |       | PFMSEC | CNT<7:0> |      |          |      | 0000      |

| -                                         | _                               |          |       |       |       | •     |        |          |      |      | •    |      |       |        |          |      |          |      |           |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity (EC) Family

### REGISTER 9-2: PRESTAT: PREFETCH MODULE STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | R/W-0, HS         | R/W-0, HS         | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | PFMDED            | PFMSEC            | _                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | -                 | _                 | -                 | 1                | 1                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | -                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | PFMSEC            | CNT<7:0>          |                   |                  |                  |

Legend: HS = Hardware Set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 Unimplemented: Read as '0'

bit 27 **PFMDED:** Flash Double-bit Error Detected (DED) Status bit

This bit is set in hardware and can only be cleared (i.e., set to '0') in software.

1 = A DED error has occurred

0 = A DED error has not occurred

bit 26 **PFMSEC:** Flash Single-bit Error Corrected (SEC) Status bit

1 = A SEC error occurred when PFMSECCNT<7:0> was equal to '0'

0 = A SEC error has not occurred

bit 25-8 Unimplemented: Read as '0'

bit 7-0 **PFMSECCNT<7:0>:** Flash SEC Count bits

11111111 - 00000000 = SEC count

This field decrements by one each time an SEC error occurs. It will hold at zero on the two-hundred and fifty-sixth error. When an SEC error occurs, when PFMSECCNT = 0, the PFMSEC status bit is set. If PFMSECEN is also set, an interrupt is generated.

Note: These bits count all SEC errors and are not limited to SEC errors on unique addresses.

#### REGISTER 11-2: USBCSR1: USB CONTROL STATUS REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00:40        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-0            |

| 23:16        | EP7TXIE           | EP6TXIE           | EP5TXIE           | EP4TXIE           | EP3TXIE           | EP2TXIE           | EP1TXIE          | EP0IE            |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 7:0          | R-0, HS           | R-0, HS          | U-0              |

|              | EP7RXIF           | EP6RXIF           | EP5RXIF           | EP4RXIF           | EP3RXIF           | EP2RXIF           | EP1RXIF          | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-17 EP7TXIE:EP1TXIE: Endpoint 'n' Transmit Interrupt Enable bits

1 = Endpoint Transmit interrupt events are enabled

0 = Endpoint Transmit interrupt events are not enabled

bit 16 **EP0IE**: Endpoint 0 Interrupt Enable bit

1 = Endpoint 0 interrupt events are enabled

0 = Endpoint 0 interrupt events are not enabled

bit 15-8 Unimplemented: Read as '0'

bit 7-1 **EP7RXIF:EP1RXIF:** Endpoint 'n' RX Interrupt bit

1 = Endpoint has a receive event to be serviced

0 = No interrupt event

bit 0 Unimplemented: Read as '0'

## REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

bit 10-0 TXMAXP<10:0>: Maximum TX Payload per transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

TXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

TABLE 12-1: INPUT PIN SELECTION (CONTINUED)

| Peripheral Pin      | [pin name]R SFR      | [pin name]R bits          | [pin name]R Value to<br>RPn Pin Selection                  |

|---------------------|----------------------|---------------------------|------------------------------------------------------------|

| INT1                | INT1R                | INT1R<3:0>                | 0000 = RPD1                                                |

| T4CK                | T4CKR                | T4CKR<3:0>                | 0001 = RPG9<br>0010 = RPB14                                |

| T9CK                | T9CKR                | T9CKR<3:0>                | 0010 = RPB14<br>0011 = RPD0                                |

| IC1                 | IC1R                 | IC1R<3:0>                 | 0100 = Reserved                                            |

| IC6                 | IC6R                 | IC6R<3:0>                 | 0101 = RPB6<br>0110 = RPD5                                 |

| U3CTS               | U3CTSR               | U3CTSR<3:0>               | 0111 = RPB2                                                |

| U4RX                | U4RXR                | U4RXR<3:0>                | 1000 = RPF3<br>1001 = RPF13 <sup>(1)</sup>                 |

| U6RX                | U6RXR                | U6RXR<3:0>                | 1001 = RPF13(*)<br>1010 = No Connect                       |

| SS2                 | SS2R                 | SS2R<3:0>                 | 1011 = RPF2 <sup>(1)</sup>                                 |

| SDI6 <sup>(1)</sup> | SDI6R <sup>(1)</sup> | SDI6R<3:0> <sup>(1)</sup> | 1100 = RPC2 <sup>(1)</sup><br>- 1101 = RPE8 <sup>(1)</sup> |

| OCFA                | OCFAR                | OCFAR<3:0>                | 1110 = RFE6()                                              |

| REFCLKI3            | REFCLKI3R            | REFCLKI3R<3:0>            | 1111 = Reserved                                            |

Note 1: This selection is not available on 64-pin devices.

<sup>2:</sup> This selection is not available on 64-pin or 100-pin devices.

<sup>3:</sup> This selection is not available on devices without a CAN module.

### REGISTER 15-7: DMTPSINTV: POST STATUS CONFIGURE DMT INTERVAL STATUS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24     | PSINTV<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22:40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16     |                   |                   |                   | PSINTV<           | :23:16>           |                   |                  |                  |  |  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8      | PSINTV<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-y               | R-y              | R-y              |  |  |

| 7:0       |                   |                   |                   | PSINTV            | ′<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  | y = Value set from Configuration bits on POR |                    |  |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit,                       | read as '0'        |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |  |

bit 31-8 PSINTV<31:0>: DMT Window Interval Configuration Status bits

This is always the value of the DMTINTV<2:0> bits in the DEVCFG1 Configuration register.

#### REGISTER 20-9: SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5      | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                      | _                 | _                 | _                 | _                | 1                |

| 22,46        | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                      | _                 | _                 | _                 | _                |                  |

|              | U-0               | U-0               | U-0                    | U-0               | U-0               | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 15:8         | _                 | _                 | _                      | -                 | -                 | PKT<br>COMPIF     | BD<br>DONEIF     | CON<br>THRIF     |

| 7:0          | R/W-1, HS         | R/W-0, HS         | R/W-1, HS              | R/W-0, HS         | R/W-1, HS         | R/W-1, HS         | R/W-0, HS        | R/W-1, HS        |

|              | CON<br>EMPTYIF    | CON<br>FULLIF     | RXTHRIF <sup>(1)</sup> | RXFULLIF          | RX<br>EMPTYIF     | TXTHRIF           | TXFULLIF         | TX<br>EMPTYIF    |

**Legend:** HS = Hardware Set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-11 Unimplemented: Read as '0'

bit 10 PKTCOMPIF: DMA Buffer Descriptor Processor Packet Completion Interrupt Status bit

1 = DMA BD packet is complete

0 = DMA BD packet is in progress

bit 9 BDDONEIF: DMA Buffer Descriptor Done Interrupt Status bit

1 = DMA BD process is done

0 = DMA BD process is in progress

bit 8 **CONTHRIF:** Control Buffer Threshold Interrupt Status bit

1 = The control buffer has more than THRES words of space available

0 = The control buffer has less than THRES words of space available

bit 7 **CONEMPTYIF:** Control Buffer Empty Interrupt Status bit

1 = Control buffer is empty

0 = Control buffer is not empty

bit 6 **CONFULLIF:** Control Buffer Full Interrupt Status bit

1 = Control buffer is full

0 = Control buffer is not full

bit 5 **RXTHRIF:** Receive Buffer Threshold Interrupt Status bit (1)

1 = Receive buffer has more than RXINTTHR words of space available

0 = Receive buffer has less than RXINTTHR words of space available

bit 4 RXFULLIF: Receive Buffer Full Interrupt Status bit

1 = Receive buffer is full

0 = Receive buffer is not full

bit 3 RXEMPTYIF: Receive Buffer Empty Interrupt Status bit

1 = Receive buffer is empty

0 = Receive buffer is not empty

bit 2 TXTHRIF: Transmit Buffer Interrupt Status bit

1 = Transmit buffer has more than TXINTTHR words of space available

0 = Transmit buffer has less than TXINTTHR words of space available

Note 1: In the case of Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

#### REGISTER 28-4: AD1IMOD: ADC1 INPUT MODE CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3            | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0       |

|-----------|-------------------|-------------------|-------------------|-------------------|------------------------------|-------------------|------------------------------|------------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0                          | U-0               | R/W-0                        | R/W-0                  |

| 31.24     | _                 | _                 | _                 | _                 | _                            | _                 | SH4ALT                       | <1:0> <sup>(1,2)</sup> |

| 22,46     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0             | R/W-0                        | R/W-0                  |

| 23:16     | SH3ALT<1:0>(1,2)  |                   | SH2ALT<1:0>(1,2)  |                   | SH1ALT<1:0> <sup>(1,2)</sup> |                   | SH0ALT<1:0> <sup>(1,2)</sup> |                        |

| 15.0      | U-0               | U-0               | U-0               | U-0               | R/W-0                        | R/W-0             | R/W-0                        | R/W-0                  |

| 15:8      | _                 | _                 | _                 | _                 | SH5MC                        | D<1:0>            | SH4M0                        | DC<1:0>                |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0             | R/W-0                        | R/W-0                  |

|           | SH3MOD<1:0>       |                   | SH2MOD<1:0>       |                   | SH1MOD<1:0>                  |                   | SH0MOD<1:0>                  |                        |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25-24 SH4ALT<1:0>: Analog Input to Dedicated S&H 4 (SH4) Select bits<sup>(1,2)</sup>

11 = Reserved

10 = Reserved

01 = Alternate input AN49

00 = Default Class 1 input AN4

bit 23-22 SH3ALT<1:0>: Analog Input to Dedicated S&H 3 (SH3) Select bits<sup>(1,2)</sup>

11 = Reserved

10 = Reserved

01 = Alternate input AN48

00 = Default Class 1 input AN3

bit 21-20 SH2ALT<1:0>: Analog Input to Dedicated S&H 2 (SH2) Select bits<sup>(1,2)</sup>

11 = Reserved

10 = Reserved

01 = Alternate input AN47

00 = Default Class 1 input AN2

bit 19-18 SH1ALT<1:0>: Analog Input to Dedicated S&H 1 (SH1) Select bits<sup>(1,2)</sup>

11 = Reserved

10 = Reserved

01 = Alternate input AN46

00 = Default Class 1 input AN1

bit 17-16 SH0ALT<1:0>: Analog Input to Dedicated S&H 0 (SH0) Select bits<sup>(1,2)</sup>

11 = Reserved

10 = Reserved

01 = Alternate input AN45

00 = Default Class 1 input AN0

bit 15-12 **Unimplemented:** Read as '0'

Note 1: Alternate inputs are only available for Class 1 Inputs.

2: When an alternate input is selected (SHxALT<1:0> ≠ 0), the data, status, and control registers for the default Class 1 input are still used. Selecting an alternate input changes the physical input source only.

### REGISTER 29-19: CIFIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |

| 31.24        | CiFIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |

| 23.10        | CiFIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |

| 15.6         | CiFIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |

|              | CiFIFOBA<7:0>     |                   |                   |                   |                   |                   |                    |                    |  |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 CiFIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Note that bits <1:0> are read-only and read '0', forcing the messages to be 32-bit word-aligned in device RAM.

Note 1: This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

## REGISTER 30-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)

- bit 7 CRCERREN: CRC Error Collection Enable bit

- 1 = The received packet CRC must be invalid for the packet to be accepted

- 0 = Disable CRC Error Collection filtering

This bit allows the user to collect all packets that have an invalid CRC.

- bit 6 CRCOKEN: CRC OK Enable bit

- 1 = The received packet CRC must be valid for the packet to be accepted

- 0 = Disable CRC filtering

This bit allows the user to reject all packets that have an invalid CRC.

- bit 5 RUNTERREN: Runt Error Collection Enable bit

- 1 = The received packet must be a runt packet for the packet to be accepted

- 0 = Disable Runt Error Collection filtering

This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1).

- bit 4 RUNTEN: Runt Enable bit

- 1 = The received packet must not be a runt packet for the packet to be accepted

- 0 = Disable Runt filtering

This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes.

- bit 3 UCEN: Unicast Enable bit

- 1 = Enable Unicast Filtering

- 0 = Disable Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address.

- bit 2 NOTMEEN: Not Me Unicast Enable bit

- 1 = Enable Not Me Unicast Filtering

- 0 = Disable Not Me Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address.

- bit 1 MCEN: Multicast Enable bit

- 1 = Enable Multicast Filtering

- 0 = Disable Multicast Filtering

This bit allows the user to accept all Multicast Address packets.

- bit 0 BCEN: Broadcast Enable bit

- 1 = Enable Broadcast Filtering

- 0 = Disable Broadcast Filtering

This bit allows the user to accept all Broadcast Address packets.

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

- Note 1: This register is only used for RX operations.

- 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

## REGISTER 30-17: ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | FRMTXOKCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   | FRMTXOKCNT<7:0>   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

TABLE 33-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS<sup>(1)</sup> (CONTINUED)

| Peripheral               | PMDx bit Name | Register Name and Bit Location |

|--------------------------|---------------|--------------------------------|

| UART3                    | U3MD          | PMD5<2>                        |

| UART4                    | U4MD          | PMD5<3>                        |

| UART5                    | U5MD          | PMD5<4>                        |

| UART6                    | U6MD          | PMD5<5>                        |

| SPI1                     | SPI1MD        | PMD5<8>                        |

| SPI2                     | SPI2MD        | PMD5<9>                        |

| SPI3                     | SPI3MD        | PMD5<10>                       |

| SPI4                     | SPI4MD        | PMD5<11>                       |

| SPI5                     | SPI5MD        | PMD5<12>                       |

| SPI6                     | SPI6MD        | PMD5<13>                       |

| I2C1                     | I2C1MD        | PMD5<16>                       |

| I2C2                     | I2C2MD        | PMD5<17>                       |

| I2C3                     | I2C3MD        | PMD5<18>                       |

| I2C4                     | I2C4MD        | PMD5<19>                       |

| I2C5                     | I2C5MD        | PMD5<20>                       |

| USB <sup>(2)</sup>       | USBMD         | PMD5<24>                       |

| CAN1                     | CAN1MD        | PMD5<28>                       |

| CAN2                     | CAN2MD        | PMD5<29>                       |

| RTCC                     | RTCCMD        | PMD6<0>                        |

| Reference Clock Output 1 | REFO1MD       | PMD6<8>                        |

| Reference Clock Output 2 | REFO2MD       | PMD6<9>                        |

| Reference Clock Output 3 | REFO3MD       | PMD6<10>                       |

| Reference Clock Output 4 | REFO4MD       | PMD6<11>                       |

| PMP                      | PMPMD         | PMD6<16>                       |

| EBI                      | EBIMD         | PMD6<17>                       |

| SQI1                     | SQI1MD        | PMD6<23>                       |

| Ethernet                 | ETHMD         | PMD6<28>                       |

| DMA                      | DMAMD         | PMD7<4>                        |

| Random Number Generator  | RNGMD         | PMD7<20>                       |

| Crypto                   | CRYPTMD       | PMD7<22>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MZ EC Family Features" for the lists of available peripherals.

<sup>2:</sup> Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

TABLE 37-12: DC CHARACTERISTICS: PROGRAM MEMORY(3)

| DC CHA        | DC CHARACTERISTICS |                                                                       |        |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |            |             |  |  |  |

|---------------|--------------------|-----------------------------------------------------------------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------|------------|-------------|--|--|--|

| Param.<br>No. | Sym.               | Sym. Characteristics Min. Typ. <sup>(1)</sup> Max. Unit               |        | Units  | Conditions                                                                                                                    |            |             |  |  |  |

| D130a         | ЕР                 | Cell Endurance                                                        | 10,000 | _      | _                                                                                                                             | E/W        | Without ECC |  |  |  |

| D130b         |                    |                                                                       | 20,000 | _      | _                                                                                                                             | E/W        | With ECC    |  |  |  |

| D131          | VPR                | VDD for Read                                                          | VDDMIN | _      | VDDMAX                                                                                                                        | V          | _           |  |  |  |

| D132          | VPEW               | VDD for Erase or Write                                                | VDDMIN |        | VDDMAX                                                                                                                        | V          | _           |  |  |  |

| D134a         | TRETD              | Characteristic Retention                                              | 10     | _      | _                                                                                                                             | Year       | Without ECC |  |  |  |

| D134b         |                    |                                                                       | 20     | _      | _                                                                                                                             | Year       | With ECC    |  |  |  |

| D135          | IDDP               | Supply Current during<br>Programming                                  | _      | _      | 30                                                                                                                            | mA         | _           |  |  |  |

| D136          | Trw                | Row Write Cycle Time (Notes 2, 4)                                     | _      | 66813  | _                                                                                                                             | FRC Cycles | _           |  |  |  |

| D137          | TQWW               | Quad Word Write Cycle Time (Note 4)                                   | _      | 773    | _                                                                                                                             | FRC Cycles | _           |  |  |  |

| D138          | Tww                | Word Write Cycle Time (Note 4)                                        | _      | 383    | _                                                                                                                             | FRC Cycles | _           |  |  |  |

| D139          | TCE                | Chip Erase Cycle Time (Note 4)                                        | _      | 515373 | _                                                                                                                             | FRC Cycles | _           |  |  |  |

| D140          | TPFE               | All Program Flash (Upper and Lower regions) Erase Cycle Time (Note 4) | _      | 256909 | _                                                                                                                             | FRC Cycles | _           |  |  |  |

| D141          | Трве               | Program Flash (Upper or Lower regions) Erase Cycle Time (Note 4)      | _      | 128453 | _                                                                                                                             | FRC Cycles | _           |  |  |  |

| D142          | TPGE               | Page Erase Cycle Time (Note 4)                                        |        | 128453 | _                                                                                                                             | FRC Cycles | _           |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **2:** The minimum PBCLK5 for row programming is 4 MHz.

- **3:** Refer to the "PIC32 Flash Programming Specification" (DS60001145) for operating conditions during programming and erase cycles.

- 4: This parameter depends on FRC accuracy (see Table 37-20) and FRC tuning values (see the OSCTUN register: Register 8-2).

TABLE 37-13: DC CHARACTERISTICS: PROGRAM FLASH MEMORY WAIT STATES

| DC CHARACTERISTICS                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |         |            |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| Required Flash Wait States <sup>(1)</sup> | SYSCLK                                                                                                                                                                 | Units   | Conditions |  |  |

| With ECC:                                 |                                                                                                                                                                        |         |            |  |  |

| 0 Wait states                             | 0 < SYSCLK ≤ 66                                                                                                                                                        | MHz     | _          |  |  |

| 1 Wait state                              | 66 < SYSCLK ≤ 133                                                                                                                                                      | IVII IZ |            |  |  |

| 2 Wait states                             | 133 < SYSCLK ≤ 200                                                                                                                                                     |         |            |  |  |

| Without ECC:                              |                                                                                                                                                                        |         |            |  |  |

| 0 Wait states                             | 0 < SYSCLK ≤ 83                                                                                                                                                        | MHz     | _          |  |  |

| 1 Wait state                              | 83 < SYSCLK ≤ 166                                                                                                                                                      | IVII IZ |            |  |  |

| 2 Wait states                             | 166 < SYSCLK ≤ 200                                                                                                                                                     |         |            |  |  |

Note 1: To use Wait states, the PFMWS<2:0> bits must be written with the desired Wait state value.

TABLE 37-23: I/O TIMING REQUIREMENTS (CONTINUED)

| AC CHA        | RACTERIS                                                                                                                | STICS                                                                                                                              |                  | perating Conditions: 2.3V to 3.6V<br>erwise stated)<br>emperature -40°C ≤ TA ≤ +85°C for Industrial |                     |      |       |               |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|---------------------|------|-------|---------------|--|

| Param.<br>No. | Symbol Characteris                                                                                                      |                                                                                                                                    |                  | Min.                                                                                                | Typ. <sup>(1)</sup> | Max. | Units | Conditions    |  |

| DO32          | TioF                                                                                                                    | Port Output Fall Tim<br>I/O Pins:<br>4x Source Driver Pins<br>RA3, RA9, RA10, RA<br>RB0-7, RB11, RB13<br>RC12-RC15                 | s -<br>.14, RA15 | _                                                                                                   | _                   | 9.5  | ns    | CLOAD = 50 pF |  |

|               | RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11 |                                                                                                                                    | s, RH8-RH13      | _                                                                                                   | _                   | 6    | ns    | CLOAD = 20 pF |  |

|               |                                                                                                                         | Port Output Fall Tir<br>I/O Pins:<br>8x Source Driver Pin<br>RA0-RA2, RA4, RA5<br>RB8-RB10, RB12, R<br>RC1-RC4<br>RD1-RD5, RD9, RD | s -<br>B14, RB15 | _                                                                                                   | _                   | 8    | ns    | CLOAD = 50 pF |  |

|               |                                                                                                                         | RD13, RD15<br>RE4-RE7<br>RF0, RF4, RF5, RF1:<br>RG0, RG1, RG6-RG9<br>RH2, RH3, RH7, RH7<br>RJ3-RJ7, RJ10, RJ12<br>RK0-RK7          | 9<br>14, RH15    | _                                                                                                   | _                   | 6    | ns    | CLOAD = 20 pF |  |

|               |                                                                                                                         | Port Output Fall Time<br>I/O Pins:<br>12x Source Driver Pins -<br>RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                          |                  | _                                                                                                   | _                   | 3.5  | ns    | CLOAD = 50 pF |  |

|               |                                                                                                                         |                                                                                                                                    |                  | _                                                                                                   | _                   | 2    | ns    | CLOAD = 20 pF |  |

| DI35          | TINP                                                                                                                    | INTx Pin High or Low                                                                                                               | Time             | 5                                                                                                   | _                   | _    | ns    | _             |  |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

CNx High or Low Time (input)

DI40

ns

<sup>2:</sup> This parameter is characterized, but not tested in manufacturing.

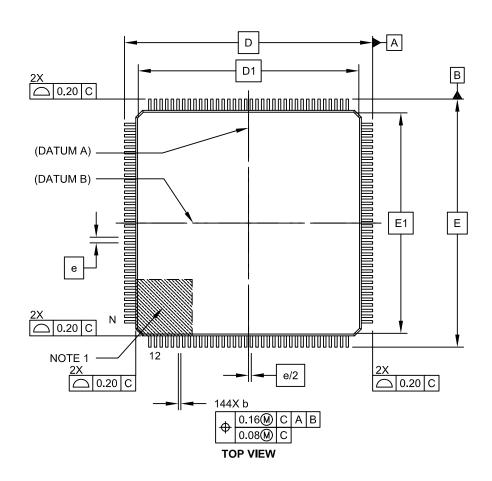

# 144-Lead Plastic Low Profile Quad Flatpack (PL) – 20x20x1.40 mm Body, with 2.00 mm Footprint [LQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-044B Sheet 1 of 2