Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecg100t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents provided in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). This data sheet contains device-specific information for PIC32MZ Embedded Connectivity (EC) devices.

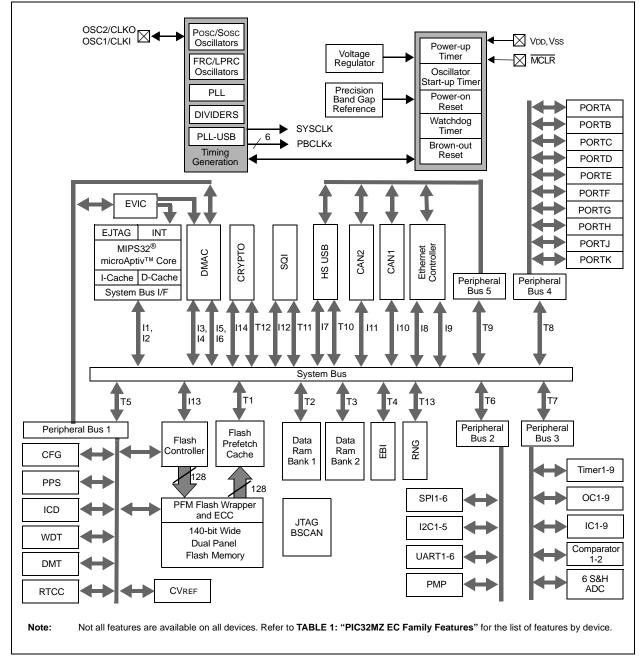

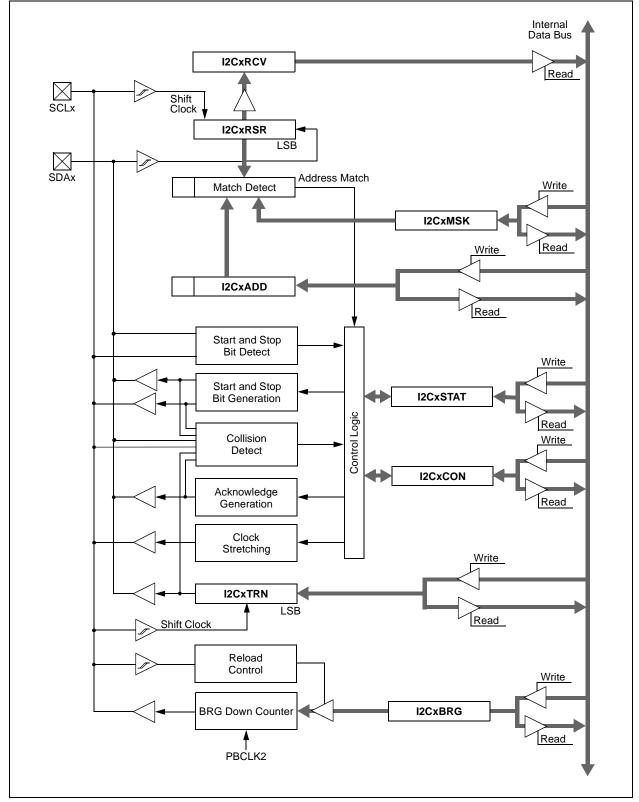

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EC family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

#### FIGURE 1-1: PIC32MZ EC FAMILY BLOCK DIAGRAM

#### **TABLE 1-20: SQI1 PINOUT I/O DESCRIPTIONS**

|          |                        | Pin Nu          | mber            |                          |             |                |                                     |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                         |  |

| SQICLK   | 57                     | 89              | A61             | 129                      | 0           | —              | Serial Quad Interface Clock         |  |

| SQICS0   | 52                     | 81              | A56             | 118                      | 0           | —              | Serial Quad Interface Chip Select 0 |  |

| SQICS1   | 53                     | 82              | B46             | 119                      | 0           |                | Serial Quad Interface Chip Select 1 |  |

| SQID0    | 58                     | 97              | B55             | 141                      | I/O         | ST             | Serial Quad Interface Data 0        |  |

| SQID1    | 61                     | 96              | A65             | 140                      | I/O         | ST             | Serial Quad Interface Data 1        |  |

| SQID2    | 62                     | 95              | B54             | 139                      | I/O         | ST             | Serial Quad Interface Data 2        |  |

| SQID3    | 63                     | 90              | B51             | 130                      | I/O         | ST             | Serial Quad Interface Data 3        |  |

| Legend:  | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power              |  |

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output

PPS = Peripheral Pin Select

I = Input

#### POWER, GROUND, AND VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS **TABLE 1-21:**

|          |                          | Pin Nu                                  | mber                                                         |                                                   |             |                |                                                                                             |

|----------|--------------------------|-----------------------------------------|--------------------------------------------------------------|---------------------------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP   | 100-pin<br>TQFP                         | 124-pin<br>VTLA                                              | 144-pin<br>TQFP/<br>LQFP                          | Pin<br>Type | Buffer<br>Type | Description                                                                                 |

|          |                          |                                         |                                                              |                                                   | Power a     | nd Ground      |                                                                                             |

| AVdd     | 19                       | 30                                      | B16                                                          | 41                                                | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times.                |

| AVss     | 20                       | 31                                      | A21                                                          | 42                                                | Р           | Р              | Ground reference for analog modules. This pin must be connected at all times                |

| Vdd      | 8, 26, 39,<br>54, 60     | 14, 37,<br>46, 62,<br>74, 83, 93        | B35,<br>A50,<br>A58, B53                                     |                                                   | Р           | _              | Positive supply for peripheral logic and I/O pins. This pin must be connected at all times. |

| Vss      | 7, 25, 35,<br>40, 55, 59 | 13, 36,<br>45, 53,<br>63, 75,<br>84, 92 | A9, B13,<br>B20,<br>B29,<br>A29,<br>A43,<br>A51,<br>B48, A63 | 17, 32,<br>54, 63,<br>75, 89,<br>108,<br>123, 136 | Ρ           | ľ              | Ground reference for logic, I/O pins, and USB. This pin must be connected at all times.     |

|          |                          |                                         |                                                              |                                                   | Voltage     | Reference      | ·                                                                                           |

| VREF+    | 16                       | 29                                      | A20                                                          | 40                                                | I           | Analog         | Analog Voltage Reference (High) Input                                                       |

| VREF-    | 15                       | 28                                      | B15                                                          | 39                                                | I           | Analog         | Analog Voltage Reference (Low) Input                                                        |

| •        | CMOS = CI<br>ST = Schmi  | •                                       | •                                                            | •                                                 | s           | O = Outpu      | Analog input     P = Power       ut     I = Input                                           |

TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

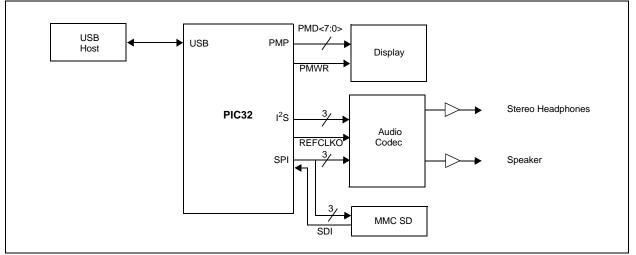

#### 2.11 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-9 and Figure 2-10.

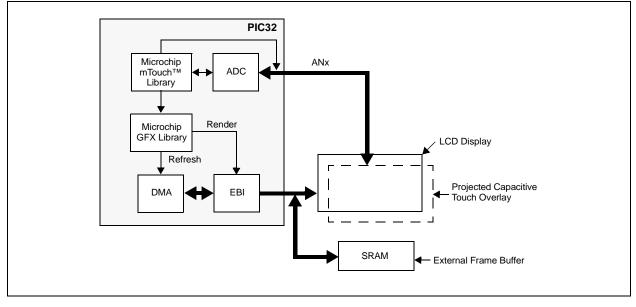

# FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

#### Physical Memory Map<sup>(1)</sup> 0x1FC74000 0x1FC70000 Sequence/Configuration Space<sup>(3)</sup> 0x1FC6FF00 Boot Flash 2 0x1FC60000 Reserved 0x1FC54028 Serial Number<sup>(5)</sup> 0x1FC54020 ADC Calibration Space<sup>(3)</sup> 0x1FC54000 0x1FC50000 Sequence/Configuration Space<sup>(4)</sup> 0x1FC4FF00 Boot Flash 1 0x1FC40000 Reserved 0x1FC34000 0x1FC30000 Unused Configuration Space(6) 0x1FC2FF00 Upper Boot Alias 0x1FC20000 Reserved 0x1FC14000 0x1FC10000 Configuration Space<sup>(2,3)</sup> 0x1FC0FF00 Lower Boot Alias 0x1FC00000 Note 1: Memory areas are not shown to scale. Memory locations 0x1FC0FF40 2: through 0x1FC0FFFC are used to initialize Configuration registers (see Section 34.0 "Special Features"). 3: Memory locations 0x1FC54000 through 0x1FC54010 are used to initialize the ADC Calibration registers (see Section 34.0 "Special Features"). Refer to Section 4.1.1 "Boot Flash 4: Sequence and Configuration Spaces" for more information. 5: Memory locations 0x1FC54020 and 0x1FC54024 contain a unique device serial number (see Section 34.0 "Special Features"). 6: This configuration space cannot be used for executing code in the upper

#### FIGURE 4-5: BOOT AND ALIAS MEMORY MAP

#### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | dress           |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| System Bus <sup>(1)</sup> | 0xBF8F0000 | 0x0000          |

| RNG                       |            | 0x6000          |

| Crypto                    | 7          | 0x5000          |

| USB                       | 0,405,0000 | 0x3000          |

| SQI1                      | 0xBF8E0000 | 0x2000          |

| EBI                       | 7          | 0x1000          |

| Prefetch                  | 7          | 0x0000          |

| Ethernet                  | 0.0000000  | 0x2000          |

| CAN1 and CAN2             | 0xBF880000 | 0x0000          |

| PORTA-PORTK               | 0xBF860000 | 0x0000          |

| Comparator 1, 2           |            | 0xC000          |

| ADC1                      | 7          | 0xB000          |

| OC1-OC9                   | 0xBF840000 | 0x4000          |

| IC1-IC9                   |            | 0x2000          |

| Timer1-Timer9             | 7          | 0x0000          |

| PMP                       |            | 0xE000          |

| UART1-UART6               | 0.0000000  | 0x2000          |

| SPI1-SPI6                 | 0xBF820000 | 0x1000          |

| I2C1-I2C5                 | 7          | 0x0000          |

| DMA                       | 0.000      | 0x1000          |

| Interrupt Controller      | 0xBF810000 | 0x0000          |

| PPS                       |            | 0x1400          |

| Oscillator                |            | 0x1200          |

| CVREF                     |            | 0x0E00          |

| RTCC                      | 0.0000000  | 0x0C00          |

| Deadman Timer             | 0xBF800000 | 0x0A00          |

| Watchdog Timer            | 1          | 0x0800          |

| Flash Controller          | 1          | 0x0600          |

| Configuration             | 7          | 0x0000          |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

boot alias.

#### TABLE 4-18: SYSTEM BUS TARGET 10 REGISTER MAP

| ess                         |                  | Ċ,        |       |       |       |          |          |       |       |      | Bits     |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             | A820 SBT10ELOG1  | 31:16     | MULTI | _     | _     | _        |          | CODE  | <3:0> |      |          | -     | _         | _    |        | _      | —       | _      | 0000          |

| A020                        | SBIIICELOGI      | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      |          | REGIO | N<3:0>    |      | -      | C      | MD<2:0> |        | 0000          |

| A824                        | SBT10ELOG2       | 31:16     | _     | _     | —     | —        | —        | —     | —     | —    | _        | _     | _         | _    | -      | _      | —       | _      | 0000          |

| A0Z4                        | 3BT IVELOG2      | 15:0      |       |       | —     | —        | —        | —     | —     | —    |          |       |           | —    |        | _      | GROU    | P<1:0> | 0000          |

| 1000                        | SBT10ECON        | 31:16     |       |       | —     | —        | —        | —     | —     | ERRP |          |       |           | —    |        | _      | _       | —      | 0000          |

| A828                        | SETTUECON        | 15:0      | —     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| A830                        | SBT10ECLRS       | 31:16     | —     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| A630                        | SBI IUECLKS      | 15:0      | —     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | CLEAR  | 0000          |

| A838                        | SBT10ECLRM       | 31:16     | —     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| A030                        | SETTUECLEN       | 15:0      | —     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | CLEAR  | 0000          |

| 4.0.40                      |                  | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| A840                        | SBT10REG0        | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   |      |          |       | SIZE<4:0: | >    |        | —      | —       | _      | xxxx          |

| 4.050                       | 00740000         | 31:16     | _     |       | —     | _        | _        | _     | _     | _    | —        | _     | —         | _    | —      | —      | —       | _      | xxxx          |

| A850                        | SBT10RD0         | 15:0      | _     |       | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 4.050                       |                  | 31:16     |       | —     | _     | _        |          | _     | _     |      | _        | _     | _         | _    | _      | _      | _       | _      | xxxx          |

| A858                        | SBT10WR0         | 15:0      |       | _     | _     | _        | _        | _     | _     | —    |          |       |           |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

© 2013-2016 Microchip Technology Inc.

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

|              |                   | $(\mathbf{X} = 0 - 13)$ |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                       | _                 | —                 | —                 | _                 | —                | —                |

| 00.40        | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                       |                   | _                 | —                 | _                 |                  | —                |

| 45.0         | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                       | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7:0          |                   | _                       |                   |                   | _                 | _                 |                  | CLEAR            |

|              |                   |                         |                   |                   |                   |                   |                  |                  |

## REGISTER 4-6: SBTxECLRS: SYSTEM BUS TARGET 'x' SINGLE ERROR CLEAR REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Single Error on Read bit A single error as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

**Note:** Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-7: SBTxECLRM: SYSTEM BUS TARGET 'x' MULTIPLE ERROR CLEAR REGISTER ('x' = 0-13)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   |                   | _                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   |                   | _                 |                   | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   |                   |                  | CLEAR            |

#### Legend:

| _ogonan           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Multiple Errors on Read bit Multiple errors as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

© 2013-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-1             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | PWPULOCK          | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | PWP<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | PWP<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | PWP<              | 7:0>              |                   |                  |                  |  |  |  |

#### REGISTER 5-6: NVMPWP: PROGRAM FLASH WRITE-PROTECT REGISTER

#### Legend:

| Legena.           |                  |                                          |

|-------------------|------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |

bit 31 **PWPULOCK:** Program Flash Memory Page Write-protect Unlock bit

1 = Register is not locked and can be modified

0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any reset.

bit 30-24 Unimplemented: Read as '0'

bit 23-0 PWP<23:0>: Flash Program Write-protect (Page) Address bits

Physical memory below address 0x1Dxxxxxx is write protected, where 'xxxxx' is specified by PWP<23:0>. When PWP<23:0> has a value of '0', write protection is disabled for the entire program Flash. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

**Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        |                     |                   |                   | CHPIGI            | N<7:0>            |                   |                  |                       |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | —                 | —                 | _                 | —                | —                     |

| 45-0         | R/W-0               | U-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | _                 | CHIPGNEN          | —                 | CHPATLEN          | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

#### REGISTER 10-7: DCHxCON: DMA CHANNEL x CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-24 CHPIGN<7:0>: Channel Register Data bits

Pattern Terminate mode:

Any byte matching these bits during a pattern match may be ignored during the pattern match determination when the CHPIGNEN bit is set. If a byte is read that is identical to this data byte, the pattern match logic will treat it as a "don't care" when the pattern matching logic is enabled and the CHPIGEN bit is set.

#### bit 23-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **CHPIGNEN:** Enable Pattern Ignore Byte bit

- 1 = Treat any byte that matches the CHPIGN<7:0> bits as a "don't care" when pattern matching is enabled

0 = Disable this feature

- bit 12 Unimplemented: Read as '0'

- bit 11 CHPATLEN: Pattern Length bit

- 1 = 2 byte length

- 0 = 1 byte length

#### bit 10-9 Unimplemented: Read as '0'

- bit 8 **CHCHNS:** Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

bit 7

- 0 = Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

- bit 5 CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

# PIC32MZ Embedded Connectivity (EC) Family

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|----------------------|-------------------|-------------------|---------------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0                  | U-0               | U-0               | U-0                       | U-0 U-0           |                  | U-0              |  |

| 31:24        | —                 | -                    | _                 | _                 |                           |                   | _                | —                |  |

| 00.40        | U-0               | U-0                  | U-0               | U-0               | U-0                       | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                    | _                 | _                 | _                         | _                 | _                | —                |  |

| 45-0         | R-0               | R/W-0                | R/W-0             | R/W-0             | R/W-0 R/W-0               |                   | R/W-0            | R/W-0            |  |

| 15:8         | BUSY              | IRQM                 | <1:0>             | INCM              | <1:0>                     | MODE16            | MODE<1:0>        |                  |  |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0 R/W-0               |                   | R/W-0            | R/W-0            |  |

| 7:0          | WAITB             | <1:0> <sup>(1)</sup> |                   | WAITM             | WAITE<1:0> <sup>(1)</sup> |                   |                  |                  |  |

#### REGISTER 23-2: PMMODE: PARALLEL PORT MODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

- bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

#### bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<15:0> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<15:0> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

#### bit 10 MODE16: 8/16-bit Mode bit

- 1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

- 0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

#### bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, and PMD<15:0>)<sup>(3)</sup>

- 10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, and PMD<15:0>)(3)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCSx, PMD<7:0>, and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCSx, and PMD<7:0>)

#### bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPBCLK2; multiplexed address phase of 4 TPBCLK2

- 10 = Data wait of 3 TPBCLK2; multiplexed address phase of 3 TPBCLK2

- 01 = Data wait of 2 TPBCLK2; multiplexed address phase of 2 TPBCLK2

- 00 = Data wait of 1 TPBCLK2; multiplexed address phase of 1 TPBCLK2 (default)

## **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK2 cycle for a write operation; WAITB = 1 TPBCLK2 cycle, WAITE = 0 TPBCLK2 cycles for a read operation.

- 2: Address bits 14 and 15 are is not subject to auto-increment/decrement if configured as Chip Select.

- 3: The PMD<15:8> bits are not active is the MODE16 bit = 1.

| Bit<br>Range | Bit<br>31/23/15/7 |       |        | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------|--------|-----------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | R/W-0 | R/W-0  | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31:24        | IVRIE             | WAKIE | CERRIE | SERRIE                | RBOVIE            | _                 | —                | —                |

| 23:16        | U-0               | U-0   | U-0    | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | _     | —      | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0 | R/W-0  | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF | CERRIF | SERRIF <sup>(1)</sup> | RBOVIF            | _                 | —                | —                |

| 7:0          | U-0               | U-0   | U-0    | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _     | _      | _                     | MODIF             | CTMRIF            | RBIF             | TBIF             |

#### **REGISTER 29-3: CIINT: CAN INTERRUPT REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | <ul> <li>IVRIE: Invalid Message Received Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                       |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                          |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                  |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                             |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                    |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                           |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                          |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by                                                                                             |

Note 1: This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24        |                   |                   |                   | _                 | _                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16        |                   |                   |                   |                   | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |

| 15:8         |                   |                   |                   | _                 | _                 | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |

| 7:0          | _                 | _                 | _                 |                   | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

#### **REGISTER 29-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-27 Unimplemented: Read as '0'

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------|

|           | 1 = Interrupt enabled for FIFO not full                                                                         |

|           | 0 = Interrupt disabled for FIFO not full                                                                        |

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

| h:+ 0.4   | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit                                                      |

|           | <ul><li>1 = Interrupt enabled for FIFO empty</li><li>0 = Interrupt disabled for FIFO empty</li></ul>            |

| hit 23-20 | Unimplemented: Read as '0'                                                                                      |

| bit 19    | <b>RXOVFLIE:</b> Overflow Interrupt Enable bit                                                                  |

| DIC 15    | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

|           | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 16    | RXNEMPTYIE: Empty Interrupt Enable bit                                                                          |

|           | <ul> <li>1 = Interrupt enabled for FIFO not empty</li> <li>0 = Interrupt disabled for FIFO not empty</li> </ul> |

| hi+ 15 11 |                                                                                                                 |

|           | Unimplemented: Read as '0'                                                                                      |

| bit 10    | <b>TXNFULLIF:</b> Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                      |

|           | <u>TXEN = 1:</u> (FIFO configured as a Transmit Buffer)<br>1 = FIFO is not full                                 |

|           | 0 = FIFO is full                                                                                                |

|           | TXEN = 0: (FIFO configured as a Receive Buffer)                                                                 |

|           | Unused, reads '0'                                                                                               |

|           |                                                                                                                 |

**Note 1:** This bit is read-only and reflects the status of the FIFO.

#### REGISTER 30-17: ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK STATISTICS REGISTER

| Bit<br>Range | e Bit Bit Bit 31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0                                 | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | —                                   | —     | -                 |                   |                   |                   | -                | —                |  |  |  |  |  |

| 23:16        | U-0                                 | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        | —                                   | —     | _                 | _                 | _                 | _                 | —                | —                |  |  |  |  |  |

| 15.0         | R/W-0                               | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | FRMTXOKCNT<15:8>                    |       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0 R/W-0                         |       | R/W-0 R/W-0       |                   | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                                     |       |                   | FRMTXOK           | (CNT<7:0>         |                   |                  |                  |  |  |  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

#### 31.1 Comparator Control Registers

#### TABLE 31-1: COMPARATOR REGISTER MAP

| ess                                                            |                                 | â         |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |      |       |       | ú         |

|----------------------------------------------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|------|-------|-------|-----------|

| Virtual Address<br>(BF84_#)<br>Register<br>Name <sup>(1)</sup> | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Reset |

| C000                                                           | CM1CON                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _      | _    | _    | _    | _    | _     | _     | 0000      |

| C000                                                           | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | —     | _     | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | —    | _    | CCH   | <1:0> | 00C3      |

| C010                                                           | CM2CON                          | 31:16     | _     | _     | _     | —     | _     | —     | —    | _    | _    | —      | _    | —    | —    | _    | —     | _     | 0000      |

| 0010                                                           | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     | —     | —     | —    | COUT | EVPO | L<1:0> | —    | CREF | -    | —    | CCH   | <1:0> | 00C3      |

| 0060                                                           | CMSTAT                          | 31:16     | —     | _     | _     | —     | —     | —     | —    | _    | _    | —      | _    | —    | —    | _    | —     | _     | 0000      |

| 000                                                            | CMSTAT                          | 15:0      | _     | _     | SIDL  | _     | —     | —     | —    | —    | —    | —      | _    | _    | —    | _    | C2OUT | C10UT | 0000      |

| 1                                                              |                                 |           |       |       |       |       |       |       |      |      |      |        |      |      |      |      |       |       |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 |                   | -                 | _                 | -                 |                  | _                |

| 00.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 |                   | -                 | _                 |                   |                  | —                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | SIDL              |                   | _                 |                   |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7.0          |                   | _                 |                   |                   |                   |                   | C2OUT            | C1OUT            |

#### REGISTER 31-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in IDLE Control bit

- 1 = All Comparator modules are disabled in IDLE mode

- 0 = All Comparator modules continue to operate in the IDLE mode

#### bit 12-2 Unimplemented: Read as '0'

- bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 C1OUT: Comparator Output bit

- 1 =Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

#### 33.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of the PIC32MZ Embedded Connectivity       |

|       | (EC) Family of devices. It is not intended |

|       |                                            |

|       | to be a comprehensive reference source.    |

|       | To complement the information in this      |

|       | data sheet, refer to Section 10. "Power-   |

|       | Saving Features" (DS60001130), which       |

|       | is available from the Documentation >      |

|       | Reference Manual section of the            |

|       | Microchip PIC32 web site                   |

|       | (www.microchip.com/pic32).                 |

This section describes power-saving features for the PIC32MZ EC devices. These devices offer various methods and modes that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

#### 33.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the speed of PBCLK7, or selecting a lower power clock source (i.e., LPRC or Sosc).

In addition, the Peripheral Bus Scaling mode is available for each peripheral bus where peripherals are clocked at reduced speed by selecting a higher divider for the associated PBCLKx, or by disabling the clock completely.

### 33.2 Power-Saving with CPU Halted

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 33.2.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted and the associated clocks are disabled. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the peripheral bus clocks will start running and the device will enter into Idle mode.

#### 33.2.2 IDLE MODE

In Idle mode, the CPU is Halted; however, all clocks are still enabled. This allows peripherals to continue to operate. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### TABLE 37-20: INTERNAL FRC ACCURACY

| AC CHA        |                        | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |   |    |   |                                        |  |

|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|----|---|----------------------------------------|--|

| Param.<br>No. | Characteristics        | Min. Typ. Max. Units Conditions                                                                                                                 |   |    |   | Conditions                             |  |

| Internal      | FRC Accuracy @ 8.00 MH | z <sup>(1)</sup>                                                                                                                                |   |    |   |                                        |  |

| F20           | FRC                    | -5                                                                                                                                              | — | +5 | % | $0^{\circ}C \le TA \le +85^{\circ}C$   |  |

|               |                        | -8                                                                                                                                              | _ | +8 | % | $-40^{\circ}C \le TA \le +85^{\circ}C$ |  |

Note 1: Frequency calibrated at +25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 37-21: INTERNAL LPRC ACCURACY

| AC CHA        | RACTERISTICS                     | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |     |   |                                      |  |

|---------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|---|--------------------------------------|--|

| Param.<br>No. | Characteristics                  | Min. Typ. Max. Units Conditions                                                                                                                 |  |     |   |                                      |  |

| Internal      | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                 |  |     |   |                                      |  |

| F21           | LPRC                             | -8                                                                                                                                              |  | +8  | % | $0^{\circ}C \le TA \le +85^{\circ}C$ |  |

|               |                                  | -25                                                                                                                                             |  | +25 | % | $-40^{\circ}C \le TA < +85^{\circ}C$ |  |

Note 1: Change of LPRC frequency as VDD changes.

#### TABLE 37-22: INTERNAL BACKUP FRC (BFRC) ACCURACY

| AC CHA                                      | RACTERISTICS    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |       |            |  |

|---------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Param.<br>No.                               | Characteristics | Min.                                                                                                                                            | Тур. | Max. | Units | Conditions |  |

| Internal BFRC Accuracy @ 8 MHz <sup>I</sup> |                 |                                                                                                                                                 |      |      |       |            |  |

| F22                                         | BFRC            | -30                                                                                                                                             | _    | +30  | %     | —          |  |

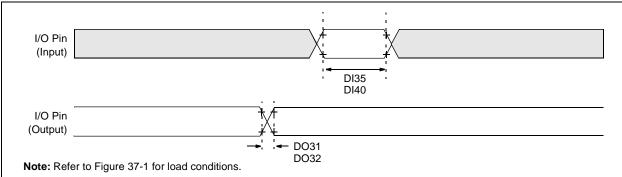

#### TABLE 37-23: I/O TIMING REQUIREMENTS

| AC CHAI       | RACTERIS                                                                                                                                                                                                                                                                                                | STICS                                                                                                                                       | (unless other           | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                     |      |               |               |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------------|---------------|--|--|

| Param.<br>No. | Symbol                                                                                                                                                                                                                                                                                                  | Characteris                                                                                                                                 | stics <sup>(2)</sup>    | Min.                                                                                                                                            | Тур. <sup>(1)</sup> | Max. | Units         | Conditions    |  |  |

| DO31          | TIOR                                                                                                                                                                                                                                                                                                    | Port Output Rise Time<br>I/O Pins:<br>4x Source Driver Pins -<br>RA3, RA9, RA10, RA14, RA15<br>RB0-7, RB11, RB13<br>RC12-RC15               |                         | _                                                                                                                                               | _                   | 9.5  | ns            | Cload = 50 pF |  |  |

|               | RC12-RC13<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11<br><b>Port Output Rise Time</b><br>I/O Pins:<br>8x Source Driver Pins -<br>RA0-RA2, RA4, RA5<br>RB8-RB10, RB12, RB14, RB15<br>RC1-RC4<br>RD1-RD5, RD9, RD10, RD12, |                                                                                                                                             | 6, RH8-RH13             | _                                                                                                                                               | _                   | 6    | ns            | Cload = 20 pF |  |  |

|               |                                                                                                                                                                                                                                                                                                         |                                                                                                                                             | ns -<br>5<br>RB14, RB15 | _                                                                                                                                               | _                   | 8    | ns            | Cload = 50 pF |  |  |

|               |                                                                                                                                                                                                                                                                                                         | RD13, RD15<br>RE4-RE7<br>RF0, RF4, RF5, RF12, RF13<br>RG0, RG1, RG6-RG9<br>RH2, RH3, RH7, RH14, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15<br>RK0-RK7 |                         | _                                                                                                                                               | _                   | 6    | ns            | CLOAD = 20 pF |  |  |

|               | Port Output Rise Time<br>I/O Pins:<br>12x Source Driver Pins -<br>RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                                                                                                                                                                                               |                                                                                                                                             |                         | _                                                                                                                                               | _                   | 3.5  | ns            | CLOAD = 50 pF |  |  |

|               |                                                                                                                                                                                                                                                                                                         |                                                                                                                                             | _                       | _                                                                                                                                               | 2                   | ns   | CLOAD = 20 pF |               |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

#### TABLE 37-26: TIMER2-TIMER9 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS | TICS                                                      | (unless                     | ard Operating Conditions: 2.3V to 3.6V<br>s otherwise stated)<br>ting temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |                |                                        |                                                      |

|---------------|-----------|-----------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|----------------|----------------------------------------|------------------------------------------------------|

| Param.<br>No. | Symbol    | Cha                                                       | racteristics <sup>(1)</sup> | Min.                                                                                                                                    | Max. | Units          | Conditions                             |                                                      |

| TB10          | ТтхН      | TxCK<br>High Time                                         | Synchronous, with prescaler | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                                                                  |      | ns             | Must also<br>meet<br>parameter<br>TB15 | N = prescale<br>value<br>(1, 2, 4, 8,<br>16, 32, 64, |

| TB11          | TTXL      | TxCK<br>Low Time                                          | Synchronous, with prescaler | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                                                                  | —    | ns             | Must also<br>meet<br>parameter<br>TB15 | 256)                                                 |

| TB15          | ΤτχΡ      | TxCK<br>Input                                             | Synchronous, with prescaler | [(Greater of [(25 ns or<br>2 TPBCLK3)/N] + 30 ns                                                                                        |      | ns             | VDD > 2.7V                             |                                                      |

|               |           | Period                                                    |                             | [(Greater of [(25 ns or<br>2 TPBCLK3)/N] + 50 ns                                                                                        | —    | ns             | VDD < 2.7V                             |                                                      |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                             | _                                                                                                                                       | 1    | <b>TPBCLK3</b> |                                        | —                                                    |

Note 1: These parameters are characterized, but not tested in manufacturing.

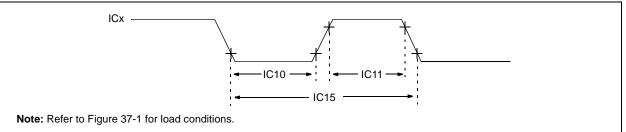

#### FIGURE 37-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 37-27: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |           | (unless oth              | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |                                         |                                  |  |  |

|--------------------|--------|-----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------|----------------------------------|--|--|

| Param.<br>No.      | Symbol | Charac    | teristics <sup>(1)</sup> | Min.                                                                                                                                                    | Max. | Units | Con                                     | ditions                          |  |  |

| IC10               | TccL   | ICx Input | Low Time                 | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                                                                                  | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |  |  |

| IC11               | TccH   | ICx Input | : High Time              | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                                                                                  | -    | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |  |  |

| IC15               | TccP   | ICx Input | Period                   | [(25 ns or 2 TPBCLK3)<br>/N] + 50 ns                                                                                                                    | —    | ns    | —                                       |                                  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

#### TABLE A-4: CPU DIFFERENCES (CONTINUED)

| PIC32MX5XX/6XX/7XX Feature                                                                                                         | PIC32MZ Feature                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Core Instruction Execution                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| On PIC32MX devices, the CPU can execute MIPS16e instruc-<br>tions and uses a 16-bit instruction set, which reduces memory<br>size. | On PIC32MZ devices, the CPU can operate a mode called microMIPS. microMIPS mode is an enhanced MIPS32® instruction set that uses both 16-bit and 32-bit opcodes. This mode of operation reduces memory size with minimum performance impact.                                                                                                                                                                                                             |  |  |  |  |  |  |