Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-TQFP                                                                          |

| Supplier Device Package    | 144-TQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecg144t-i-ph |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-20: SQI1 PINOUT I/O DESCRIPTIONS**

|          |                        | Pin Nu          | mber            |                          |             |                |                                     |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                         |  |  |

| SQICLK   | 57                     | 89              | A61             | 129                      | 0           | —              | Serial Quad Interface Clock         |  |  |

| SQICS0   | 52                     | 81              | A56             | 118                      | 0           | —              | Serial Quad Interface Chip Select 0 |  |  |

| SQICS1   | 53                     | 82              | B46             | 119                      | 0           |                | Serial Quad Interface Chip Select 1 |  |  |

| SQID0    | 58                     | 97              | B55             | 141                      | I/O         | ST             | Serial Quad Interface Data 0        |  |  |

| SQID1    | 61                     | 96              | A65             | 140                      | I/O         | ST             | Serial Quad Interface Data 1        |  |  |

| SQID2    | 62                     | 95              | B54             | 139                      | I/O         | ST             | Serial Quad Interface Data 2        |  |  |

| SQID3    | 63                     | 90              | B51             | 130                      | I/O         | ST             | Serial Quad Interface Data 3        |  |  |

| Legend:  | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power              |  |  |

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output

PPS = Peripheral Pin Select

I = Input

#### POWER, GROUND, AND VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS **TABLE 1-21:**

|          |                          | Pin Nu                                  | mber                                                         |                                                   |             |                |                                                                                             |

|----------|--------------------------|-----------------------------------------|--------------------------------------------------------------|---------------------------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP   | 100-pin<br>TQFP                         | 124-pin<br>VTLA                                              | 144-pin<br>TQFP/<br>LQFP                          | Pin<br>Type | Buffer<br>Type | Description                                                                                 |

|          |                          |                                         |                                                              |                                                   | Power a     | nd Ground      |                                                                                             |

| AVdd     | 19                       | 30                                      | B16                                                          | 41                                                | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times.                |

| AVss     | 20                       | 31                                      | A21                                                          | 42                                                | Р           | Р              | Ground reference for analog modules. This pin must be connected at all times                |

| Vdd      | 8, 26, 39,<br>54, 60     | 14, 37,<br>46, 62,<br>74, 83, 93        | B35,<br>A50,<br>A58, B53                                     |                                                   | Р           | _              | Positive supply for peripheral logic and I/O pins. This pin must be connected at all times. |

| Vss      | 7, 25, 35,<br>40, 55, 59 | 13, 36,<br>45, 53,<br>63, 75,<br>84, 92 | A9, B13,<br>B20,<br>B29,<br>A29,<br>A43,<br>A51,<br>B48, A63 | 17, 32,<br>54, 63,<br>75, 89,<br>108,<br>123, 136 | Ρ           | ľ              | Ground reference for logic, I/O pins, and USB. This pin must be connected at all times.     |

|          |                          |                                         |                                                              |                                                   | Voltage     | Reference      | ·                                                                                           |

| VREF+    | 16                       | 29                                      | A20                                                          | 40                                                | I           | Analog         | Analog Voltage Reference (High) Input                                                       |

| VREF-    | 15                       | 28                                      | B15                                                          | 39                                                | I           | Analog         | Analog Voltage Reference (Low) Input                                                        |

| •        | CMOS = CI<br>ST = Schmi  | •                                       | •                                                            | •                                                 | s           | O = Outpu      | Analog input     P = Power       ut     I = Input                                           |

TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

#### 3.2 Architecture Overview

The MIPS32 microAptiv Microprocessor core in PIC32MZ EC family devices contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System control coprocessor (CP0)

- Memory Management Unit (MMU)

- Instruction/Data cache controllers

- Power Management

- Instructions and data caches

- microMIPS support

- Enhanced JTAG (EJTAG) controller

#### 3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. Seven additional register file shadow sets (containing thirty-two registers) are added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- · Shifter and store aligner

- DSP ALU and logic block for performing DSP instructions, such as arithmetic/shift/compare operations

#### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations, and DSP ASE multiply instructions. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x32 booth recoded multiplier, four pairs of result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x32) represents the *rs* operand. The second number ('32' of 32x32) represents the *rt* operand.

The MDU supports execution of one multiply or multiply-accumulate operation every clock cycle.

Divide operations are implemented with a simple 1-bitper-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the processor core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

|                                | DE UNIT LATENCIES AND REFEA                    | I KAILS |             |

|--------------------------------|------------------------------------------------|---------|-------------|

| Opcode                         | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

| MULT/MULTU, MADD/MADDU,        | 16 bits                                        | 5       | 1           |

| MSUB/MSUBU (HI/LO destination) | 32 bits                                        | 5       | 1           |

| MUL (GPR destination)          | 16 bits                                        | 5       | 1           |

|                                | 32 bits                                        | 5       | 1           |

| DIV/DIVU                       | 8 bits                                         | 12/14   | 12/14       |

|                                | 16 bits                                        | 20/22   | 20/22       |

|                                | 24 bits                                        | 28/30   | 28/30       |

|                                | 32 bits                                        | 36/38   | 36/38       |

# TABLE 3-1: MIPS32 microAptiv MICROPROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| ss                          |                  |           |          |                                                |           |            |             |             |          | Bi         | its           |                |       |      |      |      |      |      |          |

|-----------------------------|------------------|-----------|----------|------------------------------------------------|-----------|------------|-------------|-------------|----------|------------|---------------|----------------|-------|------|------|------|------|------|----------|

| Virtual Address<br>(BFC4_#) | Register<br>Name | Bit Range | 31/15    | 30/14                                          | 29/13     | 28/12      | 27/11       | 26/10       | 25/9     | 24/8       | 23/7          | 22/6           | 21/5  | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 |          |

| FF40                        | ABF1DEVCFG3      | 31:0      |          |                                                | 1         |            |             | 1           |          |            |               |                | 1     |      |      |      |      | 1    | xx       |

| FF44                        | ABF1DEVCFG2      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | xx       |

| FF48                        | ABF1DEVCFG1      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | xx       |

| FF4C                        | ABF1DEVCFG0      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FF50                        | ABF1DEVCP3       | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      |          |

| FF54                        | ABF1DEVCP2       | 31:0      |          | Note: See Table 34-2 for the bit descriptions. |           |            |             |             |          |            |               |                |       |      |      |      |      |      |          |

| FF58                        | ABF1DEVCP1       | 31:0      |          |                                                |           |            |             |             | Note. Se |            |               | it description | 5115. |      |      |      |      |      | x        |

| FF5C                        | ABF1DEVCP0       | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FF60                        | ABF1DEVSIGN3     | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FF64                        | ABF1DEVSIGN2     | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FF68                        | ABF1DEVSIGN1     | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FF6C                        | ABF1DEVSIGN0     | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | xx       |

| FF70                        | ABF1SEQ3         | 31:16     | —        | —                                              | —         | —          | —           | —           | —        | —          | —             | —              | —     | —    | —    | —    | —    | —    | xz       |

| 1170                        | ADI IGLQ3        | 15:0      | _        |                                                | _         |            |             | _           |          | _          |               |                | _     | _    |      | _    | _    | _    | x        |

| FF74                        | ABF1SEQ2         | 31:16     | -        | _                                              | -         | —          | —           |             | -        | —          | _             | _              |       | -    | _    | —    | —    | -    | x        |

| FF/4                        | ADFISEQ2         | 15:0      | _        | —                                              | —         |            |             | —           | —        | -          | —             | —              | —     | —    | —    | _    | _    | —    | xx       |

|                             | 10510501         | 31:16     | _        |                                                | _         | _          | _           | _           |          | _          | _             | _              | _     | _    | _    | _    | _    | _    | XX       |

| FF/8                        | ABF1SEQ1         | 15:0      | _        | _                                              | _         | _          | _           | _           |          | _          | _             | _              | _     | _    | _    | _    | _    | _    | XX       |

|                             | 10510500         | 31:16     |          | CSEQ<15:0> xxx                                 |           |            |             |             |          |            |               |                |       |      |      |      |      |      |          |

| FF/C                        | ABF1SEQ0         | 15:0      |          |                                                |           |            |             |             |          | TSEQ       | <15:0>        |                |       |      |      |      |      |      | xx       |

| FFC0                        | BF1DEVCFG3       | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

|                             | BF1DEVCFG2       | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | xx       |

| FFC8                        | BF1DEVCFG1       | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

|                             | BF1DEVCFG0       | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FFD0                        | BF1DEVCP3        | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | xx       |

| FFD4                        | BF1DEVCP2        | 31:0      |          |                                                |           |            |             |             | Nata: Ca | a Tabla 24 | 1 for the h   | it descriptio  |       |      |      |      |      |      | x        |

| FFD8                        | BF1DEVCP1        | 31:0      |          |                                                |           |            |             |             | Note: Se | e Table 34 | - i loi the b | it description | JNS.  |      |      |      |      |      | x        |

| FFDC                        | BF1DEVCP0        | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FFE0                        | BF1DEVSIGN3      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FFE4                        | BF1DEVSIGN2      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FFE8                        | BF1DEVSIGN1      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

| FFEC                        | BF1DEVSIGN0      | 31:0      |          |                                                |           |            |             |             |          |            |               |                |       |      |      |      |      |      | x        |

|                             | BF1SEQ3          | 31:16     | -        | _                                              |           | —          | —           | -           | _        | —          | _             | _              | -     | -    | _    | —    | —    |      | x        |

| FFF0                        | BF ISEQ3         | 15:0      | _        | _                                              | _         | _          | _           | _           | _        | _          | _             | _              | _     | _    | _    | _    | _    | _    | xz       |

|                             |                  | 31:16     | _        | _                                              | _         | _          | _           | _           | _        | _          | _             | _              | _     | _    | _    | _    | _    | _    | x        |

| FFF4                        | BF1SEQ2          | 15:0      | _        | _                                              | _         | _          | _           | _           | _        | _          | _             | _              | _     | _    | _    | _    | _    | _    | x        |

|                             |                  | 31:16     | _        | _                                              | _         | _          | _           | _           | _        | _          | _             | _              | _     | _    | _    | _    | _    | _    | x>       |

| FFF8                        | BF1SEQ1          | 15:0      | _        | _                                              | _         | _          | _           | —           | _        | _          | _             | _              | _     | _    | _    | _    | _    | —    | XX       |

|                             | DE40500          | 31:16     |          |                                                |           |            |             |             |          | CSEQ       | <15:0>        |                |       |      |      |      |      |      | xx       |

| FFFC                        | BF1SEQ0          | 15:0      |          | TSEQ<15:0>                                     |           |            |             |             |          |            |               |                |       |      |      |      |      |      |          |

| Legen                       | d - v - unknow   |           | on Reset | — = Rese                                       | rved read | as '1' Res | et values a | re shown ir | hexadeci |            |               |                |       |      |      |      |      |      | <u> </u> |

PIC32MZ Embedded

**Connectivity**

(EC) Family

#### TABLE 4-2: BOOT FLASH 1 SEQUENCE AND CONFIGURATION WORDS SUMMARY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | NVMDATA<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |

#### **REGISTER 5-4:** NVMDATAX: FLASH DATA REGISTER (x = 0-3)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 NVMDATA<31:0>: Flash Data bits

Word Program: Writes NVMDATA0 to the target Flash address defined in NVMADDR Quad Word Program: Writes NVMDATA3:NVMDATA2:NVMDATA1:NVMDATA0 to the target Flash address defined in NVMADDR. NVMDATA0 contains the Least Significant Instruction Word.

**Note:** The bits in this register are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

#### REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | NVMSRCADDR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

**Note:** The bits in this register are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

### 7.1 CPU Exceptions

CPU coprocessor 0 contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events or program errors. Table 7-1 lists the exception types in order of priority.

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> MICROPROCESSOR CORE EXCEPTION TYPES

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                                                      | Branches to                       | Status<br>Bits Set | Debug Bits<br>Set | EXCCODE | XC32 Function Name         |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------|-------------------|---------|----------------------------|

|                                             |                                                                                                                                  | Highest Priority                  |                    |                   |         |                            |

| Reset                                       | Assertion MCLR or a Power-on Reset (POR).                                                                                        | 0xBFC0_0000                       | BEV, ERL           | —                 | —       | _on_reset                  |

| Soft Reset                                  | Assertion of a software Reset.                                                                                                   | 0xBFC0_0000                       | BEV, SR,<br>ERL    | _                 | _       | _on_reset                  |

| DSS                                         | EJTAG debug single step.                                                                                                         | 0xBFC0_0480                       | —                  | DSS               | —       |                            |

| DINT                                        | EJTAG debug interrupt. Caused by the assertion of the external EJ_DINT input or by setting the EjtagBrk bit in the ECR register. | 0xBFC0_0480                       | —                  | DINT              | _       | _                          |

| NMI                                         | Assertion of NMI signal.                                                                                                         | 0xBFC0_0000                       | BEV, NMI,<br>ERL   | —                 | —       | _nmi_handler               |

| Machine Check                               | TLB write that conflicts with an existing entry.                                                                                 | EBASE+0x180                       | MCHECK,<br>EXL     | —                 | 0x18    | _general_exception_handler |

| Interrupt                                   | Assertion of unmasked hardware or software inter-<br>rupt signal.                                                                | See Table 7-2.                    | IPL<2:0>           | —                 | 0x00    | See Table 7-2.             |

| Deferred Watch                              | Deferred watch (unmasked by K DM=>!(K DM) transition).                                                                           | EBASE+0x180                       | WP, EXL            | —                 | 0x17    | _general_exception_handler |

| DIB                                         | EJTAG debug hardware instruction break matched.                                                                                  | 0xBFC0_0480                       | _                  | DIB               | _       | _                          |

| WATCH                                       | A reference to an address that is in one of the Watch registers (fetch).                                                         | EBASE+0x180                       | EXL                | —                 | 0x17    | _general_exception_handler |

| AdEL                                        | Fetch address alignment error. Fetch reference to protected address.                                                             | EBASE+0x180                       | EXL                | —                 | 0x04    | _general_exception_handler |

| TLBL                                        | Fetch TLB miss or fetch TLB hit to page with $V = 0$ .                                                                           | EBASE if Status.EXL = 0           | _                  | —                 | 0x02    | _                          |

|                                             |                                                                                                                                  | EBASE+0x180 if<br>Status.EXL == 1 | —                  | —                 | 0x02    | _general_exception_handler |

| TLBL Execute<br>Inhibit                     | An instruction fetch matched a valid TLB entry that had the XI bit set.                                                          | EBASE+0x180                       | EXL                | —                 | 0x14    | _general_exception_handler |

| IBE                                         | Instruction fetch bus error.                                                                                                     | EBASE+0x180                       | EXL                | —                 | 0x06    | _general_exception_handler |

# PIC32MZ Embedded Connectivity **E**C Family

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0                |  |

| 31:24        | —                 | —                 | —                 | _                 | _                 | FRCDIV<2:0>       |                  |                      |  |

| 00.46        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 23:16        | DRMEN             | SOSCRDY           | —                 | _                 | _                 | —                 | —                | —                    |  |

| 45.0         | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y                |  |

| 15:8         | —                 |                   | COSC<2:0>         |                   | _                 | NOSC<2:0>         |                  |                      |  |

| 7.0          | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0, HS         | U-0               | R/W-y            | R/W-y                |  |

| 7:0          | CLKLOCK           | ULOCK             | SLOCK             | SLPEN             | CF                |                   | SOSCEN           | OSWEN <sup>(1)</sup> |  |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | onfiguration bits on POR | HS = Hardware Set  |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit    | , read as '0'      |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-27 Unimplemented: Read as '0'

bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2

- 000 = FRC divided by 1 (default setting)

- bit 23 DRMEN: Dream Mode Enable bit

- 1 = Dream mode is enabled

- 0 = Dream mode is disabled

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21-15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)

- 110 = Back-up Fast RC (BFRC) Oscillator

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Reserved

- 010 = Primary Oscillator (Posc) (HS or EC)

- 001 = System PLL (SPLL)

- 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)

- bit 11 Unimplemented: Read as '0'

- **Note 1:** The reset value for this bit depends on the setting of the IESO (DEVCFG1<7>) bit. When IESO = 1, the reset value is '1'. When IESO = 0, the reset value is '0'.

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 | -                   | —                | —                |

| 22.46        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 23:16        |                   | -                 |                   |                   |                   |                     |                  | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                   | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | _                 |                   |                   |                   | TUN<              | 5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced |

|-------|-----------------------------------------------------------------------------------------------------|

|       | PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.                               |

#### TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ess                          |                                 |               |        |       |          |       |                |       |      | Bit    | s      |        |        |        |        |        |        |         |    |

|------------------------------|---------------------------------|---------------|--------|-------|----------|-------|----------------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|----|

| VII LUAI AULIESS<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13    | 28/12 | 27/11          | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0    |    |

|                              | DCH1SSIZ                        | 31:16         | _      |       | —        |       |                | _     |      | —      |        | —      | _      | _      | _      |        | _      |         | 00 |

| 170                          | DCITI3312                       | 15:0          |        |       |          |       |                |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |         | 00 |

| 180                          | DCH1DSIZ                        | 31:16         | _      | _     | —        | _     | —              | _     | —    | _      | _      | —      | —      | —      | —      | —      | —      | —       | 0  |

| 100                          | DCITIDOIZ                       | 15:0          |        |       |          |       |                |       |      | CHDSIZ | <15:0> | -      | -      | -      |        |        | -      |         | 0  |

| 100                          | DCH1SPTR                        | 31:16         | —      | —     | —        | _     | —              | _     | —    | —      | —      |        |        |        | _      | —      | —      | —       | 0  |

| 190                          |                                 | 15:0          |        |       |          |       |                |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |         | 0  |

| 140                          | DCH1DPTR                        | 31:16         | —      | —     | —        | —     | —              | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —       | 0  |

| / 10                         |                                 | 15:0          |        |       |          |       |                |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |         | (  |

| B0                           | DCH1CSIZ                        | 31:16         | _      |       | —        | _     |                | _     | _    | _      | —      | —      | _      | —      | —      | —      | —      | —       | (  |

| 50                           |                                 | 15:0          |        |       |          |       |                |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |         | (  |

| CO                           | DCH1CPTR                        | 31:16         | _      |       | —        | _     |                | _     | _    | _      | —      | —      | _      | —      | —      | —      | —      | —       | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |         | (  |

| D0                           | DCH1DAT                         | 31:16         | —      | _     | —        | _     | —              | _     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —       | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      | CHPDAT | <15:0> |        |        |        |        |        | -      |         | (  |

| IE0                          | DCH2CON                         | 31:16         |        |       |          | CHPIG |                |       |      |        | -      | —      | —      | —      | —      | —      | —      | —       | (  |

|                              |                                 | 15:0          | CHBUSY | —     | CHPIGNEN | —     | CHPATLEN       | —     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | 21<1:0> | (  |

| IF0                          | DCH2ECON                        | 31:16         | —      | —     | —        | —     | —              | —     | —    | —      |        | -      | -      | CHAIR  |        |        |        |         | (  |

|                              |                                 | 15:0          |        |       |          | CHSIR | Q<7:0>         |       |      |        | CFORCE |        | PATEN  | SIRQEN | AIRQEN | —      | -      | —       | I  |

| 200                          | DCH2INT                         | 31:16         | —      |       | —        | _     | —              | _     | —    | _      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE  | (  |

|                              |                                 | 15:0          | —      | _     | —        | _     | —              | _     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF  | _  |

| 210                          | DCH2SSA                         | 31:16         |        |       |          |       |                |       |      | CHSSA  | <31:0> |        |        |        |        |        |        |         | (  |

| -                            |                                 | 15:0          |        |       |          |       |                |       |      |        |        |        |        |        |        |        |        |         | (  |

| 220                          | DCH2DSA                         | 31:16         |        |       |          |       |                |       |      | CHDSA- | <31:0> |        |        |        |        |        |        |         | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      |        |        |        |        |        |        |        |        |         | (  |

| 230                          | DCH2SSIZ                        | 31:16         | —      | _     | —        | _     | _              | _     | _    | -      | -      | —      | _      | —      | —      | _      | —      | _       | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      | CHSSIZ | <15:0> |        |        |        |        |        | r      |         | (  |

| 240                          | DCH2DSIZ                        | 31:16         | —      | _     | —        | _     | _              | _     | _    |        | -      | _      | _      | _      | _      | _      | —      | _       | (  |

|                              |                                 | 15:0<br>31:16 | _      |       |          |       |                |       |      | CHDSIZ | <15:0> |        |        |        |        | _      |        |         | 0  |

| 250                          | DCH2SPTR                        |               | _      | _     | _        | _     |                | _     |      |        |        | _      | _      | _      | _      | _      | _      | _       | 0  |

|                              |                                 | 15:0<br>31:16 |        |       |          |       | _              |       |      | CHSPTR | <10:0> |        | _      | _      | _      | _      |        |         | 0  |

| 260                          | DCH2DPTR                        |               | —      |       | —        | _     |                |       |      | CHDPTR |        |        |        |        |        | _      | —      | —       | 0  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      |        | <10:0> |        |        |        |        |        |        |         | 0  |

| 270                          | DCH2CSIZ                        | 31:16         | _      | _     | _        | _     | _              | _     | _    |        |        | _      |        | _      | _      |        | _      | —       | C  |

|                              |                                 | 15:0          |        |       |          |       | s '0'. Reset v |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |         | 0  |

PIC32MZ Embedded Connectivity (EC) Family

All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

| REGISTE | R 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | CHDDIF: Channel Destination Done Interrupt Flag bit                                                                                                                                        |

|         | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)</li> <li>0 = No interrupt is pending</li> </ul>                                                  |

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul> <li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li> <li>0 = No interrupt is pending</li> </ul>                                                       |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected<br/>Either the source or the destination address is invalid.</li> <li>0 = No interrupt is pending</li> </ul>                        |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|----------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04        | R/W-0             | R/W-0                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | VPLEN<7:0>                 |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-1                      | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |

| 23:16        |                   | WTCO                       | N<3:0>            |                   |                   | WTID              | <3:0>            | R/W-0            |  |  |

| 15.0         | R-1               | R-0                        | R-0               | R-0               | R-1               | R-1               | R-0              | R-0              |  |  |

| 15:8         |                   | DMACHANS<3:0> RAMBITS<3:0> |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-1                        | R-1               | R-1               | R-0               | R-1               | R-1              | R-1              |  |  |

| 7:0          |                   | RXENDF                     | PTS<3:0>          |                   | TXENDPTS<3:0>     |                   |                  |                  |  |  |

#### **REGISTER 11-16: USBINFO: USB INFORMATION REGISTER**

#### Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-24 VPLEN<7:0>: VBUS pulsing charge length bits

Sets the duration of the VBUS pulsing charge in units of 546.1  $\mu s.$  (The default setting corresponds to 32.77 ms.)

- bit 23-20 WTCON<3:0>: Connect/Disconnect filter control bits Sets the wait to be applied to allow for the connect/disconnect filter in units of 533.3 ns. The default setting corresponds to 2.667 μs.

- bit 19-6 WTID<3:0>: ID delay valid control bits

Sets the delay to be applied from IDPULLUP being asserted to IDDIG being considered valid in units of 4.369ms. The default setting corresponds to 52.43ms.

#### bit 15-12 DMACHANS<3:0>: DMA Channels bits

These read-only bits provide the number of DMA channels in the USB module. For the PIC32MZ EC family, this number is 8.

#### bit 11-8 **RAMBITS<3:0>:** RAM address bus width bits

These read-only bits provide the width of the RAM address bus. For the PIC32MZ EC family, this number is 12.

#### bit 7-4 RXENDPTS<3:0>: Included RX Endpoints bits

This read-only register gives the number of RX endpoints in the design. For the PIC32MZ EC family, this number is 7.

bit 3-0 TXENDPTS<3:0>: Included TX Endpoints bits

These read-only bits provide the number of TX endpoints in the design. For the PIC32MZ EC family, this number is 7.

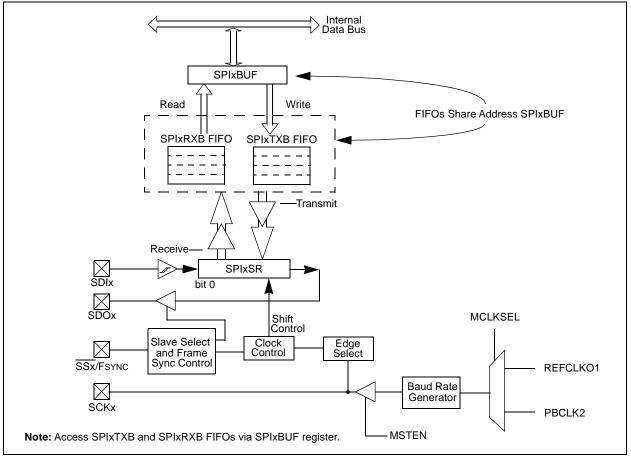

### 19.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well as digital audio devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The following are some of the key features of the SPI module:

- Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-iustified

- Right-justified

- PCM

#### FIGURE 19-1: SPI/I<sup>2</sup>S MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5      | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                      | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                      | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0                    | U-0               | U-0               | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 15:8         | —                 | —                 | _                      | —                 |                   | PKT<br>COMPIF     | BD<br>DONEIF     | CON<br>THRIF     |

|              | R/W-1, HS         | R/W-0, HS         | R/W-1, HS              | R/W-0, HS         | R/W-1, HS         | R/W-1, HS         | R/W-0, HS        | R/W-1, HS        |

| 7:0          | CON<br>EMPTYIF    | CON<br>FULLIF     | RXTHRIF <sup>(1)</sup> | RXFULLIF          | RX<br>EMPTYIF     | TXTHRIF           | TXFULLIF         | TX<br>EMPTYIF    |

#### REGISTER 20-9: SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER

| Legend:           | HS = Hardware Set |                                    |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31-11 | Unimplemented: Read as '0'                                                        |

|-----------|-----------------------------------------------------------------------------------|

| bit 10    | PKTCOMPIF: DMA Buffer Descriptor Processor Packet Completion Interrupt Status bit |

|           | 1 = DMA BD packet is complete                                                     |

|           | 0 = DMA BD packet is in progress                                                  |

| bit 9     | BDDONEIF: DMA Buffer Descriptor Done Interrupt Status bit                         |

|           | 1 = DMA BD process is done                                                        |

|           | 0 = DMA BD process is in progress                                                 |

| bit 8     | CONTHRIF: Control Buffer Threshold Interrupt Status bit                           |

|           | 1 = The control buffer has more than THRES words of space available               |

|           | 0 = The control buffer has less than THRES words of space available               |

| bit 7     | CONEMPTYIF: Control Buffer Empty Interrupt Status bit                             |

|           | 1 = Control buffer is empty                                                       |

|           | 0 = Control buffer is not empty                                                   |

| bit 6     | CONFULLIF: Control Buffer Full Interrupt Status bit                               |

|           | 1 = Control buffer is full                                                        |

|           | 0 = Control buffer is not full                                                    |

| bit 5     | <b>RXTHRIF:</b> Receive Buffer Threshold Interrupt Status bit <sup>(1)</sup>      |

|           | 1 = Receive buffer has more than RXINTTHR words of space available                |

|           | 0 = Receive buffer has less than RXINTTHR words of space available                |

| bit 4     | RXFULLIF: Receive Buffer Full Interrupt Status bit                                |

|           | 1 = Receive buffer is full                                                        |

|           | 0 = Receive buffer is not full                                                    |

| bit 3     | <b>RXEMPTYIF:</b> Receive Buffer Empty Interrupt Status bit                       |

|           | 1 = Receive buffer is empty                                                       |

|           | 0 = Receive buffer is not empty                                                   |

| bit 2     | TXTHRIF: Transmit Buffer Interrupt Status bit                                     |

- bit 2 **TXTHRIF:** Transmit Buffer Interrupt Status bit

- 1 = Transmit buffer has more than TXINTTHR words of space available

- 0 = Transmit buffer has less than TXINTTHR words of space available

- Note 1: In the case of Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

#### REGISTER 20-20: SQI1BDRXDSTAT: SQI BUFFER DESCRIPTOR DMA RECEIVE STATUS REGISTER

|              | 1                 | LOISTEN           |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |  |  |

| 31:24        | —                 | _                 | _                 |                   | RXSTATE<3:0>      |                   |                  |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |

| 23:16        | —                 | —                 | _                 |                   | RXBUFCNT<4:0>     |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | _                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |

| 7:0          |                   |                   |                   | RXCURBUF          | LEN<7:0>          |                   |                  |                  |  |  |

| Leg | genc | 1: |  |  |  |

|-----|------|----|--|--|--|

|     |      |    |  |  |  |

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-25 **RXSTATE<3:0>:** Current DMA Receive State Status bits These bits provide information on the current DMA receive states.

bit 24-21 Unimplemented: Read as '0'

bit 20-16 **RXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits These bits provide information on the internal FIFO space.

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **RXCURBUFLEN<7:0>:** Current DMA Receive Buffer Length Status bits These bits provide the length of the current DMA receive buffer.

| r            |                   |                   |                   |                   | 1                 |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | PCIE              | SCIE              | BOEN              | SDAHT             | SBCDE             | AHEN             | DHEN             |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | —                 | SIDL              | SCKREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

|              | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

## REGISTER 21-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Legend:           | HC = Cleared in Hardware |                          |                    |  |  |  |

|-------------------|--------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

| bit 22 | PCIE: Stop Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 = Enable interrupt on detection of Stop condition                                                                                                                                                                                                                                       |

|        | 0 = Stop detection interrupts are disabled                                                                                                                                                                                                                                                |

| bit 21 | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                             |

|        | 1 = Enable interrupt on detection of Start or Restart conditions                                                                                                                                                                                                                          |

|        | 0 = Start detection interrupts are disabled                                                                                                                                                                                                                                               |

| bit 20 | BOEN: Buffer Overwrite Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                      |

|        | <ul> <li>1 = I2CxRCV is updated and ACK is generated for a received address/data byte, ignoring the state of the I2COV bit (I2CxSTAT&lt;6&gt;)only if the RBF bit (I2CxSTAT&lt;2&gt;) = 0</li> <li>0 = I2CxRCV is only updated when the I2COV bit (I2CxSTAT&lt;6&gt;) is clear</li> </ul> |

| bit 19 | SDAHT: SDA Hold Time Selection bit                                                                                                                                                                                                                                                        |

|        | 1 = Minimum of 300 ns hold time on SDA after the falling edge of SCL                                                                                                                                                                                                                      |

|        | 0 = Minimum of 100 ns hold time on SDA after the falling edge of SCL                                                                                                                                                                                                                      |

| bit 18 | SBCDE: Slave Mode Bus Collision Detect Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                      |

|        | 1 = Enable slave bus collision interrupts                                                                                                                                                                                                                                                 |

|        | 0 = Slave bus collision interrupts are disabled                                                                                                                                                                                                                                           |

| bit 18 | AHEN: Address Hold Enable bit (Slave mode only)                                                                                                                                                                                                                                           |