Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

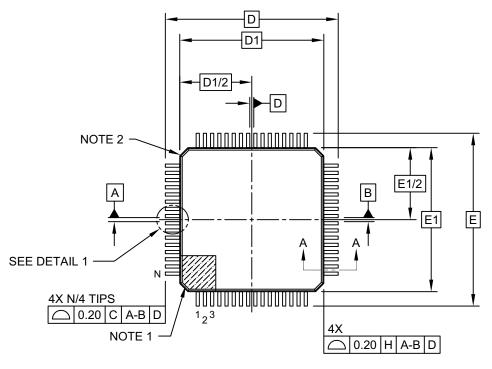

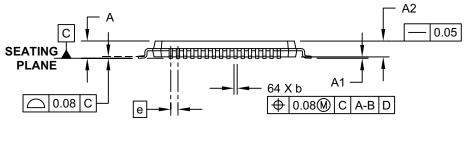

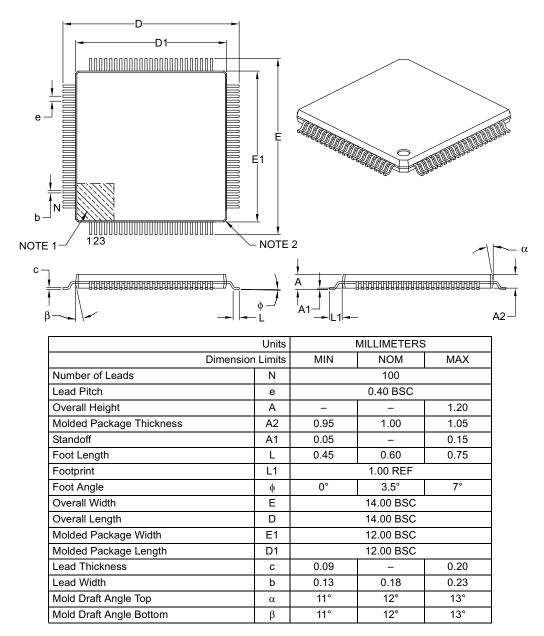

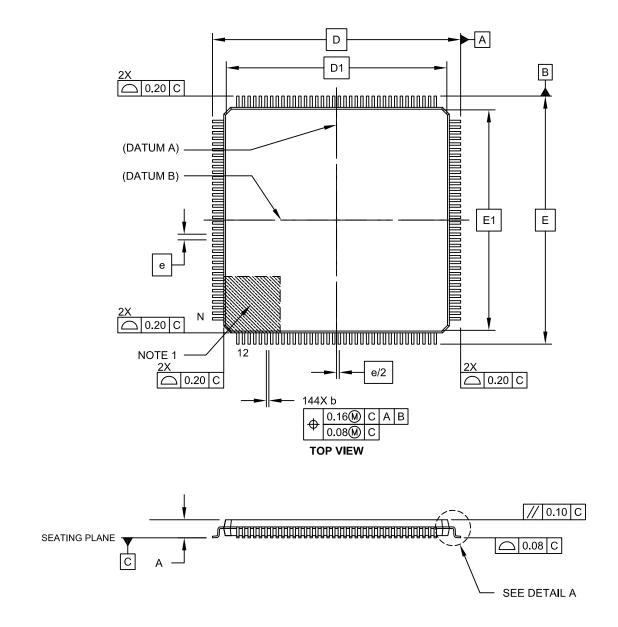

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecg144t-i-pl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Device Pin Tables**

| 64·      | -PIN QFN <sup>(4)</sup> AND TQFP (TOP VIEW)                                                      |           |             |                                             |

|----------|--------------------------------------------------------------------------------------------------|-----------|-------------|---------------------------------------------|

| Pl<br>Pl | C32MZ0512EC(E/F/K)064<br>C32MZ1024EC(G/H/M)064<br>C32MZ1024EC(E/F/K)064<br>C32MZ2048EC(G/H/M)064 | 64<br>QFN | <b>(</b> 4) | 1<br>64 1<br><b>TQFP</b>                    |

| Pin #    | Full Pin Name                                                                                    | Pin       | #           | Full Pin Name                               |

| 1        | AN17/ETXEN/RPE5/PMD5/RE5                                                                         | 33        | 3           | VBUS                                        |

| 2        | AN16/ETXD0/PMD6/RE6                                                                              | 34        |             | VUSB3V3                                     |

| 3        | AN15/ETXD1/PMD7/RE7                                                                              | 35        | ;           | Vss                                         |

| 4        | AN14/C1IND/RPG6/SCK2/PMA5/RG6                                                                    | 36        | ;           | D-                                          |

| 5        | AN13/C1INC/RPG7/SDA4/PMA4/RG7                                                                    | 37        | ,           | D+                                          |

| 6        | AN12/C2IND/RPG8/SCL4/PMA3/RG8                                                                    | 38        | 3           | RPF3/USBID/RF3                              |

| 7        | Vss                                                                                              | 39        | ,           | Vdd                                         |

| 8        | Vdd                                                                                              | 40        | )           | Vss                                         |

| 9        | MCLR                                                                                             | 41        |             | RPF4/SDA5/PMA9/RF4                          |

| 10       | AN11/C2INC/RPG9/PMA2/RG9                                                                         | 42        |             | RPF5/SCL5/PMA8/RF5                          |

| 11       | AN45/C1INA/RPB5/RB5                                                                              | 43        |             | AERXD0/ETXD2/RPD9/SDA1/PMCS2/PMA15/RD9      |

| 12       | AN4/C1INB/RB4                                                                                    | 44        | Ļ I         | ECOL/RPD10/SCL1/SCK4/RD10                   |

| 13       | AN3/C2INA/RPB3/RB3                                                                               | 45        | ;           | AERXCLK/AEREFCLK/ECRS/RPD11/PMCS1/PMA14/RD1 |

| 14       | AN2/C2INB/RPB2/RB2                                                                               | 46        | ;           | AERXD1/ETXD3/RPD0/RTCC/INT0/RD0             |

| 15       | PGEC1/VREF-/CVREF-/AN1/RPB1/RB1                                                                  | 47        | ,           | SOSCI/RPC13/RC13                            |

| 16       | PGED1/VREF+/CVREF+/AN0/RPB0/PMA6/RB0                                                             | 48        | 3           | SOSCO/RPC14/T1CK/RC14                       |

| 17       | PGEC2/AN46/RPB6/RB6                                                                              | 49        | ,           | EMDIO/AEMDIO/RPD1/SCK1/RD1                  |

| 18       | PGED2/AN47/RPB7/RB7                                                                              | 50        | )           | ETXERR/AETXEN/RPD2/SDA3/RD2                 |

| 19       | AVdd                                                                                             | 51        |             | AERXERR/ETXCLK/RPD3/SCL3/RD3                |

| 20       | AVss                                                                                             | 52        | ,           | SQICS0/RPD4/PMWR/RD4                        |

| 21       | AN48/RPB8/PMA10/RB8                                                                              | 53        | 3           | SQICS1/RPD5/PMRD/RD5                        |

| 22       | AN49/RPB9/PMA7/RB9                                                                               | 54        |             | Vdd                                         |

| 23       | TMS/CVREFOUT/AN5/RPB10/PMA13/RB10                                                                | 55        | ;           | Vss                                         |

| 24       | TDO/AN6/PMA12/RB11                                                                               | 56        |             | ERXD3/AETXD1/RPF0/RF0                       |

| 25       | Vss                                                                                              | 57        | ,           | TRCLK/SQICLK/ERXD2/AETXD0/RPF1/RF1          |

| 26       | Vdd                                                                                              | 58        |             | TRD0/SQID0/ERXD1/PMD0/RE0                   |

| 27       | TCK/AN7/PMA11/RB12                                                                               | 59        |             | Vss                                         |

| 28       | TDI/AN8/RB13                                                                                     | 60        |             | VDD                                         |

| 29       | AN9/RPB14/SCK3/PMA1/RB14                                                                         | 61        |             | TRD1/SQID1/ERXD0/PMD1/RE1                   |

| 30       | AN10/EMDC/AEMDC/RPB15/OCFB/PMA0/RB15                                                             | 62        |             | TRD2/SQID2/ERXDV/ECRSDV/AECRSDV/PMD2/RE2    |

|          | OSC1/CLKI/RC12                                                                                   | 63        |             |                                             |

| 31       | USCI/CLNI/RCIZ                                                                                   | 0.        | <b>)</b> 1  | TRD3/SQID3/ERXCLK/EREFCLK/RPE3/PMD3/RE3     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

**3:** Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

|          |                        | Pin Nu          | mber            |                          |             |                |                        |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description            |

| AN0      | 16                     | 25              | A18             | 36                       | Ι           | Analog         | Analog Input Channels  |

| AN1      | 15                     | 24              | A17             | 35                       | I           | Analog         |                        |

| AN2      | 14                     | 23              | A16             | 34                       | I           | Analog         |                        |

| AN3      | 13                     | 22              | A14             | 31                       | I           | Analog         |                        |

| AN4      | 12                     | 21              | A13             | 26                       | Ι           | Analog         |                        |

| AN5      | 23                     | 34              | B19             | 49                       | -           | Analog         |                        |

| AN6      | 24                     | 35              | A24             | 50                       | Ι           | Analog         |                        |

| AN7      | 27                     | 41              | A27             | 59                       | Ι           | Analog         |                        |

| AN8      | 28                     | 42              | B23             | 60                       | -           | Analog         |                        |

| AN9      | 29                     | 43              | A28             | 61                       | I           | Analog         | 1                      |

| AN10     | 30                     | 44              | B24             | 62                       | Ι           | Analog         |                        |

| AN11     | 10                     | 16              | B9              | 21                       | -           | Analog         |                        |

| AN12     | 6                      | 12              | B7              | 16                       | Ι           | Analog         |                        |

| AN13     | 5                      | 11              | A8              | 15                       | I           | Analog         |                        |

| AN14     | 4                      | 10              | B6              | 14                       | I           | Analog         |                        |

| AN15     | 3                      | 5               | A4              | 5                        | Ι           | Analog         |                        |

| AN16     | 2                      | 4               | B2              | 4                        | I           | Analog         |                        |

| AN17     | 1                      | 3               | A3              | 3                        | I           | Analog         |                        |

| AN18     | 64                     | 100             | A67             | 144                      | Ι           | Analog         |                        |

| AN19     | _                      | 9               | A7              | 13                       | Ι           | Analog         |                        |

| AN20     | _                      | 8               | B5              | 12                       | -           | Analog         |                        |

| AN21     | _                      | 7               | A6              | 11                       | Ι           | Analog         |                        |

| AN22     | _                      | 6               | B3              | 6                        | Ι           | Analog         |                        |

| AN23     | _                      | 1               | A2              | 1                        | -           | Analog         |                        |

| AN24     | _                      | 17              | A11             | 22                       | Ι           | Analog         |                        |

| AN25     |                        | 18              | B10             | 23                       | -           | Analog         |                        |

| AN26     |                        | 19              | A12             | 24                       | -           | Analog         |                        |

| AN27     | _                      | 28              | B15             | 39                       | Ι           | Analog         |                        |

| AN28     | —                      | 29              | A20             | 40                       | I           | Analog         | 1                      |

| AN29     | —                      | 38              | B21             | 56                       | I           | Analog         | 1                      |

| AN30     |                        | 39              | A26             | 57                       | I           | Analog         | ]                      |

| AN31     |                        | 40              | B22             | 58                       | I           | Analog         | ]                      |

| AN32     | —                      | 47              | B27             | 69                       | I           | Analog         | 1                      |

| AN33     | —                      | 48              | A32             | 70                       | I           | Analog         | 1                      |

| AN34     | —                      | 2               | B1              | 2                        | I           | Analog         | 1                      |

| AN35     | _                      | —               | A5              | 7                        | I           | Analog         | 1                      |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | or output                |             | Analog =       | Analog input P = Power |

#### TABLE 1-1: ADC1 PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

|                             | LE 7-3:                         |               |       |       |       |       | (CONTI | NUED) |      |                 |          |      |      |      |      |      |                                       |       |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|--------|-------|------|-----------------|----------|------|------|------|------|------|---------------------------------------|-------|------------|

| ess                         |                                 | æ             |       |       |       |       |        |       |      | В               | its      |      |      |      |      |      |                                       |       | s          |

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8            | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1                                  | 16/0  | All Resets |

| 0568                        | OFF010                          | 31:16         |       | _     | —     | —     | _      | —     | _    | —               |          | —    | _    | —    | _    | _    | VOFF<1                                | 7:16> | 0000       |

| 0000                        | 011010                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       | _     | 0000       |

| 056C                        | OFF011                          | 31:16         | —     | —     | —     | —     | —      | —     | —    | —               | —        | —    | —    | —    | —    | —    | VOFF<1                                | 7:16> | 0000       |

|                             | 011011                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       |       | 0000       |

| 0570                        | OFF012                          | 31:16         | —     | _     | —     | —     | —      | —     | —    | —               | _        | —    | —    | —    | —    | —    | VOFF<1                                | 7:16> | 0000       |

|                             |                                 | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        | i    |      | i    |      |      |                                       | _     | 0000       |

| 0574                        | OFF013                          | 31:16         |       | —     | —     | —     | —      |       | —    | —               | —        | —    | —    | —    | —    | —    | VOFF<1                                | 7:16> | 0000       |

|                             |                                 | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       |          |      |      |      |      |      |                                       |       | 0000       |

| 0578                        | OFF014                          | 31:16         | —     | —     | —     | —     | —      | _     | —    | —               | _        | —    | —    | —    | —    | _    | VOFF<1                                |       | 0000       |

|                             |                                 | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       |          |      |      |      |      |      |                                       |       | 0000       |

| 057C                        | OFF015                          | 31:16<br>15:0 | —     | _     | —     | _     | —      | —     | —    | —<br>VOFF<15:1: | _        | —    | _    | _    | _    | _    | VOFF<1                                |       | 0000       |

|                             |                                 | 31:16         | _     |       |       |       |        |       | _    | VOFF<15:1       | <u> </u> | _    |      |      |      | _    | VOFF<1                                | 7:16: | 0000       |

| 0580                        | OFF016                          | 15:0          | —     | —     | _     | —     | _      | _     | _    |                 |          | _    | —    | _    | —    | _    | VUFF<1                                |       | 0000       |

|                             |                                 | 31:16         | _     |       | _     |       | _      | _     | _    |                 | _        | _    |      |      |      | _    | VOFF<1                                |       | 0000       |

| 0584                        | OFF017                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       |          |      |      |      |      |      | 00111                                 |       | 0000       |

|                             |                                 | 31:16         | _     |       | _     |       | _      | _     | _    | _               |          |      | _    |      |      |      | VOFF<1                                |       | 0000       |

| 0588                        | OFF018                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       | _     | 0000       |

|                             |                                 | 31:16         | _     | _     | _     | _     | _      | _     | _    | _               | _        | _    | _    | _    | _    | _    | VOFF<1                                | 7:16> | 0000       |

| 058C                        | OFF019                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      | · · · · · · · · · · · · · · · · · · · | _     | 0000       |

|                             | 0.55000                         | 31:16         | _     | _     | _     | _     | —      | _     | _    | _               | _        | _    | _    | _    | _    | _    | VOFF<1                                | 7:16> | 0000       |

| 0590                        | OFF020                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       | _     | 0000       |

| 0594                        | OFF021                          | 31:16         |       | _     | —     | —     | —      | —     | —    | _               | _        | —    | _    | —    | —    | —    | VOFF<1                                | 7:16> | 0000       |

| 0594                        | UFF021                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       | _     | 0000       |

| 0598                        | OFF022                          | 31:16         | _     | _     | —     | —     |        | —     | -    | —               | _        | —    | -    | —    | _    | _    | VOFF<1                                | 7:16> | 0000       |

| 0590                        | UFF022                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        | -    |      | -    |      |      |                                       | _     | 0000       |

| 059C                        | OFF023                          | 31:16         | _     | _     | -     | _     | _      | —     | _    | _               | _        | _    | _    | _    | _    | _    | VOFF<1                                | 7:16> | 0000       |

| 0000                        | 011023                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       | _     | 0000       |

| 05A0                        | OFF024                          | 31:16         | _     | _     | —     | —     | _      | _     | —    | _               | _        | —    | —    | —    | —    | _    | VOFF<1                                | 7:16> | 0000       |

| 50, 10                      | 511024                          | 15:0          |       |       |       |       |        |       |      | VOFF<15:1       | >        |      |      |      |      |      |                                       | _     | 0000       |

#### TARIE 7-3. INTEDDUDT DECISTED MAD (CONTINUED)

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Note 1: **Registers**" for more information.

2:

This bit or register is not available on 64-pin devices. This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

This bit or register is not available on devices without a Crypto module. 7:

8: This bit or register is not available on 124-pin devices.

# PIC32MZ Embedded Connectivity (EC) Family

| REGISTE      | CEGISTER 11-20. USBDMAINT: USB DMA INTERROFT REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | U-0                                                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                                                     | —                 | —                 | —                 | —                 |                   | —                | —                |  |  |  |

| 23:16        | U-0                                                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                                                     | _                 | _                 | _                 | _                 | _                 |                  | —                |  |  |  |

| 15:8         | U-0                                                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | _                                                     | _                 | _                 | _                 | _                 | _                 |                  | —                |  |  |  |

| 7:0          | R/W-0, HS                                             | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |  |  |  |

| 7:0          | DMA8IF                                                | DMA7IF            | DMA6IF            | DMA5IF            | DMA4IF            | DMA3IF            | DMA2IF           | DMA1IF           |  |  |  |

#### REGISTER 11-20: USBDMAINT: USB DMA INTERRUPT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 DMAxIF: DMA Channel 'x' Interrupt bit

1 = The DMA channel has an interrupt event

0 = No interrupt event

All bits are cleared on a read of the register.

#### REGISTER 11-28: USBLPMR1: USB LINK POWER MANAGEMENT CONTROL REGISTER 1 (CONTINUED)

#### bit 16 LPMXMT: LPM Transition to the L1 State bit

#### When in Device mode:

- 1 = USB module will transition to the L1 state upon the receipt of the next LPM transaction. LPMEN must be set to `0b11. Both LPMXMT and LPMEN must be set in the same cycle.

- 0 = Maintain current state

When LPMXMT and LPMEN are set, the USB module can respond in the following ways:

- If no data is pending (all TX FIFOs are empty), the USB module will respond with an ACK. The bit will self clear and a software interrupt will be generated.

- If data is pending (data resides in at least one TX FIFO), the USB module will respond with a NYET. In this case, the bit will not self clear however a software interrupt will be generated.

#### When in Host mode:

- 1 = USB module will transmit an LPM transaction. This bit is self clearing, and will be immediately cleared upon receipt of any Token or three time-outs have occurred.

- 0 = Maintain current state

#### bit 15-12 ENDPOINT<3:0>: LPM Token Packet Endpoint bits

This is the endpoint in the token packet of the LPM transaction.

#### bit 11-9 Unimplemented: Read as '0'

bit 8 **RMTWAK:** Remote Wake-up Enable bit

This bit is applied on a temporary basis only and is only applied to the current suspend state.

- 1 = Remote wake-up is enabled

- 0 = Remote wake-up is disabled

#### bit 7-4 HIRD<3:0>: Host Initiated Resume Duration bits

The minimum time the host will drive resume on the bus. The value in this register corresponds to an actual resume time of:

Resume Time = 50  $\mu$ s + HIRD \* 75  $\mu$ s. The resulting range is 50  $\mu$ s to 1200  $\mu$ s.

#### bit 3-0 LNKSTATE<3:0>: Link State bits

This value is provided by the host to the peripheral to indicate what state the peripheral must transition to after the receipt and acceptance of a LPM transaction. The only valid value for this register is '1' for Sleep State (L1). All other values are reserved.

| Bit<br>Range | Bit<br>31/23/15/7 |             |               | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------|---------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0         | U-0           | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —           | _             | _                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0         | U-0           | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —           | —             | _                 | _                 | —                 | —                | -                |

| 45.0         | R-0, HS, HC       | R-0, HS, HC | R/C-0, HS, HC | U-0               | U-0               | R/C-0, HS         | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ACKSTAT           | TRSTAT      | ACKTIM        | —                 | —                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS   | R-0, HS, HC   | R/C-0, HS, HC     | R/C-0, HS, HC     | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 7:0          | IWCOL             | I2COV       | D_A           | Р                 | S                 | R_W               | RBF              | TBF              |

## REGISTER 21-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared              |                   |  |  |  |

|-------------------|-------------------|------------------------------------|-------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                   |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | C = Clearable bit |  |  |  |

#### 64 04 46 LIN d. D . . .

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                      |

|           | 1 = NACK received from slave                                                                                                                                                                     |

|           | 0 = ACK received from slave                                                                                                                                                                      |

|           | Hardware set or clear at end of slave Acknowledge.                                                                                                                                               |

| bit 14    | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                 |

|           | 1 = Master transmit is in progress (8 bits + ACK)                                                                                                                                                |

|           | 0 = Master transmit is not in progress                                                                                                                                                           |

|           | Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.                                                                                                    |

| bit 13    | ACKTIM: Acknowledge Time Status bit (Valid in I <sup>2</sup> C Slave mode only)                                                                                                                  |

|           | <ul> <li>1 = I<sup>2</sup>C bus is in an Acknowledge sequence, set on 8th falling edge of SCL clock</li> <li>0 = Not an Acknowledge sequence, cleared on 9th rising edge of SCL clock</li> </ul> |

| bit 12-11 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                                             |

|           | 1 = A bus collision has been detected during a master operation                                                                                                                                  |

|           | 0 = No collision                                                                                                                                                                                 |

|           | Hardware set at detection of bus collision.                                                                                                                                                      |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                                                  |

|           | 1 = General call address was received                                                                                                                                                            |

|           | 0 = General call address was not received                                                                                                                                                        |

|           | Hardware set when address matches general call address. Hardware clear at Stop detection.                                                                                                        |

| bit 8     | ADD10: 10-bit Address Status bit                                                                                                                                                                 |

|           | 1 = 10-bit address was matched                                                                                                                                                                   |

|           | 0 = 10-bit address was not matched                                                                                                                                                               |

|           | Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                                                   |

| bit 7     | IWCOL: Write Collision Detect bit                                                                                                                                                                |

|           | 1 = An attempt to write the I2CxTRN register failed because the $I^2C$ module is busy                                                                                                            |

|           | 0 = No collision                                                                                                                                                                                 |

|           | Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).                                                                                                                 |

| bit 6     | I2COV: Receive Overflow Flag bit                                                                                                                                                                 |

|           | 1 = A byte was received while the I2CxRCV register is still holding the previous byte                                                                                                            |

|           | <ul> <li>0 = No overflow</li> <li>Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).</li> </ul>                                                                       |

|           |                                                                                                                                                                                                  |

|           |                                                                                                                                                                                                  |

|           |                                                                                                                                                                                                  |

#### **EBI Control Registers** 24.1

#### TABLE 24-2: EBI REGISTER MAP

| ess                         |                        |               |       |          |       |        |          |          |             |         | Bits       |          |          |       |      |          |           |      | s          |

|-----------------------------|------------------------|---------------|-------|----------|-------|--------|----------|----------|-------------|---------|------------|----------|----------|-------|------|----------|-----------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name       | Bit Range     | 31/15 | 30/14    | 29/13 | 28/12  | 27/11    | 26/10    | 25/9        | 24/8    | 23/7       | 22/6     | 21/5     | 20/4  | 19/3 | 18/2     | 17/1      | 16/0 | All Resets |

| 1014                        | EBICS0 <sup>(1)</sup>  | 31:16         |       | -        |       |        | -        |          | -           | CS      | SADDR<15:0 | >        |          |       |      | -        |           | -    | 2000       |

| 1014                        |                        | 15:0          | _     | —        | —     | —      | —        | —        |             | —       | —          | —        | —        | —     | —    |          | —         | —    | 0000       |

| 1018                        | EBICS1(2)              | 31:16         |       |          |       |        |          |          |             | CS      | SADDR<15:0 | >        |          |       |      |          |           |      | 1000       |

|                             |                        | 15:0          | —     | —        | —     | —      |          | —        | —           | —       | _          | —        | —        | —     | —    | —        | —         | —    | 0000       |

| 101C                        | EBICS2(2)              | 31:16         |       |          |       |        |          |          |             | CS      | SADDR<15:0 | >        |          | r     |      |          |           |      | 2040       |

|                             |                        | 15:0          | —     | _        | —     | _      | _        | —        |             | —       |            | —        | _        | —     | _    | —        | —         | _    | 0000       |

| 1020                        | EBICS3(2)              | 31:16         |       |          |       |        |          |          |             |         | SADDR<15:0 |          |          |       |      |          |           |      | 1040       |

|                             |                        | 15:0          | _     |          | _     |        | _        |          | —           | _       | —          |          |          |       | _    | —        | _         | _    | 0000       |

| 1054                        | EBIMSK0 <sup>(1)</sup> | 31:16         |       |          |       |        |          | —<br>DFC | <br>SEL<2:0 | _       |            | EMTYPE<2 |          |       |      | EMSIZE<4 | -         | _    | 0000       |

|                             |                        | 15:0<br>31:16 |       |          | _     |        |          | REG      | SEL<2:0     | >       | IVI        |          | .0>      |       | IVI  |          | .0>       |      | 0020       |

| 1058                        | EBIMSK1(2)             | 15:0          |       |          |       |        |          | - REG    | SEL<2:0     |         | M          | EMTYPE<2 |          |       | M    | EMSIZE<4 |           |      | 0020       |

|                             |                        | 31:16         |       |          |       |        |          | _        |             | _       |            |          |          |       |      |          |           | _    | 00020      |

| 105C                        | EBIMSK2 <sup>(2)</sup> | 15:0          | _     | _        | _     | _      |          | REG      | SEL<2:0     |         | М          | EMTYPE<2 |          |       | M    | EMSIZE<4 | .0>       |      | 0120       |

|                             | (2)                    | 31:16         | _     | _        | _     |        | _        | _        | _           | _       | _          |          | _        | _     | _    | _        | _         | _    | 0000       |

| 1060                        | EBIMSK3 <sup>(2)</sup> | 15:0          | _     | _        | _     | _      | _        | REG      | SEL<2:0     | >       | М          | EMTYPE<2 | :0>      |       | M    | EMSIZE<4 | :0>       |      | 0120       |

|                             |                        | 31:16         | _     | _        | _     | _      | _        | RDYMODE  | PAGESI      | ZE<1:0> | PAGEMODE   |          | TPRC<    | <3:0> |      |          | TBTA<2:0> |      | 041C       |

| 1094                        | EBISMT0                | 15:0          |       |          | TW    | P<5:0> |          |          | TWR         | <1:0>   | TAS<       | 1:0>     |          |       | TRC< | 5:0>     |           |      | 2D4B       |

| 4000                        | EBISMT1                | 31:16         | _     | _        | _     | _      | _        | RDYMODE  | PAGESI      | ZE<1:0> | PAGEMODE   |          | TPRC<    | <3:0> |      |          | TBTA<2:0> |      | 041C       |

| 1098                        | ERIZMIT                | 15:0          |       |          | TW    | P<5:0> |          |          | TWR         | <1:0>   | TAS<       | 1:0>     |          |       | TRC< | 5:0>     |           |      | 2D4B       |

| 109C                        | EBISMT2                | 31:16         | _     | —        | _     | _      | _        | RDYMODE  | PAGESI      | ZE<1:0> | PAGEMODE   |          | TPRC<    | <3:0> |      |          | TBTA<2:0> |      | 041C       |

| 1090                        | EDISIVITZ              | 15:0          |       |          | TW    | P<5:0> |          |          | TWR         | <1:0>   | TAS<       | 1:0>     |          |       | TRC< | 5:0>     |           |      | 2d\$b      |

| 1040                        | EBIFTRPD               | 31:16         | _     | _        | —     | _      | _        | _        | _           | —       | _          | —        | -        | —     | _    | _        | —         | -    | 0000       |

| 1070                        |                        | 15:0          | —     | -        | —     |        |          |          |             |         |            | TR       | PD<11:0> |       |      |          |           |      | 00C8       |

| 10A4                        | EBISMCON               | 31:16         | —     | —        | —     | —      | —        | —        | —           | —       | —          | —        | —        | —     | —    | —        | —         | —    | 0000       |

| 10/14                       |                        | 15:0          | SMD   | WIDTH2<2 | 2:0>  | SME    | DWIDTH1< | :2:0>    | SM          | IDWIDTH | 10<2:0>    | —        | —        | —     | —    | —        | —         | SMRP | 0201       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is not available on 64-pin devices.

This register is available on 144-pin devices only. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | —                 | _                 | —                 | _                 | -                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | -                 | —                | —                |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | _                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | HDRLEN<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 26-9: CEHDLEN: CRYPTO ENGINE HEADER LENGTH REGISTER

#### Legend:

| Logona            |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **HDRLEN<7:0>:** DMA Header Length bits For every packet, skip this length of locations and start filling the data.

#### REGISTER 26-10: CETRLLEN: CRYPTO ENGINE TRAILER LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 |                   | —                 | —                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | —                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | —                 | —                 | _                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | TRLRLE            | N<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 **Unimplemented:** Read as '0'

bit 7-0 TRLRLEN<7:0>: DMA Trailer Length bits

For every packet, skip this length of locations at the end of the current packet and start putting the next packet.

#### 27.1 RNG Control Registers

#### TABLE 27-2: RANDOM NUMBER GENERATOR (RNG) REGISTER MAP

| ess                         |                  | 0         |       |            |       |        |         |       |        | В      | its    |      |      |        |                |      |      |      | 6          |

|-----------------------------|------------------|-----------|-------|------------|-------|--------|---------|-------|--------|--------|--------|------|------|--------|----------------|------|------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15 | 30/14      | 29/13 | 28/12  | 27/11   | 26/10 | 25/9   | 24/8   | 23/7   | 22/6 | 21/5 | 20/4   | 19/3           | 18/2 | 17/1 | 16/0 | All Resets |

| 6000                        | RNGVER           | 31:16     |       |            |       |        |         |       |        | ID<1   | 5:0>   |      |      |        |                |      |      |      | xxxx       |

| 0000                        | KNOVER           | 15:0      |       |            |       | VERSIC | )N<7:0> |       |        |        |        |      |      | REVISI | ON<7:0>        |      |      |      | xxxx       |

| 6004                        | RNGCON           | 31:16     | _     | _          | _     | _      | _       | —     | _      | -      | -      | —    | —    | —      | _              | —    | —    | _    | 0000       |

| 0004                        | RINGCON          | 15:0      | Ι     | -          | -     | LOAD   |         | CONT  | PRNGEN | TRNGEN |        |      |      | PLEN   | <b> </b> <7:0> |      |      |      | 0064       |

| 6008                        | RNGPOLY1         | 31:16     |       |            |       |        |         |       |        | POLY   | -21.0  |      |      |        |                |      |      |      | FFFF       |

| 0000                        | RINGFOLT         | 15:0      |       |            |       |        |         |       |        | FULI   | <31.0> |      |      |        |                |      |      |      | 0000       |

| 600C                        | RNGPOLY2         | 31:16     |       |            |       |        |         |       |        |        | <31:0> |      |      |        |                |      |      |      | FFFF       |

| 000C                        | RINGFOLT2        | 15:0      |       |            |       |        |         |       |        | FULI   | <31.0> |      |      |        |                |      |      |      | 0000       |

| 6010                        | RNGNUMGEN1       | 31:16     |       |            |       |        |         |       |        | PNG    | :31:0> |      |      |        |                |      |      |      | FFFF       |

| 0010                        | RINGINOWIGEINT   | 15:0      |       |            |       |        |         |       |        | KNG    | .01.0> |      |      |        |                |      |      |      | FFFF       |

| 6014                        |                  | 31:16     |       |            |       |        |         |       |        | BNC    | :31:0> |      |      |        |                |      |      |      | FFFF       |

| 6014                        | RNGNUMGEN2       | 15:0      |       |            |       |        |         |       |        | RNG<   | 31:0>  |      |      |        |                |      |      |      | FFFF       |

| 0040                        |                  | 31:16     |       |            |       |        |         |       |        | 0550   | 04.0   |      |      |        |                |      |      |      | 0000       |

| 6018                        | RNGSEED1         | 15:0      |       | SEED<31:0> |       |        |         |       |        |        |        |      |      |        |                |      |      |      |            |

| 004.0                       | DNOOFEDO         | 31:16     |       | 0000       |       |        |         |       |        |        |        |      |      |        |                |      |      |      |            |

| 601C                        | RNGSEED2         | 15:0      |       | SEED<31:0> |       |        |         |       |        |        |        |      |      |        |                |      |      |      |            |

| 0000                        | DNOONT           | 31:16     | _     | —          | —     | —      | _       | —     | —      | —      | —      | —    | —    | _      | _              | —    | —    | —    | 0000       |

| 6020                        | RNGCNT           | 15:0      | -     | _          | _     | _      | _       | —     | _      | -      | -      |      | •    |        | RCNT<6:0>      | >    | •    |      | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24     |                   |                   |                   | ADCMPH            | H<15:8>           |                   |                  |                  |  |  |

| 00.46     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     |                   |                   |                   | ADCMP             | HI<7:0>           |                   |                  |                  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      |                   |                   |                   | ADCMPL            | .0<15:8>          |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | ADCMPLO<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 28-13: AD1CMPn: ADC1 DIGITAL COMPARATOR REGISTER 'n' ('n' = 1, 2, 3, 4, 5 OR 6)

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 **ADCMPHI<15:0>:** Digital Analog Comparator High Limit Value bits These bits store the high limit value, which is used for comparisons with the analog-to-digital conversion data. The user is responsible for formatting the data as signed or unsigned to match the data format as specified by the SHxMOD<1:0> bits for the associated S&H circuit and the FRACT bit.

#### bit 15-0 **ADCMPLO<15:0>:** Digital Analog Comparator Low Limit Value bits These bits store the low limit value, which is used for comparisons with the analog-to-digital conversion data. The user is responsible for formatting the data as signed or unsigned to match the data format as specified by the SHxMOD<1:0> bits for the associated S&H circuit and the FRACT bit.

**Note:** Changing the bits in this register while the Digital Comparator is enabled (ENDCMP = 1) can result in unpredictable behavior.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |

|--------------|-----------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|------------------|

| 31:24        | U-0                         | U-0                | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              |

| 31.24        | _                           |                    | _                 |                   |                   |                   | -                        | —                |

| 23:16        | U-0                         | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0            |

| 23.10        | _                           | WAKFIL             | _                 | -                 |                   | SEG               | 62PH<2:0> <sup>(1</sup>  | ,4)              |

| 45.0         | R/W-0                       | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |

| 15:8         | SEG2PHTS <sup>(1)</sup>     | SAM <sup>(2)</sup> | S                 | EG1PH<2:0>        | (4)               | PR                | SEG<2:0> <sup>(4</sup> ) | )                |

| 7.0          | R/W-0                       | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |

| 7:0          | 7:0 SJW<1:0> <sup>(3)</sup> |                    | BRP<5:0>          |                   |                   |                   |                          |                  |

#### **REGISTER 29-2: CICFG: CAN BAUD RATE CONFIGURATION REGISTER**

| Legend:               | HC = Hardware Clear        | S = Settable bit      |                  |

|-----------------------|----------------------------|-----------------------|------------------|

| R = Readable bit      | W = Writable bit           | P = Programmable bit  | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: ('0 | 0', '1', x = Unknown) |                  |

bit 31-23 Unimplemented: Read as '0'

bit 22 WAKFIL: CAN Bus Line Filter Enable bit

1 = Use CAN bus line filter for wake-up

- 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|

|           | 111 = Length is 8 x TQ                                                                                                             |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | 000 = Length is 1 x TQ                                                                                                             |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                                                                           |

|           | <ul><li>1 = Freely programmable</li><li>0 = Maximum of SEG1PH or Information Processing Time, whichever is greater</li></ul>       |

| bit 14    | SAM: Sample of the CAN Bus Line bit <sup>(2)</sup>                                                                                 |

|           | <ul><li>1 = Bus line is sampled three times at the sample point</li><li>0 = Bus line is sampled once at the sample point</li></ul> |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                                                                            |

|           | 111 = Length is 8 x TQ                                                                                                             |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | 000 - 1 on the is 1 x To                                                                                                           |

$000 = \text{Length is } 1 \times TQ$

- Note 1: SEG2PH  $\leq$  SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

- 2: 3 Time bit sampling is not allowed for BRP < 2.

- **3:** SJW  $\leq$  SEG2PH.

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> Note: (CiCON < 23:21 >) = 100).

| REGISTE   | R 29-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3 (CONTINUED)                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

| bit 15    | FLTEN13: Filter 13 Enable bit                                                                                            |

|           | 1 = Filter is enabled                                                                                                    |

|           | 0 = Filter is disabled                                                                                                   |

| bit 14-13 | MSEL13<1:0>: Filter 13 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 12-8  | FSEL13<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

| bit 7     | FLTEN12: Filter 12 Enable bit                                                                                            |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 6-5   | MSEL12<1:0>: Filter 12 Mask Select bits                                                                                  |

| DIL 0-5   | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected                                                                                          |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 4-0   | FSEL12<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           |                                                                                                                          |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

|           |                                                                                                                          |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                   |

## REGISTER 30-32: EMAC1MCMD: ETHERNET CONTROLLER MAC MII MANAGEMENT COMMAND REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   | —                 | —                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   | —                 | —                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   |                   | —                 | —                 | -                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 | _                 |                   | _                 | SCAN             | READ             |

#### Legend:

| - 3               |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-2 Unimplemented: Read as '0'

- bit 1 SCAN: MII Management Scan Mode bit

- 1 = The MII Management module will perform read cycles continuously (for example, useful for monitoring the Link Fail)

- 0 = Normal Operation

#### bit 0 READ: MII Management Read Command bit

- 1 = The MII Management module will perform a single read cycle. The read data is returned in the EMAC1MRDD register

- 0 = The MII Management module will perform a write cycle. The write data is taken from the EMAC1MWTD register

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

#### 33.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of the PIC32MZ Embedded Connectivity       |

|       | (EC) Family of devices. It is not intended |

|       |                                            |

|       | to be a comprehensive reference source.    |

|       | To complement the information in this      |

|       | data sheet, refer to Section 10. "Power-   |

|       | Saving Features" (DS60001130), which       |

|       | is available from the Documentation >      |

|       | Reference Manual section of the            |

|       | Microchip PIC32 web site                   |

|       | (www.microchip.com/pic32).                 |

This section describes power-saving features for the PIC32MZ EC devices. These devices offer various methods and modes that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

#### 33.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the speed of PBCLK7, or selecting a lower power clock source (i.e., LPRC or Sosc).

In addition, the Peripheral Bus Scaling mode is available for each peripheral bus where peripherals are clocked at reduced speed by selecting a higher divider for the associated PBCLKx, or by disabling the clock completely.

## 33.2 Power-Saving with CPU Halted

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 33.2.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted and the associated clocks are disabled. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the peripheral bus clocks will start running and the device will enter into Idle mode.

#### 33.2.2 IDLE MODE