Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ech100-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

Crystals with a speed of 4 MHz to 12 MHz that meet the following requirements will meet the PIC32MZ EC oscillation requirements when configured, as depicted in Figure 8-1.

- 1. Manufacturer Drive Level (min)  $\leq$  10  $\mu$ W (hard requirements, 1  $\mu$ W preferred).

- 2. Manufacturer ESR  $\leq 50\Omega$  (hard requirement, lower is better).

```

2.7.1.1 Calculating XTAL Capacitive Loading:

```

- 1. PIC32 CIN = COUT =  $\sim$ 4 pF (PIC32 OSCI and OSCO package pin capacitance).

- 2. C1MFG = C2MFG = Manufacturer Recommended Load Capacitance.

- 3. CLOAD = {([CIN + C1MFG] [C2MFG + COUT]) / [CIN + C1MFG + C2MFG + COUT]} + estimated PCB stray capacitance (2.5 pF).

(Simplified) CLOAD = (((CIN + C1MFG)/2) + 2.5 pF).

Actual C1, C2 Load value to use:

- C2 = CLOAD

- C1 = (CLOAD 2 pF)

Note: These recommendations are atypical, and are only applicable to the PIC32MZ EC family.

## 2.7.1.2 Validated Crystals

Temperature Range: (-45°C to +110°C)

VDD = 2.4V to 3.6V, RP = 1 M\Omega, RK = 10  $k\Omega$

• ABLS-12.000 MHz-L4Q-T (12 MHz surface mount)

**Note:** These recommendations are atypical, and only applicable to the PIC32MZ EC family.

#### 2.7.1.3 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.9 Designing for High-Speed Peripherals

The PIC32MZ EC family devices have peripherals that operate at frequencies much higher than typical for an embedded environment. Table 2-1 lists the peripherals that produce high-speed signals on their external pins:

#### TABLE 2-1: PERIPHERALS THAT PRODUCE HS SIGNALS ON EXTERNAL PINS

| Peripheral | High-Speed Signal Pins | Maximum<br>Speed on<br>Signal Pin |

|------------|------------------------|-----------------------------------|

| EBI        | EBIAx, EBIDx           | 50 MHz                            |

| SQI1       | SQICLK, SQICSX, SQIDx  | 50 MHz                            |

| HS USB     | D+, D-                 | 480 MHz                           |

Due to these high-speed signals, it is important to take into consideration several factors when designing a product that uses these peripherals, as well as the PCB on which these components will be placed. Adhering to these recommendations will help achieve the following goals:

- Minimize the effects of electromagnetic interference to the proper operation of the product

- Ensure signals arrive at their intended destination at the same time

- Minimize crosstalk

- Maintain signal integrity

- Reduce system noise

- Minimize ground bounce and power sag

|              | ('2               | x' = 1 AND 2      | 2)                |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04-04        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 31:24        | 24 CSEQ<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00:40        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 23:16        | CSEQ<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 15:8         | TSEQ<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 7:0          | TSEQ<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 4-1: BFxSEQ0/ABFxSEQ0: BOOT FLASH 'x' SEQUENCE WORD 0 REGISTER

| Legend:           |                  | P = Programmable bit               | P = Programmable bit |  |  |  |  |

|-------------------|------------------|------------------------------------|----------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown   |  |  |  |  |

bit 31-16 **CSEQ<15:0>:** Boot Flash Complement Sequence Number bits

bit 15-0 TSEQ<15:0>: Boot Flash True Sequence Number bits

Note: The BFxSEQ1 through BFxSEQ3 and ABFxSEQ1 through ABFxSEQ3 registers are used for Quad Word programming operation when programming the BFxSEQ0/ABFxSEQ0 registers, and do not contain any valid information.

## TABLE 4-9: SYSTEM BUS TARGET 1 REGISTER MAP

| ess                         |                  |           |               |       |       |          |          |       |             |      | Bits     |       |          |      |        |        |          |        |               |

|-----------------------------|------------------|-----------|---------------|-------|-------|----------|----------|-------|-------------|------|----------|-------|----------|------|--------|--------|----------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15         | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9        | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1     | 16/0   | All<br>Resets |

| 8420                        | SBT1ELOG1        | 31:16     | MULTI         |       | —     | —        |          | CODE  | <3:0>       |      |          | —     | —        |      |        | —      | —        | —      | 0000          |

| 0420                        | SBITELOGI        | 15:0      |               |       |       | INI      | TID<7:0> |       |             |      |          | REGIC | N<3:0>   |      | _      | 0      | CMD<2:0> |        | 0000          |

| 8424                        | SBT1ELOG2        | 31:16     |               | _     |       | -        | _        | _     | _           | -    |          |       | _        | _    | —      | -      | —        | -      | 0000          |

| 0424                        | OBTILLOOZ        | 15:0      | 5:0 GROUP<1:0 |       |       |          |          |       | P<1:0>      | 0000 |          |       |          |      |        |        |          |        |               |

| 8428                        | SBT1ECON         | 31:16     | —             | —     | _     | —        | —        | —     | —           | ERRP | —        |       | —        | —    | -      | —      | —        | —      | 0000          |

| 0420                        | OBTILOON         | 15:0      | —             | —     | _     | —        | —        | —     | —           | —    | —        |       | —        | —    | -      | —      | —        | —      | 0000          |

| 8430                        | SBT1ECLRS        | 31:16     | _             | —     | _     | —        | —        | —     | —           | —    | —        | _     | —        | —    | _      | —      | —        | —      | 0000          |

| 0400                        | OBTIEGERG        | 15:0      | _             | —     | _     | —        | —        | —     | —           | —    | —        | _     | —        | —    | _      | —      | —        | CLEAR  | 0000          |

| 8438                        | SBT1ECLRM        | 31:16     | _             | —     | _     | —        | —        | —     | —           | —    | —        | _     | —        | —    | _      | —      | —        | —      | 0000          |

| 0 100                       | OBTIEGER         | 15:0      | _             | —     | —     | —        | —        | —     | —           | —    | —        | —     | —        | —    | —      | —      | —        | CLEAR  | 0000          |

| 8440                        | SBT1REG0         | 31:16     |               |       |       |          |          |       | 1           | BA   | SE<21:6> |       |          |      |        | •      |          |        | xxxx          |

| 0110                        | OBTINEOU         | 15:0      |               |       | BA    | SE<5:0>  |          |       | PRI         | —    |          |       | SIZE<4:0 | >    |        | —      | —        |        | xxxx          |

| 8450                        | SBT1RD0          | 31:16     | —             | —     | -     | —        | —        | —     | —           | —    | —        | _     | —        | —    | _      | —      | —        | —      | xxxx          |

| 8450                        |                  | 15:0      | _             | —     | _     | —        | —        | —     | —           | —    | —        | _     | —        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8458                        | SBT1WR0          | 31:16     | —             | —     | -     | —        | —        | —     | —           | —    | —        | _     | —        | —    | _      | —      | —        | —      | xxxx          |

| 0.00                        |                  | 15:0      | —             | —     | —     | —        | —        | —     | —           | —    | —        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8480                        | SBT1REG2         | 31:16     |               |       |       |          |          |       | 1           | BA   | SE<21:6> |       |          |      |        |        |          |        | XXXX          |

|                             |                  | 15:0      |               |       | BA    | SE<5:0>  |          |       | PRI         | —    |          |       | SIZE<4:0 | >    |        | —      | —        |        | XXXX          |

| 8490                        | SBT1RD2          | 31:16     | —             | —     | _     | —        | —        | _     | —           |      | —        |       |          | —    | -      | —      | —        | —      | XXXX          |

|                             | -                | 15:0      |               | —     | _     | _        | —        | _     | —           | _    | _        | _     |          | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | XXXX          |

| 8498                        | SBT1WR2          | 31:16     |               | —     | _     | _        | —        | _     | —           | _    | _        | _     |          | —    | —      | —      | —        | —      | XXXX          |

|                             |                  | 15:0      |               | —     | —     | —        | —        | —     | —           | —    | —        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | XXXX          |

| 84A0                        | SBT1REG3         | 31:16     |               |       |       |          |          |       |             |      | SE<21:6> |       |          |      |        |        |          |        | XXXX          |

|                             |                  | 15:0      |               |       |       | SE<5:0>  |          |       | PRI         | —    |          |       | SIZE<4:0 |      | -      | -      | —        | _      | XXXX          |

| 84B0                        | SBT1RD3          | 31:16     | _             |       |       |          |          |       | _           |      |          |       |          | _    | -      | -      | -        | -      | XXXX          |

|                             |                  | 15:0      | —             | —     |       | _        | _        |       | _           |      | _        | _     |          | _    | GROUP3 | GROUP2 | GROUP1   | GROUP0 |               |

| 84B8                        | SBT1WR3          | 31:16     |               | _     |       | _        | _        |       | _           |      |          | _     | _        |      |        |        |          |        | XXXX          |

|                             |                  | 15:0      |               | _     | —     | —        | —        | —     | _           | -    | -        | —     | —        |      | GROUP3 | GROUP2 | GROUP1   | GROUP0 |               |

| 84C0                        | SBT1REG4         | 31:16     |               |       |       |          |          |       |             |      | XXXX     |       |          |      |        |        |          |        |               |

|                             |                  | 15:0      |               |       | BA    | \SE<5:0> |          |       | PRI         |      |          |       | SIZE<4:0 |      | [      | _      |          | —      | XXXX          |

| 84D0                        | SBT1RD4          | 31:16     |               | _     | _     | _        | _        | _     | _           | _    | _        | _     | _        | _    |        |        |          | -      | XXXX          |

|                             |                  | 15:0      |               | _     |       | _        | _        |       | _           | —    | _        | _     |          |      | GROUP3 | GROUP2 | GROUP1   | GROUP0 | XXXX          |

| 84D8                        | SBT1WR4          | 31:16     | _             | _     |       |          |          | —     | _           | —    |          | _     |          | —    |        |        |          |        | XXXX          |

| Legen                       |                  | 15:0      | —             |       |       | —        | _        | _     | shown in he | —    | —        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | XXXX          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

NOTES:

## TABLE 12-11: PORTE REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |      | E    | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     | —     | —     | _     | -     | —     |       | —    | —    |              | —            | _            | _            | —            | —            | —            | —            | 0000          |

| 0400                        | ANGELE                          | 15:0      |       |       |       | -     | _     |       | —    | —    | ANSE7        | ANSE6        | ANSE5        | ANSE4        | —            | —            | —            | —            | 00F0          |

| 0410                        | TRISE                           | 31:16     | _     | -     | _     | -     | —     | _     | _    | _    | _            | —            | -            | -            | _            | _            | _            | _            | 0000          |

| 0410                        | TRISE                           | 15:0      | -     | -     | _     |       | _     |       | _    | _    | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 00FF          |

| 0420                        | PORTE                           | 31:16     |       |       | _     |       | _     |       | _    | _    |              | _            |              | -            | -            | _            | _            | _            | 0000          |

| 0420                        | PORTE                           | 15:0      |       |       | _     | —     | _     | —     | —    | —    | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     |       |       | _     |       | _     |       | _    | _    |              | _            |              | -            | -            | _            | _            | _            | 0000          |

| 0430                        |                                 | 15:0      | -     | -     | _     |       | _     |       | -    | _    | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 0440                        | ODCE                            | 31:16     | -     | -     | _     |       | _     |       | -    | _    | _            | _            |              |              | _            | _            | _            | -            | 0000          |

| 0440                        |                                 | 15:0      | -     | -     | _     |       | _     |       | -    | _    | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        | CNPUE                           | 31:16     | _     | _     | _     |       | —     |       | _    | _    | _            | -            |              |              | —            |              | _            | -            | 0000          |

| 0430                        |                                 | 15:0      | —     | —     | —     | —     | —     | -     | —    | —    | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0460                        | CNPDE                           | 31:16     | —     | —     | —     | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0400                        |                                 | 15:0      | —     | —     | —     | —     | —     | -     | —    | —    | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 0470                        | CNCONE                          | 31:16     | —     | —     | —     | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0470                        | CINCOINE                        | 15:0      | ON    | —     | SIDL  | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0480                        | CNENE                           | 31:16     | —     | —     | —     | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0400                        | CINEME                          | 15:0      | —     | —     | —     | —     | —     | -     | —    | —    | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     |       | —     |       | —    | —    | —            | -            |              | 1            | —            | —            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     | _     | _     | -     | _     | _     | _    | _    | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

Legend: x = Unknown value on Reset; -- = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## TABLE 12-22: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 4504                        | 000400                | 31:16     | -     | —     | —     | _     |       |       | _    | —    |      | —    | —    | _    |      | _     |        | —    | 0000       |

| 15B4                        | RPC13R                | 15:0      | _     | —     | —     | _     | _     | _     | _    | —    | _    | —    | —    | _    |      | RPC13 | R<3:0> |      | 0000       |

| 4500                        | 000440                | 31:16     |       | —     | —     | —     | —     | —     | —    | —    |      | —    | —    | _    |      | —     | —      | —    | 0000       |

| 15B8                        | RPC14R                | 15:0      | _     |       | —     | —     | —     | —     | _    |      | _    | —    |      | —    |      | RPC14 | R<3:0> |      | 0000       |

| 15C0                        | RPD0R                 | 31:16     |       | -     | _     |       |       | _     | _    | -    |      |      | -    | -    |      | _     | -      | _    | 0000       |

| 1500                        | RPDUR                 | 15:0      |       | -     | _     |       |       | _     | _    | -    |      |      | -    | -    |      | RPD0  | R<3:0> |      | 0000       |

| 15C4                        | RPD1R                 | 31:16     |       | _     | _     | —     | _     | _     | —    | _    |      | _    |      | —    |      | _     | _      | —    | 0000       |

| 1304                        | REDIK                 | 15:0      | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    |      | RPD1  | R<3:0> |      | 0000       |

| 15C8                        | RPD2R                 | 31:16     | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    | -    | —     | —      | —    | 0000       |

| 1300                        | RF D2R                | 15:0      | _     |       | —     | —     | —     | —     |      |      | _    |      |      | —    |      | RPD2  | R<3:0> |      | 0000       |

| 15CC                        | RPD3R                 | 31:16     | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    | -    | —     | —      | —    | 0000       |

| 1300                        | KF D3K                | 15:0      | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    |      | RPD3  | R<3:0> |      | 0000       |

| 15D0                        | RPD4R                 | 31:16     |       | _     | _     | —     | _     | _     | —    | _    |      | _    |      | —    |      | _     | _      | —    | 0000       |

|                             | KF D4K                | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | -    | _    | _    | —    |      | RPD4  | R<3:0> |      | 0000       |

| 15D4                        | RPD5R                 | 31:16     | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    | -    | —     | —      | —    | 0000       |

|                             |                       | 15:0      |       | _     | _     | —     | _     | _     | —    | _    |      | _    |      | —    |      | RPD5  | R<3:0> |      | 0000       |

| 15D8                        | RPD6R <sup>(2)</sup>  | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    | -    | _    | _    | —    | -    | —     | —      | —    | 0000       |

| 1300                        | KF DOK 7              | 15:0      | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    |      | RPD6  | R<3:0> |      | 0000       |

| 15DC                        | RPD7R <sup>(2)</sup>  | 31:16     |       | _     | _     | —     | _     | _     | —    | _    |      | _    |      | —    |      | _     | _      | —    | 0000       |

| 1300                        | KF D7 K <sup>e</sup>  | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | -    | _    | _    | —    |      | RPD7  | R<3:0> |      | 0000       |

| 15E4                        | RPD9R                 | 31:16     | -     |       | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    | -    | —     | —      | —    | 0000       |

| 1324                        | KF D9K                | 15:0      | _     | _     | —     | —     | —     | —     |      |      | _    |      |      | —    |      | RPD9  | R<3:0> |      | 0000       |

| 15E8                        | RPD10R                | 31:16     | _     | _     | —     | —     | —     | —     |      |      | _    |      |      | —    | _    | —     | —      | _    | 0000       |

| 1320                        | KI DIOK               | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPD10 | R<3:0> |      | 0000       |

| 15EC                        | RPD11R                | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1920                        | RIDIIR                | 15:0      | _     | _     | —     | —     | —     | —     |      |      | _    |      |      | —    |      | RPD11 | R<3:0> |      | 0000       |

| 15F0                        | RPD12R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | _    | —     | —      | —    | 0000       |

| 151.0                       | RI DIZR <sup>1</sup>  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD12 | R<3:0> |      | 0000       |

| 15F8                        | RPD14R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 101.0                       | IN DIAN               | 15:0      | _     |       | —     | —     | —     | —     |      |      | _    |      |      | _    |      | RPD14 | R<3:0> |      | 0000       |

| 15FC                        | RPD15R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     |        | —    | 0000       |

| 1010                        | IN DISK.              | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      |       | R<3:0> |      | 0000       |

| 160C                        | RPE3R                 | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1000                        |                       | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPE3  | R<3:0> |      | 0000       |

| 1614                        | RPE5R                 | 31:16     |       | —     | —     | -     | _     | —     | -    | —    |      | —    | —    | _    |      | -     | —      | —    | 0000       |

| 1014                        |                       | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | -    | —    | _    | —    |      | RPE5  | R<3:0> |      | 0000       |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is not available on 64-pin devices. Note 1:

2: This register is not available on 64-pin and 100-pin devices.

## **REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) (CONTINUED)**

bit 2 Unimplemented: Read as '0'

- bit 1 TCS: Timer Clock Source Select bit<sup>(1)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 **Unimplemented:** Read as '0'

- **Note 1:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- 2: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

....

\_\_\_\_\_

| REGISTI | ER 21-2:                 | I2CXSTAT: I <sup>-</sup> C STATUS REGISTER (CONTINUED)                                    |

|---------|--------------------------|-------------------------------------------------------------------------------------------|

| bit 5   | D_A: Data/               | Address bit (when operating as I <sup>2</sup> C slave)                                    |

|         | 1 = Indicate             | es that the last byte received was data                                                   |

|         | 0 = Indicate             | es that the last byte received was device address                                         |

|         | Hardware of              | clear at device address match. Hardware set by reception of slave byte.                   |

| bit 4   | P: Stop bit              |                                                                                           |

|         |                          | es that a Stop bit has been detected last<br>t was not detected last                      |

|         | Hardware s               | set or clear when Start, Repeated Start or Stop detected.                                 |

| bit 3   | S: Start bit             |                                                                                           |

|         | 0 = Start bi             | es that a Start (or Repeated Start) bit has been detected last<br>t was not detected last |

|         |                          | set or clear when Start, Repeated Start or Stop detected.                                 |

| bit 2   | R_W: Read                | d/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|         | 1 = Read -               | indicates data transfer is output from slave                                              |

|         |                          | indicates data transfer is input to slave                                                 |

|         | Hardware s               | set or clear after reception of I <sup>2</sup> C device address byte.                     |

| bit 1   | RBF: Rece                | ive Buffer Full Status bit                                                                |

|         |                          | e complete, I2CxRCV is full<br>e not complete, I2CxRCV is empty                           |

|         | Hardware s<br>reads I2Cx | set when I2CxRCV is written with received byte. Hardware clear when software RCV.         |

| bit 0   | TBF: Trans               | mit Buffer Full Status bit                                                                |

|         | 1 = Transm               | it in progress, I2CxTRN is full                                                           |

0 = Transmit complete, 12CxTRN is empty

2

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------------|-------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                     | U-0               | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                       | _                 | —                   | -                   | _                 | —                | _                |

| 00.40        | U-0               | U-0                     | U-0               | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                       | _                 | —                   | _                   | _                 | —                | —                |

| 45-0         | R/W-0             | U-0                     | R/W-0             | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | _                       | SIDL              | ADRMUX<1:0>         |                     | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0                   | R/W-0             | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | CSF<1:0> <sup>(1)</sup> |                   | CS2P <sup>(1)</sup> | CS1P <sup>(1)</sup> |                   | WRSP             | RDSP             |

## REGISTER 23-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit

- 1 = PMP enabled

- 0 = PMP disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins; upper 8 bits are not used

- 10 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port enabled

- 0 = PMWR/PMENB port disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port enabled

- 0 = PMRD/PMWR port disabled

- bit 7-6 **CSF<1:0>:** Chip Select Function bits<sup>(1)</sup>

- 11 = Reserved

- 10 = PMCS1 and PMCS2 function as Chip Select

- 01 = PMCS2 functions as Chip Select and PMCS1 functions as address bit 14

- 00 = PMCS1 and PMCS2 function as address bit 14 and address bit 15

- bit 5 ALP: Address Latch Polarity bit<sup>(1)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 **CS2P:** Chip Select 2 Polarity bit<sup>(1)</sup>

- 1 = Active-high (PMCS2)

- $0 = \text{Active-low}(\overline{PMCS2})$

- Note 1: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                     | —                     | _                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 22:46        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                     | —                     | _                 | —                 | —                 | —                 | —                | —                |  |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   | מחחע              | .12.0             |                  |                  |  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   | ADDR<13:8>        |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | ADDR<7:0>             |                       |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 23-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

## Legend:

bit 15

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 =Chip Select 1 is active 0 =Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------------|--------------------------|--------------------|-------------------|---------------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0                     | U-0                      | U-0                | U-0               | U-0                       | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                       | —                        | —                  | —                 | —                         | —                 | —                | —                |  |  |

| 00.40        | U-0                     | U-0                      | U-0                | U-0               | U-0                       | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                       | _                        | —                  | —                 | —                         | —                 | —                | —                |  |  |

| 45.0         | R/W-0                   | R/W-0                    | R/W-0              | R-0               | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup>     | PIV <sup>(2)</sup> | ALRMSYNC          | AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |  |

| 7:0          | R/W-0                   | R/W-0                    | R/W-0              | R/W-0             | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                         | ARPT<7:0> <sup>(2)</sup> |                    |                   |                           |                   |                  |                  |  |  |

#### REGISTER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER

#### Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is more than 32 real-time clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved

- 1011 = Reserved

- 11xx = Reserved

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

**Note:** This register is reset only on a Power-on Reset (POR).

## 28.2 ADC Control Registers

## TABLE 28-1: ADC REGISTER MAP

| SS                          |                  |           |         |         |               |          |           |         |         | Bits        |         |         |         |         |           |         |          |         | Τ          |

|-----------------------------|------------------|-----------|---------|---------|---------------|----------|-----------|---------|---------|-------------|---------|---------|---------|---------|-----------|---------|----------|---------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13         | 28/12    | 27/11     | 26/10   | 25/9    | 24/8        | 23/7    | 22/6    | 21/5    | 20/4    | 19/3      | 18/2    | 17/1     | 16/0    | All Resets |

|                             | AD1CON1          | 31:16     |         |         | FILTRDLY4:0>  | <b>`</b> |           |         | S       | TRGSRC<4:0: | >       |         | —       | _       | -         |         | EIE<2:0> |         | 0000       |

| D000                        | ADICONT          | 15:0      | ADCEN   | —       | ADSIDL        | —        | FRACT     | —       | —       | —           | —       | —       | —       | -       | —         | —       | —        | —       | 0000       |

| B004                        | AD1CON2          | 31:16     | ADCRDY  | -       | —             | -        | _         | _       | _       | —           |         |         |         | SAMC<   | :7:0>     |         |          |         | 0000       |

| D004                        | ADTOONZ          | 15:0      | _       | BOOST   | LOWPWR        | —        | —         | _       | ADCS    | EL<1:0>     |         |         |         | AD      | CDIV<6:0: | >       |          |         | 0000       |

| B008                        | AD1CON3          | 31:16     | CAL     | GSWTRG  | RQCNVRT       | —        | —         | _       |         | —           | —       | -       | _       | -       | —         | —       | -        | -       | 0000       |

| Dooo                        |                  | 15:0      | _       | —       | —             | V        | REFSEL<2: | 0>      |         |             | —       | _       |         |         | ADINS     | EL<5:0> |          |         | 0000       |

| BOOC                        | AD1IMOD          | 31:16     | _       | —       | —             | —        | _         | —       |         | LT<1:0>     |         | LT<1:0> | SH2AL   | -       | SH1AL     | -       | SH0AL    | -       | 0000       |

| 2000                        | / B HINOB        | 15:0      | —       | —       | _             | —        | SH5MC     | D<1:0>  | SH4M0   | OD<1:0>     | SH3M0   | DD<1:0> | SH2MC   |         |           | )D<1:0> | SH0MC    |         | 0000       |

| B010                        | AD1GIRQEN1       | 31:16     | AGIEN31 | AGIEN30 | AGIEN29       | AGIEN28  | AGIEN27   | AGIEN26 | AGIEN25 | AGIEN24     | AGIEN23 | AGIEN22 | AGIEN21 | AGIEN20 |           | AGIEN18 | AGIEN17  |         | _          |

| 2010                        |                  | 15:0      | AGIEN15 | AGIEN14 | AGIEN13       | AGIEN12  | AGIEN11   | AGIEN10 | AGIEN9  | AGIEN8      | AGIEN7  | AGIEN6  | AGIEN5  | AGIEN4  | AGIEN3    | AGIEN2  | AGIEN1   | AGIEN0  | 0000       |

| B014                        | AD1GIRQEN2       | 31:16     | —       | —       | _             | —        | —         | —       | —       | —           | —       | _       | —       | —       | —         | —       | —        | —       | 0000       |

|                             |                  | 15:0      | _       | —       | —             | AGIEN44  | AGIEN43   | AGIEN42 | AGIEN41 | AGIEN40     | AGIEN39 | AGIEN38 | AGIEN37 | AGIEN36 | AGIEN35   | AGIEN34 | AGIEN33  | AGIEN32 | 2 0000     |

| B018                        | AD1CSS1          | 31:16     | CSS31   | CSS30   | CSS29         | CSS28    | CSS27     | CSS26   | CSS25   | CSS24       | CSS23   | CSS22   | CSS21   | CSS20   | CSS19     | CSS18   | CSS17    | CSS16   | 0000       |

| 2010                        |                  | 15:0      | CSS15   | CSS14   | CSS13         | CSS12    | CSS11     | CSS10   | CSS9    | CSS8        | CSS7    | CSS6    | CSS5    | CSS4    | CSS3      | CSS2    | CSS1     | CSS0    | 0000       |

| B01C                        | AD1CSS2          | 31:16     | _       | —       | _             | —        | —         | —       | —       | —           | —       | —       | —       | —       | —         | —       | —        | _       | 0000       |

|                             |                  | 15:0      | —       | —       | -             | CSS44    | CSS43     | CSS42   | CSS41   | CSS40       | CSS39   | CSS38   | CSS37   | CSS36   | CSS35     | CSS34   | CSS33    | CSS32   | 0000       |

| B020                        | AD1DSTAT1        | 31:16     | ARDY31  | ARDY30  | ARDY29        | ARDY28   | ARDY27    | ARDY26  | ARDY25  | ARDY24      | ARDY23  | ARDY22  | ARDY21  | ARDY20  | ARDY19    | ARDY18  | ARDY17   | ARDY16  | _          |

|                             | -                | 15:0      | ARDY15  | ARDY14  | ARDY13        | ARDY12   | ARDY11    | ARDY10  | ARDY9   | ARDY9       | ARDY7   | ARDY6   | ARDY5   | ARDY4   | ARDY3     | ARDY2   | ARDY1    | ARDY0   | 0000       |

| B024                        | AD1DSTAT2        | 31:16     | —       | —       |               | —        |           | —       |         | —           | —       | —       | —       | —       | —         | —       | —        |         | 0000       |

|                             |                  | 15:0      | —       | —       | —             | ARDY44   | ARDY43    | ARDY42  | ARDY41  | ARDY40      | ARDY39  | ARDY38  | ARDY37  | ARDY36  | ARDY35    | ARDY34  | ARDY33   | ARDY32  |            |

| B028                        | AD1CMPEN1        | 31:16     | CMPE31  | CMPE30  | CMPE29        | CMPE28   | CMPE27    | CMPE26  | CMPE25  | CMPE24      | CMPE23  | CMPE22  | CMPE21  | CMPE20  | CMPE19    | CMPE18  | CMPE17   | CMPE16  |            |

|                             |                  | 15:0      | CMPE15  | CMPE14  | CMPE13        | CMPE12   | CMPE11    | CMPE10  | CMPE9   | CMPE8       | CMPE7   | CMPE6   | CMPE5   | CMPE4   | CMPE3     | CMPE2   | CMPE1    | CMPE0   | _          |

| B02C                        | AD1CMP1          | 31:16     |         |         |               |          |           |         |         | ACMPHI<15:0 |         |         |         |         |           |         |          |         | 0000       |

|                             |                  | 15:0      |         |         |               |          |           |         |         | ADCMPLO<15  |         |         |         |         |           |         |          |         | 0000       |

| B030                        | AD1CMPEN2        | 31:16     | CMPE31  | CMPE30  | CMPE29        | CMPE28   | CMPE27    | CMPE26  | CMPE25  | CMPE24      | CMPE23  | CMPE22  | CMPE21  | CMPE20  | CMPE19    |         | CMPE17   | CMPE16  |            |

|                             |                  | 15:0      | CMPE15  | CMPE14  | CMPE13        | CMPE12   | CMPE11    | CMPE10  | CMPE9   | CMPE8       | CMPE7   | CMPE6   | CMPE5   | CMPE4   | CMPE3     | CMPE2   | CMPE1    | CMPE0   | 0000       |

| B034                        | AD1CMP2          | 31:16     |         |         |               |          |           |         |         | ADCMPHI<15: |         |         |         |         |           |         |          |         | 0000       |

|                             |                  | 15:0      |         |         |               |          |           |         |         | ADCMPLO<15  |         |         |         |         |           |         |          |         | 0000       |

| B038                        | AD1CMPEN3        | 31:16     | CMPE31  | CMPE30  | CMPE29        | CMPE28   | CMPE27    | CMPE26  | CMPE25  | CMPE24      | CMPE23  | CMPE22  | CMPE21  | CMPE20  | CMPE19    |         | CMPE17   | CMPE16  | _          |

|                             |                  | 15:0      | CMPE15  | CMPE14  | CMPE13        | CMPE12   | CMPE11    | CMPE10  | CMPE9   | CMPE8       | CMPE7   | CMPE6   | CMPE5   | CMPE4   | CMPE3     | CMPE2   | CMPE1    | CMPE0   | 0000       |

| B03C                        | AD1CMP3          | 31:16     |         |         |               |          |           |         |         | ADCMPHI<15: |         |         |         |         |           |         |          |         | 0000       |

|                             |                  | 15:0      | 01056   | 011050- | 01/050-       | 0.00565  | 011050-   | 0110505 |         | ADCMPLO<15  |         | 010565  |         | 0110565 | 0.455     | 0.455   | 0.455/=  | 0405    | 0000       |

| B040                        | AD1CMPEN4        | 31:16     | CMPE31  | CMPE30  | CMPE29        | CMPE28   | CMPE27    | CMPE26  | CMPE25  | CMPE24      | CMPE23  | CMPE22  | CMPE21  | CMPE20  |           | CMPE18  | CMPE17   | CMPE16  | -          |

|                             |                  | 15:0      | CMPE15  | CMPE14  | CMPE13        | CMPE12   | CMPE11    | CMPE10  | CMPE9   | CMPE8       | CMPE7   | CMPE6   | CMPE5   | CMPE4   | CMPE3     | CMPE2   | CMPE1    | CMPE0   | 0000       |

| B044                        | AD1CMP4          | 31:16     |         |         |               |          |           |         |         | ADCMPHI<15: |         |         |         |         |           |         |          |         | 0000       |

|                             | d: v – unkn      | 15:0      |         |         | nlemented re: |          |           |         |         | ADCMPLO<15  | :0>     |         |         |         |           |         |          |         | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 28-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 21-19 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 18-16 | <b>EIE&lt;2:0&gt;:</b> Early Interrupt Enable bits <sup>(1)</sup><br>These bits select the number of clocks prior to the actual arrival of valid data when the associated<br>ARDYx bit is set. Since the ARDYx bit triggers an interrupt, these bits allow for early interrupt generation.<br>111 = The data ready bit, ARDYx, is set 7 TAD clocks prior to when the data is ready<br>100 = The data ready bit, ARDYx, is set 6 TAD clocks prior to when the data is ready<br>101 = The data ready bit, ARDYx, is set 5 TAD clocks prior to when the data is ready<br>100 = The data ready bit, ARDYx, is set 4 TAD clocks prior to when the data is ready<br>111 = The data ready bit, ARDYx, is set 3 TAD clocks prior to when the data is ready<br>112 = The data ready bit, ARDYx, is set 3 TAD clocks prior to when the data is ready<br>113 = The data ready bit, ARDYx, is set 2 TAD clocks prior to when the data is ready<br>114 = The data ready bit, ARDYx, is set 1 TAD clocks prior to when the data is ready<br>115 = The data ready bit, ARDYx, is set 1 TAD clock prior to when the data is ready<br>116 = The data ready bit, ARDYx, when the data is ready |

| bit 15    | ADCEN: ADC Operating Mode bit <sup>(2,4)</sup><br>1 = ADC module is enabled<br>0 = ADC module is off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 13    | ADSIDL: Stop in Idle Mode bit<br>1 = Discontinue module operation when device enters Idle mode<br>0 = Continue module operation in Idle mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 12    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 11    | FRACT: Fractional Data Output Format bit<br>1 = Fractional<br>0 = Integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 10-0  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Note 1:   | The early interrupt feature should not be used if polling any of the ARDY bits to determine if the conversion is complete. Early interrupts should be used only when all results from the ADC module are retrieved using an individual interrupt routine to fetch ADC results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2:        | The ADCEN bit should be set only after the ADC module has been configured. Changing ADC Configura-<br>tion bits when $ADCEN = 1$ , will result in unpredictable behavior. When $ADCEN = 0$ , the ADC clocks are<br>disabled, the internal control logic is reset, and all status flags used by the module are cleared. However,<br>the SFRs are available for reading and writing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3:        | The rising edge of the module output signal triggers an ADC conversion. See Figure 18-1 in <b>Section 18.0</b><br>"Output Compare" and Figure 31-1 in <b>Section 31.0</b> "Comparator" for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4:        | See 28.1 "ADC Configuration Requirements" for detailed ADC calibration information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Note: The ADC module is not available for normal operations until the ADCRDY bit (AD1CON2<31>) is set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | ADCAL             | <31:24>           |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | ADCAL<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | ADCAL<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                   |                   |                   | ADCAL<7:0>        |                   |                   |                  |                  |  |  |  |

## **REGISTER 28-19:** AD1CALx: ADC1 CALIBRATION REGISTER 'x' ('x' = 1-5)

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 ADCAL<31:0>: Calibration Data for the ADC Module bits

.

.

This data must be copied from the corresponding DEVADCx register. Refer to **Section 34.1** "**Configuration Bits**" for more information.

## 29.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

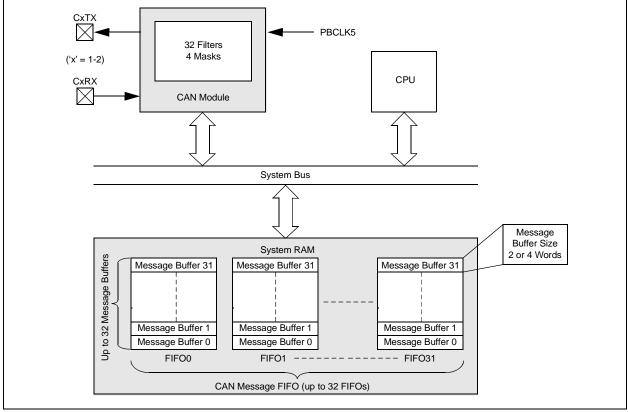

The Controller Area Network (CAN) module supports the following key features:

- Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 32 message FIFOs

- Each FIFO can have up to 32 messages for a total of 1024 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 32 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

DeviceNet<sup>™</sup> addressing support

- Additional Features:

- Loopback, Listen All Messages and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 System Bus

- Use of DMA is not required

- Dedicated time-stamp timer