Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ech100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                      |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                          |

|          |                        |                 |                 | Ti                       | imer1 thr   | ough Timer     | 9                                    |

| T1CK     | 48                     | 73              | A49             | 106                      | I           | ST             | Timer1 External Clock Input          |

| T2CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer2 External Clock Input          |

| T3CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer3 External Clock Input          |

| T4CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer4 External Clock Input          |

| T5CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer5 External Clock Input          |

| T6CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer6 External Clock Input          |

| T7CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer7 External Clock Input          |

| T8CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer8 External Clock Input          |

| T9CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer9 External Clock Input          |

|          | •                      | •               | •               | Real-                    | Time Clo    | ck and Cale    | endar                                |

| RTCC     | 46                     | 71              | A48             | 104                      | 0           | —              | Real-Time Clock Alarm/Seconds Output |

| Legend:  | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power               |

#### **TABLE 1-7:** TIMER1 THROUGH TIMER9 AND RTCC PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levelsO = OutputTTL = Transistor-transistor Logic input bufferPPS = Peripl

Analog = Analog input

PPS = Peripheral Pin Select

I = Input

DS60001191G-page 24

|           |                        | Pin Nu          | mber            |                          |             |                |                        |

|-----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------|

| Pin Name  | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description            |

|           |                        |                 | Unive           | ersal Asyn               | chronou     | IS Receive     | r Transmitter 1        |

| U1RX      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART1 Receive          |

| U1TX      | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART1 Transmit         |

| U1CTS     | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART1 Clear to Send    |

| U1RTS     | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART1 Ready to Send    |

|           |                        |                 | Unive           | rsal Asyn                | chronou     | s Receive      | r Transmitter 2        |

| U2RX      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART2 Receive          |

| U2TX      | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART2 Transmit         |

| U2CTS     | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART2 Clear To Send    |

| U2RTS     | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART2 Ready To Send    |

|           |                        |                 | Unive           | ersal Asyn               | chronou     | Is Receive     | r Transmitter 3        |

| U3RX      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART3 Receive          |

| U3TX      | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART3 Transmit         |

| U3CTS     | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART3 Clear to Send    |

| U3RTS     | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART3 Ready to Send    |

|           |                        |                 | Unive           | ersal Asyn               | chronou     | Is Receive     | r Transmitter 4        |

| U4RX      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART4 Receive          |

| U4TX      | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART4 Transmit         |

| U4CTS     | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART4 Clear to Send    |

| U4RTS     | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART4 Ready to Send    |

|           |                        |                 | Unive           | ersal Asyn               | chronou     | Is Receive     | r Transmitter 5        |

| U5RX      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART5 Receive          |

| U5TX      | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART5 Transmit         |

| U5CTS     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART5 Clear to Send    |

| U5RTS     | PPS                    | PPS             | PPS             | PPS                      | 0           | —              | UART5 Ready to Send    |

|           |                        | •               | Unive           | ersal Asyn               | chronou     | s Receive      | r Transmitter 6        |

| U6RX      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART6 Receive          |

| U6TX      | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART6 Transmit         |

| U6CTS     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART6 Clear to Send    |

| U6RTS     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART6 Ready to Send    |

| Legend: ( | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power |

#### **TABLE 1-8: UART1 THROUGH UART6 PINOUT I/O DESCRIPTIONS**

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

I = Input

© 2013-2016 Microchip Technology Inc.

# 3.3 **Power Management**

The processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during Idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 33.0 "Power-Saving Features".

## 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MZ family makes extensive use of local gatedclocks to reduce this dynamic power consumption.

# 3.4 L1 Instruction and Data Caches

# 3.4.1 INSTRUCTION CACHE (I-CACHE)

The I-Cache is an on-core memory block of 16 Kbytes. Because the I-Cache is virtually indexed, the virtual-tophysical address translation occurs in parallel with the cache access rather than having to wait for the physical address translation. The tag holds 22 bits of physical address, a valid bit, and a lock bit. The LRU replacement bits are stored in a separate array.

The I-Cache block also contains and manages the instruction line fill buffer. Besides accumulating data to be written to the cache, instruction fetches that reference data in the line fill buffer are serviced either by a bypass of that data, or data coming from the external interface. The I-Cache control logic controls the bypass function.

The processor core supports I-Cache locking. Cache locking allows critical code or data segments to be locked into the cache on a per-line basis, enabling the system programmer to maximize the efficiency of the system cache.

The cache locking function is always available on all I-Cache entries. Entries can then be marked as locked or unlocked on a per entry basis using the CACHE instruction.

## 3.4.2 DATA CACHE (D-CACHE)

The D-Cache is an on-core memory block of 4 Kbytes. This virtually indexed, physically tagged cache is protected. Because the D-Cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access. The tag holds 22 bits of physical address, a valid bit, and a lock bit. There is an additional array holding dirty bits and LRU replacement algorithm bits for each set of the cache. In addition to I-Cache locking, the processor core also supports a D-Cache locking mechanism identical to the I-Cache. Critical data segments are locked into the cache on a per-line basis. The locked contents can be updated on a store hit, but cannot be selected for replacement on a cache miss.

The D-Cache locking function is always available on all D-Cache entries. Entries can then be marked as locked or unlocked on a per-entry basis using the CACHE instruction.

# 3.4.3 ATTRIBUTES

The processor core I-Cache and D-Cache attributes are listed in the Configuration registers (see Register 3-1 through Register 3-4).

# 3.5 EJTAG Debug Support

The processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the processor core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

# 3.6 MIPS DSP ASE Extension

The MIPS DSP Application-Specific Extension Revision 2 is an extension to the MIPS32 architecture. This extension comprises new integer instructions and states that include new HI/LO accumulator register pairs and a DSP control register. This extension is crucial in a wide range of DSP, multimedia, and DSPlike algorithms covering Audio and Video processing applications. The extension supports native fractional format data type operations, register Single Instruction Multiple Data (SIMD) operations, such as add, subtract, multiply, and shift. In addition, the extension includes the following features that are essential in making DSP algorithms computationally efficient:

- Support for multiplication of complex operands

- Variable bit insertion and extraction

- Implementation and use of virtual circular buffers

- Arithmetic saturation and overflow handling support

- Zero cycle overhead saturation and rounding operations

NOTES:

# TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ess                          |                                 |               |        |       |          |       |                |       |      | Bit    | s      |        |        |        |        |        |        |         |    |

|------------------------------|---------------------------------|---------------|--------|-------|----------|-------|----------------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|----|

| VII LUAI AULIESS<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13    | 28/12 | 27/11          | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0    |    |

|                              | DCH1SSIZ                        | 31:16         | _      |       | —        |       |                | _     |      | —      |        | —      | _      | _      | _      |        | _      |         | 00 |

| 170                          | DOITISSIZ                       | 15:0          |        |       |          |       |                |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |         | 00 |

| 180                          | DCH1DSIZ                        | 31:16         | _      | _     | —        | _     | —              | _     | —    | _      | _      | —      | —      | —      | —      | —      | —      | —       | 0  |

| 100                          | DCITIDOIZ                       | 15:0          |        |       |          |       |                |       |      | CHDSIZ | <15:0> | -      | -      | -      |        |        | -      |         | 0  |

| 100                          | DCH1SPTR                        | 31:16         | —      | —     | —        | _     | —              | _     | —    | —      | —      |        |        |        | _      | —      | —      | —       | 0  |

| 190                          |                                 | 15:0          |        |       |          |       |                |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |         | 0  |

| 140                          | DCH1DPTR                        | 31:16         | —      | —     | —        | —     | —              | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —       | 0  |

| / 10                         |                                 | 15:0          |        |       |          |       |                |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |         | (  |

| B0                           | DCH1CSIZ                        | 31:16         | _      |       | —        | _     |                | _     | _    |        | —      | —      | _      | —      | —      | —      | —      | —       | (  |

| 80                           |                                 | 15:0          |        |       |          |       |                |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |         | (  |

| CO                           | DCH1CPTR                        | 31:16         | _      |       | —        | _     |                | _     | _    |        | —      | —      | _      | —      | —      | —      | —      | —       | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |         | (  |

| D0                           | DCH1DAT                         | 31:16         | —      | _     | —        | _     | —              | _     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —       | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      | CHPDAT | <15:0> |        |        |        |        |        | -      |         | (  |

| IE0                          | DCH2CON                         | 31:16         |        |       |          | CHPIG |                |       |      |        | -      | —      | —      | —      | —      | —      | —      | —       | (  |

|                              |                                 | 15:0          | CHBUSY | —     | CHPIGNEN | —     | CHPATLEN       | —     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | 21<1:0> | (  |

| IF0                          | DCH2ECON                        | 31:16         | —      | —     | —        | —     | —              | —     | —    | —      |        | -      | -      | CHAIR  |        |        |        |         | (  |

|                              |                                 | 15:0          |        |       |          | CHSIR | Q<7:0>         |       |      |        | CFORCE |        | PATEN  | SIRQEN | AIRQEN | —      | -      | —       | I  |

| 200                          | DCH2INT                         | 31:16         | —      |       | —        | _     | —              | _     | —    | _      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE  | (  |

|                              |                                 | 15:0          | —      | _     | —        | _     | —              | _     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF  | _  |

| 210                          | DCH2SSA                         | 31:16         |        |       |          |       |                |       |      | CHSSA  | <31:0> |        |        |        |        |        |        |         | (  |

| -                            |                                 | 15:0          |        |       |          |       |                |       |      |        |        |        |        |        |        |        |        |         | (  |

| 220                          | DCH2DSA                         | 31:16         |        |       |          |       |                |       |      | CHDSA- | <31:0> |        |        |        |        |        |        |         | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      |        |        |        |        |        |        |        |        |         | (  |

| 230                          | DCH2SSIZ                        | 31:16         | —      | _     | —        | _     | _              | _     | _    | -      | -      | —      | _      | —      | —      | _      | —      | _       | (  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      | CHSSIZ | <15:0> |        |        |        |        |        | r      |         | (  |

| 240                          | DCH2DSIZ                        | 31:16         | —      | _     | —        | _     | _              | _     | _    |        | -      | _      | _      | _      | _      | _      | —      | _       | (  |

|                              |                                 | 15:0<br>31:16 | _      |       |          |       |                |       |      | CHDSIZ | <15:0> |        |        |        |        | _      |        |         | 0  |

| 250                          | DCH2SPTR                        |               | _      | _     | _        | _     |                | _     |      |        |        | _      | _      | _      | _      | _      | _      | _       | 0  |

|                              |                                 | 15:0<br>31:16 |        |       |          |       | _              |       |      | CHSPTR | <10:0> |        | _      | _      | _      | _      |        |         | 0  |

| 260                          | DCH2DPTR                        |               | —      |       | —        | _     |                |       |      | CHDPTR |        |        |        |        |        | _      | —      | —       | 0  |

|                              |                                 | 15:0          |        |       |          |       |                |       |      |        | <10:0> |        |        |        |        |        |        |         | 0  |

| 270                          | DCH2CSIZ                        | 31:16         |        | _     | _        | _     | _              | _     | _    |        |        | _      |        | _      | _      |        | _      | —       | C  |

|                              |                                 | 15:0          |        |       |          |       | s '0'. Reset v |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |         | 0  |

PIC32MZ Embedded Connectivity (EC) Family

All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

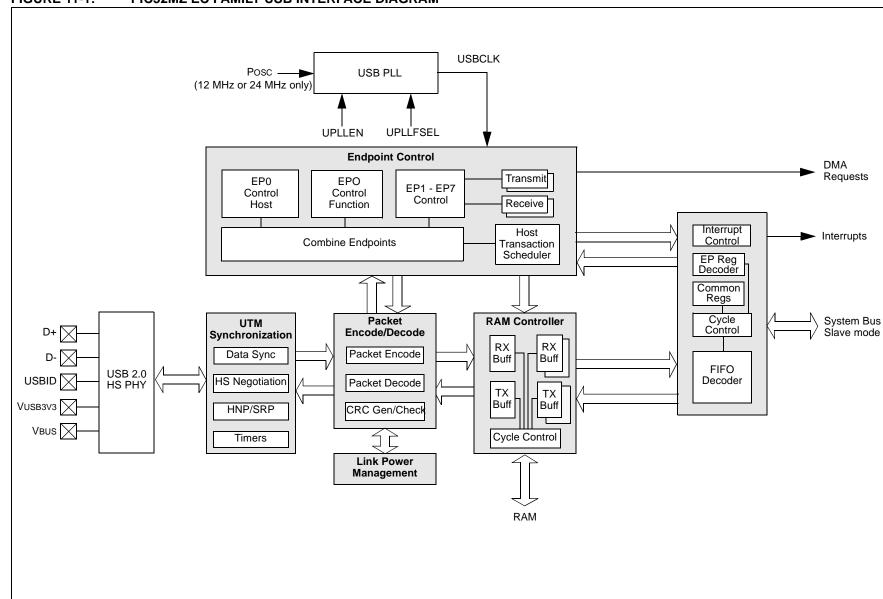

# FIGURE 11-1: PIC32MZ EC FAMILY USB INTERFACE DIAGRAM

|              |                   |                   |                   | OI I/ AI ALE      |                   | <b>NBBILE00</b>   |                  | (x = 10)         |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DMAADD            | R<31:24>          |                   |                  |                  |  |  |  |

| 00.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | DMAADE            | DR<15:8>          |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 7:0          | DMAADDR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 11-22: USBDMAxA: USB DMA CHANNEL 'x' MEMORY ADDRESS REGISTER ('x' = 1-8)

#### Legend:

| =ogonan           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-0 DMAADDR<31:0>: DMA Memory Address bits

This register identifies the current memory address of the corresponding DMA channel. The initial memory address written to this register during initialization must have a value such that its modulo 4 value is equal to '0'. The lower two bits of this register are read only and cannot be set by software. As the DMA transfer progresses, the memory address will increment as bytes are transferred.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | DMACOUI           | NT<31:24>         |                   |                  |                  |  |  |  |  |

| 22.16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DMACOUNT<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | DMACOU            | NT<15:8>          |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | DMACOUNT<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 11-23: USBDMAXN: USB DMA CHANNEL 'x' COUNT REGISTER ('X' = 1-8)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DMACOUNT<31:0>: DMA Transfer Count bits

This register identifies the current DMA count of the transfer. Software will set the initial count of the transfer which identifies the entire transfer length. As the count progresses this count is decremented as bytes are transferred.

#### TABLE 12-14: PORTG REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |           |               |               |               |               |       |       |              | Bit          | 5            |              |      |      |      |      |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|-------|-------|--------------|--------------|--------------|--------------|------|------|------|------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3 | 18/2 | 17/1         | 16/0         | All<br>Resets |

| 0600                        | ANSELG                          | 31:16     | _             | _             | —             | —             | _     | —     | —            |              |              | —            | —    | _    |      | —    |              | —            | 0000          |

|                             | /                               | 15:0      | ANSG15        | _             | _             | —             | _     | _     | ANSG9        | ANSG8        | ANSG7        | ANSG6        | _    | —    | _    | —    | —            | _            | 83C0          |

| 0610                        | TRISG                           | 31:16     | —             | —             | —             | —             | —     | —     | —            | —            | —            | —            | _    | —    | _    | —    | —            | —            | 0000          |

| 0010                        | 1100                            | 15:0      | TRISG15       | TRISG14       | TRISG13       | TRISG12       | _     | —     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | —    | _    | —    | TRISG1       | TRISG0       | F3C3          |

| 0620                        | PORTG                           | 31:16     | —             |               |               | —             | _     | _     |              |              |              | —            | _    | _    | _    | _    | _            |              | 0000          |

| 0020                        | TOKIO                           | 15:0      | RG15          | RG14          | RG13          | RG12          | —     | —     | RG9          | RG8          | RG7          | RG6          | —    | —    | -    | —    | RG1          | RG0          | xxxx          |

| 0630                        | LATG                            | 31:16     | _             | _             | _             | —             | —     | —     | _            | -            | -            | _            | _    | _    | _    | —    | —            | —            | 0000          |

| 0030                        | LAIG                            | 15:0      | LATG15        | LATG14        | LATG13        | LATG12        | —     | -     | LATG9        | LATG8        | LATG7        | LATG6        | _    | -    |      | _    | LATG1        | LATG0        | xxxx          |

| 0640                        | ODCG                            | 31:16     |               |               | —             | —             | —     | _     | —            |              |              | _            | —    | Ι    | -    | _    | —            | -            | 0000          |

| 0040                        | ODCG                            | 15:0      | ODCG15        | ODCG14        | ODCG13        | ODCG12        | —     | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | —    | Ι    | -    | _    | ODCG1        | ODCG0        | 0000          |

| 0650                        | CNPUG                           | 31:16     |               | —             | —             | —             | _     | _     | —            | —            | —            | —            | _    | —    | —    | _    | —            | —            | 0000          |

| 0050                        | CINFUG                          | 15:0      | CNPUG15       | CNPUG14       | CNPUG13       | CNPUG12       | _     | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | —    | —    | _    | CNPUG1       | CNPUG0       | 0000          |

| 0660                        | CNPDG                           | 31:16     |               | —             | —             | —             | _     | _     | —            | —            | —            | —            | _    | —    | —    | _    | —            | —            | 0000          |

| 0000                        | CINFUG                          | 15:0      | CNPDG15       | CNPDG14       | CNPDG13       | CNPDG12       | _     | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | —    | —    | _    | CNPDG1       | CNPDG0       | 0000          |

| 0670                        | CNCONG                          | 31:16     | Ι             | _             | _             | —             | _     | -     | _            | _            | _            | _            | _    | -    | _    | _    | —            | —            | 0000          |

| 0070                        | CINCOING                        | 15:0      | ON            | _             | SIDL          | —             | _     | -     | _            | _            | _            | _            | _    | -    | _    | _    | —            | —            | 0000          |

| 0000                        | CNENG                           | 31:16     | _             | _             | _             | _             | _     | _     | _            | _            | _            | _            | _    | _    | _    | —    | _            | —            | 0000          |

| 0660                        | CINEING                         | 15:0      | CNIEG15       | CNIEG14       | CNIEG13       | CNIEG12       | _     | _     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | _    | _    | _    | _    | CNIEG1       | CNIEG0       | 0000          |

|                             |                                 | 31:16     | _             | _             | —             | —             | —     | —     | —            | _            | _            | —            | _    | —    |      | —    | —            | —            | 0000          |

| 0690                        | CNSTATG                         | 15:0      | CN<br>STATG15 | CN<br>STATG14 | CN<br>STATG13 | CN<br>STATG12 | _     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | _    | _    | _    | —    | CN<br>STATG1 | CN<br>STATG0 | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

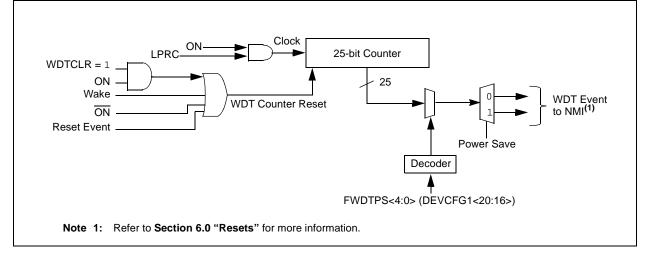

# 16.0 WATCHDOG TIMER (WDT)

This data sheet summarizes the features Note: of the PIC32MZ Embedded Connectivity (EC) Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

# FIGURE 16-1: WATCHDOG TIMER BLOCK DIAGRAM

# REGISTER 19-3: SPIxSTAT: SPI STATUS REGISTER

- bit 3 **SPITBE:** SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

- bit 2 Unimplemented: Read as '0'

- bit 1 SPITBF: SPI Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPITXB is full

- 0 = Transmit buffer is not full

Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

- bit 0 SPIRBF: SPI Receive Buffer Full Status bit

- 1 = Receive buffer, SPIxRXB is full

- 0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB. Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

# REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER (CONTINUED)

- bit 16 ACTIVE: Buffer Descriptor Processor Status bit

- 1 = BDP is active

- 0 = BDP is idle

- bit 15-0 **BDCTRL<15:0>:** Descriptor Control Word Status bits These bits contain the current descriptor control word.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | SID<1             | 0:3>              |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 23.10        |                   | SID<2:0>          |                   | —                 | MIDE              | —                 | EID<             | 17:16>           |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         |                   |                   |                   | EID<1             | 5:8>              |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | EID<7             | 7:0>              |                   |                  |                  |

#### REGISTER 29-9: CIRXMN: CAN ACCEPTANCE FILTER MASK N REGISTER (N = 0, 1, 2 OR 3)

#### Legend:

| - <b>J</b>        |                  |                                         |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include bit, SIDx, in filter comparison

- 0 = Bit SIDx is 'don't care' in filter operation

- bit 20 Unimplemented: Read as '0'

- bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

0 = Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include bit, EIDx, in filter comparison

- 0 = Bit EIDx is 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

#### REGISTER 29-20: CIFIFOCONn: CAN FIFO CONTROL REGISTER (n = 0 THROUGH 31) bit 6 TXABAT: Message Aborted bit<sup>(2)</sup> 1 = Message was aborted 0 = Message completed successfully TXLARB: Message Lost Arbitration bit<sup>(3)</sup> bit 5 1 = Message lost arbitration while being sent 0 = Message did not loose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a Receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest Message Priority 10 = High Intermediate Message Priority 01 = Low Intermediate Message Priority 00 = Lowest Message Priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits

- Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- **2:** This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- **3:** This bit is reset on any read of this register or when the FIFO is reset.

## REGISTER 34-4: DEVCFG1/ADEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

- 110 = Reserved

- 101 = LPRC

- 100 **= S**OSC

- 011 = Reserved

- 010 = Posc (HS, EC)

- 001 = SPLL

- 000 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

## TABLE 37-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CHA        | ARACTER | RISTICS                                              | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise<br>stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |   |              |       |                                                                                                                                |  |  |  |  |  |

|---------------|---------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                      | 6 Min. Typ. <sup>(1)</sup> Max.                                                                                                                     |   |              | Units | Conditions                                                                                                                     |  |  |  |  |  |

| DI50          | lı∟     | Input Leakage Current (Not                           | e 3)                                                                                                                                                | 1 | 1            |       |                                                                                                                                |  |  |  |  |  |

|               |         | I/O Ports (with the follow-<br>ing three exceptions) | —                                                                                                                                                   | — | <u>+</u> 1   | μA    | $\label{eq:VSS} \begin{split} VSS &\leq V PIN \leq V DD, \\ \mathbf{Pin} \mbox{ at high-impedance } \end{split}$               |  |  |  |  |  |

|               |         | SOSCI/RPC13/RC13                                     | —                                                                                                                                                   | — | <u>+</u> 500 | μA    | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                           |  |  |  |  |  |

|               |         | SOSCO/RPC14/TI1CK/<br>RC14                           | _                                                                                                                                                   | — | <u>+</u> 500 | μA    | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                           |  |  |  |  |  |

|               |         | RPF3/USBID/RF3                                       | —                                                                                                                                                   | — | <u>+</u> 500 | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance } \end{split}$ |  |  |  |  |  |

| DI51          | lı∟     | Analog Input Pins                                    | _                                                                                                                                                   | — | <u>+</u> 1   | μΑ    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance } \end{split}$ |  |  |  |  |  |

| DI55          | lı∟     | MCLR <sup>(2)</sup>                                  | _                                                                                                                                                   |   | <u>+</u> 1   | μA    | $V\text{SS} \leq V\text{PIN} \leq V\text{DD}$                                                                                  |  |  |  |  |  |

| DI56          | lı∟     | OSC1                                                 | —                                                                                                                                                   | — | <u>+</u> 1   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ HS \mbox{ mode} \end{array}$                                       |  |  |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the pin name tables (Table 2 through Table 4) for the 5V-tolerant pins.

- **6:** The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

#### TABLE 37-14: COMPARATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \end{array}$ |      |       |       |                                                                                        |

|--------------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|----------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                       | Min.                                                                                                                                                                                                                               | Тур. | Max.  | Units | Comments                                                                               |

| D300               | VIOFF  | Input Offset Voltage                  | —                                                                                                                                                                                                                                  | ±10  | —     | mV    | AVDD = VDD,<br>AVSS = VSS                                                              |

| D301               | VICM   | Input Common Mode Voltage             | 0                                                                                                                                                                                                                                  | _    | Vdd   | V     | AVDD = VDD,<br>AVss = Vss <b>(Note 2)</b>                                              |

| D302               | CMRR   | Common Mode Rejection Ratio           | 55                                                                                                                                                                                                                                 | —    | —     | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |

| D303               | TRESP  | Response Time                         | —                                                                                                                                                                                                                                  | 150  | —     | ns    | AVDD = VDD,<br>AVSS = VSS <b>(Notes 1,2)</b>                                           |

| D304               | ON20V  | Comparator Enabled to Output<br>Valid | _                                                                                                                                                                                                                                  |      | 10    | μS    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |

| D305               | IVref  | Internal Voltage Reference            | 1.194                                                                                                                                                                                                                              | 1.2  | 1.206 | V     | —                                                                                      |

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is guaranteed, but not characterized.

| DC CHARACTERISTICS |         |                                                             | Standard Operating Conditions (see Note 3): 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |                    |       |                                                                 |  |

|--------------------|---------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|

| Param.<br>No.      | Symbol  | Characteristics                                             | Min.                                                                                                                                                         | Тур. | Max.               | Units | Comments                                                        |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                            |      | 10                 | μs    | See Note 1                                                      |  |

| D313               | DACREFH | H CVREF Input Voltage                                       | AVss                                                                                                                                                         | _    | AVdd               | V     | CVRSRC with CVRSS = 0                                           |  |

|                    |         | Reference Range                                             | Vref-                                                                                                                                                        |      | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |

| D314               | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                                                                                                                            | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |

|                    |         |                                                             | 0.25 x<br>DACREFH                                                                                                                                            | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/32<br>step size |  |

| D315               | DACRES  | Resolution                                                  | —                                                                                                                                                            |      | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |

|                    |         |                                                             | —                                                                                                                                                            |      | DACREFH/32         |       | CVRCON <cvrr> = 0</cvrr>                                        |  |

| D316               | DACACC  | Absolute Accuracy <sup>(2)</sup>                            | —                                                                                                                                                            | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |

|                    |         |                                                             | —                                                                                                                                                            |      | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

| AC CHARACTERISTICS |         |                  |                        | IIREMENTS (MASTER MODE) (CONTINUED)Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |    |                                        |  |

|--------------------|---------|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|----------------------------------------|--|

| Param.<br>No.      | Symbol  | Characteristics  |                        | Min. <sup>(1)</sup>                                                                                                                                                                | Max. Units |    | Conditions                             |  |

| IM21               | TR:SCL  | SDAx and SCLx    | 100 kHz mode           | —                                                                                                                                                                                  | 1000       | ns | CB is specified to be                  |  |

|                    |         | Rise Time        | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                        | 300        | ns | from 10 to 400 pF                      |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | —                                                                                                                                                                                  | 300        | ns |                                        |  |

| IM25               | TSU:DAT | Data Input       | 100 kHz mode           | 250                                                                                                                                                                                | —          | ns | —                                      |  |

|                    |         | Setup Time       | 400 kHz mode           | 100                                                                                                                                                                                | _          | ns |                                        |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | 100                                                                                                                                                                                | _          | ns |                                        |  |

| IM26               | THD:DAT | Data Input       | 100 kHz mode           | 0                                                                                                                                                                                  | —          | μs | —                                      |  |

|                    |         | Hold Time        | 400 kHz mode           | 0                                                                                                                                                                                  | 0.9        | μs | 1                                      |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | 0                                                                                                                                                                                  | 0.3        | μs |                                        |  |

| IM30               | TSU:STA | Start Condition  | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | _          | μs | Only relevant for                      |  |

|                    |         | Setup Time       | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | _          | μs | Repeated Start                         |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | Трвськ2 * (BRG + 2)                                                                                                                                                                | _          | μs | condition                              |  |

| IM31               | THD:STA | Start Condition  | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | Ι          | μS | After this period, the                 |  |

|                    |         | Hold Time        | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | _          | μs | first clock pulse is                   |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | Трвськ2 * (BRG + 2)                                                                                                                                                                | _          | μs | generated                              |  |

| IM33               | Tsu:sto | Stop Condition   | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | _          | μs | —                                      |  |

|                    |         | Setup Time       | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                |            | μS |                                        |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | Трвськ2 * (BRG + 2)                                                                                                                                                                | _          | μs |                                        |  |

| IM34               | THD:STO | Stop Condition   | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | —          | ns | —                                      |  |

|                    |         | Hold Time        | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                                                                                                                                                | _          | ns | -                                      |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | Трвськ2 * (BRG + 2)                                                                                                                                                                | _          | ns |                                        |  |

| IM40               | TAA:SCL | Output Valid     | 100 kHz mode           | —                                                                                                                                                                                  | 3500       | ns | —                                      |  |

|                    |         | from Clock       | 400 kHz mode           | —                                                                                                                                                                                  | 1000       | ns | —                                      |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | —                                                                                                                                                                                  | 350        | ns | —                                      |  |

| IM45               | TBF:SDA | Bus Free Time    | 100 kHz mode           | 4.7                                                                                                                                                                                | —          | μs | The amount of time                     |  |

|                    |         |                  | 400 kHz mode           | 1.3                                                                                                                                                                                | —          | μs | the bus must be free                   |  |

|                    |         |                  | 1 MHz mode<br>(Note 2) | 0.5                                                                                                                                                                                | _          | μs | before a new<br>transmission can start |  |

| IM50               | Св      | Bus Capacitive L | oading                 | —                                                                                                                                                                                  | _          | pF | See parameter DO58                     |  |

| IM51               | Tpgd    | Pulse Gobbler De | elay                   | 52                                                                                                                                                                                 | 312        | ns | See Note 3                             |  |

# TABLE 37-35: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

3: The typical value for this parameter is 104 ns.

# PIC32MZ Embedded Connectivity (EC) Family

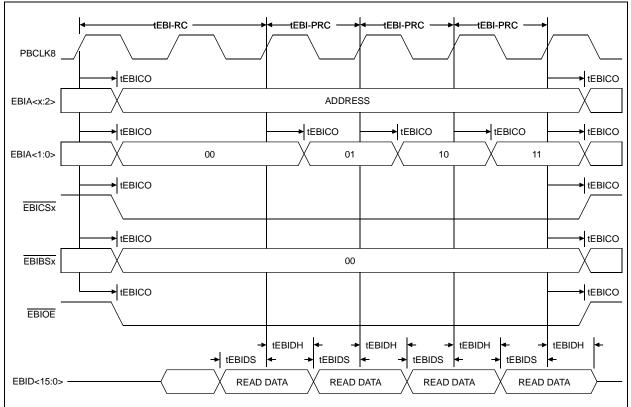

## FIGURE 37-28: EBI PAGE READ TIMING

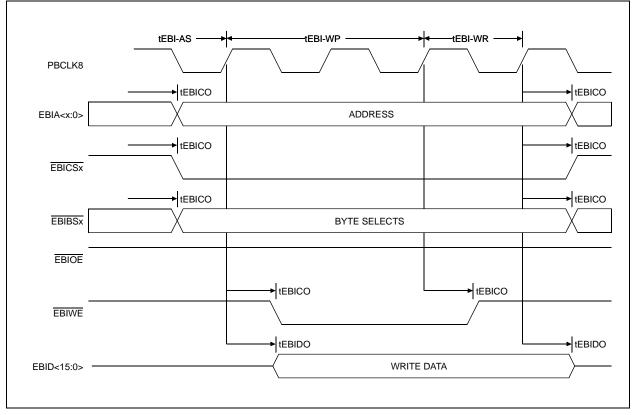

# FIGURE 37-29: EBI WRITE TIMING

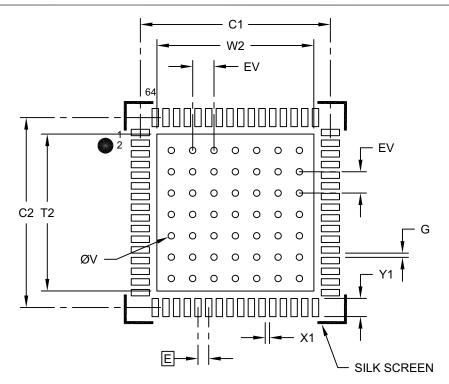

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 7.70x7.70mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |      |          |      |

|---------------------------------|-------------|------|----------|------|

| Dimension                       | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch                   | E           |      | 0.50 BSC |      |

| Optional Center Pad Width       | W2          |      |          | 7.50 |

| Optional Center Pad Length      | T2          |      |          | 7.50 |

| Contact Pad Spacing             | C1          |      | 8.90     |      |

| Contact Pad Spacing             | C2          |      | 8.90     |      |

| Contact Pad Width (X20)         | X1          |      |          | 0.30 |

| Contact Pad Length (X20)        | Y1          |      |          | 0.90 |

| Contact Pad to Center Pad (X20) | G           | 0.20 |          |      |

| Thermal Via Diameter            | V           |      | 0.30     |      |

| Thermal Via Pitch               | EV          |      | 1.00     |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2213B

## **Revision E (October 2015)**

| Note: | The                                          | Preliminary | footer, | which | was |  |

|-------|----------------------------------------------|-------------|---------|-------|-----|--|

|       | inadvertently omitted in the "D" revision of |             |         |       |     |  |

|       | the document was added.                      |             |         |       |     |  |

In this revision, all references to the V-Temp temperature range (-40°C to +105°C) were removed throughout the data sheet.

This revision also includes the following major changes, which are referenced by their respective chapter in Table B-5.

#### TABLE B-5: MAJOR SECTION UPDATES

| Section Name                                                                                                                                      | Update Description                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit MCUs (up to 2 MB Live-<br>Update Flash and 512 KB SRAM)<br>with Audio and Graphics<br>Interfaces, HS USB, Ethernet, and<br>Advanced Analog | Removed the shading from the RPF3/USBID/RF3 pins, which are not 5V tolerant in the Device Pin Tables (see Table 2 through Table 5).           |

| 1.0 "Device Overview"                                                                                                                             | Updated the USB Pinout I/O Description for the VUSB3V3 pin (see Table 1-14).                                                                  |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"                                                                                 | Added 2.10.2.1 "EMI Suppression Considerations".                                                                                              |

| 3.0 "CPU"                                                                                                                                         | Updated the <b>K0&lt;2:0&gt;:</b> Kseg0 Coherency Algorithm bits in the Configuration Register; CP0 Register 16, Select 0 (see Register 3-1). |

| 4.0 "Memory Organization"                                                                                                                         | The Boot and Alias Memory Map was updated (see Figure 4-5).                                                                                   |

|                                                                                                                                                   | Note 1 was added to the SFR Memory Map (see Table 4-1).                                                                                       |

|                                                                                                                                                   | Legal information for the System Bus was added (see <b>4.2</b> "System Bus Arbitration").                                                     |

| 7.0 "CPU Exceptions and Interrupt Controller"                                                                                                     | Updated the Notes in the Interrupt Register Map (see Table 7-3).                                                                              |

| 8.0 "Oscillator Configuration"                                                                                                                    | The System and Peripheral Clock Distribution was updated (see Table 8-1).                                                                     |

|                                                                                                                                                   | The <b>PLLIDIV&lt;2:0&gt;:</b> System PLL Input Clock Divider bits in the SPLLCON register were updated (see Register 8-3).                   |

| 9.0 "Prefetch Module"                                                                                                                             | The PRESTAT register was updated (see Register 9-2).                                                                                          |

| 11.0 "Hi-Speed USB with On-The-<br>Go (OTG)"                                                                                                      | The USBCSR2 register was updated (see Register 11-3).                                                                                         |