Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

|                            |                                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecm064-i-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-18: ALTERNATE ETHERNET MII PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                          |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                              |

| AERXD0   | _                      | 18              | _               | _                        | ı           | ST             | Alternate Ethernet Receive Data 0        |

| AERXD1   | _                      | 19              | _               | _                        | ı           | ST             | Alternate Ethernet Receive Data 1        |

| AERXD2   | _                      | 28              | _               | _                        | I           | ST             | Alternate Ethernet Receive Data 2        |

| AERXD3   | _                      | 29              | _               | _                        | I           | ST             | Alternate Ethernet Receive Data 3        |

| AERXERR  | _                      | 1               | _               | _                        | I           | ST             | Alternate Ethernet Receive Error Input   |

| AERXDV   | _                      | 12              | _               | _                        | I           | ST             | Alternate Ethernet Receive Data Valid    |

| AERXCLK  | _                      | 16              | _               | _                        | I           | ST             | Alternate Ethernet Receive Clock         |

| AETXD0   | _                      | 47              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Data 0       |

| AETXD1   | _                      | 48              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Data 1       |

| AETXD2   | _                      | 44              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Data 2       |

| AETXD3   | _                      | 43              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Data 3       |

| AETXERR  | _                      | 35              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Error        |

| AECOL    | _                      | 42              | _               | _                        | I           | ST             | Alternate Ethernet Collision Detect      |

| AECRS    | _                      | 41              | _               | _                        | I           | ST             | Alternate Ethernet Carrier Sense         |

| AETXCLK  | _                      | 66              | _               | _                        | I           | ST             | Alternate Ethernet Transmit Clock        |

| AEMDC    | _                      | 70              | _               | _                        | 0           | _              | Alternate Ethernet Management Data Clock |

| AEMDIO   | _                      | 71              | _               | _                        | I/O         | _              | Alternate Ethernet Management Data       |

| AETXEN   | _                      | 67              | _               | _                        | 0           |                | Alternate Ethernet Transmit Enable       |

Legend: CMOS = CMOS-compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

P = Power I = Input

TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

TABLE 1-19: ALTERNATE ETHERNET RMII PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                             |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|---------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                 |

| AERXD0   | 43                     | 18              | _               | _                        | I           | ST             | Alternate Ethernet Receive Data 0           |

| AERXD1   | 46                     | 19              | _               | _                        | I           | ST             | Alternate Ethernet Receive Data 1           |

| AERXERR  | 51                     | 1               | _               | _                        | I           | ST             | Alternate Ethernet Receive Error Input      |

| AETXD0   | 57                     | 47              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Data 0          |

| AETXD1   | 56                     | 48              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Data 1          |

| AEMDC    | 30                     | 70              | _               | _                        | 0           | _              | Alternate Ethernet Management Data Clock    |

| AEMDIO   | 49                     | 71              | _               | _                        | I/O         | _              | Alternate Ethernet Management Data          |

| AETXEN   | 50                     | 67              | _               | _                        | 0           | _              | Alternate Ethernet Transmit Enable          |

| AEREFCLK | 45                     | 16              | _               | _                        | I           | ST             | Alternate Ethernet Reference Clock          |

| AECRSDV  | 62                     | 12              | _               | _                        | I           | ST             | Alternate Ethernet Carrier Sense Data Valid |

Legend: CMC

CMOS = CMOS-compatible input or output

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input

O = Output

P = Power I = Input

or Logic input buffer PPS = Peripheral Pin Select

#### 2.9.1 SYSTEM DESIGN

#### 2.9.1.1 Impedance Matching

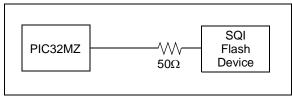

When selecting parts to place on high-speed buses, particularly the SQI bus, if the impedance of the peripheral device does not match the impedance of the pins on the PIC32MZ EC device to which it is connected, signal reflections could result, thereby degrading the quality of the signal.

If it is not possible to select a product that matches impedance, place a series resistor at the load to create the matching impedance. See Figure 2-4 for an example.

## FIGURE 2-4: SERIES RESISTOR

#### 2.9.1.2 PCB Layout Recommendations

The following list contains recommendations that will help ensure the PCB layout will promote the goals previously listed.

#### Component Placement

- Place bypass capacitors as close to their component power and ground pins as possible, and place them on the same side of the PCB

- Devices on the same bus that have larger setup times should be placed closer to the PIC32MZ EC device

## Power and Ground

- Multi-layer PCBs will allow separate power and ground planes

- Each ground pin should be connected to the ground plane individually

- Place bypass capacitor vias as close to the pad as possible (preferably inside the pad)

- If power and ground planes are not used, maximize width for power and ground traces

- Use low-ESR, surface-mount bypass capacitors

#### · Clocks and Oscillators

- Place crystals as close as possible to the PIC32MZ EC device OSC/SOSC pins

- Do not route high-speed signals near the clock or oscillator

- Avoid via usage and branches in clock lines (SQICLK)

- Place termination resistors at the end of clock lines

#### Traces

- Higher-priority signals should have the shortest traces

- Match trace lengths for parallel buses (EBIAx, EBIDx, SQIDx)

- Avoid long run lengths on parallel traces to reduce coupling

- Make the clock traces as straight as possible

- Use rounded turns rather than right-angle turns

- Have traces on different layers intersect on right angles to minimize crosstalk

- Maximize the distance between traces, preferably no less than three times the trace width

- Power traces should be as short and as wide as possible

- High-speed traces should be placed close to the ground plane

| o     |

|-------|

| Ś     |

| 60    |

| S6000 |

| ₹     |

| 19    |

| ᄎ     |

| 꿄     |

| ă     |

| ge    |

| ω     |

| _     |

|       |

TABLE 4-14: SYSTEM BUS TARGET 6 REGISTER MAP

| sse                         |                  |           |       |       |       |          |         |       |          |      | Bits          |       |          |      |        |        |         |        |               |  |  |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|---------|-------|----------|------|---------------|-------|----------|------|--------|--------|---------|--------|---------------|--|--|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11   | 26/10 | 25/9     | 24/8 | 23/7          | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |  |  |

| 9820                        | SBT6ELOG1        | 31:16     | MULTI | _     | _     | _        |         | CODE  | <3:0>    |      | _             | _     | _        | _    | _      | _      | _       | _      | 0000          |  |  |

| 3020                        | OBTOLLOGT        | 15:0      |       |       |       | INIT     | TD<7:0> |       |          |      |               | REGIO | N<3:0>   |      | _      | С      | MD<2:0> |        | 0000          |  |  |

| 9824                        | SBT6ELOG2        | 31:16     | _     | _     | _     | _        | _       | _     | _        | _    | _             | _     | _        | _    | _      | _      | _       | _      | 0000          |  |  |

| 3024                        | OBTOLLOGZ        | 15:0      | _     | _     | _     | _        | _       | _     | _        | _    | _             | _     | _        | _    | _      | _      | GROU    | P<1:0> | 0000          |  |  |

| 9828                        | SBT6ECON         | 31:16     | _     |       |       |          |         |       | _        | ERRP | _             | _     | _        | _    | _      | _      | _       | _      | 0000          |  |  |

| 3020                        | SBIOLOGIA        | 15:0      | _     | _     | _     | _        |         | _     | _        | _    | _             | _     | _        | _    | _      | _      | _       | _      | 0000          |  |  |

| 9830                        | SBT6ECLRS        | 31:16     | _     | _     | _     | _        | _       | _     | _        | _    | _             | _     | _        | _    | _      | _      | _       | _      | 0000          |  |  |

| 3000                        | OBTOLOLINO       | 15:0      | _     | _     | _     | _        | _       | _     | _        | _    |               |       |          |      | _      | _      | _       | CLEAR  | 0000          |  |  |

| 9838                        | SBT6ECLRM        | 31:16     | _     | _     | _     | _        | _       | _     | _        | _    | _             | _     | _        | _    | _      | _      | _       | _      | 0000          |  |  |

| 0000                        | OBTOLOLINI       | 15:0      | _     | _     | _     | _        | _       | _     | _        |      |               |       |          |      | _      | _      | _       | CLEAR  | 0000          |  |  |

| 9840                        | SBT6REG0         | 31:16     |       |       |       |          |         |       | 1        | BAS  | SE<21:6>      |       |          |      |        |        |         |        |               |  |  |

| 00.0                        |                  | 15:0      |       |       | BA    | \SE<5:0> |         |       | PRI      | _    |               |       | SIZE<4:0 | >    |        | _      | _       | _      | xxxx          |  |  |

| 9850                        | SBT6RD0          | 31:16     | _     | _     | _     | _        | _       | _     |          |      |               |       |          |      | _      | _      | _       | _      | xxxx          |  |  |

|                             |                  | 15:0      | _     | _     | _     | _        | _       | _     |          |      |               |       |          |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |  |  |

| 9858                        | SBT6WR0          | 31:16     | _     |       | _     | _        | _       | _     |          | _    |               |       |          |      | _      | _      | _       | _      | xxxx          |  |  |

|                             |                  | 15:0      | _     | _     | _     | _        | _       | _     | _        | _    | _             | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |  |  |

| 9860                        | SBT6REG1         | 31:16     |       |       |       |          |         |       |          | BAS  | SE<21:6>      |       |          |      |        | I      |         | 1      | xxxx          |  |  |

|                             |                  | 15:0      |       |       | BA    | \SE<5:0> |         | I     | PRI      | _    |               |       | SIZE<4:0 | >    | I      | _      | _       | _      | xxxx          |  |  |

| 9870                        | SBT6RD1          | 31:16     | _     | _     | _     |          |         |       |          |      |               |       |          |      | _      | _      | _       | _      | xxxx          |  |  |

|                             | - ***-           | 15:0      | _     | _     | _     | _        | _       | _     | _        | _    | GROUP3 GROUP2 |       |          |      | GROUP1 | GROUP0 | xxxx    |        |               |  |  |

| 9878                        | SBT6WR1          | 31:16     | _     | _     | _     | _        | _       | _     | _        | _    | _             | _     | _        | _    | _      | _      | _       | _      | xxxx          |  |  |

|                             |                  | 15:0      | _     | _     | _     | _        | -       | _     | <u> </u> |      | _             | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |  |  |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                   | -                    |                       |                   |                   | _                | _                |

| 22:40        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                   | _                    | _                     | _                 | _                 | _                | _                |

| 45.0         | R/W-0, HC         | R/W-0               | R-0, HS, HC          | R-0, HS, HC           | U-0               | U-0               | U-0              | U-0              |

| 15:8         | WR <sup>(1)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | U-0                 | U-0                  | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | SWAP              | _                   | _                    | _                     |                   | NVMOP             | <3:0>            |                  |

| Legend:           | HS = Hardware Set | HC = Hardware Cleared      |                    |

|-------------------|-------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit (1)

This bit cannot be cleared and can be set only when WREN = 1 and the unlock sequence has been performed.

1 = Initiate a Flash operation

0 = Flash operation is complete or inactive

bit 14 WREN: Write Enable bit<sup>(1)</sup>

1 = Enable writes to the WR bit and disables writes to the NVMOP<3:0> bits

0 = Disable writes to WR bit and enables writes to the NVMOP<3:0> bits

bit 13 WRERR: Write Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 = Voltage level is acceptable for programming

bit 11-8 Unimplemented: Read as '0'

bit 7 **SWAP:** Program Flash Bank Swap Control bit

This bit can be modified only when the WREN bit is '0' and the unlock sequence has been performed.

- 1 = Program Flash Bank 2 is mapped to the lower mapped region and program Flash Bank 1 is mapped to the upper mapped region

- 0 = Program Flash Bank 1 is mapped to the lower mapped region and program Flash Bank 2 is mapped to the upper mapped region

bit 6-4 Unimplemented: Read as '0'

Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

#### REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|-------------------|----------------------------|-------------------|----------------------|------------------|--|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |  |

| 31:24        |                   | PRI7SS            | <3:0> <sup>(1)</sup> |                   |                            | PRI6SS            | <3:0> <sup>(1)</sup> |                  |  |  |  |  |

| 00:40        | R/W-0 R/W-0       |                   | R/W-0                | R/W-0             | R/W-0                      | R/W-0 R/W-0 R/W-0 |                      |                  |  |  |  |  |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup> |                   | PRI4SS<3:0> <sup>(1)</sup> |                   |                      |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |  |

| 15:8         |                   | PRI3S             | S<3:0>               |                   |                            | PRI2SS            | <3:0> <sup>(1)</sup> |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | U-0                        | U-0               | U-0                  | R/W-0            |  |  |  |  |

| 7:0          |                   | PRI1SS            | <3:0> <sup>(1)</sup> | •                 | _                          | _                 | _                    | SS0              |  |  |  |  |

```

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

x = Bit is unknown

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

bit 31-28 PRI7SS<3:0>: Interrupt with Priority Level 7 Shadow Set bits(1)

1xxx = Reserved (by default, an interrupt with a priority level of 7 uses Shadow Set 0)

0111 = Interrupt with a priority level of 7 uses Shadow Set 7

0110 = Interrupt with a priority level of 7 uses Shadow Set 6

0001 = Interrupt with a priority level of 7 uses Shadow Set 1

0000 = Interrupt with a priority level of 7 uses Shadow Set 0

bit 27-24 PRI6SS<3:0>: Interrupt with Priority Level 6 Shadow Set bits<sup>(1)</sup>

1xxx = Reserved (by default, an interrupt with a priority level of 6 uses Shadow Set 0)

0111 = Interrupt with a priority level of 6 uses Shadow Set 7

0110 = Interrupt with a priority level of 6 uses Shadow Set 6

0001 = Interrupt with a priority level of 6 uses Shadow Set 1

0000 = Interrupt with a priority level of 6 uses Shadow Set 0

bit 23-20 PRI5SS<3:0>: Interrupt with Priority Level 5 Shadow Set bits(1)

1xxx = Reserved (by default, an interrupt with a priority level of 5 uses Shadow Set 0)

0111 = Interrupt with a priority level of 5 uses Shadow Set 7

0110 = Interrupt with a priority level of 5 uses Shadow Set 6

0001 = Interrupt with a priority level of 5 uses Shadow Set 1

0000 = Interrupt with a priority level of 5 uses Shadow Set 0

bit 19-16 PRI4SS<3:0>: Interrupt with Priority Level 4 Shadow Set bits(1)

1xxx = Reserved (by default, an interrupt with a priority level of 4 uses Shadow Set 0)

0111 = Interrupt with a priority level of 4 uses Shadow Set 7

0110 = Interrupt with a priority level of 4 uses Shadow Set 6

0001 = Interrupt with a priority level of 4 uses Shadow Set 1

0000 = Interrupt with a priority level of 4 uses Shadow Set 0

```

**Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

Legend:

### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | W-0 R/W-0 R/W-0   |                   | R/W-0            | R/W-0            |  |

| 31.24        | _                 | _                 | _                 | _ I               |                   |                   | IS3<             | :1:0>            |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | _                 | _                 |                   | IP2<2:0>          |                   | IS2<             | 1:0>             |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |

| 13.6         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<1:0>         |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 25-24 IS3<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 17-16 IS2<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 15-13 Unimplemented: Read as '0'

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

#### REGISTER 11-14: USBFIFOA: USB FIFO ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31.24        | _                 | _                 | F                 |                   | Rλ                | (FIFOAD<12:       | 8>               |                  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23.10        | RXFIFOAD<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15.6         | _                 | _                 | _                 |                   | TΣ                | (FIFOAD<12:       | 8>               |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | TXFIFO            | AD<7:0>           |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-16 RXFIFOAD<12:0>: Receive Endpoint FIFO Address bits

Start address of the endpoint FIFO in units of 8 bytes as follows:

1111111111111 = 0xFFF8

•

•

•

0000000000010 = 0x00100000000000001 = 0x0008

00000000000000 = 0x0000

bit 15-13 Unimplemented: Read as '0'

bit 12-0 TXFIFOAD<12:0>: Transmit Endpoint FIFO Address bits

Start address of the endpoint FIFO in units of 8 bytes as follows:

1111111111111 = 0xFFF8

•

•

0000000000010 = 0x0010 00000000000001 = 0x0008 000000000000000 = 0x0000

TABLE 12-19: PORTJ REGISTER MAP FOR 144-PIN DEVICES ONLY

| ess<br>)                    |                                 | ø         |               |               |               |               |               |               |              | Bits         |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0800                        | ANSELJ                          | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | 71110220                        | 15:0      | _             | _             | _             | _             | ANSJ11        | _             | ANSJ9        | ANSJ8        | _            | _            | _            | _            | _            | _            | _            | _            | 0B00          |

| 0810                        | TRISJ                           | 31:16     | _             | _             | _             |               | -             | _             | _            | -            | 1            | _            | _            | _            | _            | _            | 1            | _            | 0000          |

| 00.0                        |                                 | 15:0      | TRISJ15       | TRISJ14       | TRISJ13       | TRISJ12       | TRISJ11       | TRISJ10       | TRISJ9       | TRISJ8       | TRISJ7       | TRISJ6       | TRISJ5       | TRISJ4       | TRISJ3       | TRISJ2       | TRISJ1       | TRISJ0       | FFFF          |

| 0820                        | PORTJ                           | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            |              | _            | _            | _            |              | 0000          |

|                             |                                 | 15:0      | RJ15          | RJ14          | RJ13          | RJ12          | RJ11          | RJ10          | RJ9          | RJ8          | RJ7          | RJ6          | RJ5          | RJ4          | RJ3          | RJ2          | RJ1          | RJ0          | XXXX          |

| 0830                        | 301 IAT.J ⊨                     | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            |              | _            | _            | _            |              | 0000          |

|                             |                                 | 15:0      | LATJ15        | LATJ14        | LATJ13        | LATJ12        | LATJ11        | LATJ10        | LATJ9        | LATJ8        | LATJ7        | LATJ6        | LATJ5        | LATJ4        | LATJ3        | LATJ2        | LATJ1        | LATJ0        | XXXX          |

| 0840                        | ODCJ                            | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            |              | _            | _            | _            |              | 0000          |

|                             |                                 | 15:0      | ODCJ15        | ODCJ14        | ODCJ13        | ODCJ12        | ODCJ11        | ODCJ10        | ODCJ9        | ODCJ18       | ODCJ7        | ODCJ6        | ODCJ5        | ODCJ4        | ODCJ3        | ODCJ2        | ODCJ1        | ODCJ0        | 0000          |

| 0850                        | CNPUJ                           | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            |              | _            | _            | _            |              | 0000          |

|                             |                                 | 15:0      | CNPUJ15       | CNPUJ14       | CNPUJ13       | CNPUJ12       | CNPUJ11       | CNPUJ10       | CNPUJ9       | CNPUJ8       | CNPUJ7       | CNPUJ6       | CNPUJ5       | CNPUJ4       | CNPUJ3       | CNPUJ2       | CNPUJ1       | CNPUJ0       | 0000          |

| 0860                        | CNPDJ                           | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            |              | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | CNPDJ15       | CNPDJ14       | CNPDJ13       | CNPDJ12       | CNPDJ11       | CNPDJ10       | CNPDJ9       | CNPDJ8       | CNPDJ7       | CNPDJ6       | CNPDJ5       | CNPDJ4       | CNPDJ3       | CNPDJ2       | CNPDJ1       | CNPDJ0       | 0000          |

| 0870                        | CNCONJ                          | 31:16     | _             | _             | _             | _             |               | _             | _            |              |              | _            | _            |              | _            | _            |              | _            | 0000          |

|                             |                                 | 15:0      | ON            |               | SIDL          | _             |               | _             | _            | _            | _            |              | _            |              |              |              |              |              | 0000          |

| 0880                        | CNENJ                           | 31:16     | _             | _             | _             | _             |               | _             | _            |              |              | _            | _            |              | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | CNIEJ15       | CNIEJ14       | CNIEJ13       | CNIEJ12       | CNIEJ11       | CNIEJ10       | CNIEJ9       | CNIEJ8       | CNIEJ7       | CNIEJ6       | CNIEJ5       | CNIEJ4       | CNIEJ3       | CNIEJ2       | CNIEJ1       | CNIEJ0       | 0000          |

| 0000                        |                                 | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0890                        | CNSTATJ                         | 15:0      | CN<br>STATJ15 | CN<br>STATJ14 | CN<br>STATJ13 | CN<br>STATJ12 | CN<br>STATJ11 | CN<br>STATJ10 | CN<br>STATJ9 | CN<br>STATJ8 | CN<br>STATJ7 | CN<br>STATJ6 | CN<br>STATJ5 | CN<br>STATJ4 | CN<br>STATJ3 | CN<br>STATJ2 | CN<br>STATJ1 | CN<br>STATJ0 | 0000          |

**Legend:** x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity (EC) Family

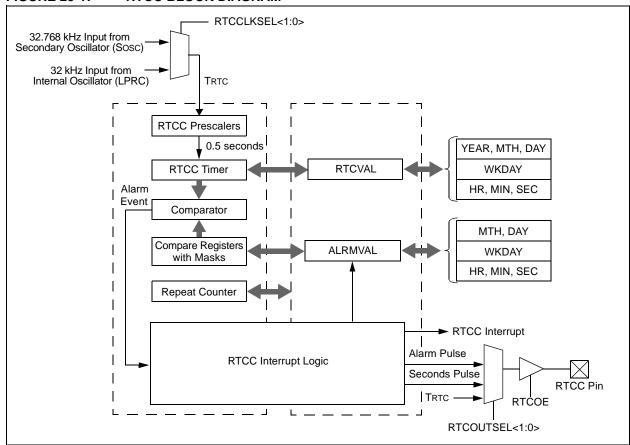

# 25.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are key features of the RTCC module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month, and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for smaller firmware overhead

- · Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- Calibrates up to 260 ppm of crystal error

- Uses external 32.768 kHz crystal or 32 kHz internal oscillator

- Alarm pulse, seconds clock, or internal clock output on RTCC pin

FIGURE 25-1: RTCC BLOCK DIAGRAM

TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |           | Bits  |                                    |       |       |       |       |        |                  |           |      |      |      |      |      |      |      |            |

|-----------------------------|------------------|-----------|-------|------------------------------------|-------|-------|-------|-------|--------|------------------|-----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name | Bit Range | 31/15 | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8             | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

|                             | ADADATAG         | 31:16     |       | ı                                  | I.    |       |       | ı     | ADC O  | utput Register   | 0 <31:16> | ı    |      |      | 1    |      |      |      | 0000       |

| R0R8                        | AD1DATA0         | 15:0      |       |                                    |       |       |       |       | ADC O  | utput Register   | 0 <15:0>  |      |      |      |      |      |      |      | 0000       |

| DODG                        | AD4DATA4         | 31:16     |       | i e                                |       |       |       |       |        |                  |           |      |      |      |      |      |      | 0000 |            |

| BOBC                        | AD1DATA1         | 15:0      |       | · · ·                              |       |       |       |       |        |                  |           |      |      |      |      |      |      | 0000 |            |

| POCO.                       | AD1DATA2         | 31:16     |       |                                    |       |       |       |       | ADC O  | utput Register : | 2 <31:16> |      |      |      |      |      |      |      | 0000       |

| В                           | ADIDATAZ         | 15:0      |       | · · ·                              |       |       |       |       |        |                  |           |      |      |      |      |      |      | 0000 |            |

| DOC4                        | AD1DATA3         | 31:16     |       | · · ·                              |       |       |       |       |        |                  |           |      |      |      |      |      |      | 0000 |            |

| B0C4                        | ADIDATAS         | 15:0      |       | ADC Output Register 3 <15:0>       |       |       |       |       |        |                  |           |      |      |      |      |      |      | 0000 |            |

| BUC8                        | AD1DATA4         | 31:16     |       | ' · · ·                            |       |       |       |       |        |                  |           |      |      |      |      |      |      | 0000 |            |

| В                           | ADIDAIA          | 15:0      |       |                                    |       |       |       |       |        |                  |           |      |      |      |      |      | 0000 |      |            |

| BUCC                        | AD1DATA5         | 31:16     |       |                                    |       |       |       |       | ADC O  | utput Register   | 5 <31:16> |      |      |      |      |      |      |      | 0000       |

| В                           | ADIDATAS         | 15:0      |       |                                    |       |       |       |       |        | Output Registe   |           |      |      |      |      |      |      |      | 0000       |

| BUDU                        | AD1DATA6         | 31:16     |       |                                    |       |       |       |       | ADC O  | utput Register   | 3 <31:16> |      |      |      |      |      |      |      | 0000       |

| ססס                         | ADIDATAO         | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| BUD4                        | AD1DATA7         | 31:16     |       |                                    |       |       |       |       | ADC O  | utput Register   | 7 <31:16> |      |      |      |      |      |      |      | 0000       |

| ם טם                        | ADIDAIA          | 15:0      |       |                                    |       |       |       |       | ADC O  | utput Register   | 7 <15:0>  |      |      |      |      |      |      |      | 0000       |

| BUD8                        | AD1DATA8         | 31:16     |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| ВОВО                        | ADIDATAG         | 15:0      |       |                                    |       |       |       |       | ADC O  | utput Register   | 8 <15:0>  |      |      |      |      |      |      |      | 0000       |

| BUDC                        | AD1DATA9         | 31:16     |       |                                    |       |       |       |       | ADC O  | utput Register ! | 9 <31:16> |      |      |      |      |      |      |      | 0000       |

| DODC                        | ADIDAIA9         | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| BOEO                        | AD1DATA10        | 31:16     |       |                                    |       |       |       |       | ADC Ou | tput Register 1  | 0 <31:16> |      |      |      |      |      |      |      | 0000       |

| DOLO                        | ADIBAIAIO        | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B0E4                        | AD1DATA11        | 31:16     |       |                                    |       |       |       |       |        | tput Register 1  |           |      |      |      |      |      |      |      | 0000       |

| DOLT                        | ADIDAIAII        | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B0F8                        | AD1DATA12        | 31:16     |       |                                    |       |       |       |       | ADC Ou | tput Register 1  | 2 <31:16> |      |      |      |      |      |      |      | 0000       |

| DOLO                        | 7.0 107117112    | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B0FC                        | AD1DATA13        | 31:16     |       |                                    |       |       |       |       |        | tput Register 1  |           |      |      |      |      |      |      |      | 0000       |

| 5020                        | , 12 12, 11, 110 | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B0F0                        | AD1DATA14        | 31:16     |       |                                    |       |       |       |       |        | tput Register 1  |           |      |      |      |      |      |      |      | 0000       |

| 2010                        | 7.0 107.17.11    | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B0F4                        | AD1DATA15        | 31:16     |       |                                    |       |       |       |       |        | tput Register 1  |           |      |      |      |      |      |      |      | 0000       |

| 20                          | , 12 12, 11, 110 | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B0F8                        | AD1DATA16        | 31:16     |       |                                    |       |       |       |       |        | tput Register 1  |           |      |      |      |      |      |      |      | 0000       |

| _ 3. 3                      |                  | 15:0      |       | ADC Output Register 16 <15:0> 0000 |       |       |       |       |        |                  |           |      |      |      |      |      |      |      |            |

| B0FC                        | AD1DATA17        | 31:16     |       |                                    |       |       |       |       |        | tput Register 1  |           |      |      |      |      |      |      |      | 0000       |

|                             |                  | 15:0      |       |                                    |       |       |       |       |        | utput Register   |           |      |      |      |      |      |      |      | 0000       |

| B100                        | AD1DATA18        | 31:16     | 1 0   |                                    |       |       |       |       |        |                  |           |      |      |      |      |      |      |      |            |

|                             | d: v = unkn      | 15:0      |       |                                    |       |       |       |       |        |                  |           |      |      | 0000 |      |      |      |      |            |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### AD1IMOD: ADC1 INPUT MODE CONTROL REGISTER (CONTINUED) REGISTER 28-4:

- bit 11-10 SH5MOD<1:0>: Input Configuration for S&H 5 (SH5) Select bits 11 = Differential inputs, two's complement (signed) data output 10 = Differential inputs, unipolar encoded (unsigned) data output 01 = Single ended inputs, two's complement (signed) data output 00 = Single ended inputs, unipolar encoded (unsigned) data output SH4MOD<1:0>: Input Configuration for S&H 4 (SH4) Select bits bit 9-8 11 = Differential inputs, two's complement (signed) data output 10 = Differential inputs, unipolar encoded (unsigned) data output 01 = Single ended inputs, two's complement (signed) data output 00 = Single ended inputs, unipolar encoded (unsigned) data output bit 7-6 SH3MOD<1:0>: Input Configuration for S&H 3 (SH3) Select bits 11 = Differential inputs, two's complement (signed) data output 10 = Differential inputs, unipolar encoded (unsigned) data output 01 = Single ended inputs, two's complement (signed) data output 00 = Single ended inputs, unipolar encoded (unsigned) data output bit 5-4 SH2MOD<1:0>: Input Configuration for S&H 2 (SH2) Select bits 11 = Differential inputs, two's complement (signed) data output 10 = Differential inputs, unipolar encoded (unsigned) data output 01 = Single ended inputs, two's complement (signed) data output 00 = Single ended inputs, unipolar encoded (unsigned) data output bit 3-2 SH1MOD<1:0>: Input Configuration for S&H 1 (SH1) Select bits 11 = Differential inputs, two's complement (signed) data output

- 10 = Differential inputs, unipolar encoded (unsigned) data output

- 01 = Single ended inputs, two's complement (signed) data output

- 00 = Single ended inputs, unipolar encoded (unsigned) data output

- bit 1-0 SH0MOD<1:0>: Input Configuration for S&H 0 (SH0) Select bits

- 11 = Differential inputs, two's complement (signed) data output

- 10 = Differential inputs, unipolar encoded (unsigned) data output

- 01 = Single ended inputs, two's complement (signed) data output

- 00 = Single ended inputs, unipolar encoded (unsigned) data output

- Note 1: Alternate inputs are only available for Class 1 Inputs.

- When an alternate input is selected (SHxALT<1:0>  $\neq$  0), the data, status, and control registers for the default Class 1 input are still used. Selecting an alternate input changes the physical input source only.

#### REGISTER 28-16: AD1TRG2: ADC1 INPUT CONVERT CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4           | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-----------------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | _                 | _                 | _                 | TRGSRC7<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | _                 | _                 | TRGSRC6<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 13.6         | _                 | _                 | _                 | TRGSRC5<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | 1                 | _                 | _                 | TRGSRC4<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-24 TRGSRC7<4:0>: Trigger Source for Conversion of Analog Channel AN7 Select bits<sup>(1)</sup>

11111 = Reserved

•

01101 = Reserved

01100 = Comparator 2 COUT(2)

01011 = Comparator 1 COUT<sup>(2)</sup>

$01010 = OCMP5^{(2)}$

01001 = OCMP3<sup>(2)</sup>

01000 = OCMP1<sup>(2)</sup>

00111 = TMR5 match

00110 = TMR3 match

00101 = TMR1 match

00100 = INT0

$00011 = STRIG^{(3)}$

00010 = Reserved

00001 = Global software trigger (GSWTRG)

00000 = No trigger

bit 23-21 Unimplemented: Read as '0'

bit 20-16 TRGSRC6<4:0>: Trigger Source for Conversion of Analog Channel AN6 Select bits<sup>(1)</sup>

See bits 28-24 for bit value definitions.

bit 15-13 Unimplemented: Read as '0'

bit 12-8 TRGSRC5<4:0>: Trigger Source for Conversion of Analog Channel AN5 Select bits<sup>(1)</sup>

See bits 28-24 for bit value definitions.

bit 7-5 Unimplemented: Read as '0'

bit 4-0 TRGSRC4<4:0>: Trigger Source for Conversion of Analog Channel AN4 Select bits<sup>(1)</sup>

See bits 28-24 for bit value definitions.

- Note 1: If the same trigger source is used for multiple ANx channels, the trigger source must wait until the hold time for all channels has completed (due to the last trigger) and the sample time for all ANx channels is satisfied before issuing the next trigger. This condition can cause hole insertions into the ADC pipeline and affect overall ADC throughput.

- 2: The rising edge of the associated module output signal triggers the conversion. Refer to the block diagram of the specific module for more information.

- 3: Using STRIG as the trigger source specifies this input to use the Scan Trigger source for its trigger. The STRGSRC<4:0> bits (AD1CON1<26:22>), as well as the appropriate CSSx bit(s) in the AD1CSS1 and AD1CSS2 registers must be set for proper scan operation.

#### REGISTER 29-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04:04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     | FLTEN3            | MSEL3<1:0>        |                   | FSEL3<4:0>        |                   |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     | FLTEN2            | MSEL2<1:0>        |                   | FSEL2<4:0>        |                   |                   |                  |                  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | FLTEN1            | MSEL              | 1<1:0>            |                   | F                 | SEL1<4:0>         |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN0            | MSEL0<1:0>        |                   | FSEL0<4:0>        |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN3: Filter 3 Enable bit

1 = Filter is enabled0 = Filter is disabled

bit 30-29 MSEL3<1:0>: Filter 3 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL3<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN2: Filter 2 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 22-21 MSEL2<1:0>: Filter 2 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 20-16 FSEL2<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

•

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 30-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER

bit 7 **RXDONE:** Receive Done Interrupt bit<sup>(2)</sup>

1 = RX packet was successfully received

0 = No interrupt pending

This bit is set whenever an RX packet is successfully received. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 6 **PKTPEND:** Packet Pending Interrupt bit<sup>(2)</sup>

1 = RX packet pending in memory

0 = RX packet is not pending in memory

This bit is set when the BUFCNT counter has a value other than '0'. It is cleared by either a Reset or by writing the BUFCDEC bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.

bit 5 **RXACT:** Receive Activity Interrupt bit<sup>(2)</sup>

1 = RX packet data was successfully received

0 = No interrupt pending

This bit is set whenever RX packet data is stored in the RXBM FIFO. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 4 **Unimplemented:** Read as '0'

bit 3 **TXDONE:** Transmit Done Interrupt bit<sup>(1)</sup>

1 = TX packet was successfully sent

0 = No interrupt pending

This bit is set when the currently transmitted TX packet completes transmission, and the Transmit Status Vector is loaded into the first descriptor used for the packet. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 2 **TXABORT:** Transmit Abort Condition Interrupt bit<sup>(1)</sup>

1 = TX abort condition occurred on the last TX packet

0 = No interrupt pending

This bit is set when the MAC aborts the transmission of a TX packet for one of the following reasons:

- Jumbo TX packet abort

- Underrun abort

- · Excessive defer abort

- · Late collision abort

- · Excessive collisions abort

This bit is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 1 **RXBUFNA:** Receive Buffer Not Available Interrupt bit<sup>(2)</sup>

1 = RX Buffer Descriptor Not Available condition has occurred

0 = No interrupt pending

This bit is set by a RX Buffer Descriptor Overrun condition. It is cleared by either a Reset or a CPU write of a '1' to the CLR register.

bit 0 **RXOVFLW:** Receive FIFO Over Flow Error bit<sup>(2)</sup>

1 = RX FIFO Overflow Error condition has occurred

0 = No interrupt pending

RXOVFLW is set by the RXBM Logic for an RX FIFO Overflow condition. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

Note 1: This bit is only used for TX operations.

This bit is only used for RX operations.

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## REGISTER 30-34: EMAC1MWTD: ETHERNET CONTROLLER MAC MII MANAGEMENT WRITE DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | -                 | _                 | _                 | _                 | _                |                  |

| 00:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | MWTD<15:8>        |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | MWTD<7:0>         |                   |                   |                   |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 MWTD<15:0>: MII Management Write Data bits

When written, a MII Management write cycle is performed using the 16-bit data and the preconfigured PHY and Register addresses from the EMAC1MADR register.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## REGISTER 30-35: EMAC1MRDD: ETHERNET CONTROLLER MAC MII MANAGEMENT READ DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6         | MRDD<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | MRDD<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 MRDD<15:0>: MII Management Read Data bits

Following a MII Management Read Cycle, the 16-bit data can be read from this location.

Note: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

### REGISTER 30-37: EMAC1SA0: ETHERNET CONTROLLER MAC STATION ADDRESS 0 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |  |

| 15:8         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 13.6         | STNADDR6<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 7.0          | STNADDR5<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  | P = Programmable bit  |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 STNADDR6<7:0>: Station Address Octet 6 bits

These bits hold the sixth transmitted octet of the station address.

bit 7-0 STNADDR5<7:0>: Station Address Octet 5 bits

These bits hold the fifth transmitted octet of the station address.

**Note 1:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

TABLE 33-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS<sup>(1)</sup> (CONTINUED)

| Peripheral               | PMDx bit Name | Register Name and Bit Location |

|--------------------------|---------------|--------------------------------|

| UART3                    | U3MD          | PMD5<2>                        |

| UART4                    | U4MD          | PMD5<3>                        |

| UART5                    | U5MD          | PMD5<4>                        |

| UART6                    | U6MD          | PMD5<5>                        |

| SPI1                     | SPI1MD        | PMD5<8>                        |

| SPI2                     | SPI2MD        | PMD5<9>                        |

| SPI3                     | SPI3MD        | PMD5<10>                       |

| SPI4                     | SPI4MD        | PMD5<11>                       |

| SPI5                     | SPI5MD        | PMD5<12>                       |

| SPI6                     | SPI6MD        | PMD5<13>                       |

| I2C1                     | I2C1MD        | PMD5<16>                       |

| I2C2                     | I2C2MD        | PMD5<17>                       |

| I2C3                     | I2C3MD        | PMD5<18>                       |

| I2C4                     | I2C4MD        | PMD5<19>                       |

| I2C5                     | I2C5MD        | PMD5<20>                       |

| USB <sup>(2)</sup>       | USBMD         | PMD5<24>                       |

| CAN1                     | CAN1MD        | PMD5<28>                       |

| CAN2                     | CAN2MD        | PMD5<29>                       |

| RTCC                     | RTCCMD        | PMD6<0>                        |

| Reference Clock Output 1 | REFO1MD       | PMD6<8>                        |

| Reference Clock Output 2 | REFO2MD       | PMD6<9>                        |

| Reference Clock Output 3 | REFO3MD       | PMD6<10>                       |

| Reference Clock Output 4 | REFO4MD       | PMD6<11>                       |

| PMP                      | PMPMD         | PMD6<16>                       |

| EBI                      | EBIMD         | PMD6<17>                       |

| SQI1                     | SQI1MD        | PMD6<23>                       |

| Ethernet                 | ETHMD         | PMD6<28>                       |

| DMA                      | DMAMD         | PMD7<4>                        |

| Random Number Generator  | RNGMD         | PMD7<20>                       |

| Crypto                   | CRYPTMD       | PMD7<22>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MZ EC Family Features" for the lists of available peripherals.

<sup>2:</sup> Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

## REGISTER 34-5: DEVCFG2/ADEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 3 Reserved: Write as '1'

- bit 2-0 FPLLIDIV<2:0>: PLL Input Divider bits

- 111 = Divide by 8

- 110 = Divide by 7

- 101 = Divide by 6

- 100 = Divide by 5

- 011 = Divide by 4

- 010 = Divide by 3

- 001 = Divide by 2

- 000 = Divide by 1

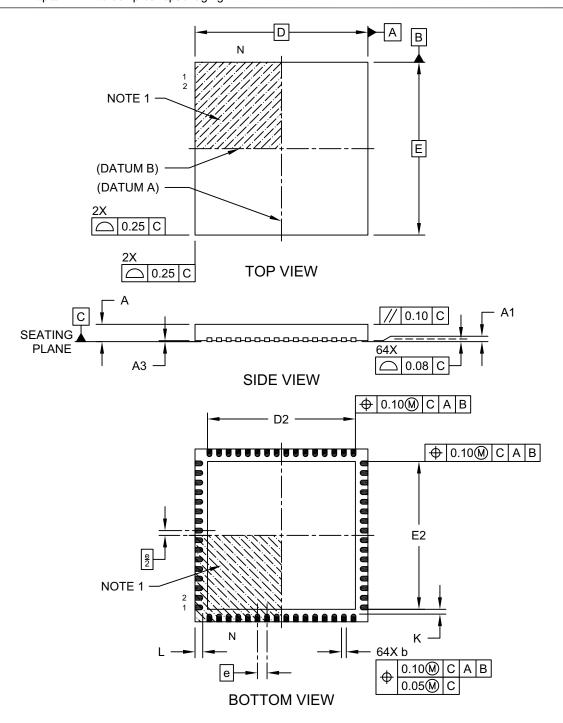

## 39.2 Package Details

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.70 x 7.70 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-213B Sheet 1 of 2