Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 98                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                  |

| Supplier Device Package    | 124-VTLA (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecm124t-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

100-PIN TQFP (TOP VIEW)

PIC32MZ0512EC(E/F/K)100 PIC32MZ1024EC(G/H/M)100 PIC32MZ1024EC(E/F/K)100 PIC32MZ2048EC(G/H/M)100

100

1

| Pin# | Full Pin Name                   |

|------|---------------------------------|

| 71   | EMDIO/AEMDIO/RPD0/RTCC/INT0/RD0 |

| 72   | SOSCI/RPC13/RC13                |

| 73   | SOSCO/RPC14/T1CK/RC14           |

| 74   | VDD                             |

| 75   | Vss                             |

| 76   | RPD1/SCK1/RD1                   |

| 77   | EBID14/ETXEN/RPD2/PMD14/RD2     |

| 78   | EBID15/ETXCLK/RPD3/PMD15/RD3    |

| 79   | EBID12/ETXD2/RPD12/PMD12/RD12   |

| 80   | EBID13/ETXD3/PMD13/RD13         |

| 81   | SQICS0/RPD4/RD4                 |

| 82   | SQICS1/RPD5/RD5                 |

| 83   | VDD                             |

| 84   | Vss                             |

| 85   | EBID11/ETXD1/RPF0/PMD11/RF0     |

|      |                                 |

| Pin# | Full Pin Name               |

|------|-----------------------------|

| 86   | EBID10/ETXD0/RPF1/PMD10/RF1 |

| 87   | EBID9/ETXERR/RPG1/PMD9/RG1  |

| 88   | EBID8/RPG0/PMD8/RG0         |

| 89   | TRCLK/SQICLK/RA6            |

| 90   | TRD3/SQID3/RA7              |

| 91   | EBID0/PMD0/RE0              |

| 92   | Vss                         |

| 93   | VDD                         |

| 94   | EBID1/PMD1/RE1              |

| 95   | TRD2/SQID2/RG14             |

| 96   | TRD1/SQID1/RG12             |

| 97   | TRD0/SQID0/RG13             |

| 98   | EBID2/PMD2/RE2              |

| 99   | EBID3/RPE3/PMD3/RE3         |

| 100  | EBID4/AN18/PMD4/RE4         |

#### Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select (PPS)" for restrictions.

- 2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note:

This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents provided in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

#### 2.1 Basic Connection Requirements

Note:

The PIC32MZ EC family of devices require a unique VDD ramp-up time. Please refer to parameter DC17 in Table 37-4 of **37.0** "Electrical Characteristics" before finalizing regulator design.

Getting started with the PIC32MZ EC family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- MCLR pin (see 2.3 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP™) and debugging purposes (see 2.4 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

Note:

The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 μF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close to

the pins as possible. It is recommended that the

capacitors be placed on the same side of the board

as the device. If space is constricted, the capacitor

can be placed on another layer on the PCB using a

via; however, ensure that the trace length from the

pin to the capacitor is within one-quarter inch

(6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

## 2.10 Considerations When Interfacing to Remotely Powered Circuits

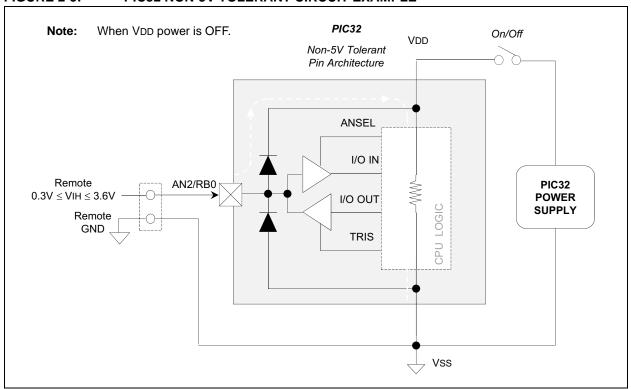

#### 2.10.1 NON-5V TOLERANT INPUT PINS

A quick review of the absolute maximum rating section in **37.0** "Electrical Characteristics" will indicate that the voltage on any non-5v tolerant pin may not exceed AVDD/VDD + 0.3V. Figure 2-5 shows an example of a remote circuit using an independent power source, which is powered while connected to a PIC32 non-5V tolerant circuit that is not powered.

FIGURE 2-5: PIC32 NON-5V TOLERANT CIRCUIT EXAMPLE

#### TABLE 3-3: COPROCESSOR 0 REGISTERS (CONTINUED)

| Register<br>Number | Register<br>Name | Function                                                                                              |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------|

| 23                 | Debug            | EJTAG debug register.                                                                                 |

|                    | TraceControl     | EJTAG trace control.                                                                                  |

|                    | TraceControl2    | EJTAG trace control 2.                                                                                |

|                    | UserTraceData1   | EJTAG user trace data 1 register.                                                                     |

|                    | TraceBPC         | EJTAG trace breakpoint register.                                                                      |

|                    | Debug2           | Debug control/exception status 1.                                                                     |

| 24                 | DEPC             | Program counter at last debug exception.                                                              |

|                    | UserTraceData2   | EJTAG user trace data 2 register.                                                                     |

| 25                 | PerfCtl0         | Performance counter 0 control.                                                                        |

|                    | PerfCnt0         | Performance counter 0.                                                                                |

|                    | PerfCtl1         | Performance counter 1 control.                                                                        |

|                    | PerfCnt1         | Performance counter 1.                                                                                |

| 26                 | ErrCtl           | Software test enable of way-select and data RAM arrays for I-Cache and D-Cache (microAptiv MPU only). |

| 27                 | Reserved         | Reserved in the PIC32 core.                                                                           |

| 28                 | TagLo/DataLo     | Low-order portion of cache tag interface (microAptiv MPU only).                                       |

| 29                 | Reserved         | Reserved in the PIC32 core.                                                                           |

| 30                 | ErrorEPC         | Program counter at last error exception.                                                              |

| 31                 | DeSave           | Debug exception save.                                                                                 |

#### 3.3 Power Management

The processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see **Section 33.0** "Power-Saving Features".

#### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MZ family makes extensive use of local gated-clocks to reduce this dynamic power consumption.

#### 3.4 L1 Instruction and Data Caches

#### 3.4.1 INSTRUCTION CACHE (I-CACHE)

The I-Cache is an on-core memory block of 16 Kbytes. Because the I-Cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access rather than having to wait for the physical address translation. The tag holds 22 bits of physical address, a valid bit, and a lock bit. The LRU replacement bits are stored in a separate array.

The I-Cache block also contains and manages the instruction line fill buffer. Besides accumulating data to be written to the cache, instruction fetches that reference data in the line fill buffer are serviced either by a bypass of that data, or data coming from the external interface. The I-Cache control logic controls the bypass function.

The processor core supports I-Cache locking. Cache locking allows critical code or data segments to be locked into the cache on a per-line basis, enabling the system programmer to maximize the efficiency of the system cache.

The cache locking function is always available on all I-Cache entries. Entries can then be marked as locked or unlocked on a per entry basis using the CACHE instruction.

#### 3.4.2 DATA CACHE (D-CACHE)

The D-Cache is an on-core memory block of 4 Kbytes. This virtually indexed, physically tagged cache is protected. Because the D-Cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access. The tag holds 22 bits of physical address, a valid bit, and a lock bit. There is an additional array holding dirty bits and LRU replacement algorithm bits for each set of the cache.

In addition to I-Cache locking, the processor core also supports a D-Cache locking mechanism identical to the I-Cache. Critical data segments are locked into the cache on a per-line basis. The locked contents can be updated on a store hit, but cannot be selected for replacement on a cache miss.

The D-Cache locking function is always available on all D-Cache entries. Entries can then be marked as locked or unlocked on a per-entry basis using the CACHE instruction.

#### 3.4.3 ATTRIBUTES

The processor core I-Cache and D-Cache attributes are listed in the Configuration registers (see Register 3-1 through Register 3-4).

#### 3.5 EJTAG Debug Support

The processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the processor core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

#### 3.6 MIPS DSP ASE Extension

The MIPS DSP Application-Specific Extension Revision 2 is an extension to the MIPS32 architecture. This extension comprises new integer instructions and states that include new HI/LO accumulator register pairs and a DSP control register. This extension is crucial in a wide range of DSP, multimedia, and DSP-like algorithms covering Audio and Video processing applications. The extension supports native fractional format data type operations, register Single Instruction Multiple Data (SIMD) operations, such as add, subtract, multiply, and shift. In addition, the extension includes the following features that are essential in making DSP algorithms computationally efficient:

- Support for multiplication of complex operands

- · Variable bit insertion and extraction

- · Implementation and use of virtual circular buffers

- Arithmetic saturation and overflow handling support

- Zero cycle overhead saturation and rounding operations

| TARI F 10-3. | DMA CHANNEL | 0 THROUGH CHANNEL  | 7 REGISTER MAP   |

|--------------|-------------|--------------------|------------------|

| IADLE 10-3.  |             | U I HROUGH CHANNEL | . / NEGIOTEN WAR |

| sse                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                 |                                                                                     |                       |          |        |          |       |      | Bit         | s        |        |        |           |        |          |        |        |            |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------|-----------------------|----------|--------|----------|-------|------|-------------|----------|--------|--------|-----------|--------|----------|--------|--------|------------|

| Virtual Address<br>(BF81_#)                       | Register<br>Name <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit Range         | 31/15                                                                               | 30/14                 | 29/13    | 28/12  | 27/11    | 26/10 | 25/9 | 24/8        | 23/7     | 22/6   | 21/5   | 20/4      | 19/3   | 18/2     | 17/1   | 16/0   | All Resets |

| 4000                                              | DOLLOCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | •                                                                                   |                       |          | CHPIG  | N<7:0>   |       | •    |             | _        | _      | _      | _         | _      | _        | _      | _      | 0000       |

| 1060                                              | DCH0CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15:0              | CHBUSY                                                                              | _                     | CHPIGNEN | _      | CHPATLEN | _     | _    | CHCHNS      | CHEN     | CHAED  | CHCHN  | CHAEN     | _      | CHEDET   | CHPR   | I<1:0> | 0000       |

| 1070                                              | DCH0ECON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | _                                                                                   | _                     | _        | _      | _        | _     | _    | _           |          |        |        | CHAIR     | Q<7:0> |          |        |        | 00FF       |

| 1070                                              | DOI IOLOGIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15:0              |                                                                                     |                       |          | CHSIR  | Q<7:0>   |       |      |             | CFORCE   | CABORT | PATEN  | SIRQEN    | AIRQEN | _        | _      | _      | FF00       |

| 1080                                              | DCH0INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31:16             | _                                                                                   | _                     | _        | _      | _        | _     | _    | _           | CHSDIE   | CHSHIE | CHDDIE | CHDHIE    | CHBCIE | CHCCIE   | CHTAIE | CHERIE | 0000       |

| 1000                                              | DOTTON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15:0              | _                                                                                   | _                     | _        | _      | _        | _     | _    | _           | CHSDIF   | CHSHIF | CHDDIF | CHDHIF    | CHBCIF | CHCCIF   | CHTAIF | CHERIF | 0000       |

| 1090                                              | DCH0SSA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31:16<br>15:0     |                                                                                     | CHSSA<31:0> 0000 0000 |          |        |          |       |      |             |          |        |        |           |        |          |        |        |            |

| 10A0                                              | DCH0DSA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31:16<br>15:0     |                                                                                     |                       |          |        |          |       |      | CHDSA       | <31:0>   |        |        |           |        |          |        |        | 0000       |

| 10P0                                              | DCH0SSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | _                                                                                   | _                     | _        | _      | _        | _     | _    | _           | _        | _      | _      | _         | _      | _        | _      | _      | 0000       |

| 1000                                              | DCHUSSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15:0 CHSSIZ<15:0> |                                                                                     |                       |          |        |          |       |      |             |          | 0000   |        |           |        |          |        |        |            |

| 10C0 DCH0DSIZ 31:16 — — — — — — — — — — — — — — — |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                                     |                       |          |        |          |       |      | _           | _        |        | 0000   |           |        |          |        |        |            |

| 15:0 CHDSIZ<15:0>                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                                     |                       |          |        |          |       |      |             | 0000     |        |        |           |        |          |        |        |            |

| 1000                                              | DCH0SPTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | _                                                                                   |                       | _        |        | _        |       | _    | _           | _        | _      | _      | _         | _      | _        |        | _      | 0000       |

| 1000                                              | DOTTOOL TIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15:0              |                                                                                     |                       |          |        |          |       |      | CHSPTR      | <15:0>   |        |        |           |        |          |        |        | 0000       |

| 10F0                                              | DCH0DPTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | _                                                                                   | _                     | _        | _      | _        | _     | _    | _           | _        | _      | _      | _         | _      | _        | _      | _      | 0000       |

| .020                                              | 2011021 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15:0              |                                                                                     |                       |          |        |          |       | 1    | CHDPTR      | <15:0>   | 1      |        |           | I      |          |        |        | 0000       |

| 10F0                                              | DCH0CSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | _                                                                                   |                       | _        | _      | _        |       | _    |             | _        | _      | _      | _         | _      | _        |        | _      | 0000       |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15:0              |                                                                                     |                       |          |        |          |       |      | CHCSIZ      | <15:0>   | ı      |        |           |        |          |        |        | 0000       |

| 1100                                              | DCH0CPTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16             | _                                                                                   |                       | _        |        | _        |       | _    |             | <u> </u> | _      | _      | _         | _      | _        |        | _      | 0000       |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15:0              |                                                                                     |                       |          |        |          |       |      | CHCPTR      | <15:0>   |        |        |           |        |          |        |        | 0000       |

| 1110                                              | DCH0DAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31:16             | _                                                                                   |                       | _        |        | _        |       | _    | CHPDAT      | -45.0:   | _      |        |           | _      | _        |        | _      | 0000       |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15:0              |                                                                                     |                       |          | OLIDIO | N. 70    |       |      | CHPDAI      | <15:0>   |        |        |           |        |          |        |        | 0000       |